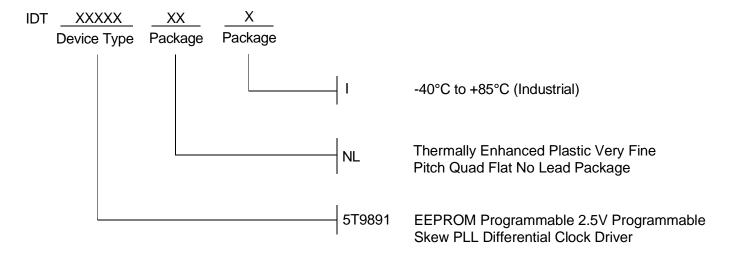

# EEPROM PROGRAMMABLE 2.5V PROGRAMMABLE SKEW PLL DIFFERENTIAL CLOCK DRIVER

IDT5T9891

## **FEATURES**:

- 2.5 Vpp

- · 6 pairs of programmable skew outputs

- Low skew: 100ps all outputs at same interface level, 250ps all outputs at different interface levels

- · Selectable positive or negative edge synchronization

- Tolerant of spread spectrum input clock

- Synchronous output enable

- · Selectable inputs

- Input frequency: 4.17MHz to 250MHz

- Output frequency: 12.5MHz to 250MHz

- · Internal non-volatile EEPROM

- · JTAG or I<sup>2</sup>C bus serial interface for programming

- · Hot insertable and over-voltage tolerant inputs

- Feedback divide selection with multiply ratios of (1-6, 8, 10, 12)

- Selectable HSTL, eHSTL, 1.8V/2.5V LVTTL, or LVEPECL input interface

- Selectable HSTL, eHSTL, or 1.8V/2.5V LVTTL output interface for each output bank

- Selectable differential or single-ended inputs and six differential outputs

- · PLL bypass for DC testing

- External differential feedback, internal loop filter

- Low Jitter: <75ps cycle-to-cycle, all outputs at same interface level: <100ps cycle-to-cycle all outputs at different interface levels

- · Power-down mode

- · Lock indicator

- · Available in VFQFPN package

## **DESCRIPTION:**

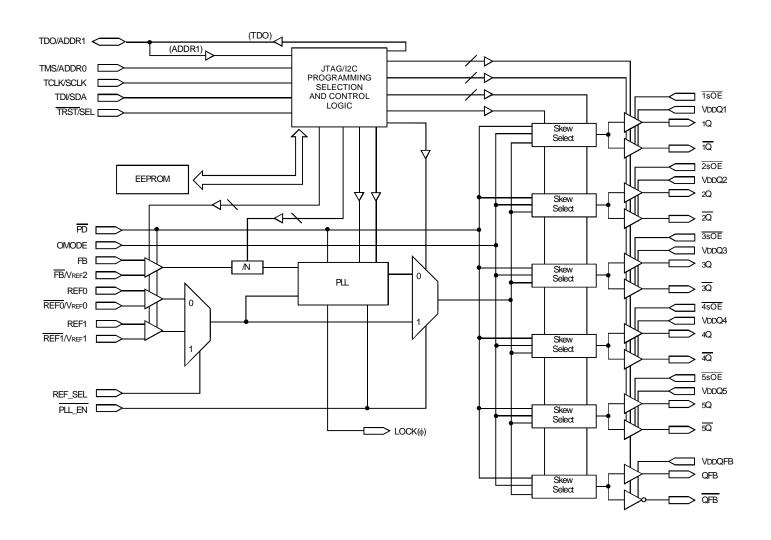

The IDT5T9891 is a 2.5V PLL differential clock driver intended for high performance computing and data-communications applications. A key feature of the programmable skew is the ability of outputs to lead or lag the REF input signal. The IDT5T9891 has six differential programmable skew outputs in six banks, including a dedicated differential feedback through the use of JTAG or  $\rm I^2C$  programming. The redundant input capability allows for a smooth change over to a secondary clock source when the primary clock source is absent.

The clock driver can be configured through the use of JTAG/ $l^2$ C programming. An internal EEPROM will allow the user to save and restore the configuration of the device.

The feedback bank allows divide-by-functionality from 1 to 12 through the use of JTAG or  $I^2C$  programming. This provides the user with frequency multiplication 1 to 12 without using divided outputs for feedback. Each output bank also allows for a divide-by functionality of 2 or 4.

The IDT5T9891 features a user-selectable, single-ended or differential input to six differential outputs. The differential clock driver also acts as a translator from a differential HSTL, eHSTL, 1.8V/2.5V LVTTL, LVEPECL, or single-ended 1.8V/2.5V LVTTL input to HSTL, eHSTL, or 1.8V/2.5V LVTTL outputs. Each output bank can be individually configured to be either HSTL, eHSTL, 2.5V LVTTL, or 1.8V LVTTL, including the feedback bank. Also, each clock input can be individually configured to accept 2.5V LVTTL, 1.8V LVTTL, or differential signals. The outputs can be synchronously enabled/disabled. The differential outputs can be synchronously enabled/disabled.

Furthermore, all the outputs can be synchronized with the positive edge of the REF clock input or the negative edge of REF.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

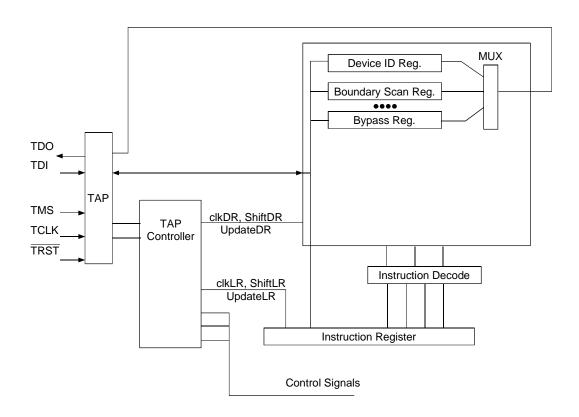

# FUNCTIONAL BLOCK DIAGRAM

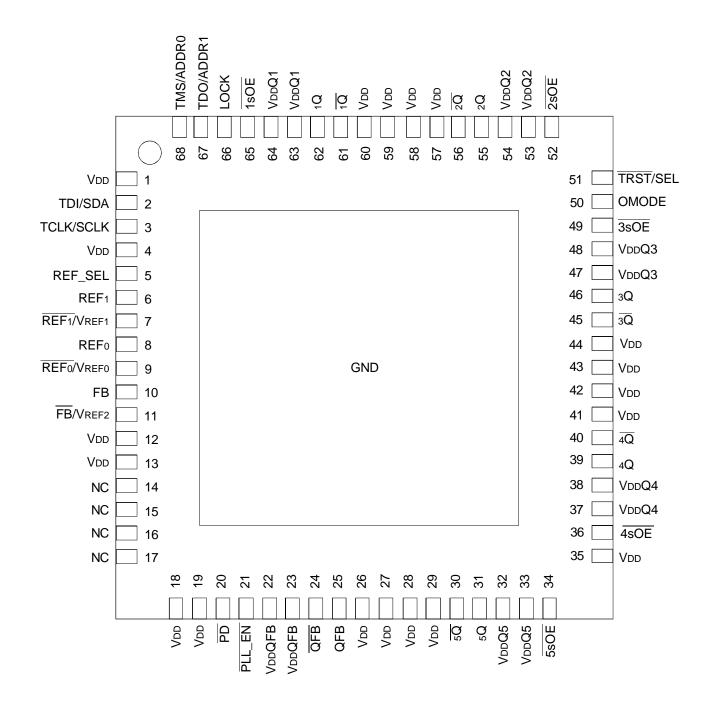

# **PIN CONFIGURATION**

VFQFPN TOP VIEW

### EEPROM PROGRAMMABLE 2.5V PROGRAMMABLE SKEW PLL DIFFERENTIAL

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol     | Description                        | Max               | Unit |

|------------|------------------------------------|-------------------|------|

| VDDQN, VDD | VDDQN, VDD Power Supply Voltage(2) |                   | ٧    |

| Vı         | Input Voltage                      | -0.5 to +3.6      | ٧    |

| Vo         | Output Voltage                     | -0.5 to VDDQ +0.5 | ٧    |

| VREF       | Reference Voltage <sup>(3)</sup>   | -0.5 to +3.6      | ٧    |

| TJ         | Junction Temperature               | 150               | °C   |

| Tstg       | Storage Temperature                | -65 to +165       | °C   |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- VDDON and VDD internally operate independently. No power sequencing requirements need to be met.

- 3. Not to exceed 3.6V.

# CAPACITANCE (TA = +25°C, f = 1MHz, VIN = 0V)

| Parameter Description |                    | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------|------|------|------|------|

| CIN                   | Input Capacitance  | 2.5  | 3    | 3.5  | pF   |

| Соит                  | Output Capacitance | _    | 6.3  | 7    | pF   |

#### NOTE:

1. Capacitance applies to all inputs except JTAG/I<sup>2</sup>C signals, SEL, ADDR0, and ADDR1.

# RECOMMENDED OPERATING RANGE

| Symbol                                                       | Description                                              | Min. | Тур.    | Max. | Unit |

|--------------------------------------------------------------|----------------------------------------------------------|------|---------|------|------|

| TA Ambient Operating Temperature                             |                                                          | -40  | +25     | +85  | °C   |

| V <sub>DD</sub> <sup>(1)</sup> Internal Power Supply Voltage |                                                          | 2.3  | 2.5     | 2.7  | V    |

|                                                              | HSTL Output Power Supply Voltage                         | 1.4  | 1.5     | 1.6  | V    |

| VDDQN <sup>(1)</sup>                                         | Extended HSTL and 1.8V LVTTL Output Power Supply Voltage | 1.65 | 1.8     | 1.95 | V    |

|                                                              | 2.5V LVTTL Output Power Supply Voltage                   |      | Vdd     |      | V    |

| VT                                                           | Termination Voltage                                      |      | VDDQN/2 |      | V    |

#### NOTE:

## **PIN DESCRIPTION**

| Symbol                 | I/O | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REF[1:0]               |     | Adjustable <sup>(1)</sup> | Clock input. REF[1:0] is the "true" side of the differential clock input. If operating in single-ended mode, REF[1:0] is the clock input.                                                                                                                                                                                                                                   |  |  |

| REF[1:0]/<br>VREF[1:0] | Ī   | Adjustable <sup>(1)</sup> | Complementary clock input. $\overline{REF}$ [1:0]/VREF[1:0] is the "complementary" side of REF[1:0] if the input is in differential mode. If operating in single-ended mode, $\overline{REF}$ [1:0]/VREF[1:0] is left floating. For single-ended operation in differential mode, $\overline{REF}$ [1:0]/VREF[1:0] should be set to the desired toggle voltage for REF[1:0]: |  |  |

|                        |     |                           | 2.5V LVTTL VREF = 1250mV (SSTL2 compatible)                                                                                                                                                                                                                                                                                                                                 |  |  |

|                        |     |                           | 1.8V LVTTL, eHSTL VREF = 900mV                                                                                                                                                                                                                                                                                                                                              |  |  |

|                        |     |                           | HSTL VREF = 750mV                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                        |     |                           | LVEPECL VREF = 1082mV                                                                                                                                                                                                                                                                                                                                                       |  |  |

| FB                     | I   | Adjustable <sup>(1)</sup> | Clock input. FB is the "true" side of the differential feedback clock input. If operating in single-ended mode, FB is the feedback clock input.                                                                                                                                                                                                                             |  |  |

| FB/VREF2               | l   | Adjustable <sup>(1)</sup> | Complementary feedback clock input. FB/VREF2 is the "complementary" side of FB if the input is in differential mode. If operating in single-ended mode, FB/VREF2 is left floating. For single-ended operation in differential mode, FB/VREF2 should be set to the desired toggle voltage for FB:                                                                            |  |  |

|                        |     |                           | 2.5VLVTTL VREF = 1250mV (SSTL2 compatible)                                                                                                                                                                                                                                                                                                                                  |  |  |

|                        |     |                           | 1.8V LVTTL, eHSTL VREF = 900mV                                                                                                                                                                                                                                                                                                                                              |  |  |

|                        |     |                           | HSTL VREF = 750mV                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                        |     |                           | LVEPECL VREF = 1082mV                                                                                                                                                                                                                                                                                                                                                       |  |  |

#### NOTE:

1. Inputs are capable of translating the following interface standards. User can select between:

Single-ended 2.5V LVTTL levels

Single-ended 1.8V LVTTL levels

10

Differential 2.5V/1.8V LVTTL levels

Differential HSTL and eHSTL levels

Differential LVEPECL levels

<sup>1.</sup> All power supplies should operate in tandem. If VDD or VDDON is at maximum, then VDDON or VDD (respectively) should be at maximum, and vice-versa.

# PIN DESCRIPTION, CONTINUED

| Symbol      | I/O | Туре                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REF_SEL     | I   | LVTTL <sup>(1)</sup>                              | Reference clock select. When LOW, selects REF0 and REF0/VREF0. When HIGH, selects REF1 and REF1/VREF1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| nsOE        | I   | LVTTL <sup>(1)</sup>                              | Synchronous output enable/disable. Each outputs's enable/disable state can be controlled either with the nsOE pin or through JTAG or I <sup>2</sup> C programming, corresponding bits 52 - 56. When the nsOE is HIGH or the corresponding Bit (52 - 56) is 1, the output will be synchronously disabled. When the nsOE is LOW and the corresponding Bit (52 - 56) is 0, the output will be enabled. (See JTAG/I <sup>2</sup> C Serial Configuration table.)                                                                                                                                                                                                                                                             |

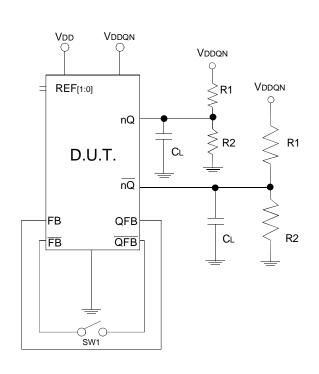

| QFB         | 0   | Adjustable <sup>(2)</sup>                         | Feedback clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| QFB         | 0   | Adjustable <sup>(2)</sup>                         | Complementaryfeedbackclockoutput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| nQ          | 0   | Adjustable <sup>(2)</sup>                         | Clock outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| nQ          | 0   | Adjustable <sup>(2)</sup>                         | Complementary clock outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PLL_EN      | I   | LVTTL <sup>(1)</sup>                              | PLL enable/disable control. The PLL's enable/disable state can be controlled either with the PLL_EN pin or through JTAG or 12C programming, corresponding Bit 57. When PLL_EN is HIGH or the corresponding Bit 57 is 1, the PLL is disabled and REF[1:0] goes to all outputs. When PLL_EN is LOW and the corresponding Bit 57 is 0, the PLL will be active.                                                                                                                                                                                                                                                                                                                                                             |

| PD          | I   | LVTTL <sup>(1)</sup>                              | Power down control. When $\overline{PD}$ is LOW, the inputs are disabled and internal switching is stopped. The OMODE pin in conjunction with the corresponding Bit 59 selects whether the outputs are gated LOW/HIGH or tri-stated. When OMODE is HIGH or Bit 59 is 1, Bit 58 determines the level at which the outputs stop. When Bit 58 is 0/1, the nQ and QFB are stopped in a HIGH/LOW state, while the $\overline{nQ}$ and $\overline{QFB}$ are stopped in a LOW/HIGH state. When OMODE is LOW and Bit 59 is 0, the outputs are tri-stated. Set $\overline{PD}$ HIGH for normal operation. (See JTAG/I <sup>2</sup> C Serial Configuration table.)                                                                |

| LOCK        | 0   | LVTTL                                             | PLL lock indication signal. HIGH indicates lock. LOW indicates that the PLL is not locked and outputs may not be synchronized to the inputs. The output will be 2.5V LVTTL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OMODE       | I   | LVTTL <sup>(1)</sup>                              | Output disable control. Used in conjunction with $\overline{nsOE}$ and $\overline{PD}$ . The outputs' disable state can be controlled either with the OMODE pin or through JTAG or I <sup>2</sup> C programming, corresponding Bit 59. When OMODE is HIGH or the corresponding Bit 59 is 1, the outputs' disable state will be gated and Bit 58 will determine the level at which the outputs stop. When Bit 58 is 0/1, the nQ and QFB are stopped in a HIGH/LOW state, while the $\overline{nQ}$ and $\overline{QFB}$ are stopped in a LOW/HIGH state. When OMODE is LOW and its corresponding bit 59 is 0, the outputs disable state will be the tri-state. (See JTAG/I <sup>2</sup> C Serial Configurations tables.) |

| TRST/SEL    | 1/1 | LVTTL/                                            | TRST- Active LOW input to asynchronously reset the JTAG boundary-scan circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     | LVTTL <sup>(4,5)</sup> 3-Level <sup>(3,4,5)</sup> | SEL - Select programming interface control for the dual-function pins. When HIGH, the dual-function pins are set for JTAG programming. When LOW, the dual-function pins are set for I <sup>2</sup> C programming and the JTAG interface is asynchronously placed in the Test Logic Reset state.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TDO/ADDR1   | O/I | LVTTL/                                            | TDO - Serial data output pin for instructions as well as test and programming data. Data is shifted in on the falling edge of TCLK. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1Bom BBitti | 0/1 |                                                   | pin is tri-stated if data is not being shifted out of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |     | 3-Level <sup>(3,4,5)</sup>                        | ADDR1 - Used to define a unique I <sup>2</sup> C address for this device. Only for I <sup>2</sup> C programming. (See JTAG/I <sup>2</sup> C Serial Interface Description.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMS/ADDR0   | I/I | LVTTL/                                            | TMS - Input pin that provides the control signal to determine the transitions of the JTAGTAP controller state machine. Transitions within the state machine occur at the rising edge of TCLK. Therefore, TMS must be set up before the rising edge of TCLK. TMS is evaluated on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |     | LVTTL <sup>(4,5)</sup>                            | ADDR0 - Used to define a unique I <sup>2</sup> C address for this device. Only for I <sup>2</sup> C programming. (See JTAG/I <sup>2</sup> C Serial Interface Description.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TCLK/SCLK   | 1/1 | LVTTL/                                            | TCLK - The clock input to the JTAG BST circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |     | LVTTL <sup>(4,5)</sup>                            | SCLK - Serial clock for I <sup>2</sup> C programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TDI/SDA     | 1/1 | LVTTL/                                            | TDI - Serial input pin for instructions as well as test and programming data. Data is shifted in on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |     |                                                   | SDA - Serial data (see JTAG/I <sup>2</sup> C Serial Description table)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDQN       |     | PWR                                               | Power supply for each pair of outputs. When using 2.5V LVTTL, 1.8V LVTTL, HSTL, or eHSTL outputs, VDDQN should be set to its corresponding outputs (see Front Block Diagram). When using 2.5V LVTTL outputs, VDDQN should be connected to VDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Vdd         |     | PWR                                               | Power supply for phase locked loop, lock output, inputs, and other internal circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GND         |     | PWR                                               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

- 1. Pins listed as LVTTL inputs can be configured to accept 1.8V or 2.5V signals through the use of the I<sup>2</sup>C/JTAG programming, bit 61. (See JTAG/I<sup>2</sup>C Serial Description.)

- 2. Outputs are user selectable to drive 2.5V, 1.8V LVTTL, eHSTL, or HSTL interface levels when used with the appropriate VDDON voltage.

- 3. 3-level inputs are static inputs and must be tied to Vpp or GND or left floating. These inputs are not hot-insertable or over voltage tolerant.

- 4. The JTAG (TDO, TMS, TCLK, and TDI) and I<sup>2</sup>C (ADDR1, ADDR0, SCLK, and SDA) signals share the same pins (dual-function pins) for which the TRST/SEL pin will select between the two programming interfaces.

- 5. JTAG and I<sup>2</sup>C pins accept 2.5V signals. The JTAG input pins (TMS, TCLK, TDI, TRST) will also accept 1.8V signals.

# JTAG/ I2C SERIAL DESCRIPTION

| Bit   | Description                                                                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 95:62 | Reserved Bits. Set bits 95:62 to '0'.                                                                                                                                                                                              |

| 61    | Input interface selection for control pins (REF_SEL, $\overline{PD}$ , $\overline{PLL}$ _EN, OMODE, $\overline{nSOE}$ ). When bit 61 is '1', the control pins are 2.5V LVTTL. When bit 61 is '0', the control pins are 1.8V LVTTL. |

| 60    | VCO frequency range. When '0', range is 50MHz-125MHz. When '1', range is 100MHz-250MHz.                                                                                                                                            |

| 59    | Output's disable state. See corresponding external pin OMODE for Pin Description table.                                                                                                                                            |

| 58    | $Positive/Negative\ edge\ control.\ When\ '0'/'1', the\ outputs\ are\ synchronized\ with\ the\ negative/positive\ edge\ of\ the\ reference\ clock.$                                                                                |

| 57    | PLL enable/disable. See corresponding external pin PLL_EN in Pin Description table. (1)                                                                                                                                            |

| 56    | Output disable/enable for 1Q[1:0] outputs. See corresponding external pin 1SOE in Pin Description table.                                                                                                                           |

| 55    | Output disable/enable for 2Q[1:0] outputs. See corresponding external pin $\overline{\text{2SOE}}$ in Pin Description table.                                                                                                       |

| 54    | Output disable/enable for 3Q[1:0] outputs. See corresponding external pin 3SOE in Pin Description table.                                                                                                                           |

| 53    | Output disable/enable for $4Q[1:0]$ outputs. See corresponding external pin $\overline{4SOE}$ in Pin Description table.                                                                                                            |

| 52    | Output disable/enable for 5Q[1:0] outputs. See corresponding external pin 5SOE in Pin Description table.                                                                                                                           |

| 51    | FB Divide-by-N selection                                                                                                                                                                                                           |

| 50    | FB Divide-by-N selection                                                                                                                                                                                                           |

| 49    | FB Divide-by-N selection                                                                                                                                                                                                           |

| 48    | FB Divide-by-N selection                                                                                                                                                                                                           |

| 47    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 1                                                                                                                                                |

| 46    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 1                                                                                                                                                |

| 45    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 2                                                                                                                                                |

| 44    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 2                                                                                                                                                |

| 43    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 3                                                                                                                                                |

| 42    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 3                                                                                                                                                |

| 41    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 4                                                                                                                                                |

| 40    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 4                                                                                                                                                |

| 39    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 5                                                                                                                                                |

| 38    | Output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on bank 5                                                                                                                                                |

| 37    | FB output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on FB bank                                                                                                                                            |

| 36    | FB output drive strength selection for 2.5V LVTTL, 1.8V LVTTL, or HSTL/eHSTL on FB bank                                                                                                                                            |

| 35    | REF0 Input interface selection for 2.5V LVTTL, 1.8V LVTTL, or Differential                                                                                                                                                         |

| 34    | REF0 Input interface selection for 2.5V LVTTL, 1.8V LVTTL, or Differential                                                                                                                                                         |

| 33    | REF1 input interface selection for 2.5V LVTTL, 1.8V LVTTL, or Differential                                                                                                                                                         |

| 32    | REF1 input interface selection for 2.5V LVTTL, 1.8V LVTTL, or Differential                                                                                                                                                         |

| 31    | FB input interface selection for 2.5V LVTTL, 1.8V LVTTL, or Differential                                                                                                                                                           |

| 30    | FB input interface selection for 2.5V LVTTL, 1.8V LVTTL, or Differential                                                                                                                                                           |

| 29    | Skew or frequency selection for bank 1                                                                                                                                                                                             |

| 28    | Skew or frequency selection for bank 1                                                                                                                                                                                             |

| 27    | Skew or frequency selection for bank 1                                                                                                                                                                                             |

| 26    | Skew or frequency selection for bank 1                                                                                                                                                                                             |

| 25    | Skew or frequency selection for bank 1                                                                                                                                                                                             |

| 24    | Skew or frequency selection for bank 2                                                                                                                                                                                             |

| 23    | Skew or frequency selection for bank 2                                                                                                                                                                                             |

| 22    | Skew or frequency selection for bank 2                                                                                                                                                                                             |

#### NOTE

<sup>1.</sup> Only for EEPROM operation; bit 57 must be set to 0 to enable the PLL for proper EEPROM operation. The EEPROM access times are based on the VCO frequency of the PLL (refer to the EEPROM Operation section).

# JTAG/ I<sup>2</sup>C SERIAL DESCRIPTION, CONT.

| Bit | Description                             |

|-----|-----------------------------------------|

| 21  | Skew or frequency selection for bank 2  |

| 20  | Skew or frequency selection for bank 2  |

| 19  | Skew or frequency selection for bank 3  |

| 18  | Skew or frequency selection for bank 3  |

| 17  | Skew or frequency selection for bank 3  |

| 16  | Skew or frequency selection for bank 3  |

| 15  | Skew or frequency selection for bank 3  |

| 14  | Skew or frequency selection for bank 4  |

| 13  | Skew or frequency selection for bank 4  |

| 12  | Skew or frequency selection for bank 4  |

| 11  | Skew or frequency selection for bank 4  |

| 10  | Skew or frequency selection for bank 4  |

| 9   | Skew or frequency selection for bank 5  |

| 8   | Skew or frequency selection for bank 5  |

| 7   | Skew or frequency selection for bank 5  |

| 6   | Skew or frequency selection for bank 5  |

| 5   | Skew or frequency selection for bank 5  |

| 4   | Skew or frequency selection for FB bank |

| 3   | Skew or frequency selection for FB bank |

| 2   | Skew or frequency selection for FB bank |

| 1   | Skew or frequency selection for FB bank |

| 0   | Skew or frequency selection for FB bank |

# JTAG/ I<sup>2</sup>C SERIAL CONFIGURATIONS: OUTPUT ENABLE/DISABLE

| Bit 59 (OMODE) | Bit 56-52 (nsOE) | Output               |

|----------------|------------------|----------------------|

| X (X)          | 0 and (L)        | Normal Operation     |

| 0 and (L)      | 1 or (H)         | Tri-Sate             |

| 1 or (H)       | 1 or (H)         | Gated <sup>(1)</sup> |

#### NOTE

1. OMODE and its corresponding Bit 59 selects whether the outputs are gated LOW/ HIGH or tri-stated. When OMODE is HIGH or the corresponding Bit 59 is 1, the outputs' disable state will be gated. Bit 58 determines the level at which the outputs stop. When Bit 58 is 0/ 1, the nQ and QFB are stopped in a HIGH/LOW state, while the  $\overline{\text{nQ}}$  and  $\overline{\text{QFB}}$  are stopped in a LOW/HIGH state. When OMODE is LOW and its corresponding Bit 59 is 0, the outputs' disable state will be the tri-state.

# JTAG/ I<sup>2</sup>C SERIAL CONFIGURATIONS: CLOCK INPUT INTERFACE SELEC-TION<sup>(1)</sup>

| Bit 31, 33, 35 | Bit 30, 32, 34 | Interface                   |

|----------------|----------------|-----------------------------|

| 0              | 0              | Differential <sup>(2)</sup> |

| 0              | 1              | 2.5V LVTTL                  |

| 1              | 1              | 1.8V LVTTL                  |

#### NOTES:

- 1. All other states that are undefined in the table will be reserved.

- 2. Differential input interface for HSTL/eHSTL, LVEPECL (2.5V), and 2.5V/1.8V LVTTL.

# JTAG/ I<sup>2</sup>C SERIAL CONFIGURATIONS: POWERDOWN

| PD Bit 59 (OMODE) |           | Output               |

|-------------------|-----------|----------------------|

| Н                 | X (X)     | Normal Operation     |

| L                 | 0 and (L) | Tri-Sate             |

| L                 | 1 or (H)  | Gated <sup>(1)</sup> |

#### NOTE:

1. OMODE and its corresponding Bit 59 selects whether the outputs are gated LOW/ HIGH or tri-stated. When OMODE is HIGH or the corresponding Bit 59 is 1, the outputs' disable state will be gated. Bit 58 determines the level at which the outputs stop. When Bit 58 is 0/1, the nQ and QFB are stopped in a HIGH/LOW state, while the  $\overline{nQ}$  and  $\overline{QFB}$  are stopped in a LOW/HIGH state. When OMODE is LOW and its corresponding Bit 59 is 0, the outputs' disable state will be the tri-state.

# JTAG/ I<sup>2</sup>C SERIAL CONFIGURATIONS: OUTPUT DRIVE STRENGTH SELECTION<sup>(1)</sup>

| Bit 37, 39, 41, | Bit 36, 38, 40, |            |

|-----------------|-----------------|------------|

| 43, 45, 47      | 42, 44, 46      | Interface  |

| 0               | 0               | 2.5V LVTTL |

| 0               | 1               | 1.8V LVTTL |

| 1               | 0               | HSTL/eHSTL |

#### NOTE:

1. All other states that are undefined in the table will be reserved.

# JTAG/ I2C SERIAL CONFIGURATIONS: SKEW OR FREQUENCY SELECT(1)

| Bit 4, 9, 14,<br>19, 24, 29 | Bit 3, 8, 13,<br>18, 23, 28 | Bit 2, 7, 12,<br>17, 22, 27 | Bit 1, 6, 11,<br>16, 21, 26 | Bit 0, 5, 10,<br>15, 20, 25 | Output Skew |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------|

| 0                           | 0                           | 0                           | 0                           | 1                           | +7tu        |

| 0                           | 0                           | 0                           | 1                           | 0                           | +6tu        |

| 0                           | 0                           | 0                           | 1                           | 1                           | +5tu        |

| 0                           | 0                           | 1                           | 0                           | 0                           | +4tu        |

| 0                           | 0                           | 1                           | 0                           | 1                           | +3tu        |

| 0                           | 0                           | 1                           | 1                           | 0                           | +2tu        |

| 0                           | 0                           | 1                           | 1                           | 1                           | +1tu        |

| 0                           | 0                           | 0                           | 0                           | 0                           | Zero Skew   |

| 0                           | 1                           | 0                           | 0                           | 1                           | -1tu        |

| 0                           | 1                           | 0                           | 1                           | 0                           | -2tu        |

| 0                           | 1                           | 0                           | 1                           | 1                           | -3tu        |

| 0                           | 1                           | 1                           | 0                           | 0                           | -4tu        |

| 0                           | 1                           | 1                           | 0                           | 1                           | -5tu        |

| 0                           | 1                           | 1                           | 1                           | 0                           | -6tu        |

| 0                           | 1                           | 1                           | 1                           | 1                           | -7tu        |

| 1                           | 0                           | 0                           | 0                           | 0                           | Inverted    |

| 1                           | 0                           | 0                           | 0                           | 1                           | Divide-by-2 |

| 1                           | 0                           | 0                           | 1                           | 0                           | Divide-by-4 |

#### NOTE:

# JTAG/ I<sup>2</sup>C SERIAL CONFIGURATIONS: FB DIVIDE-BY-N<sup>(1)</sup>

| Bit 51 | Bit 50 | Bit 49 | Bit 48 | Divide-by-N | Permitted Output Divide-by-N connected to FB and FB/VREF2 (2) |

|--------|--------|--------|--------|-------------|---------------------------------------------------------------|

| 0      | 0      | 0      | 0      | 1           | 1, 2, 4                                                       |

| 0      | 0      | 0      | 1      | 2           | 1, 2                                                          |

| 0      | 0      | 1      | 0      | 3           | 1                                                             |

| 0      | 0      | 1      | 1      | 4           | 1, 2                                                          |

| 0      | 1      | 0      | 0      | 5           | 1, 2                                                          |

| 0      | 1      | 0      | 1      | 6           | 1, 2                                                          |

| 0      | 1      | 1      | 0      | 8           | 1                                                             |

| 0      | 1      | 1      | 1      | 10          | 1                                                             |

| 1      | 0      | 0      | 0      | 12          | 1                                                             |

#### NOTES:

- 1. All other states that are undefined in the table will be reserved.

- 2. Permissible output division ratios connected to FB and FB/VREF2. The frequencies of the REF[1:0] and REF [1:0]/VREF[1:0] inputs will be Fvco/N when the parts are configured for frequency multiplication by using an undivided output for FB and FB/VREF2 and setting N (N = 1-6, 8, 10, 12).

# JTAG/ I<sup>2</sup>C SERIAL CONFIGURATIONS: VCOFREQUENCY SELECT

| Bit 60 | Min.   | Max.   |

|--------|--------|--------|

| 0      | 50Mhz  | 125MHz |

| 1      | 100MHz | 250Mhz |

<sup>1.</sup> All other states that are undefined in the table will result in zero skew.

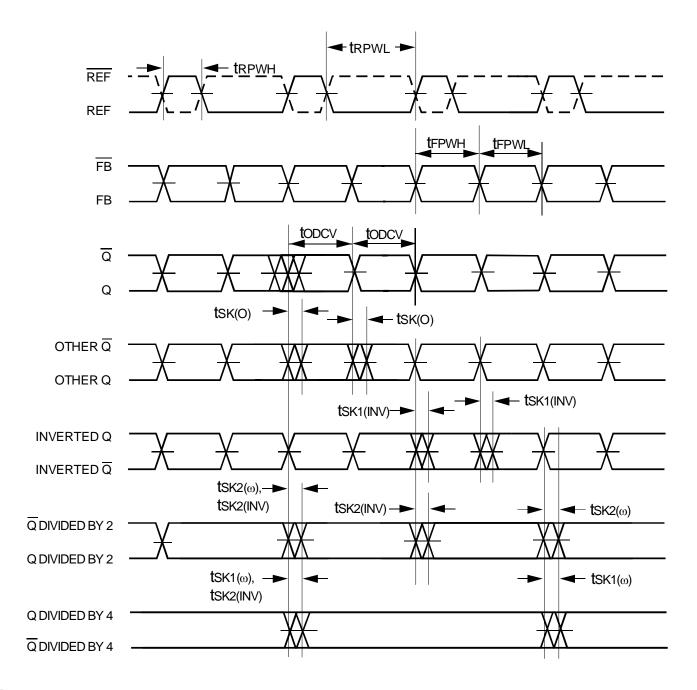

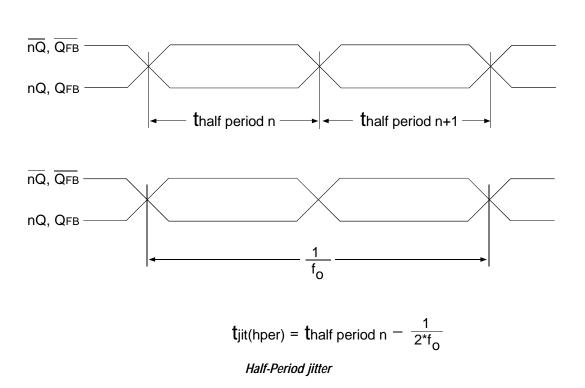

## **PROGRAMMABLE SKEW**

Output skew with respect to the REF[1:0] and REF[1:0]/VREF[1:0] input is adjustable to compensate for PCB trace delays, backplane propagation delays or to accommodate requirements for special timing relationships between clocked components. Skew is selectable as a multiple of a time unit (tu) which ranges from 250ps to 1.25ns (see Programmable Skew Range and Resolution Table). There are 18 skew/divide configurations available for each output pair. These configurations are chosen through JTAG/I<sup>2</sup>C programming.

# PROGRAMMABLE SKEW RANGE AND RESOLUTION TABLE

|                                             | Bit 60 = 0    | Bit 60 = 1    | Comments        |

|---------------------------------------------|---------------|---------------|-----------------|

| Timing Unit Calculation (tu)                | 1/(16 х Fnом) | 1/(16 x Fnom) |                 |

| VCO Frequency Range (FNOM) <sup>(1,2)</sup> | 50 to 125MHz  | 100 to 250MHz |                 |

| Skew Adjustment Range <sup>(3)</sup>        |               |               |                 |

| Max Adjustment:                             | ±8.75ns       | ±4.375ns      | ns              |

|                                             | ±157.5°       | ±157.5°       | Phase Degrees   |

|                                             | ±43.75%       | ±43.75%       | % of Cycle Time |

| Example 1, FNOM = 50MHz                     | tu = 1.25ns   | _             |                 |

| Example 2, FNOM = 75MHz                     | tu = 0.833ns  | _             |                 |

| Example 3, FNOM = 100MHz                    | tu = 0.625ns  | tu=0.625ns    |                 |

| Example 4, FNOM = 150MHz                    | _             | tu = 0.417ns  |                 |

| Example 5, FNOM = 200MHz                    | _             | tu = 0.313ns  |                 |

| Example 6, FNOM = 250MHz                    | _             | tu = 0.25ns   |                 |

#### NOTES:

- 1. The device may be operated outside recommended frequency ranges without damage, but functional operation is not guaranteed.

- 2. The VCO frequency always appears at nQ and  $\overline{\text{NQ}}$  outputs when they are operated in their undivided modes. The frequency appearing at the REF[1:0] and  $\overline{\text{REF}}$ [1:0]/VREF[1:0] and FB and  $\overline{\text{FB/VREF2}}$  inputs will be FNOM when the QFB and  $\overline{\text{QFB}}$  are undivided and FB divide-by-1. The frequency of the REF[1:0] and  $\overline{\text{REF}}$ [1:0]/VREF[1:0] and FB and  $\overline{\text{FB/VREF2}}$  inputs will be FNOM /2 or FNOM /4 when the part is configured for frequency multiplication by using a divided QFB and  $\overline{\text{QFB}}$  and setting FB divide-by-1. Using the FB divide-by-N configuration inputs allows a different method for frequency multiplication (see JTAG/I<sup>2</sup>C Serial Configurations: FB Divide-by-N).

- 3. Skew adjustment range assumes that a zero skew output is used for feedback. If a skewed QFB and QFB output is used for feedback, then adjustment range will be greater. For example if a 4tu skewed output is used for feedback, all other outputs will be skewed –4tu in addition to whatever skew value is programmed for those outputs. 'Max adjustment' range applies to all output pairs where ±7tu skew adjustment is possible and at the lowest FNOM value.

## **EXTERNAL DIFFERENTIAL FEEDBACK**

By providing a dedicated external differential feedback, the IDT5T9891 gives users flexibility with regard to divide selection. The FB and  $\overline{\text{FB}}/\text{VREF2}$  signals are compared with the input REF[1:0] and  $\overline{\text{REF}}$ [1:0]/VREF[1:0] signals at the phase detector in order to drive the VCO. Phase differences cause the VCO of the PLL to adjust upwards or downwards accordingly.

An internal loop filter moderates the response of the VCO to the phase detector. The loop filter transfer function has been chosen to provide minimal jitter (or frequency variation) while still providing accurate responses to input frequency changes.

### MASTER RESET FUNCTIONALITY

The IDT5T9891 performs a reset of the internal output divide circuitry when all five output banks are disabled by toggling the  $\overline{\mathsf{nSOE}}$  pins HIGH. When one or more banks of outputs are enabled by toggling the  $\overline{\mathsf{nSOE}}$  LOW (if the corresponding  $\overline{\mathsf{nSOE}}$  programming bits are also set LOW), the divide circuitry starts again from a known state. In the case that the FB output is selected for divide-by-2 or divide-by-4, the FB output will stop toggling while all five  $\overline{\mathsf{nSOE}}$  pins and bits are LOW, and loss of lock will occur.

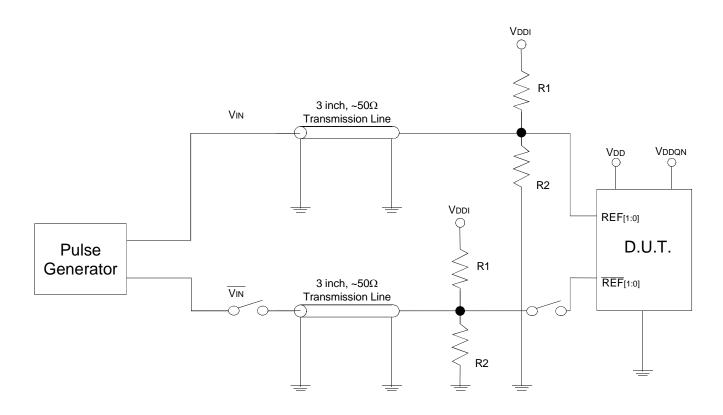

# INPUT/OUTPUT SELECTION<sup>(1)</sup>

| input          | Output <sup>(2)</sup> |

|----------------|-----------------------|

| 2.5V LVTTL SE  | 2.5V LVTTL,           |

| 1.8V LVTTL SE  | 1.8V LVTTL,           |

| 2.5V LVTTL DSE | HSTL,                 |

| 1.8V LVTTL DSE | eHSTL                 |

| LVEPECL DSE    |                       |

| eHSTL DSE      |                       |

| HSTL DSE       |                       |

| 2.5V LVTTL DIF |                       |

| 1.8V LVTTL DIF |                       |

| LVEPECL DIF    |                       |

| eHSTL DIF      |                       |

| HSTL DIF       |                       |

| NOTEC          |                       |

Output(2)

- 1. The INPUT/OUTPUT SELECTION Table describes the total possible combinations of input and output interfaces. Single-Ended (SE) inputs in a single-ended mode require the REF[1:0] / VREF[1:0] and FB/VREF2 pins to be left floating. Differential Single-Ended (DSE) is for single-ended operation in differential mode, requiring VREF[1:0] and VREF2. Differential (DIF) inputs are used only in differential mode.

- 2. For each output bank.

## I<sup>2</sup>C SERIAL INTERFACE CONTROL

The  $I^2C$  interface permits the configuration of the IDT5T9891. The IDT5T9891 is a read/write slave device meeting Philips  $I^2C$  bus specifications. The  $I^2C$  bus is controlled by a master device that generates the serial clock SCLK, controls bus access, and generates the START and STOP conditions while the device works as a slave. Both master and slave can operate as a transmitter and receiver but the master device determines which mode is activated.

#### **BUS CONDITIONS**

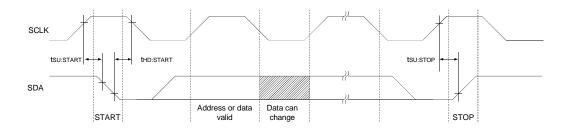

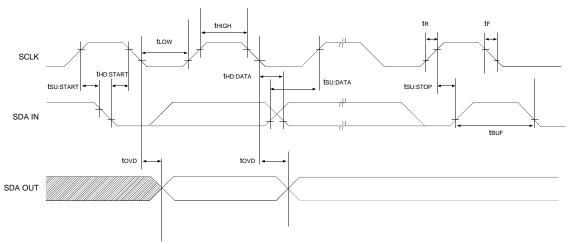

Data transfer on the bus can only be initiated when the bus is not busy. During data transfer, the data line (SDA) must remain stable whenever the clock line (SCLK) is high. Changes in the data line while the clock line is high will be interpreted by the device as a START or STOP condition. The following bus conditions are defined by the  $I^2C$  bus protocol and are illustrated in figure 1.

#### **NOT BUSY**

Both the data (SDA) and clock (SCLK) lines remain high to indicate the bus is not busy.

#### START DATA TRANSFER

A high to low transition of the SDA line while the SCLK input is high indicates a START condition. All commands to the device must be preceded by a START condition.

#### **STOP DATA TRANSFER**

A low to high transition of the SDA line while SCLK is held high indicates a STOP condition. All commands to the device must be followed by a STOP condition.

#### **DATA VALID**

The state of the SDA line represents valid data if the SDA line is stable for the duration of the high period of the SCLK line after a START condition occurs. The data on the SDA line must be changed only during the low period of the SCLK signal. There is one clock pulse per data bit. Each data transfer is initiated by a START condition and terminated with a STOP condition.

#### **ACKNOWLEDGE**

When addressed, the receiving device is required to generate an Acknowledge after each byte is received. The master device must generate an extra clock pulse to coincide with the Acknowledge bit. The acknowledging device must pull the SDA line low during the high period of the master acknowledge clock pulse. Setup and hold times must be taken into account.

#### I<sup>2</sup>C BUS OPERATION

The IDT5T9891  $\rm l^2C$  interface supports Standard-Mode (100kHz) and Fast-Mode (400kHz) data transfer rates. Data is transferred in bytes in sequential order from the lowest to highest byte. After generating a START condition, the bus master broadcasts a 7-bit slave address followed by a read/write bit.

## I<sup>2</sup>C ADDRESS

| A7 | A6 | <b>A</b> 5 | A4 | A3 | A2 | A1 |

|----|----|------------|----|----|----|----|

| 1  | 1  | 0          | 1  | Χ  | Χ  | Χ  |

Address A0 is the read/write bit and is set to '0' for writes and '1' for reads. The ADDR0 and ADDR1 tri-level pins allow the last three bits of the 7-bit address to be defined by the user.

| ADDR1 | ADDR0 | A3 | A2 | A1 |

|-------|-------|----|----|----|

| LOW   | LOW   | 0  | 0  | 0  |

| LOW   | MID   | 0  | 0  | 1  |

| LOW   | HIGH  | 0  | 1  | 0  |

| MID   | LOW   | 0  | 1  | 1  |

| MID   | MID   | 1  | 0  | 0  |

| MID   | HIGH  | 1  | 0  | 1  |

| HIGH  | LOW   | 1  | 1  | 0  |

| HIGH  | MID   | 1  | 1  | 1  |

| HIGH  | HIGH  | 1  | 1  | 0  |

#### WRITE OPERATION

#### (see FC Interface Definition for ProgWrite)

To initiate a write operation (ProgWrite), the read/write bit is set to '0'. During the write operation, the first two bytes transferred must be the Device Address followed by the Command Code. The internal programming registers of the device ignore these first two bytes. The subsequent bytes are the Data Bytes, which total twelve. All twelve Data Bytes must be written into the device during the write operation in order for the internal programming registers to be updated. If a STOP condition is generated before the 12th Data Byte, the internal programming registers will remain unchanged to prevent an invalid PLL configuration. An Acknowledge by the device between each byte must occur before the next byte is sent. After the transfer of the 12th Data Byte, an Acknowledge signal will be sent to the bus master after which it will generate a STOP condition. Once the STOP condition has occurred, the internal programming registers of the device will be updated.

#### **READ OPERATION**

#### (see FC Interface Definition for ProgRead)

To initiate a read operation (ProgRead), the read/write bit is set to '1'. During the read operation, there will be a total of fourteen data bytes returned following an Acknowledge of the device address. The first two data bytes are the ID Byte and a Reserved Byte, in that order. The subsequent bytes are the same twelve Data Bytes that were written during the write operation. The read back can be terminated at any time by issuing a STOP condition.

### I<sup>2</sup>C ID BYTE

| ID7 | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |

#### **EEPROMOPERATION**

#### (see FC Interface Definition for the EEPROM instructions)

The IDT5T9891 can also store its configuration in internal EEPROM. The contents of the device's internal programming registers can be saved to the EEPROM by issuing a save instruction (ProgSave) and can be loaded back to the internal programming registers by issuing a restore instruction (ProgRestore). To initiate a save or restore, only two bytes are transferred. The Device Address is issued with the read/write bit set to '0' followed by the appropriate Command Code. The save or restore instruction executes after the STOP condition is received, during which time the IDT5T9891 will not generate Acknowledge bits. The device is ready to accept a new programming instruction once it Acknowledges its 7-bit address. The time it takes for the save and restore instructions to complete depends on the PLL oscillator frequency, Fvco. The restore time, Trestore, and the save time, Tsave, can be calculated as follows:

Trestore =  $1.23X10^6/Fvco$  (mS) Tsave =  $3.09X10^6/Fvco + 52$  (mS)

In order for the save and restore instructions to function properly, the IDT5T9891 must not be in power-down mode ( $\overline{PD}$  must be HIGH), and the PLL must be enabled ( $\overline{PLL}$  EN must be LOW and Bit 57 = 0).

On power-up of the IDT5T9891, an automatic restore is performed to load the EEPROM contents into the internal programming registers. The auto-restore will not function properly if the device is in power-down mode ( $\overline{PD}$  must be HIGH). The device's auto-restore feature will function regardless of the state of the  $\overline{PLL}$  $\underline{EN}$  pin or Bit 57. The IDT5T9891 will be ready to accept a programming instruction once it acknowledges its 7-bit I $^2$ C address. The time it takes for the device to complete the auto-restore is approximately 3ms.

#### **PROGRAMMING NOTES**

Once the IDT5T9891 has been programmed either with a ProgWrite or ProgRestore instruction, the device will attempt to achieve phase lock using the new PLL configuration. If there is a valid REF and FB input clock connected to the device and it does not achieve lock, the user should issue a ProgRead instruction to confirm that the PLL configuration data is valid.

On power-up and before the automatic ProgRestore instruction has completed, the internal programming registers will contain the value of '0' for all bits 95:0. The PLL will remain at the minimum frequency and will not achieve phase lock until after the automatic restore is completed. If the outputs are enabled by the  $\overline{\text{nSOE}}$  pins, the outputs will toggle at the minimum frequency. If the outputs are disabled by the  $\overline{\text{nSOE}}$  pins and the OMODE pin is set HIGH, the nQ and QFB are stopped HIGH, while  $\overline{\text{nQ}}$  and  $\overline{\text{QFB}}$  are stopped LOW.

Figure 1: PC Timing Data

# I<sup>2</sup>C INTERFACE DEFINITION

|           |   | Device A | ddress | W     |   | Command Code | е      |   | Data                       |   |   |

|-----------|---|----------|--------|-------|---|--------------|--------|---|----------------------------|---|---|

| ProgWrite | S | 7'b110   | 1xxx   | 0     | Α | 8'bxxxxxx00  |        | Α | Data Byte 1 (Bits 95 - 88) | Α |   |

|           |   | М        | L      |       |   | M            | L      |   | Data Byte 2                | Α |   |

|           |   | S<br>B   | S<br>B |       |   | S<br>B       | S<br>B |   | Data Byte 3                | Α |   |

|           |   | J        |        |       |   | 5            |        |   | Data Byte 4                | Α |   |

|           |   |          |        |       |   |              |        |   | Data Byte 5                | Α |   |

|           |   |          |        |       |   |              |        |   | Data Byte 6                | Α |   |

|           |   | Part #   | ID E   | Byte: |   |              |        |   | Data Byte 7                | Α |   |

|           |   | 5T9891   | 0000   |       |   |              |        |   | Data Byte 8                | Α |   |

|           |   |          |        |       |   |              |        |   | Data Byte 9                | Α |   |

|           |   |          |        |       |   |              |        |   | Data Byte 10               | Α |   |

|           |   |          |        |       |   |              |        |   | Data Byte 11               | Α |   |

|           |   |          |        |       |   |              |        |   | Data Byte 12 (Bits 7 - 0)  | Α | Р |

|          |   | Device Address | R |   | ID Byte                    |   |   |

|----------|---|----------------|---|---|----------------------------|---|---|

| ProgRead | S | 7'b1101xxx     | 1 | Α | 8'b00000111                | Α |   |

|          |   |                |   |   | Reserved Byte              | Α |   |

|          |   |                |   |   | Data Byte 1 (Bits 95 - 88) | Α |   |

|          |   |                |   |   | Data Byte 2                | Α |   |

|          |   |                |   |   | Data Byte 3                | Α |   |

|          |   |                |   |   | Data Byte 4                | Α |   |

|          |   |                |   |   | Data Byte 5                | Α |   |

|          |   |                |   |   | Data Byte 6                | Α |   |

|          |   |                |   |   | Data Byte 7                | Α |   |

|          |   |                |   |   | Data Byte 8                | Α |   |

|          |   |                |   |   | Data Byte 9                | Α |   |

|          |   |                |   |   | Data Byte 10               | Α |   |

|          |   |                |   |   | Data Byte 11               | Α |   |

|          |   |                |   |   | Data Byte 12 (Bits 7 - 0)  | Α | Р |

| ProgSave    | S | Device Address 7'b1101xxx | W | Α | Command Code<br>8'bxxxxxx01 | Α | Р |

|-------------|---|---------------------------|---|---|-----------------------------|---|---|

| J           |   |                           |   |   | <u> </u>                    |   |   |

|             |   | Device Address            | W |   | Command Code                |   |   |

| ProgRestore | S | 7'b1101xxx                | 0 | Α | 8'bxxxxxx10                 | Α | Р |

# I<sup>2</sup>C BUS DC CHARACTERISTICS

| Symbol | Parameter             | Conditions | Min        | Тур | Max       | Unit |

|--------|-----------------------|------------|------------|-----|-----------|------|

| VIH    | Input HIGH Level      |            | 0.7 * Vdd  |     |           | V    |

| VIL    | Input LOW Level       |            |            |     | 0.3 * VDD | V    |

| VHYS   | Hysteresis of Inputs  |            | 0.05 * Vdd |     |           | V    |

| lin    | Input Leakage Current |            |            |     | ±1.0      | μΑ   |

| Vol    | Output LOW Voltage    | IoL = 3 mA |            |     | 0.4       | V    |

# I<sup>2</sup>C BUS AC CHARACTERISTICS FOR STANDARD MODE

| Symbol    | Parameter                                  | Min | Тур | Max  | Unit |

|-----------|--------------------------------------------|-----|-----|------|------|

| Fsclk     | Serial Clock Frequency (SCLK)              | 0   |     | 100  | KHz  |

| tBUF      | Bus free time between STOP and START       | 4.7 |     |      | μS   |

| tsu:start | Setup Time, START                          | 4.7 |     |      | μS   |

| thd:start | Hold Time, START                           | 4   |     |      | μS   |

| tsu:data  | Setup Time, data input (SDA)               | 250 |     |      | ns   |

| thd:data  | Hold Time, data input (SDA) <sup>(1)</sup> | 0   |     |      | μS   |

| tovo      | Output data valid from clock               |     |     | 3.45 | μS   |

| Св        | Capacitive Load for Each Bus Line          |     |     | 400  | pF   |

| tr        | Rise Time, data and clock (SDA, SCLK)      |     |     | 1000 | ns   |

| tF        | Fall Time, data and clock (SDA, SCLK)      |     |     | 300  | ns   |

| thigh     | HIGH Time, clock (SCLK)                    | 4   |     |      | μS   |

| tLow      | LOW Time, clock (SCLK)                     | 4.7 |     |      | μS   |

| tsu:stop  | Setup Time, STOP                           | 4   |     |      | μS   |

#### NOTE:

# I<sup>2</sup>C BUS AC CHARACTERISTICS FOR FAST MODE

| Symbol       | Parameter                                  | Min                       | Тур | Max | Unit |

|--------------|--------------------------------------------|---------------------------|-----|-----|------|

| Fsclk        | Serial Clock Frequency (SCLK)              | 0                         |     | 400 | KHz  |

| <b>t</b> BUF | Bus free time between STOP and START       | 1.3                       |     |     | μS   |

| tsu:start    | Setup Time, START                          | 0.6                       |     |     | μS   |

| thd:start    | Hold Time, START                           | 0.6                       |     |     | μS   |

| tsu:data     | Setup Time, data input (SDA)               | 100                       |     |     | ns   |

| thd:data     | Hold Time, data input (SDA) <sup>(1)</sup> | 0                         |     |     | μS   |

| tovd         | Output data valid from clock               |                           |     | 0.9 | μs   |

| Св           | Capacitive Load for Each Bus Line          |                           |     | 400 | pF   |

| tr           | Rise Time, data and clock (SDA, SCLK)      | 20 + 0.1 * C <sub>B</sub> |     | 300 | ns   |

| tF           | Fall Time, data and clock (SDA, SCLK)      | 20 + 0.1 * C <sub>B</sub> |     | 300 | ns   |

| thigh        | HIGH Time, clock (SCLK)                    | 0.6                       |     |     | μS   |

| tLOW         | LOW Time, clock (SCLK)                     | 1.3                       |     |     | μS   |

| tsu:stop     | Setup Time, STOP                           | 0.6                       |     |     | μS   |

<sup>1.</sup> A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIHMIN of the SCLK signal) to bridge the undefined region of the falling edge of SCLK.

<sup>1.</sup> A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIHMIN of the SCLK signal) to bridge the undefined region of the falling edge of SCLK.

## JTAG INTERFACE

Five additional pins (TDI, TDO, TMS, TCLK and TRST) are provided to support the JTAG boundary scan interface. The IDT5T9891 incorporates the necessary tap controller and modified pad cells to implement the JTAG facility.

Note that IDT provides appropriate Boundary Scan Description Language program files for these devices.

The Standard JTAG interface consists of four basic elements:

- Test Access Port (TAP)

- TAP controller

- Instruction Register (IR)

- Data Register Port (DR)

The following sections provide a brief description of each element. For a complete description refer to the IEEE Standard Test Access Port Specification (IEEE Std. 1149.1-1990).

**Boundary Scan Architecture**

#### TEST ACCESS PORT (TAP)

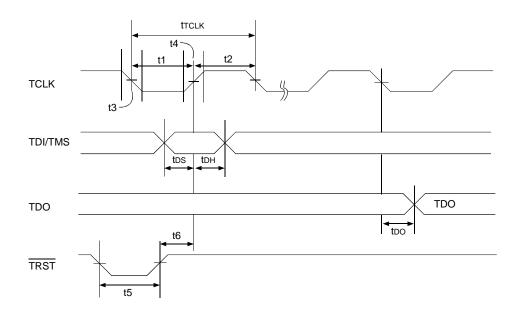

The Tap interface is a general-purpose port that provides access to the internal of the processor. It consists of four input ports (TCLK, TMS, TDI,  $\overline{\text{TRST}}$ ) and one output port (TDO).

#### THE TAP CONTROLLER

The Tap controller is a synchronous finite state machine that responds to TMS and TCLK signals to generate clock and control signals to the Instruction and Data Registers for capture and update of data.

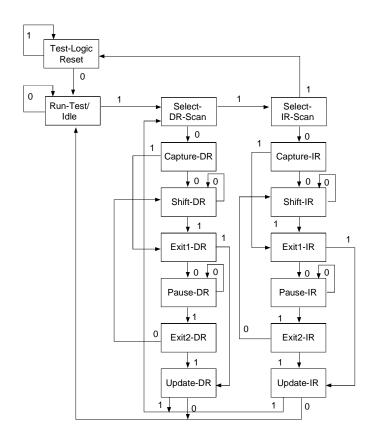

TAP Controller State Diagram

#### NOTES

- 1. Five consecutive TCLK cycles with TMS = 1 will reset the TAP.

- 2. TAP controller must be reset before normal PLL operations can begin.

Refer to the IEEE Standard Test Access Port Specification (IEEE Std.1149.1) for the full state diagram

All state transitions within the TAP controller occur at the rising edge of the TCLK pulse. The TMS signal level (0 or 1) determines the state progression that occurs on each TCLK rising edge. The TAP controller takes precedence over the PLL and must be reset after power up of the device. See TRST description for more details on TAP controller reset.

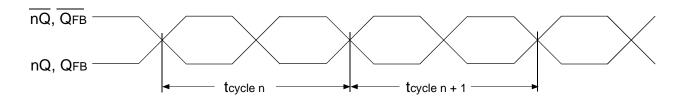

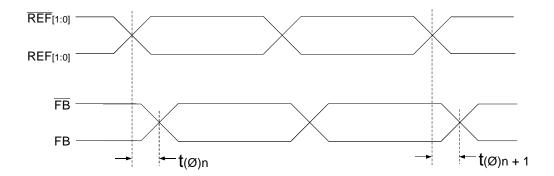

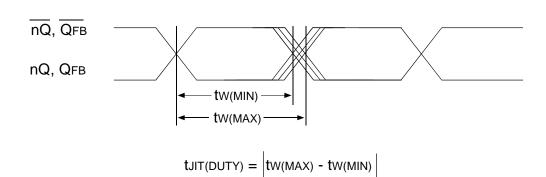

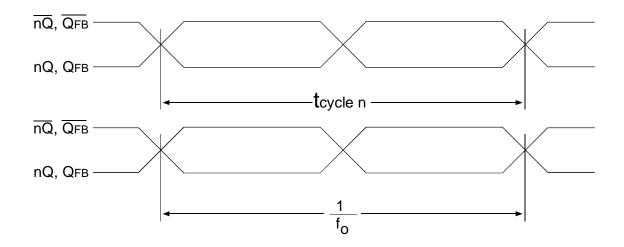

**Test-Logic-Reset** All test logic is disabled in this controller state enabling the normal operation of the IC. The TAP controller state machine is designed in such a way that, no matter what the initial state of the controller is, the Test-Logic-Reset state can be entered by holding TMS at high and pulsing TCLK five times. This is the reason why the Test Reset  $(\overline{TRST})$  pin is optional.