# v.DataSheet4U.cor

### **Preliminary Information**

This document contains information on a product under development.

The parametric information are target values and are subject to change.

# Bt694

### **Distinguishing Features**

- 750 mA Output Drive

- 100 MHz Capability

- · Three-statable

- 8 V Output Swings

- -3 V to +8 V Programmable Range

- · Adjustable Slew Rate

- · On-Chip Thermal Shutdown

- Adjustable Maximum Output Current

- Digital Inputs ECL, TTL, or CMOS Compatible

- · 2.5 ns Propagation Delay

- Rout < 1 Ω</li>

# **Applications**

- In-Circuit Board ATE

- Combinational Board ATE

- Functional Board ATE

- Burn-In ATE

- Capacitive Driver

- · High-current Driver

### **Related Products**

Bt684

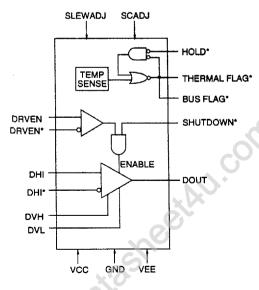

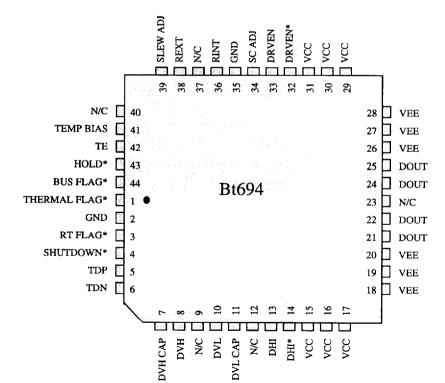

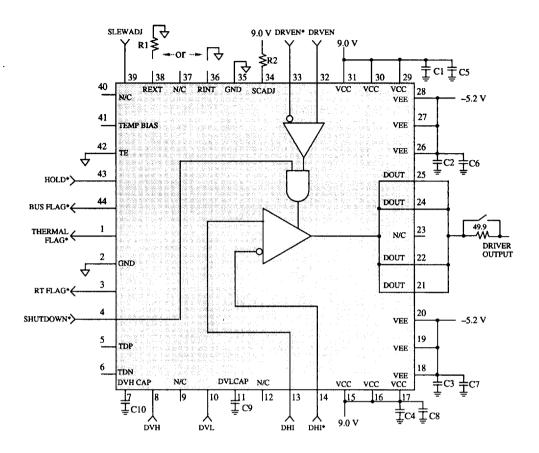

# **Functional Block Diagram**

# 100 MHz Performance In-Circuit Driver

### **Product Description**

The Bt694 is a high-current monolithic driver manufactured in a high-performance bipolar process. The DHI/DHI\* DRVEN/DRVEN\* inputs are wide voltage differential and therefore ECL, TTL, and CMOS compatible, making the Bt694 suitable in equipment based on any technology.

In Automatic Test Equipment (ATE) applications, the Bt694 serves as a driver suitable for functional testing up to 100 MHz. However, its high current rating and slew rate adjust allow it to also perform the in-circuit backdriving role. The adjustable wide voltage output range enables the Bt694 to drive TTL, CMOS, ECL and custom levels.

With both short-circuit limiting and onchip thermal shutdown, the Bt694 is robust, preventing faulty units under test from damaging the tester. The Bt694 is a small footprint, totally monolithic high-speed solution to a driver problem traditionally solved with discretes.

Brooktree Corporation • 9868 Scranton Road • San Diego, CA 92121-3707 (619) 452-7580 • 1 (800) 2-BT-APPS • TLX: 383 596 • FAX: (619) 452-1249 4-63 L694001 Rev. B

Brooktree\*

# **Circuit Description**

# Introduction

The driver circuit of the Bt694 will force its output to one of three states:

- 1. DVH (driver voltage high) level

- 2. DVL (driver voltage low) level

- 3. High-impedance condition.

All the digital inputs to Bt694 are wide-voltage differential signals. However, they may be driven differentially or single-endedly with the proper threshold voltage applied to one of each pair of differential inputs.

### **Drive Enables**

The DRVEN,DRVEN\* (drive enable) differential digital inputs control whether the driver output is forcing voltage or placed in a high-impedance state. If DRVEN is more positive than DRVEN\*, the output will force voltage DVL or DVH as selected by the DHI inputs. When DRVEN is more negative than DRVEN\*, the driver is set to the high-impedance state independent of the DHI inputs. The DRVEN inputs may be driven with ECL, TTL, or CMOS levels.

### DHI,DHI\*

The DHI,DHI\* differential inputs force the driver to DVH or DVL. The output will be DVH if DHI is higher in voltage than DHI\*. The output will be DVL if DHI is lower in voltage than DHI\*. The DHI,DHI\* inputs may be driven with ECL, TTL, or CMOS output levels.

Table 1 summarizes the functionality of the Drive Enable and DHI pins.

| DRVEN,DRVEN*                                                     | DHI,<br>DHI*                                    | SHUT<br>DOWN | DOUT |  |

|------------------------------------------------------------------|-------------------------------------------------|--------------|------|--|

| DRVEN>DRVEN*                                                     | DHI>DHI*                                        | 1            | DVH  |  |

| DRVEN>DRVEN*                                                     | DHI <dhi*< td=""><td>1</td><td>DVL</td></dhi*<> | 1            | DVL  |  |

| DRVEN <drven*< td=""><td>X</td><td>1</td><td>Hi-Z</td></drven*<> | X                                               | 1            | Hi-Z |  |

| Х                                                                | X                                               | 0            | Hi-Z |  |

Table 1. Drive Enable and DHI Pin Functionality.

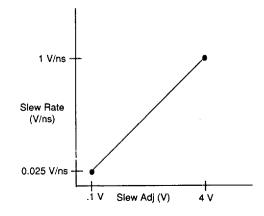

### Slew Rate Adjustment

Bt694's slew rate adjustability ranges from 0.025 V/ns to 1 V/ns. The broad range of adjustability allows the user to create a waveform as fast as the fixturing will allow. The slew rate may be controlled through the input pins SLEWADJ and RINT (or REXT).

The internal biasing current necessary for slew rate adjustment may be set through the RINT or REXT pin. One method is to simply connect RINT to GND, enabling a maximum slew rate of 1 V/ns.

Alternatively, an external resistor may be placed between the REXT pin and GND. The use of a precision external resistor is recommended in applications where the output slew rate must be set very accurately, as grounding RINT may yield nominal slew rate variations up to 10%. The recommended value for REXT is 2.7 K $\Omega$  for a 1 V/ns slew rate.

Once the internal biasing current is set through RINT (or REXT), slew rate may be adjusted via the SLEWADJ control voltage. A linear relationship exists betwen SLEWADJ voltage, REXT, and Bt694's output slew rate.

Slew Rate (V/ns) =

$$\frac{700}{100 + Rext}$$

\* SLEWADJ (V)

Please note that connecting RINT pin to GND is approximately equivalent to a 2.7 K $\Omega$  value for the REXT resistor ( $\pm 10\%$ ). Figure 1 shows the range of slew rate adjustability for REXT = 2.7 K $\Omega$ . In this case, a SLEWADJ voltage of 0.1 V nominally corresponds to 0.025 V/ns output slew rate. Similarly, a SLEWADJ voltage of 4 V nominally corresponds to 1 V/ns output slew rate.

The output drive capability remains constant over the range of output slew rates. That is, the Bt694 can drive the full 750 mA at slow, as well as fast slew rates.

Figure 1. Slew Rate Control (REXT=2.7 k Ω).

# Brooktree®

Bt694

# Circuit Description (continued)

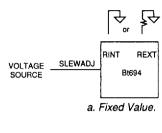

The user may set Bt694's slew rate to a fixed value by connecting the SLEWADJ pin to a fixed voltage supply (Figure 2a). Alternatively, Bt694's slew rate may be varied using a voltage DAC (Figure 2b).

Figure 2. Setting the Slew Rate.

### Thermal Shutdown

Bt694 is capable of performing the in-circuit backdriving role by providing surge currents up to 750 mA. The thermal monitor circuitry in the Bt694 continuously monitors the junction temperature of the device. When the junction temperature is raised above acceptable levels, a thermal flag is automatically asserted to inform the user that the device temperature is too high.

The THERMAL FLAG\* signal is an open-collector digital output. The user has the option of having the THERMAL FLAG\* signal latched or changing in real time. This is achieved with the HOLD\* signal which puts the THERMAL FLAG\* in latched or transparent mode. A logic low at the HOLD\* pin latches the THERMAL FLAG\* signal. A logic high at the HOLD\* pin allows the THERMAL FLAG\* signal to reflect the thermal state of the driver in real time.

Once the user has been warned by the THERMAL FLAG\* signal, the SHUTDOWN\* signal can be used to put the driver in the high-impedance state. The Bt694 can be configured to automatically self-protect or to allow external circuitry to control the shutdown process. There are three basic configuration modes which can be used with the thermal shutdown circuitry.

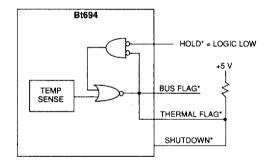

In mode A, the thermal flag is latched and Bt694 is self-protected (Figure 3). In this scheme, the THER-MAL FLAG\* signal is latched since the HOLD\* signal is asserted. By connecting SHUTDOWN\* to THER-MAL FLAG\*, Bt694 will automatically protect itself and threestate as soon as the thermal flag is raised. Bt694 will remain in high-impedance state until cleared by a logic high at the HOLD\* pin.

| THERMAL<br>FLAG* | HOLD* | SHUT<br>DOWN* | DOUT             |

|------------------|-------|---------------|------------------|

| 0                | 0     | 0             | Hi-Z             |

|                  | 0     | 1             | Normal Operation |

Figure 3. Mode A - Latched Thermal Flag, Self Protection.

# Brooktree\*

## Circuit Description (continued)

In modes of operation where the HOLD\* signal is held as logic low, Bt694 may power-up in the thermal shutdown state. The thermal shutdown circuitry must be initialized upon power-up by applying a high pulse to the HOLD\* signal

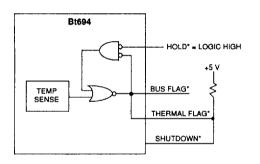

In mode B, the thermal flag is transparent (Figure 4). In this scheme, the THERMAL FLAG\* signal is not latched, since HOLD\* signal is not asserted. Therefore, the thermal flag signal reflects the thermal state of the device in real time. By connecting SHUTDOWN\* to THERMAL FLAG\*, Bt694 will automatically protect itself. In this mode, Bt694 may oscillate between a forced voltage output and a threestated output in response to the thermal flag.

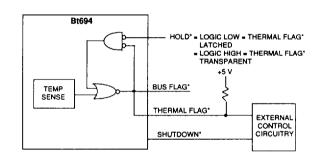

In mode C, the thermal flag may or may not be latched, and external control is used for the shutdown circuitry (Figure 5). In this scheme, control of HOLD\* depends on the user's preference and the nature of the external shutdown circuitry. When the THERMAL FLAG\* signal is asserted, the external shutdown circuitry should assert the SHUTDOWN\* signal and put the device in threestate mode. The risk inherent in using this mode is that the failure of the external control circuitry may not shut down the device in a timely manner. In this mode of operation, if the HOLD\* signal is

In this mode of operation, if the HOLD\* signal is held as logic low, Bt694 may power-up in the thermal shutdown state. The thermal shutdown circuitry must be initialized upon power-up by applying a high pulse to the HOLD\* signal.

Warning: external circuitry is required to protect the Bt694 in Mode C

| THERM<br>AL<br>FLAG* | HOLD* | SHUT<br>DOWN* | DOUT             |

|----------------------|-------|---------------|------------------|

| 0                    | 1     | 0             | Hi-Z             |

| 1                    | 1     | 1             | Normal Operation |

Figure 4. Mode B – Transparent Thermal Flag, Self-Protection.

| HOLD* | SHUT<br>DOWN* | DOUT             |

|-------|---------------|------------------|

| 0     | 0             | Hi-Z             |

| 0     | 1             | Normal Operation |

| 1     | 0             | Hi-Z             |

| 1     | 1             | Normal Operation |

|       |               |                  |

Figure 5. Mode C - Full External Control.

# DIOUKLIEE

# **Circuit Description** (continued)

### Flag Signals

The Bt694 provides two other flag signals in addition to the thermal flag, BUSFLAG\* and RTFLAG\*. BUSFLAG\* is logically equivalent to the THERMAL FLAG\* signal and allows the user to create an open-collector signal to monitor the thermal status of multiple drivers.

RT FLAG\*, however, is different from the THER-MAL FLAG\* in that it always reflects the thermal status of Bt694 in real time, even when the THERMAL FLAG\* signal is latched. When HOLD\* is asserted and the THERMAL FLAG\* is latched, it may be helpful to the user to monitor the RT FLAG\* signal to make certain that the device has sufficiently cooled down before THERMAL FLAG\* is unlatched. Of course, RT FLAG\* is functionally identical to THERMAL FLAG\* and BUS FLAG\* when the latter are not latched.

### Thermal Shut Down Trip Point

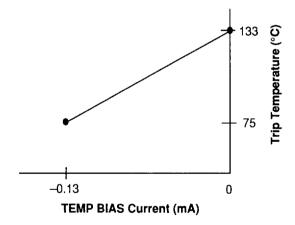

Bt694 allows the user to reduce the temperature at which the thermal shut down circuitry is activated. To set the trip temperature, a negative current should be injected into the TEMP BIAS input. This input curent is proportional to the trip temperature.

Trip Temperature ( $^{\circ}$ C) = 133 + 438 \* TEMP BIAS (mA)

From the above equation it can be seen that if the TEMP BIAS pin is left unconnected, the thermal shut down circuitry will trip when the die junction reaches approximately 133°C. Similarly, if a -0.1 mA current is injected into the TEMP BIAS node, the trip temperature is reduced to 89.5°C. Figure 6 illustrates the relationship between TEMP BIAS current and its corresponding trip temperatures. Please note that it is not recommend to increase the trip temperature above 133°C.

### Short-circuit Current

The short-circuit current limit of Bt694 can be adjusted using the SCADJ input pin. A positive current into this pin sets the bias current (ISCADJ) for the short-circuit adjustment circuitry. The level of the short-circuit limiting is directly proportional to ISCADJ bias current. The short-circuit current limit is approximately 500 times larger than ISCADJ. For example, an ISCADJ of 0.2 mA will result in 100 mA of short-circuit current limiting. An ISCADJ of 2 mA will result in 1.0 Amp of short-circuit current limiting.

Figure 10 in the Application Section shows a resistor (R2) connected between the SCADJ input pin and a positive voltage. The voltage at the SCADJ pin is +0.8V. In this example, a 8.25 K $\Omega$  value for R2 limits the short-circuit current to approximately 500 mA.

Figure 6. Trip Temperature for Different TEMP BIAS Currents.

# Bt694

# Brooktree\*

# Pin Descriptions

| Pin Name          | Description                                                                                                                                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drivers           |                                                                                                                                                                      |

| DRVEN,<br>DRVEN*  | Wide-voltage differential input pins that determine whether the driver output is forcing voltage or is placed in high-impedance state.                               |

| DHI,<br>DHI*      | Wide-voltage differential input pins that force one of two programmable voltages (DVH or DVL) at the driver output.                                                  |

| DOUT              | Driver output pins. All four output pins must be connected.                                                                                                          |

| DVL,DVH           | Buffered analog inputs that program the low and high driver output voltage levels.                                                                                   |

| DVLCAP,<br>DVHCAP | Analog inputs. Low and high-side reference compensation capacitor connections. A 0.01 µF capacitor to ground should be connected to each pin.                        |

| Slew Rate Adjust  |                                                                                                                                                                      |

| SLEWADJ           | Buffered analog voltage input that controls the driver's slew rate.                                                                                                  |

| RINT              | Analog input which biases the slew rate adjustment circuitry.                                                                                                        |

| REXT              | Analog input used for precise biasing of the slew rate adjustment circuitry. It is used as an alternative to RINT.                                                   |

| Thermal Shut Down |                                                                                                                                                                      |

| THERMAL FLAG*     | Open collector output used to indicate that the die temperature has exceeded the allowable limit.                                                                    |

| SHUTDOWN*         | TTL-compatible input that puts the driver in a high-impedance state (typically in response to the thermal flag).                                                     |

| HOLD*             | TTL-compatible input which determines whether the THERMAL FLAG* output is latched.                                                                                   |

| BUS FLAG*         | Open collector output which is identical to THERMAL FLAG*. It allows thermal signals in a board or a system to be connected to create a global flag.                 |

| RT FLAG*          | Open collector real time flag signal. This signal always reflects the real time status of thermal shutdown circuitry, even when the THERMAL FLAG* signal is latched. |

| Thermal Diode     |                                                                                                                                                                      |

| TDP               | Analog output connected to the anode of the thermal diode.                                                                                                           |

| TDN               | Analog output connected to the cathode of the thermal diode.                                                                                                         |

# Pin Descriptions (continued)

| Pin Name       | Description                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------|

| SCADJ          | Analog input which limits the maximum output current.                                                                |

| Power          |                                                                                                                      |

| VEE            | Negative analog power supply.                                                                                        |

| VCC            | Positive analog power supply.                                                                                        |

| GND            | Device ground                                                                                                        |

| Test Only Pins |                                                                                                                      |

| TEMPBIAS       | Analog input which biases the thermal shutdown temperature threshold.                                                |

| TE             | Analog input used to test the thermal shutdown circuitry. This pin must be connected to GND during normal operation. |

4

BROOKTREE CORP

# Brooktree\*

# **Applications Information**

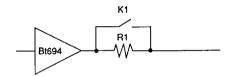

Figure 7 shows the Bt694 in a combinational configuration. When the relay K1 is open, Bt694 can be used as a high-speed functional driver capable of driving a series-terminated transmission line with speeds up to 100 MHz. When the relay K1 is closed, resistor R1 is shorted out and the Bt694 can be used as an in-circuit driver capable of sourcing up to 750 mA of surge current.

Figure 7. Combinational Driver.

### Thermal Diode

The Bt694 offers a thermal diode which reflects the actual temperature of the die in real time. The purpose of this diode is to provide information about the device to the user. The use of the thermal diode is not required during normal operation, but it is available for a variety of useful functions.

The thermal diode facilitates temperature sensing in a system. By monitoring the diode's resistance, the user can determine whether a section of the printed circuit board is dissipating too much power. Also, the diode allows the thermal characteristics of a given system to be characterized.

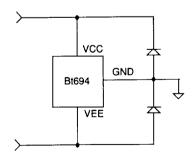

Figure 8. Power Supply Protection.

### Power Supply Decoupling

Both the VCC and VEE supply pins should be separately decoupled to GND with a 0.1 µF ceramic chip capacitor in parallel with a .001 µF chip capacitor. The bypass capacitors should be as close as possible to the device.

A ground plane and power planes are recommended to provide a low-inductance ground return path.

The VCC and VEE signals should be protected from reverse biasing during system power-up, power-down, or power supply failure. VCC below ground or VEE above ground can damage the device or compromise reliability. A reverse-biased Schottky clamp diode between VCC and ground and another between VEE and ground is recommended (Figure 8). The diodes should be capable of handling the total ICC or IEE currents on the printed circuit board. Only one set of protection diodes are needed per board.

### **Output Level Protection**

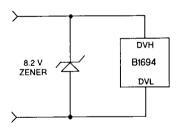

The Bt694 output drivers are designed to support adjustable digital waveforms with amplitudes up to 8 V. Adding an 8.2 V zener diode across the DVH and DVL inputs on the printed circuit board, as shown in Figure 9, is recommended to insure against accidentally programming the output levels to a too-large value.

Figure 9. DVH/DVL Protection.

Brooktree\*

# Bt694

# Applications Information (continued)

63E D

| Location                              | Description                                                                                                                                                                                                                          | Vendor Part Number                                                                                                 |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| C1-C4<br>C5-C8<br>C9, C10<br>R1<br>R2 | 0.1 μF, 50 V, 10% Ceramic Chip Capacitor<br>0.001 μF, 50 V, 10% Ceramic Chip Capacitor<br>0.01 μF, 50 V, 10% Ceramic Chip Capacitor<br>2.71 KΩ, 0.5% Thin Film Chip Resistor<br>Resistor Selected for Short-circuit Current Limiting | Sprague 11C1812CDG104K050NR<br>Sprague 11C1812CDG102K050NR<br>Sprague 11C1812CDG103K050NR<br>Dale TNP-550B-2711DAB |

The Vendor numbers above are listed only as a guide. Substitution of devices with similar characteristics will not affect performance of the Bt694. All devices should be placed as closely as possible to the Bt694.

Figure 10. Typical Connection Schematic and Parts List.

# **Applications Information** (continued)

### Power Dissipation Considerations

The Bt694 is specified for operation in environments with an ambient temperature of up to 70°C with airflow of 400 LFPM. However, operating the driver to the extremes of power supplies and output loading can increase the power dissipation to a point where the maximum ambient temperature must be lower than 70°C with 400 LFPM, or an external heatsink must be applied to the product. This temperature is for true worst-case continuous operation.

The total power equation consists of three independent terms as shown in the following equation:

$$Power_{(Total)} = Power_{(Quiescent)} + Power_{(DC Load)} + Power_{(AC Load)}$$

The individual terms are derived and explained below.

### Power (Quiescent)

The power calculation based upon supply voltage and current is:

$$Power_{(Quiescent)} = VCC(ICC) + VEE(IEE)$$

where VCC and VEE are the largest power supply voltages and ICC and IEE are the maximum supply currents. For example, if the maximum power supplies under which Bt694 is operating are VCC = 9.0 V and VEE = -5.2 V, and power supply currents are ICC = 85mA and IEE = -70 mA correspondingly, then the quiescent power dissipation is:

Power<sub>(Quiescent)</sub> =

$$(9.0 \text{ V} * 85 \text{ mA}) + (-5.2 \text{ V} * -70 \text{ mA})$$

= 1.13 watts

### Power (DC Load)

The DC loading on the driver calculates the product of the voltage difference from the power supply to the forced voltage multiplied by the current load.

For example, if Bt694 is used as a functional driver expected to force 3 V and source 20 mA into its output, the power dissipation would be:

Power (DC Load) =

$$(VCC - 3 V) * 20 mA$$

But, if Bt694 is used as an in-circuit driver expected to force 0 V and sink 500 mA into its output, the power dissipation would be:

Power (DC Load) =

$$(0 - VEE) * 500 \text{ mA}$$

Generalized, the power dissipation term for DC loading

$$Power_{(DC\ Load)} = |V_{Supply} - V_{Prog}| * I_{Load}$$

# Applications Information (continued)

### Power(AC Load)

The third term in the total power equation is the power generated by the outputs charging and discharging transmission lines. This term only applies when Bt694 is used as a functional type driver, and does not apply if the driver is used as an in-circuit type driver.

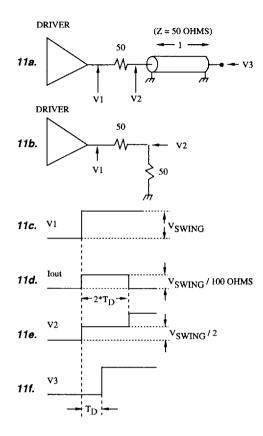

The power due to the AC Load is a more complicated calculation that requires a knowledge of transmission line theory. Figure 11a schematically represents a series-terminated 50  $\Omega$  transmission line. A 50  $\Omega$  transmission line that is series terminated will appear as a  $100 \Omega$  resistor to GND while the output is slewing (Figure 11b). The output signal of the driver is signal V1 (Figure 11c). This will be modeled as an instantaneous step of V<sub>Swing</sub> amplitude. The magnitude of the AC current Iout in Figure 11d, will depend on the size of the output swing,  $V_{Swing}$ . For instance, a 3 V output swing will require 30 mA from the driver output to charge the 50  $\Omega$  transmission line. This power is dissipated only for a short time. The time that the model is valid primarily depends on the length of transmission lines being driven.

The end of the line (Figure 11f) is also a step of amplitude V<sub>Swing</sub>, but it occurs later, T<sub>D</sub>. This period of time depends upon the velocity of propagation delay (tpd) of the transmission media and the length of the line (1). The tpd of microstrip transmission lines is about 150 ps/inch (60 ps/cm). The signal V2 must wait for the reflection from the open end of the line to return to complete its step from one half V<sub>Swing</sub> to the full value (Figure 11e). This total time is then 2 \* Tp.

For example, 18 inches of microstrip transmission line yields a  $T_D$  of 2.7 ns. The total time for the driver supplying charge current is 5.4 ns. These values are simplistic and should be viewed as true worst case for voltage swings of approximately 5 V with the nominal rise and fall times for this driver product into transmission lines 18 inches or longer.

This explanation is a basis for understanding the nature of dynamic currents and how they could affect overall power dissipation. This information is also useful for understanding the need for local capacitive bypassing near the Bt694. These currents cannot come

Figure 11. Transmission Line Waveforms.

directly from the power supplies because of interconnect inductances. Multiple drivers on a single PCB will require very good, low-inductance power distribution and adequate bypassing to supply the dynamic edge currents that possible coincident edges could demand.

To completely determine the power dissipation, a worst-case condition is presented in which the driver constantly charges and discharges the transmission line. This would occur when the signal is a clock of 50% duty cycle at a frequency (f) with a half period (T/2) equal to 2 \* T<sub>D</sub>.

# **Applications Information** (continued)

The actual programmed values of VOL and VOH do not matter for this calculation, only the  $V_{Swing}$ . The transient currents will alternately source and sink from VCC and VEE; therefore, the charging current can be multiplied by the difference in supply voltages, VCC minus VEE. The power equation for AC loading is:

$$Power_{(ACLoad)} = (VCC - VEE) * I_{AC}$$

where

$$\begin{split} I_{AC} &= (V_{Swing} * 2 * T_D) / (100 \ \Omega * T/2) \\ &= (V_{Swing} / 100 \ \Omega) * (4 * T_D/T) \\ &= (V_{Swing} / 100 \ \Omega) * 4 * T_D * f \end{split}$$

therefore,

Power(AC) = (VCC-VEE) \*

$$V_{Swing} / 100 \Omega$$

)

\* 4 \*  $T_D$  \* f

### Power (SlewAdj)

The power contributed from the slew rate adjustment circuitry is due to ICC and IEE currents increasing as the slew rate is varied from 0.025 V/ns to 1 V/ns. The power supply currents specified in the DC Characteristics section of this datasheet are typical values for slew rates of 1 V/ns. If slower slew rates are used, the supply currents will be decreased by 15.4 mA/V/ns.

For example, using the recommended operating conditions and a slew rate of 1 V/ns:

Reducing the slew rate to 0.025 V/ns:

### **Power Dissipation Summary**

Because a product of this type can be used in a variety of different environments, it is necessary to evaluate the power dissipation on a case-by-case basis. Lower die temperature results in longer operating life for semi-conductors. After calculating the worst-case power dissipation of the application, the die temperature can be calculated with the  $\theta JA$  values and the ambient temperature by:

$$T_{iunction} = T_{ambient} + \theta JA * Power_{Total}$$

A good value for maximum junction temperature during continuous operation is 125°C. Although a small area of the Bt694 die will exceed this junction temperature for short periods of time, the overall die temperature should be kept below 125°C during continuous operation. If calculations indicate that this temperature will be exceeded, the design should be altered to correct this. Use of an external heatsink or decreased ambient air temperatures should be considered.

# **Recommended Operating Conditions**

| Parameter                     | Symbol  | Min     | Тур  | Max     | Units |

|-------------------------------|---------|---------|------|---------|-------|

| Positive Power Supply         | VCC     | 4.5     | 9.0  | 12      | V     |

| Negative Power Supply         | VEE     | -4.2    | -5.2 | _7      | V     |

| Total Analog Power Supply     | VCC-VEE | 1       | 14.2 | 16.2    | V     |

| Ground                        | GND     |         | 0    |         | V     |

| Analog Inputs                 |         |         |      | 1       |       |

| DVH                           |         |         |      | VCC-2.9 | V     |

| DVL                           |         | VEE+2.9 |      | 1       | V     |

| DVH-DVL                       |         | 0.5     |      | 8.0     | V     |

| Driver Outputs                |         | 1       |      | ì       |       |

| VCC-VOL                       |         | 4.2 V   |      | 12      | v     |

| VOH-VEE                       |         | 4.2 V   |      | 12      | v     |

| Ambient Operating Temperature | TA      | 0       |      | +70     | °C    |

| Junction Temperature          | TJ      |         |      | 125     | ·C    |

P3E D

Thermal equilibrium is established by applying power for at least 2 minutes while maintaining a transverse air flow of 400 LFPM over the device mounted on the printed circuit board.

# **Absolute Maximum Rating**

|          | 1 1 | +14     | v  |

|----------|-----|---------|----|

|          |     | 1 1     | V  |

|          |     | -10     | V  |

|          |     | +18     | V  |

|          |     |         |    |

| VEE      |     | VCC     | V  |

| VEE      |     | VCC     | V  |

|          |     |         |    |

| VEE      |     | VCC     | V  |

|          |     | 17      | V  |

| 1        |     | 14      | V  |

| l        |     | 13      | V  |

|          |     |         |    |

| VEE -0.7 |     | VCC+0.7 | V  |

| -55      |     | +125    | °C |

| -65      |     | +150    | °C |

|          |     | +150    | °C |

|          |     | 260     | °C |

|          |     |         |    |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Bt694

# Brooktree\*

# **DC Characteristics**

| Parameter                                                     | Symbol   | TA<br>(°C) | Min        | Тур         | Max      | Units    |

|---------------------------------------------------------------|----------|------------|------------|-------------|----------|----------|

| Differential Digital Inputs                                   |          |            |            |             |          |          |

| DHI,DHI*, DVREN, DVREN*                                       |          |            |            |             | 200      |          |

| Input Current                                                 | IIN      | FULL       | -300       |             | +300     | μA<br>V  |

| Common Mode Input Voltage Range (Note 1)<br>(relative to GND) | VRNG     | FULL       | -2.0       |             | +5.0     | <b>'</b> |

| Differential Voltage Swing                                    | VDIFF    | FULL       | 0.25       |             | +7.0     | v        |

| Analog Inputs                                                 |          |            |            |             |          |          |

| DVH, DVL                                                      | ****     |            | 50         |             | . 50     |          |

| Input Current                                                 | IIN      | FULL       | -50        |             | +50      | μА       |

| Power Supply Current (Notes 2, 3)                             |          |            |            |             |          |          |

| Positive Power Supply                                         | ICC      | FULL       |            | 85          |          | mA       |

| Negative Power Supply                                         | IEE      | FULL       |            | <b>-7</b> 0 |          | mA       |

| Slew Rate Adjustment Input                                    |          |            |            |             |          |          |

| SLEWADJ Voltage (Note 4)                                      | VSLEWADJ |            | 0.1        |             | 4.0      | v        |

| Input Current                                                 | IIN      | FULL       | -50        |             | +50      | μА       |

| Short-Circuit Adjust (SCADJ) Input                            |          |            |            |             |          |          |

| Input Current                                                 | IIN      | FULL       | 0.25       |             | 2.0      | mA       |

| Driver Circuit                                                |          |            |            |             |          |          |

| Output Voltage Range                                          | VDOUT    | FULL       | VEE +2.9   |             | VCC -2.9 | V        |

| Static Output Current                                         | IDOUT    | FULL       | 100        |             |          | mA       |

| Surge Current                                                 | ISC      | FULL       | -500       |             | +750     | mA       |

| DOUT Leakage Current                                          | ILEAK    | FULL       | -50        |             | +50      | μА       |

| (over entire output voltage range)                            |          |            |            |             |          | ·        |

| DOUT Offset Voltage (Notes 2,5)                               |          |            |            |             |          |          |

| High Offset Voltage                                           |          |            |            |             |          |          |

| Dout = DVH = 0V                                               | }        |            | -35        | -10         | +15      | mV       |

| Change in offset due to CMR (Note 6)                          |          |            |            | -5          |          | mV/V     |

| Change in offset due to                                       |          |            |            |             |          |          |

| SLEWADJ Voltage (Note 7)                                      |          |            |            | <b>-</b> 7  |          | mV/V     |

| Low Offset Voltage                                            |          |            |            |             |          |          |

| DOUT = DVL = 0V                                               |          |            | <b>-45</b> | -20         | +5       | mV       |

| Change in offset due to CMR (Note 6)                          |          |            |            | <b>-</b> 5  |          | mV/V     |

| Change in offset due to                                       |          |            |            |             |          |          |

| SLEWADJ Voltage (Note 7)                                      |          |            |            | +7          |          |          |

| Offset Voltage Temperature Coefficient                        | DOUT TC  |            |            | -0.05       |          | mV/°C    |

| Driver Output Impedance (Note 8)                              | ZOUT     | FULL       |            | 0.5         | 1.0      | Ω        |

| Driver PSRR                                                   | PSRR     | FULL       | 40         | 0.0         |          | dB       |

| Driver Voltage Output Swing (Note 2)                          |          | FULI.      | 0.5        |             | 80       | v        |

| Driver Voltage Output Swing (Note 2)                          |          | FULL       | 0.5        |             | 8.0      | V        |

See test conditions and notes on next page.

### **DC Characteristics**

| Parameter                                                                 | Symbol   | TA<br>(°C)                   | Min                    | Тур       | Max                       | Units              |

|---------------------------------------------------------------------------|----------|------------------------------|------------------------|-----------|---------------------------|--------------------|

| THERMAL FLAG*, BUS FLAG*, RT FLAG* Trip Temperature VOL (IOL = 10 mA) IOH | ТПІРТЕМР | Full<br>Full<br>Full         | -20                    | 133<br>.4 | .5<br>+20                 | °C<br>V<br>µA      |

| SHUTDOWN*,HOLD* IIH (VIH = 5.5 V) IIL (VIL = 0 V) VIH VIL                 |          | Full<br>Full<br>Full<br>Full | -20<br>-50<br>2.0<br>0 |           | +20<br>+10<br>5.5<br>+0.8 | μΑ<br>μΑ<br>V<br>V |

DC Test conditions (unless otherwise specified): "Recommended Operating Conditions."

VCC = +9 V, Vcc = -5.2 V, SLEWADJ = 1 V, SCADJ = 0.25 mA. All parameters specified at 0°C are guaranteed by characterization and are not production tested.

- Note 1: The maximum for this specification may not be higher than Vcc-2V.

- Note 2: Assumes no load to driver.

- Note 3: SLEWADJ voltage = 4.0 V.

- Note 4: The maximum for this specification may not be higher than Vcc - 2.5 V.

- VOS = V DOUT VIN, where VIN = DVH or DVL. There are three components contributing to the DOUT offset volt-Note 5: age. The primary component is measured at DOUT = 0V and SLEWADJ = 1 V. As DOUT is varied from 0 V, the change in CMR (Common Mode Range) adds to the offset voltage. Finally, as SLEWADJ is varied from 1 V, the offset is again increased/decreased.

- Referenced to DOUT = 0 V. Note 6:

- Note 7: Referenced to SLEWADJ = 1 V.

- Zout values are doubled when IDOUT < 100 mA. Note 8:

The specified limits shown can be met only after thermal equilibrium has been established. Thermal equilibrium is established by applying power for at least 2 minutes while maintaining a transverse air flow of 400 LFPM over the device mounted on the printed circuit board.

# Brooktree\*

### **AC Characteristics**

| Parameter                                                                                                                       | Conditions                           | Symbol                                          | Min   | Тур              | Max             | Units          |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|-------|------------------|-----------------|----------------|

| Tpd from DHI to DOUT Temperature Coefficient (DHI to DOUT)                                                                      | Note 1                               | Tpd(DVR)                                        | 1.5   | 2.5<br>5         |                 | ns<br>ps/°C    |

| Propagation Delays DRVEN to DOUT (High »Hi-Z) DRVEN to DOUT (Hi-Z » High) DRVEN to DOUT (Low » Hi-Z) DRVEN to DOUT (Hi-Z » low) | Note 2<br>Note 2<br>Note 2<br>Note 2 | Tphz (DOUT) Tpzh (DOUT) Tplz (DOUT) Tpzl (DOUT) |       | 3<br>3<br>3<br>3 |                 | ns<br>ns<br>ns |

| DOUT Slew Rate<br>Slew Rate Sensitivity to SLEWADJ                                                                              | Vswing                               | SR<br>SR/SLEWADJ                                | 0.025 | 0.25             | 1.0             | V/ns<br>V/ns/V |

| Maximum Toggle Rate                                                                                                             | Note 3                               | Fmax                                            |       | 100              |                 | MHz            |

| Minimum Pulse Width                                                                                                             | Note 3,4                             | Tpw                                             |       | 5                |                 | ns             |

| Pre/Over/Under Shoot                                                                                                            | Note 5                               |                                                 |       |                  | 3%+<br>50<br>mV | % of<br>Swing  |

| Output Capacitance in Hi-Z                                                                                                      | 10 MHz to GND                        | Cout                                            |       | 10               |                 | pF             |

AC Test Conditions (unless otherwise specified): TA equals 25°C, VCC equals +9 V, VEE equals -5.2 V, VOL equals 0 V, VOH equals 3 V, and 49.9  $\Omega$  series output resistor on driver output for proper back termination into a 50  $\Omega$  transmision line. The AC parameters are not production tested, they are based upon characterization data.

- Note 1: Into 18 inches of  $50-\Omega$  transmission line terminated with  $1 \text{ k}\Omega + 2 \text{ pF}$  with proper back-termination resistor. Tpd is measured from crossover point of DHI and DHI\* to point where output changes by 50%. Tpd is specified at 1 V/ns slew rate with VOL = 0 V, and VOH = +3 V.

- Note 2: Specification condition: VOL = -1 V, VOH = +1 V. Output terminated to GND by  $50 \Omega$ . Tpd is measured from crossover point of DRVEN and DRVEN\* to the point where a 10% change in output voltage occurs.

- Note 3: Specification condition: Vswing = 3 V into 18 inches of 50  $\Omega$  transmission line terminated with 1 k $\Omega$  + 2 pF. Slewrate = 1 V/ns

- Note 4: The output pulse width is measured at the 50% points of a 3 V swing.

- Note 5:  $V \text{ swing } \ge 1 \text{ V}$ .

The specified limits shown can be met only after thermal equilibrium has been established. Thermal equilibrium is established by applying power for at least 2 minutes while maintaining a transverse air flow of 400 LFPM over the device mounted on the printed circuit board.

# **Thermal Characteristics**

| Airflow                   | Still Air | 50 LFPM | 400 LFPM |

|---------------------------|-----------|---------|----------|

| θ <sub>JA</sub> (°C/watt) | 41        | 33      | 21       |

# **Ordering Information**

| Model Number | Package                                         | Ambient<br>Temperature<br>Range |

|--------------|-------------------------------------------------|---------------------------------|

| Вt694КНЈ     | 44-pin PLCC<br>(with internal<br>heat spreader) | 0° to +70° C                    |