# UNISONIC TECHNOLOGIES CO., LTD

TS2043 **Preliminary** CMOS IC

# TOUCH PANEL CONTROLLER

#### DESCRIPTION

The UTC TS2043 is a highly integrated 12-bit SAR analog-to-digital (A/D) converter designed for touch panel controllers. It features serial interface and low on-resistance drivers for 4-wire resistive touch panels. The UTC TS2043 contains all the analog and digital circuitry needed to complete a pen request.

The UTC TS2043 features a low-power dissipation consumes only 800uW under a 125KHz sample rate and in a 2.7V supply condition, it consumes only 2.7uW at shutdown mode. The supply voltage is from 2.7V to 5.5V under normal operation.

The UTC TS2043 can be used in applications such as touch panels, personal digital Assistants (PDAs), smart phones, point-to-sales terminals, high speed data acquisition, portable instruments, and low power instruments.

#### **FEATURES**

- \* Power Supply Voltage: 2.7V ~ 5.5V

- \* Serial Interface

- \* 4-Wire Touch Panel Interface

- \* Embedded Touch Panel Drivers

- \* 12-Bit AD Converter

- \* Programmable 8 or 12 Bit Resolution

- \* Conversion Rate: 125 KHz

- \* 2 Auxiliary Analog Inputs

- \* Full Power Down Control

# ORDERING INFORMATION

| Halogen Free  | Package | Packing   |

|---------------|---------|-----------|

| TS2043G-R16-R | SSOP-16 | Tape Reel |

www.unisonic.com.tw 1 of 8 QW-R502-404.a

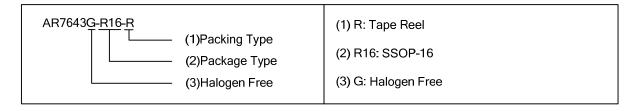

# **■ PIN CONFIGURATION**

# **■ PIN DESCRIPTION**

| PIN NO. | PIN NAME  | DESCRIPTION                                                                           |  |

|---------|-----------|---------------------------------------------------------------------------------------|--|

| 1       | $V_{DD}$  | Power Supply, 2.7V ~ 5.5V                                                             |  |

| 2       | X+        | X+ Input; ADC Input Channel 1.                                                        |  |

| 3       | Y+        | Y+ Input; ADC Input Channel 2.                                                        |  |

| 4       | X-        | X- Input.                                                                             |  |

| 5       | Y-        | Y- Input.                                                                             |  |

| 6       | GND       | Ground.                                                                               |  |

| 7       | IN3       | Auxiliary Input 1; ADC Input Channel 3.                                               |  |

| 8       | IN4       | Auxiliary Input 2; ADC Input Channel 4.                                               |  |

| 9       | $V_{REF}$ | Reference Voltage Input.                                                              |  |

| 10      | $V_{DD}$  | Power Supply, 2.7V ~ 5.5V                                                             |  |

| 11      | /PENIRQ   | Pen Interrupt. Requires $10$ K $\Omega$ ~ $100$ K $\Omega$ external pull-up resistor. |  |

| 12      | DOUT      | Serial Data Output. This output pin is high impedance when /CS is high.               |  |

| 13      | BUSY      | Busy Output. This output pin is high impedance when /CS is high.                      |  |

| 14      | DIN       | Serial Data Input.                                                                    |  |

| 15      | /CS       | Chip Select Input. This input is active low.                                          |  |

| 16      | DCLK      | External Clock Input.                                                                 |  |

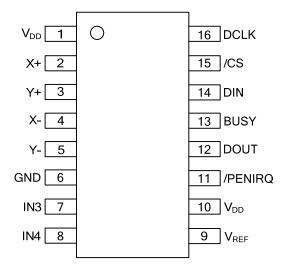

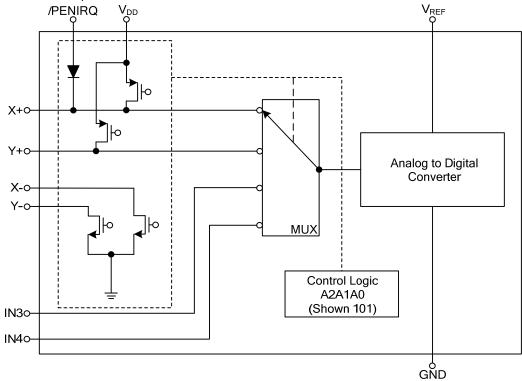

# **■ BLOCK DIAGRAM**

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                   | SYMBOL           | RATINGS                     | UNIT |

|-----------------------------|------------------|-----------------------------|------|

| V <sub>DD</sub> to GND      |                  | -0.3 ~ +6                   | V    |

| Analog Input to GND         |                  | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| Digital Input to GND        |                  | -0.3 ~ V <sub>DD</sub> +0.3 | V    |

| Junction Temperature        | TJ               | +150                        | °C   |

| Operating Temperature Range | T <sub>OPR</sub> | -40 ~ <b>+</b> 85           | °C   |

| Storage Temperature Range   | T <sub>STG</sub> | -60 ~ +150                  | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged.

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

■ **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub>=-40°C to 85°C, V<sub>DD</sub>=+2.7V, V<sub>REF</sub>=+2.7V, f<sub>sample</sub>=125KHz, f<sub>CLK</sub>=24\*f<sub>SAMPLE</sub>, 12-bit mode, Digital inputs=GND or V<sub>DD</sub>. Typical values are at T<sub>A</sub>=+25°C, unless otherwise specified.)

| PARAMETER                 | SYMBOL           | TEST CONDITIONS           | MIN          | TYP  | MAX           | UNIT |

|---------------------------|------------------|---------------------------|--------------|------|---------------|------|

| Power Supply Requirements |                  | 1 1201 001121110110       |              |      |               |      |

|                           | .,               | Specified Performance     | 2.7          |      | 3.6           | V    |

| Power Supply              | $V_{DD}$         | Operating Range           | 2.7          |      | 5.5           | V    |

|                           |                  |                           |              | 300  |               | μA   |

| Nominal Supply Current    | $I_{DD}$         | Shut Down Mode            |              |      | 4             |      |

|                           |                  | $(D_{CLK}=D_{IN}=V_{DD})$ |              |      | 1             | μΑ   |

|                           |                  |                           |              | 800  |               | μW   |

| Power Dissipation         | P <sub>D</sub>   | Shut Down Mode            |              |      | 2.7           | μW   |

|                           |                  | (V <sub>DD</sub> =2.7V)   |              |      | 2.1           | μνν  |

| System Performance        |                  |                           |              |      |               |      |

| Resolution                |                  |                           |              | 12   |               | Bit  |

| Integral nonlinear        | INL              |                           |              | +/-2 |               | LSB  |

| Differential nonlinear    | DNL              |                           |              | +/-1 |               | LSB  |

| Gain Error                |                  |                           |              | +/-4 |               | LSB  |

| Offset Error              |                  |                           |              | +/-6 |               | LSB  |

| Digital Input/Output      |                  |                           |              |      |               |      |

|                           | V <sub>OH</sub>  |                           | $V_{DD}*0.8$ |      |               | V    |

| Logic Family              | $V_{OL}$         | CMOS                      |              |      | 0.4           | V    |

|                           | V <sub>IH</sub>  | CIVIOS                    | $V_{DD}*0.7$ |      | $V_{DD}$ +0.3 | V    |

|                           | V <sub>IL</sub>  |                           | -0.3         |      | 0.8           | V    |

| /PEN Request (/PENIRQ)    | $V_{OL}$         | 100KΩ Pull-Up             |              | 0.65 |               | V    |

| Analog Input              |                  |                           |              |      |               |      |

| Input Span                |                  |                           | 0            |      | $V_{REF}$     | V    |

| Input Range               |                  |                           | -0.2         |      | $V_{DD}$ +0.2 | V    |

| Capacitance               |                  |                           |              | 25   |               | pF   |

| Reference Input           |                  |                           |              |      |               |      |

| Range                     | $V_{REF}$        |                           | 1            |      | $V_{DD}$      | V    |

| Input Current             | I <sub>REF</sub> | Specified Performance     |              | 15   |               | μΑ   |

| X / Y Switches            |                  |                           |              |      |               |      |

| X+, Y+                    |                  | Switch On-Resistance      |              | 5    |               | Ω    |

| X-, Y-                    |                  | Switch On-Resistance      |              | 5    |               | Ω    |

**CMOS IC**

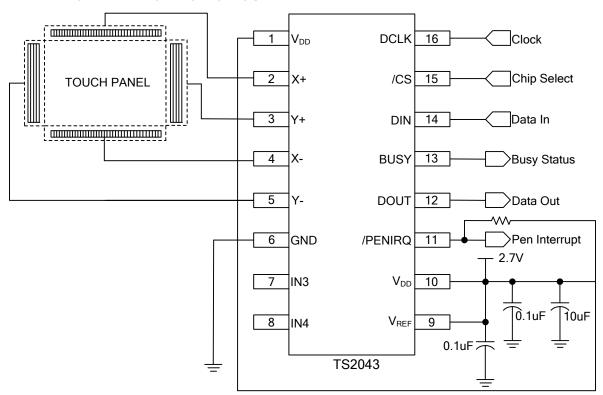

# **■ TYPICAL APPLICATION CIRCUIT**

#### **■** APPLICATION INFORMATION

#### **OVERVIEW**

The UTC **TS2043** is a 12-bit switched-capacitor Analog-to-Digital (A/D) converter and incorporates four channel inputs, a serial interface, and low on-resistance switches for touch panel.. It supplies from a single supply varying from +2.7V to +5.5V. It requires an external reference, which is directly limiting the input range of the converter. The four-channel multiplexer contained in the circuit decides the input to this converter (See **Figure 1**). In addition, an external clock is also required.

Figure 1. Diagram of Input Channel

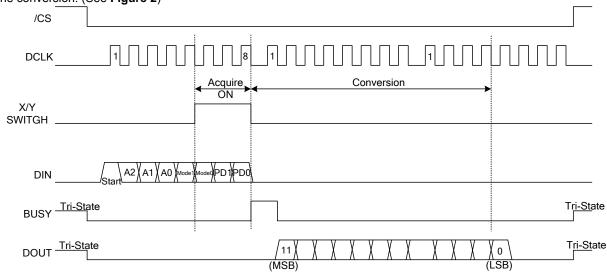

#### **OPERATION OF 24-CLOCKS**

The UTC **TS2043** communicates with microprocessors or digital signal processors through a synchronous serial interface. For a total 24 clock cycles on the DCLK input, three serial communications are needed to complete one conversion. (See **Figure 2**)

Figure 2. Serial Interface of TS2043

## ■ APPLICATION INFORMATION(Cont.)

#### **Serial Interface**

Once a falling signal applies on /CS pin (active in low), the operation is initiated. After /CS falls, the UTC **TS2043** begins to look for a start bit on the DIN input. At the end of the operation the /CS pin should be pulled high, which minimizes supply current if DCLK is left running.

#### **Control Byte**

The first eight clock cycles provides the control byte on DIN pin. (See **Table I** and **Table II** for more information). The control byte represents the start operation, addressing, resolution, and power down information.

Table I. Control Bits in the Control Byte

| Ī | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | Start | A2    | A1    | A0    | Mode1 | Mode0 | PD1   | PD0   |

**Table II. Description of the Control Bits**

| BIT   | NAME     | DESCRIPTION                |

|-------|----------|----------------------------|

| 7     | Start    | Start Bit.                 |

| 6,5,4 | A2,A1,A0 | Input Channel Select Bits. |

| 3,2   | Mode1    | 12-Bit / 8-Bit Conversion  |

|       | Mode0    | Configuration Bit.         |

| 1,0   | PD1,PD0  | Power Down Control Bits    |

#### Start Bit - Initiate Start

The control byte starts with the first high bit on DIN. The first bit must always be logic high (1) to initiate the start of the conversion. The UTC **TS2043** will not start until the start bit is detected.

#### Addressing Bits - Input Channel Selection

The next three bits on control byte are addressing bits (A2, A1, A0), which select the active input channel of the input multiplexer, and touch panel drivers. (See **Table III** for more information).

**Table III. Input Channel Configuration**

| A2 | A1 | Input<br>Channel | X Switch | Y Switch | Reference |

|----|----|------------------|----------|----------|-----------|

| 0  | 0  | X+               | OFF      | ON       | $V_{REF}$ |

| 1  | 0  | Y+               | ON       | OFF      | $V_{REF}$ |

| 0  | 1  | IN3              | OFF      | OFF      | $V_{REF}$ |

| 1  | 1  | IN4              | OFF      | OFF      | $V_{REF}$ |

#### Mode Bits - Conversion Resolution Configuration

The Mode bits (Mode1, Mode0) set the resolution of this device. With the Mode1 bit LOW (0), the following conversion will have 12 bits of resolution. With the Mode1 bit HIGH (1) the following conversion will have 8 bits of resolution. (See **Table IV** for more information.)

**Table IV. Resolution Configuration**

| Mode1 | Mode0 | DESCRIPTION       |

|-------|-------|-------------------|

| 0     | 1     | 12bits Resolution |

| 0     | 0     | 12bits Resolution |

| 1     | 1     | 8bits Resolution  |

| 1     | 0     | 8bits Resolution  |

### PD0 and PD1 Bits - Power Down Control

The last two bits are PD1 and PD0 bits, which control the power down mode of the UTC **TS2043**. Through applying a same logic high(1) this device enters a power-up mode, while enters a power-down mode by a same logic low (0) on PD1 and PD0 bits.(See **Table V** for more information).

**Table V. Power-Down Selection**

| i abic vi | I OHO. DOI | **** OCIOOLIOII |                                                                       |

|-----------|------------|-----------------|-----------------------------------------------------------------------|

| PD1       | PD0        | PENIRQ          | DESCRIPTION                                                           |

| 0         | 0          | Enable          | Power-Down between conversions. Y- switch is on.                      |

| 0         | 1          | Disable         | Power-Down between conversions. Y- switch is off. /PENIRQ is disabled |

| 1         | 0          | Disable         | No used.                                                              |

| 1         | 1          | Disable         | No Power-Down between conversions.                                    |

# ■ APPLICATION INFORMATION(Cont.)

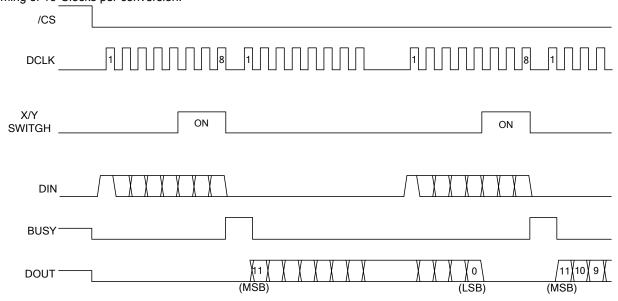

#### **OPERATION OF 16-CLOCKS**

The typical operation of the UTC **TS2043** is 24-clocks (three control bytes) per conversion. However the control bits for the next conversion can be overlapped with current conversion for a faster conversion. **Figure 3** shows the timing of 16-Clocks per conversion.

Figure 3. Timing of 16-clocks per Conversion

#### **ANALOG INPUT**

There are four channel inputs in the UTC **TS2043**. X+ and Y+ inputs are for touch panel measurement, 2 auxiliary inputs are IN3 and IN4. The input to the A/D converter is selected via the four-channel multiplexer. (see Block Diagram)

#### **Input Channel**

The input channel configuration of the UTC **TS2043** is shown in Table V. The control bits are set via the DIN pin. (see Control byte section). The selected channel is for A/D converter input. Please refer to Figure 5 for detailed input channel multiplexer. For measuring X+ and Y+, Y switches and X switches are turned on respectively. **Reference Input**

An external reference voltage source is needed for the UTC **TS2043**. The reference input sets the Analog-to-Digital converter (ADC) input range. If the reference input is from the power supply directly, to avoid noise from power supply, special care must be taken into consideration.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.