T-71-11

# ML926/7 REMOTE CONTROL RECEIVERS (WITH MOMENTARY OUTPUTS)

The ML926 and ML927 are MOS LSI monolithic circuits for use as receivers of remote control signals for television control and many other applications. They are general purpose devices each receiving sixteen of the thirty-two codes transmitted by the SL490 circuit as pulse position modulation (PPM).

#### **FEATURES**

- Minimum Package Size 8-Lead Minidip

- Four Outputs Indicate in Binary the Code Currently Being Received, and Are Switched Off (Low) When No Valid Code is Detected.

- On-Chip Oscillator

- High Power, Free Drain, Output Buffers

#### **OPERATING NOTES**

The receiver operates on a timescale fixed by an internal oscillator and its external timing components. The oscillator may be adjusted to any value between 15Hz and 150kHz (allowing different receivers to respond to different transmission rates withint the same area).

Checks are made to ensure 6 pulses, or 5 bits, are received for a word to be valid, and only after two consecutive and identical words is the receiver allowed to respond to the incoming code.

The ML926 responds only to codes 00001 to 01111 from the SL490 transmitter whereas the ML927 responds to codes 10001 to 11111.

# **ABSOLUTE MAXIMUM RATINGS**

V<sub>DD</sub> supply and inputs w.r.t. Vss Storage temperature +0.3V to -25V Operating temperature ambient +0.3V to -25V -55°C to +125°C -10°C to +65°C

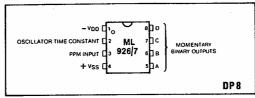

Fig.1 Pin connections (top view)

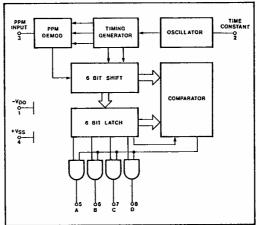

Fig 2 Block diagram

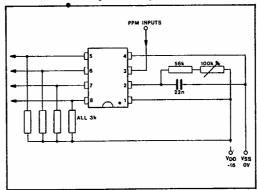

Fig. 3 Test circuit

#### **ELECTRICAL CHARACTERISTICS**

Test Conditions (unless otherwise stated):  $V_{D\dot{D}}=-16V,~V_{SS}=0V$   $T_{amb.}=25^{\circ}C$

T-77-11

| Characteristic                                               | Pin         | Value                     |         |                               |                | 0 1111                       |

|--------------------------------------------------------------|-------------|---------------------------|---------|-------------------------------|----------------|------------------------------|

|                                                              |             | Min.                      | Тур.    | Max.                          | Units          | Conditions                   |

| Operating supply voltage range<br>Current consumption        | 1           | 12<br>2                   | 14<br>3 | 18<br>4                       | V<br>mA        |                              |

| PPM input Input level high Input level low Input pulse width | 3<br>3<br>3 | 1<br>V <sub>DD</sub><br>1 |         | O<br>-6<br>22T <sub>OSC</sub> | V<br>V<br>μsec | $T = \frac{1}{f_{\rm osc}}$  |

| Oscillator time constant See Note 1                          |             |                           |         |                               |                |                              |

| Oscillator frequency                                         | 2           | 15                        | 3k      | 150k                          | Hz<br>Hz       | Typical TC: 22nF to Vss      |

| Variation wrt V <sub>DD</sub>                                |             |                           | 1       |                               | %/V            | 100kito V <sub>DD</sub>      |

| Output voltage high<br>Output device leakage (Output OFF)    | 5-8<br>5-8  | -1.5                      |         | 0<br>1                        | V<br>μΑ        | R <sub>L</sub> = 3.0K to VDD |

Note 1.  $R_{osc}$  (Pin 2) is  $56k-156k\Omega$ ,  $f_{osc} \simeq \frac{1}{0.15CR}$  ±20%

#### **PIN FUNCTIONS**

POSITIVE LOGIC '1' = Vss, '0' = VDD

1. V<sub>DD</sub>

-14V to -18V power supply

# 2. Oscillator time constant

An RC time constant of a capacitor and resistor at this pin defines the internal clock frequency. The clock frequency may be varied from 15Hz to 150kHz.

# 3. PPM input

The output of the 'front end' amplifier is connected to this pin; the signal must consist of a normal 'low' level with pulses to high level corresponding to the PPM pulses from the transmitter.

# 4. Vss 0V (ground)

#### 5-8. A,B,C,D

Four open drain high power transistors give a binary coded output of the valid code being received.

|                                                                                                                                                                                          | Momentary binary outputs                                                                                                                              |                                                                                                              |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Transmitter<br>Code                                                                                                                                                                      | ML926                                                                                                                                                 | ML927                                                                                                        |  |  |  |

| EDCBA                                                                                                                                                                                    | DCBA                                                                                                                                                  | DCBA                                                                                                         |  |  |  |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                          | 0 0 0 0<br>0 0 0 1<br>0 0 0 1 0<br>0 0 1 0 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 0 1<br>1 0 0 0<br>1 0 1 1<br>1 1 0 0<br>1 1 1 0 1<br>1 1 1 0 0<br>1 1 1 1 | 0 0 0 0                                                                                                      |  |  |  |

| 1 0 0 0 1<br>1 0 0 0 1<br>1 0 0 1 0<br>1 0 0 1 0<br>1 0 1 0 1<br>1 0 1 0 1<br>1 0 1 1 0<br>1 1 0 0 0<br>1 1 0 0 1<br>1 1 0 1 0<br>1 1 1 0 0<br>1 1 1 1 0 0<br>1 1 1 1 1 0<br>1 1 1 1 1 0 |                                                                                                                                                       | 0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0<br>0 1 0 1<br>0 1 1 1<br>1 0 0 0 1<br>1 0 1 1<br>1 1 1 0<br>1 1 1 1 |  |  |  |

Table 1 Response to SL490 codes