## HISTECH LINEAR COMPONENT DOTA SHEET

# SI-Cr THIN FILM RESISTORS VALUES OF 10Ω to 100KΩ, LASER TRIMMABLE

### **GENERAL DESCRIPTION**

HTL'S IC compatible silicon-chrome resistors are offered as an option on selected semi-custom analog arrays as well as on all custom integrated circuits. The resistors are made using a very accurate deposition process by which a thin film of high-resistivity silicon-chrome material is deposited over the field oxide surface of the chip, prior to the aluminum metalization step. This thin film resistor offers some excellent characteristics that cannot be matched by the normal IC diffused or implanted resistors. In addition to the excellent qualities of the siliconchrome resistors, they can also be laser trimmed to a very accurate matching ratio of typically  $\pm 0.005\%$ .

### **FEATURES**

Wide Range of Resistor Values

Negligible Voltage Dependence

Very Low Temperature Coefficient

Very High Breakdown Voltage

Good Matching Characteristics

Very Low Temperature Drift Matching

Very Low Capacitance

Excellent Ratio of Laser Trimmed

Resistors

### TYPICAL APPLICATIONS

Analog and Digital Precision Circuits

A/D and D/A Converters

Feedback Networks

Summing Amplifiers

Precision Voltage Dividers

Operational Amplifiers and Comparators

Voltage References and Regulators

Active Filters

Electrical characteristics, Prior to laser trimming, at ambient temperature  $T_A = 25$ °C (Unless otherwise noted)

| PARAMETER                                                                                                                                                                              | SYMBOL           | CONDITIONS                                                    | MIN | TYP                                                | MAX  | UNITS  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------|-----|----------------------------------------------------|------|--------|

| Absolute Sheet<br>Resistance                                                                                                                                                           | Р                | ν <sub>R</sub> =5ν                                            | 800 | 1000                                               | 1200 | Ω/Ω    |

| Resistor-Substrate<br>Breakdown Voltage                                                                                                                                                | BV <sub>RS</sub> | I <sub>S</sub> =1μA (Note 1)                                  | 150 |                                                    |      | v      |

| Temp. Coefficient of Resistors                                                                                                                                                         | ΔR/ΔΤ            | V <sub>R</sub> =5V -55°C < T <sub>A</sub> < 125°C             |     | <b>-3</b> 5                                        | -60  | PPM/°C |

| Matching of Equal<br>Design Value Resistors<br>10 m Resistor Width<br>15 m Resistor Width<br>25 m Resistor Width<br>50 m Resistor Width<br>75 m Resistor Width<br>100 m Resistor Width | ΔR(1:1)          | V <sub>R</sub> =5V R <sub>1</sub> = R <sub>2</sub> (Note 2,3) |     | ± 1<br>± 0.5<br>± 0.2<br>± 0.1<br>± 0.07<br>± 0.05 |      | *      |

Electrical characteristics, Prior to laser trimming, at ambient temperature  $T_A = 25$ °C (CONTINUED)

| Matching of Unequal<br>Design Value Resistors |                                                      |                                                                                                                     |                               |                                           |

|-----------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------|

| 10μm Resistor Width                           | ΔR(1:2)<br>ΔR(1:4)<br>ΔR(1:8)                        | $R_2 = 2R_1$ $R_2 = 4R_1$ $R_2 = 8R_1$ (Note 2,3)                                                                   | ± 2<br>± 3<br>± 4             |                                           |

| 15μm Resistor Width                           | ΔR(1:2)<br>ΔR(1:4)<br>ΔR(1:8)                        | $R_2 = 2R_1$ $R_2 = 4R_1$ $R_2 = 8R_1$ (Note 2,3)                                                                   | ± 1<br>± 2<br>± 3             |                                           |

| 25μm Resistor Width                           | ΔR(1:2)<br>ΔR(1:4)<br>ΔR(1:8)                        | $R_2 = 2R_1$ $R_2 = 4R_1$ $R_2 = 8R_1$ (Note 2,3)                                                                   | ± 0.5<br>± 1<br>± 2           |                                           |

| 50μm Resistor Width                           | ΔR(1:2)<br>ΔR(1:4)<br>ΔR(1:8)                        | $R_2 = 2R_1$ $R_2 = 4R_1$ $R_2 = 8R_1$ (Note 2,3)                                                                   | ±0.2<br>±0.5<br>±1            |                                           |

| 75μm Resistor Width                           | ΔR(1:2)<br>ΔR(1:4)<br>ΔR(1:8)                        | R <sub>2</sub> = 2R <sub>1</sub><br>R <sub>2</sub> = 4R <sub>1</sub> (Note 2,3)<br>R <sub>2</sub> = 8R <sub>1</sub> | ± 0.15<br>± 0.25<br>± 0.5     |                                           |

| 100μm Resistor Width                          | ΔR(1:2)<br>ΔR(1:4)<br>ΔR(1:8)                        | R <sub>2</sub> = 2R <sub>1</sub><br>R <sub>2</sub> = 4R <sub>1</sub><br>R <sub>2</sub> = 8R <sub>1</sub>            | ± 0.1<br>± 0.2<br>± 0.3       |                                           |

| Temp. Coefficient<br>of Matching Drift        | ΔR(1:1)/ΔT<br>ΔR(1:2)/ΔT<br>ΔR(1:4)/ΔT<br>ΔR(1:8)/ΔT | V <sub>R</sub> =5V -55°C < TA < 125°C                                                                               | ± 2<br>± 4<br>± 8<br>± 16     | PPM/ <sup>O</sup> C                       |

| Resistor-Substrate<br>Capacitance             | C <sub>RS</sub>                                      | 0 <v<sub>R<bv<sub>RS (Note 4)</bv<sub></v<sub>                                                                      | 0.02<br>3.1 •10 <sup>-5</sup> | pF/mil <sup>2</sup><br>pF/μm <sup>2</sup> |

#### Notes

1) Breakdown occurs through a thick layer of oxide (Field Oxide). The breakdown is destructive and non-reversible.

Resistor ratios matching is satisfied by

$$k\left(1-2\left|\frac{\Delta R_{\left(MAX\right)}}{100\lambda}\right|\right) < \frac{R_{2}}{R_{1}} < k\left(1+2\left|\frac{\Delta R_{\left(MAX\right)}}{100\lambda}\right|\right)$$

Where K is the resistor ratio of the nominal values, and  $\rm R_{1}$  and  $\rm R_{2}$  are any two resistors chosen from these populations on chip.

- These particular matching parameters apply to the various resistor ratios on chip, prior to laser triming. Matching of laser trimmed resistors is typically  $\pm 0.005\%$ .

- 4) MOS capacitance is specified. An average capacitance of 0.5pF must be added if resistor is connected to a package pin. Also included must be a capacitance of about 1pF for each bonding pad which is related to the specific resistor.

## histech Linear component Datasheets

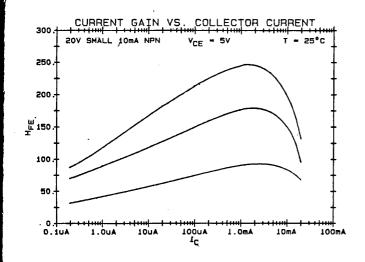

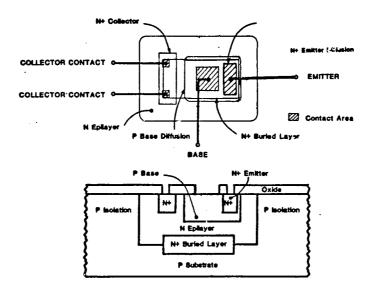

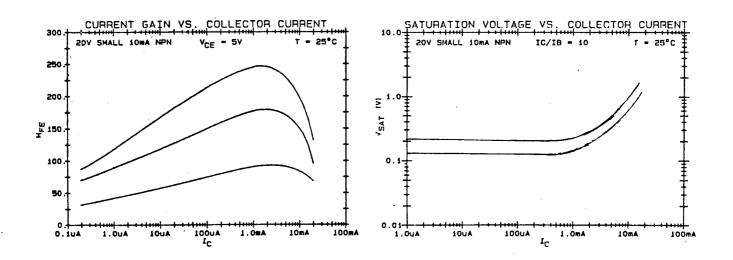

## 20V SMALL NPN TRANSISTOR 10ma QUAD COLLECTOR CONTACT

#### **GENERAL DESCRIPTION**

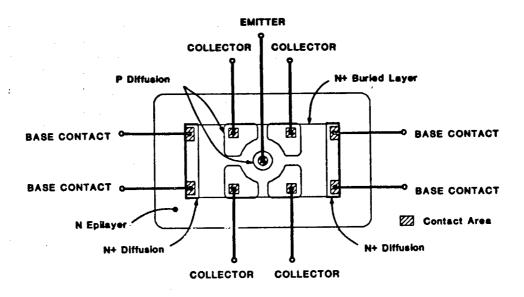

The small 10mA NPN transistor has two N+ diffusion regions in the collector area with two collector contacts in each of these diffusions. The contacts are normally connected together to reduce the series collector resistance as well as the saturation voltage. The small NPN transistor is available in two versions, with and without a deep N+ diffusion in the collector region. The deep N+ diffusion allows for an additional increase in the operating current.

#### **FEATURES**

Four Collector Contacts

Matched VBE and hFE Transistor Parameters

TYPICAL, APPLICATIONS

Amplifiers

Comparators

Current Sources

Bias Circuits

Level Shifters

Emitter Followers

Diode Connected Transistors

Zener Diode Connections

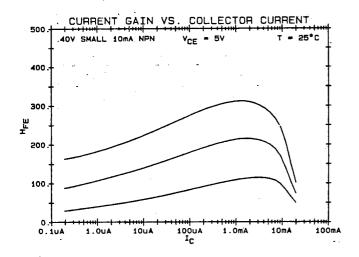

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE  $T_A=25^{\circ}C$  (Unless otherwise noted)

| PARAMETER                                    | SYMBOL                |                                      | CONDITIONS                 |                                                 |             | MIN  | ТҮР  | MAX  | UNITS |

|----------------------------------------------|-----------------------|--------------------------------------|----------------------------|-------------------------------------------------|-------------|------|------|------|-------|

| DC Current Gain                              | h <sub>FE</sub>       | I <sub>C</sub> =1mA                  | V <sub>CE</sub> =5V        |                                                 | (Note 1)    | . 80 |      | 300  |       |

| Matching of DC Current Gains                 | ∆h <sub>FE</sub>      | I <sub>C</sub> = 1mA                 | V <sub>CE</sub> =5V        |                                                 | (Note 2)    |      | ±5   | ±10  | *     |

| Temperature Coefficient of h <sub>FE</sub>   | Δħ <sub>FE</sub> /ΔΤ  | I <sub>C</sub> =1mA                  | -55°C < TA                 | < 125 <sup>0</sup> C                            |             |      | 0.5  |      | %/°(  |

| Callanter Bass Laskage Company               | ,                     | V -20V                               | TA=25°C                    |                                                 | (Note 3)    |      | 0:01 | 0.1  | nA    |

| Collector-Base Leakage Current               | <sup>I</sup> сво      | V <sub>CB</sub> =20V                 | TA=125°C                   |                                                 | (Note 3)    |      | 1    | 10   | na    |

| Callantan Fatham Lasham Command              | ,                     | V                                    | TA=25°C                    |                                                 | (Note 3)    |      | 0.2  | 2    | nA    |

| Collector-Emitter Leakage Current            | ICEO                  | V <sub>CE</sub> =20V                 | TA=125°C                   |                                                 | (Note 3)    |      | 0.2  | 2    | μА    |

| Collector-Emitter Breakdown Voltage          | LVCEO                 | Ic=1mA                               |                            |                                                 |             | 20   |      |      | ¥     |

| Collector-Base Breakdown Voltage             | вусво                 | 1 <sub>C</sub> =100µA                |                            |                                                 |             | 30   |      |      | ٧     |

| Emitter-Base Breakdown Voltage               | BV <sub>EBO</sub>     | IE=10hV                              |                            | ····                                            |             | 6.25 |      | 7.25 | ٧     |

| Collector-Substrate Breakdown<br>Voltage     | BVCS                  | Ic=10µA                              |                            |                                                 |             | 20   |      |      | V     |

| Base-Emitter Forward Voltage                 | V <sub>BE</sub>       | I <sub>E</sub>   = 1mA               | V <sub>CE</sub> =5V        |                                                 |             | 0.67 |      | 0.79 | ٧     |

| Matching of Base-Emitter Forward<br>Voltages | ΔV <sub>BE</sub>      | I <sub>E</sub>  =1mA                 | VCE=5V                     |                                                 | (Note 4)    |      | ±2   | ±6   | m∀    |

| Temperature Coefficient of V <sub>BE</sub>   | ΔV <sub>BE</sub> /ΔT  | I                                    | V <sub>CE</sub> =5V        |                                                 |             |      | -1.8 |      | mV/°C |

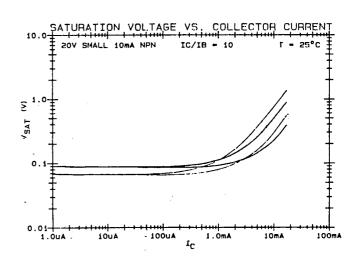

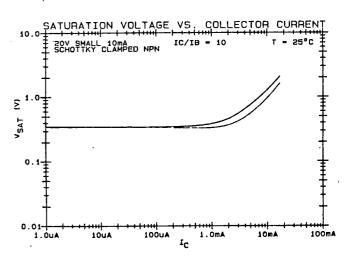

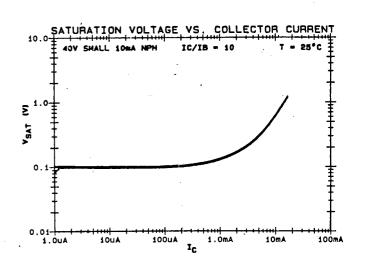

|                                              |                       | I <sub>C</sub> =lmA                  | (One Diffu                 | tor Contact<br>sion Region)                     | (Note 5)    |      | 0.16 | 0.3  |       |

| Collector-Emitter Saturation<br>Voltage      | V <sub>CE</sub> (SAT) | ·                                    | 17                         | tor Contacts<br>sion Regions)                   | (Note 5)    |      | 0.14 | 0.25 | ٧     |

|                                              |                       | (I <sub>C</sub> /I <sub>B</sub> )=10 | Four Colle<br>  (Two Diffu | sion Regions)<br>ctor Contacts<br>sion Regions) |             |      | 0.09 | 0.17 |       |

| Maximum Collector Current                    | I <sub>C(MAX)</sub>   | P <sub>D(MAX)</sub> =30              | OmW                        |                                                 | ···         |      |      | 20   | mА    |

| Cutoff Frequency                             | f <sub>T</sub>        | I <sub>C</sub> =5mA                  |                            |                                                 |             |      | 500  |      | MHz   |

|                                              |                       |                                      |                            | I <sub>C</sub> =1mA                             | ·           |      | 6    |      |       |

| Storage Time                                 | ™S                    | (1C/1B)=1                            | R <sub>B</sub> =750Ω       | I <sub>C</sub> =10mA                            | <del></del> |      | 100  |      | ns    |

| Emitter-Base Capacitance                     | CEB                   | V <sub>EB</sub> =OV                  |                            |                                                 | (Note 6)    |      | 1    |      | pF    |

| Collector-Base Capacitance                   | ССВ                   | V <sub>CB</sub> =0V                  |                            |                                                 | (Note 6)    | -    | 1    |      | pF    |

| Collector-Substrate Capacitance              | c <sub>cs</sub>       | V <sub>CS</sub> =0V                  |                            | ***                                             | (Note 6)    |      | 3.8  |      | pF    |

Information furnished by HI-Tech Linear is believed to be accurate and reliable. However, no responsibility is assumed by HTL for its use, nor for any infringements of pattents or other rights which may result from its use. HTL reserves the right to make changes at any time without notice.

- 1) -All collector contacts connected in parallel.

- h<sub>FF</sub> matching is satisfied by 2) hFE(1)  $h_{FE(1)}$  and  $h_{FE(2)}$  are any two current gains chosen from a population of like transistors on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage. 3)

- Matching of  $V_{BE}$  is satisfied by  $|V_{BE(2)} V_{BE(1)}| < 2|\Delta V_{BE(MAX)}|$  where  $V_{BE(1)}$ 4) and  $V_{BE(2)}$  are any two base-emitter voltages chosen from a population of like transistors on chip.

- 5) It is not recommended to operate the transistor in the saturation mode when only one collector contact or two collector contacts on the same  $N^+$  diffusion region are used, since a high saturation voltage is inevitable, especially at increased collector currents.

- Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction

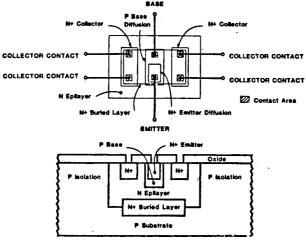

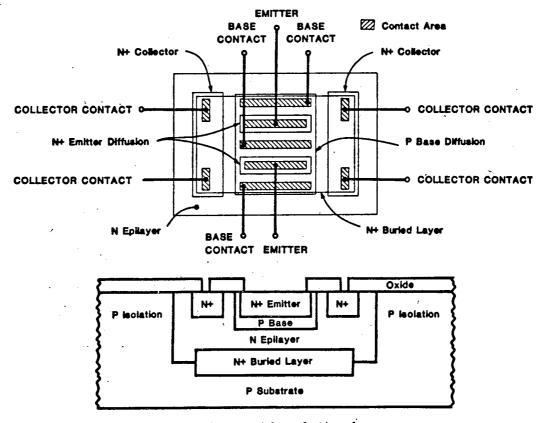

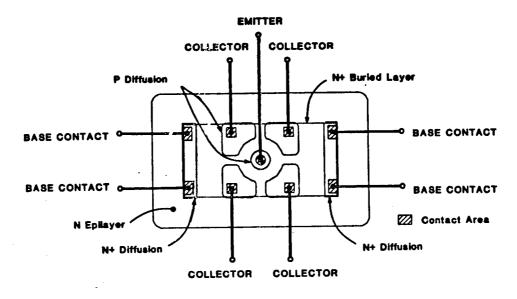

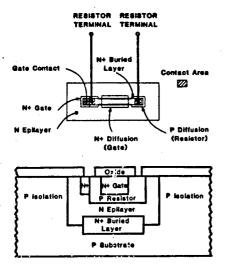

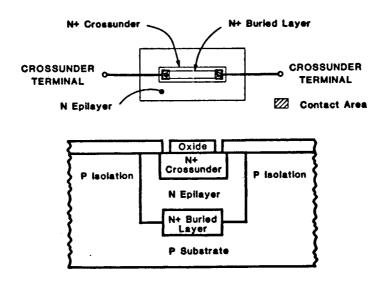

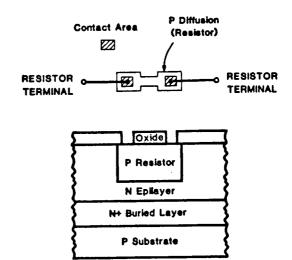

Layout and Cross-Section of Small 10mA NPN Transistor (Not to Scale)

## hi-tech linear component data shee

#### SMALL TOMA DIODE (TRANSISTOR WITH COLLECTOR AND BASE SHORTED)

### ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE $T_A = 25^{\circ}C$ (Unless otherwise noted)

| PARAMETER                                 | SYMBOL              |                       | CONDITION            |          | MIN  | ТҮР  | MAX  | UNITS |

|-------------------------------------------|---------------------|-----------------------|----------------------|----------|------|------|------|-------|

| ,                                         |                     | I <sub>F</sub> =100µA |                      |          | 0.61 |      | 0.73 |       |

| Forward Voltage Drop                      | V <sub>F</sub> .    | I <sub>F</sub> =1mA   |                      |          | 0.67 |      | 0.79 | 1 v   |

|                                           |                     | I <sub>F</sub> =10mA  |                      |          | 0.77 |      | 0.89 | 1     |

| Matching of Forward Voltages              | ۵۷ <sub>F</sub>     | I <sub>F</sub> =1mA   |                      | (Note 1) |      | ±2   | ±6   | mV    |

| Temperature Coefficient of V <sub>F</sub> | ΔV <sub>F</sub> /ΔT | I <sub>F</sub> =1mA   |                      |          |      | -1.8 |      | mV/°C |

| Leakage Current                           | ,                   | V <sub>R</sub> =20V   | T <sub>A</sub> =25°C | (Note 2) |      | 0.1  |      |       |

|                                           | I <sub>0</sub>      | R-LOV                 | TA=125°C             | (Note 2) |      | 10   |      | nA    |

| Breakdown Voltage                         | BVD                 | I <sub>R</sub> =10μA  |                      |          | 6.25 |      | 7.25 | ٧     |

| Maximum Diode Current                     | I <sub>F(MAX)</sub> |                       |                      |          |      |      | 20   | mA    |

| Junction Capacitance                      | C <sub>J</sub>      | V <sub>n</sub> =0V    |                      | (Note 3) |      | 1    |      | pF    |

#### Notes:

- Matching of  $V_F$  is satisfied by  $\|V_{F(2)} V_{F(1)}\| \le 2\|\Delta V_{F(MAX)}\|$  where  $V_{F(1)}$  and  $V_{F(2)}$  are any two forward voltages chosen from a population of like diodes on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction under test.

#### SMALL 10mA ZENER DIODE (EMITTER-BASE JUNCTION OF TRANSISTOR)

#### ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE Ta=25°C (Unless otherwise noted)

| PARAMETER                                       | SYMBOL         | CONDITIONS            |          | MIN  | ТҮР  | MAX  | UNITS              |

|-------------------------------------------------|----------------|-----------------------|----------|------|------|------|--------------------|

|                                                 |                | I <sub>Z</sub> =lµA   |          | 6.2  | 6.7  | 7.2  |                    |

|                                                 | ļ              | I <sub>Z</sub> =10μA  |          | 6.25 | 6.75 | 7.25 | 1                  |

| Breakdown Voltage                               | v <sub>z</sub> | I <sub>Z</sub> =100µA | (Note 1) | 6.3  | 6.8  | 7.3  | ) v                |

|                                                 |                | IZ=1mA                | (Note 1) | 6.4  | 6.9  | 7.4  | 1                  |

| •                                               |                | I <sub>Z</sub> =10mA  | (Note 1) | 7    | 7.5  | 8    |                    |

| Dynamic Impedance<br>(in the Breakdown Mode)    | RZ             | I Z=1mA               |          |      | 75   |      | Ω                  |

| Temperature Coefficient of Breakdown<br>Voltage | ۵ÝZ/۵۲         | I <sub>Z</sub> =1mA   |          |      | 2.4  |      | mV/ <sup>O</sup> C |

#### Notes

l) Base-emitter breakdown, unlike base-collector breakdown, can be damaging to the transistor particularly for long breakdown duration at high current. Under these conditions,  $h_{\rm FE}$  degradation is inevitable; therefore,  $V_{\rm Z}$  is tested at  $l_{\rm P}A$  and  $l0_{\rm P}A$  for each transistor. Operation at higher current has been fully characterized and is guaranteed by extrapolation.

## 8368605 0007536 7 📗 D MISTECH LINEAR COMPONENT DATA

## 20V LOW NOISE NPN TRANSISTOR 10ma DUAL COLLECTOR CONTACT

#### **GENERAL DESCRIPTION**

The low noise NPN transistor is identical in size to th 10mA small NPN transistor. It has a single N+ diffusion in the collector area with two collector contacts in it. The base diffusion and the base contact are much larger than those of the small NPN transistor. This results in a much reduced base resistance and consequently in a lower level of noise. It is recommended to use the transistor at very low current levels of 10nA to 1mA to maintain the low noise characteristics.

#### FEATURES .

Large Base Contact for Reduced Noise **Dual Collector Contacts** Matched  $v_{\mbox{\footnotesize{BE}}}$  and  $h_{\mbox{\footnotesize{FE}}}$  transistor parameters TYPICAL APPLICATIONS Low Noise Amplifiers Differential Input Stages Low Level Amplifiers

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE  $T_A=25^{\circ}C$  (Unless otherwise noted)

| PARAMETER                                    | SIMBOL               |                                     | CONDITIONS             |                      |          | MIN  | ТҮР  | MAX  | UNITS |

|----------------------------------------------|----------------------|-------------------------------------|------------------------|----------------------|----------|------|------|------|-------|

| DC Current Gain                              | h <sub>FE</sub>      | I <sub>C</sub> =1mA                 | V <sub>CE</sub> =5V    | <del></del>          | (Note 1) | 80   |      | 300  |       |

| Matching of DC Current Gains                 | Δh <sub>FE</sub>     | I <sub>C</sub> =1mA                 | °VcE=5V                |                      | (Note 2) |      | ±5   | ±10  | *     |

| Temperature Coefficient of h <sub>FE</sub>   | Δh <sub>FE</sub> /ΔT | I <sub>C</sub> =1mA                 | -55°C < TA             | < 125 <sup>0</sup> C |          |      | 0.5  |      | %/°(  |

|                                              |                      |                                     | TA=25°C                | ····                 | (Note 3) |      | 0.01 | 0.1  | ηA    |

| Collector-Base Leakage Current               | Ісво                 | V <sub>CB</sub> =20V                | TA=1250C               |                      | (Note 3) |      | 1    | 10   |       |

|                                              |                      |                                     | TA=25°C                |                      | (Note 3) |      | 0.2  | 2    | nΑ    |

| Collector-Emitter Leakage Current            | I <sub>CEO</sub>     | VCE=20V                             | TA=125°C               |                      | (Note 3) | 1    | 0.2  | 2    | μĄ    |

| Collector-Emitter Breakdown Voltage          | LV <sub>CEO</sub>    | Ic=1mA                              |                        |                      |          | 20   |      |      | ٧     |

| Collector-Base Breakdown Voltage             | вусво                | I <sub>C</sub> =100µA               |                        |                      |          | 30   |      |      | ٧     |

| Emitter-Base Breakdown Voltage               | BVEBO                | I <sub>E</sub> =10µA                |                        | <u>,,</u>            |          | 6.25 |      | 7.25 | V     |

| Collector-Substrate Breakdown<br>Voltage     | BV <sub>CS</sub>     | 1 <sub>C</sub> =10µA                |                        |                      |          | 20   |      |      | ٧     |

| Base-Emitter Forward Voltage                 | V <sub>BE</sub>      | 1 <sub>E</sub>  =1mA                | V <sub>CE</sub> =5V    |                      |          | 0.67 |      | 0.79 | ٧     |

| Matching of Base-Emitter Forward<br>Voltages | ΔVBE                 | I <sub>E-</sub>  =1mA               | VCE=5V                 |                      | (Note 4) |      | ±2   | ±6   | ψV    |

| Temperature Coefficient of VBE               | ΔV <sub>BE</sub> /ΔT | I <sub>E</sub>  =1mA                | V <sub>CE</sub> =5V    |                      |          |      | -1.8 |      | mV/C  |

| Collector-Emitter Saturation                 | v                    | Ic=lmA                              | One Coll               | ector Contac         | t        |      | 0.2  | 0.3  | V     |

| Voltage                                      | VCE (SAT)            | (I <sub>C</sub> /I <sub>B</sub> )=1 | Two Coll               | ector Contac         | ts       |      | 0.16 | 0.25 |       |

| Maximum Collector Current                    | I <sub>C</sub> (MAX) | PD(MAX)=3                           | DOmW .                 |                      |          |      |      | 20   | #RA   |

| Cutoff Frequency                             | f <sub>T</sub>       | Ic*5mA                              | V <sub>CE</sub> =5V    |                      |          |      | 500  |      | MHz   |

| Storage Time                                 | ¹s                   | (1 <sub>C</sub> /I <sub>B</sub> )=1 | 0 R <sub>B</sub> ≖750Ω | I <sub>C</sub> =1mA  |          |      | 100  |      | ns    |

| Emitter-Base Capacitance                     | CEB                  | V <sub>EB</sub> =OV                 | · · · · -              | 1 - 6                | (Note 5) | 1    | 1    |      | pF    |

| Collector-Base Capacitance                   | C <sub>CB</sub>      | V <sub>CB</sub> =OV                 |                        |                      | (Note 5) |      | 1    |      | pF    |

| Collector-Substrate Capacitance              | c <sub>cs</sub>      | V <sub>CS</sub> =0V                 | » <del></del>          |                      | (Note 5) |      | 3.8  |      | pF    |

information furnished by Hi-Tech Linear is believed to be accurate and reliable. However, no responsibility is assumed by HTL for its use, nor for any infringements of pattents or other rights which may result from its use. HTL reserves the right to make changes at any time without notice.

## HI-TECH LINEAR COMPONENT DATA SHEET

- All collector contacts connected in parallel.

- 2)  $h_{FE}$  matching is satisfied by  $1-2\left|\frac{an_{FE}(MAX)}{100\%}\right| < \frac{n_{FE}(2)}{h_{FE}(1)} < 1+2\left|\frac{an_{FE}(MAX)}{100\%}\right|$  where  $h_{FE}(1)$  and  $h_{FE}(2)$  are any two current gains chosen from a population of like transistors on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- 4) Matching of  $V_{BE}$  is satisfied by  $\|V_{BE(2)}^{-V}\|_{BE(1)}\| < 2\|\Delta V_{BE(MAX)}\|$  where  $V_{BE(1)}$  and  $V_{BE(2)}$  are any two base-emitter voltages chosen from a population of like transistors on chip.

- 5) Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction under test.

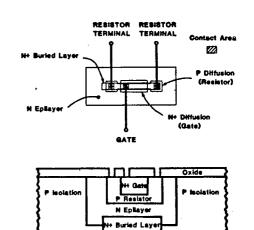

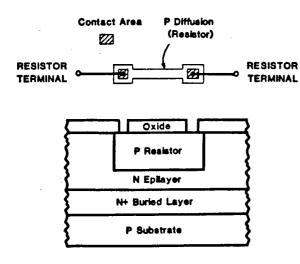

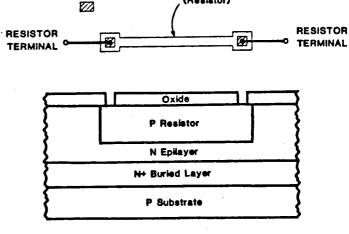

Layout and Cross-Section of Low Noise NFN Transistor (Not to Scale)

#### SMALL 10MA DIODE (TRANSISTOR WITH COLLECTOR AND BASE SHORTED)

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE Ta=25°C (Unless otherwise noted)

| PARAMETER                                 | SYMBOL               |                       | CONDITION                             |          | MIN  | ТҮР  | MAX  | UNITS              |

|-------------------------------------------|----------------------|-----------------------|---------------------------------------|----------|------|------|------|--------------------|

|                                           |                      | I <sub>F</sub> =100µA | -                                     |          | 0.61 |      | 0.73 |                    |

| Forward Voltage Drop                      | V <sub>F</sub>       | I <sub>F</sub> =1mA   |                                       |          | 0.67 |      | 0.79 | 1 v                |

|                                           |                      | I <sub>F</sub> =10mA  |                                       |          | 0.77 |      | 0.89 |                    |

| Matching of Forward Voltages              | ۵۷ <sub>F</sub>      | I <sub>F</sub> =1mA   | · · · · · · · · · · · · · · · · · · · | (Note 1) |      | ±2   | ±6   | m۷                 |

| Temperature Coefficient of V <sub>F</sub> | ΔV <sub>F</sub> /ΔT  | I <sub>F</sub> =1mA   |                                       |          |      | -1.8 |      | mV/ <sup>O</sup> C |

|                                           | _                    | V -20V                | TA=25°C                               | (Note 2) |      | 0.1  |      |                    |

| Leakage Current                           | I <sub>0</sub>       | V <sub>R</sub> =20V   | TA=125°C                              | (Note 2) |      | 10   |      | nA                 |

| Breakdown Voltage                         | ₿V <sub>D</sub>      | I <sub>R</sub> =10µA  |                                       | -        | 6.25 |      | 7.25 | ٧                  |

| Maximum Diode Current                     | I <sub>F</sub> (MAX) |                       |                                       |          |      |      | 20   | mA                 |

| Junction Capacitance                      | CJ                   | V <sub>D</sub> =0V    |                                       | (Note 3) |      | 1    |      | pF                 |

- Matching of  $V_F$  is satisfied by  $\{V_{F(2)} V_{F(1)}\}$   $\{V_{F(MAX)}\}$  where  $V_{F(1)}$  and 1) V<sub>F(2)</sub> are any two forward voltages chosen from a population of like diodes on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction under test.

#### SMALL 10MA ZENER DIODE (EMITTER-BASE JUNCTION OF TRANSISTOR)

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE  $T_A$ =25 $^{\rm O}$ C (Unless otherwise noted)

| PARAMETER                                       | SYMBOL         | CONDITIONS            |          | MIN  | ТҮР  | MAX  | UNITS              |

|-------------------------------------------------|----------------|-----------------------|----------|------|------|------|--------------------|

|                                                 |                | I <sub>Z</sub> =lµA   | -        | 6.2  | 6.7  | 7.2  |                    |

|                                                 |                | I <sub>Z</sub> =10µA  |          | 6.25 | 6.75 | 7.25 |                    |

| Breakdown Voltage                               | v <sub>z</sub> | 1 <sub>Z</sub> ≐100µA | (Note 1) | 6.3  | 6.8  | 7.3  | ٧                  |

|                                                 |                | I <sub>Z</sub> =1mA   | (Note 1) | 6.4  | 6.9  | 7.4  | ]                  |

|                                                 |                | 1 <sub>Z</sub> =10mA  | (Note 1) | 7    | 7.5  | 8    |                    |

| Dynamic Impedance<br>(in the Breakdown Mode)    | RZ             | I <sub>Z</sub> =lmA   |          |      | 75   |      | Ω                  |

| Temperature Coefficient of Breakdown<br>Voltage | △VZ/△T         | IZ*1mA                |          |      | 2.4  |      | mV/ <sup>O</sup> C |

#### Notes:

Base-emitter breakdown, unlike base-collector breakdown, can be damaging to the transistor particularly for long breakdown duration at high current. Under these conditions,  $h_{f\bar{t}}$  degradation is inevitable; therefore,  $V_{z}$  is tested at  $1\mu A$  and  $10\mu A$  for each transistor. Operation at higher current has been fully characterized and is guaranteed by extrapolation. 1)

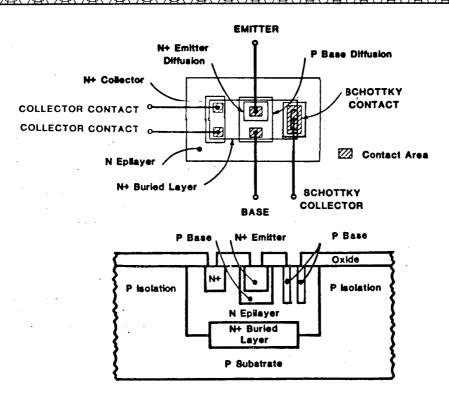

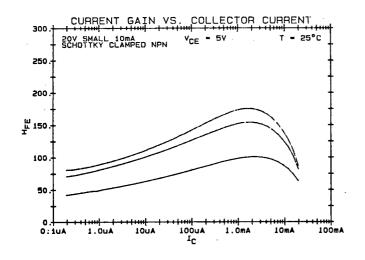

## 20V SCHOTTKY NPN TRANSISTOR 100ua Guard-Banded Schottky Diode

#### **GENERAL DESCRIPTION**

The Schottky NPN transistor is identical in size to the small NPN transistor on chip. It has a single N+ collector diffusion with two collector contacts in it. These contacts are used for the ohmic connection to the transistor's collector. In addition there is also a Schottky contact which is made directly to the N-type epilayer collector. This Schottky contact forms a Schottky diode which can be connected to the base of the transistor to form a Schottky clamped transistor or

can be used independently as a Schottky diode. The Schottky diode has a p-type ring in its periphery. The ring functions as a guard-band to reduce the leakage current in the diode.

#### **FEATURES**

Matched V<sub>BE</sub> and h<sub>FE</sub> Transistor Parameters

Matched Schottky Diode Parameters

Transistor Can be Schottky Clamped or Unclamped

TYPICAL APPLICATIONS

Non Saturating Logic Gates

High-Speed Circuitry

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE Ta=25°C'(Unless otherwise noted)

| PARAMETER                                    | SYMBOL                |                                     | CONDITION                          | 4S                                      | MIN  | TYP  | MAX  | UNITS            |

|----------------------------------------------|-----------------------|-------------------------------------|------------------------------------|-----------------------------------------|------|------|------|------------------|

| DC Current Gain                              | h <sub>FE</sub>       | I <sub>C</sub> =3mA                 | V <sub>CE</sub> ±5V                |                                         | 80   |      | 300  |                  |

| Matching of DC Current Gains                 | Δh <sub>FE</sub>      | I <sub>C</sub> =1mA                 | V <sub>CE</sub> =5V                | (Note 1)                                |      | ±5   | ±10  | %                |

| Temperature Coefficient of h <sub>FE</sub>   | Δh <sub>FE</sub> /ΔT  | I <sub>C</sub> =1mA                 |                                    | TA < 125°C                              |      | 0.5  |      |                  |

|                                              |                       |                                     | ~ oc0c                             | Transistor with<br>Clamp (Notes 2,3)    |      | 10   | 100  | nA               |

| Collector-Base Leakage Current               | Ī                     | V <sub>CB</sub> =20V                | 7 <sub>A</sub> =25 <sup>0</sup> C  | Transistor without<br>Clamp (Notes 2,3) |      | 0.01 | 0.1  | na<br>           |

| COFFECTOR - Base Leakage Current             | I <sub>CBO</sub>      | CB 201                              | 0.                                 | Transistor with Clamp (Notes 2,3)       |      | 0.1  | 1    | μА               |

|                                              |                       |                                     | T <sub>A</sub> =125 <sup>0</sup> C | Transistor without<br>Clamp (Notes 2,3) |      | 1    | 10   | nΑ               |

|                                              |                       |                                     |                                    | Transistor with Clamp (Notes 2,3)       |      | 0.5  | 5    | μА               |

| Callacton Emitton Lookago Cumment            | 1                     | V <sub>CE</sub> =20V                | TA=25°C                            | Transistor without<br>Clamp (Notes 2,3) |      | 0.2  | 2    | nA               |

| Collector-Emitter Leakage Current            | I <sub>CEO</sub>      | CE                                  |                                    | Transistor with<br>Clamp (Notes 2,3)    |      | 10   | 100  |                  |

|                                              |                       |                                     | T <sub>A</sub> =125 <sup>0</sup> C | Transistor without<br>Clamp (Notes 2,3) |      | 0.2  | 2    | μА               |

| Collector-Emitter Breakdown Voltage          | LVCEO                 |                                     |                                    | (Note 4)                                | 20   |      |      | ٧                |

| Collector-Base Breakdown Voltage             | вусво                 |                                     |                                    | (Note 4)                                | 20   |      |      | ٧                |

| Emitter-Base Breakdown Voltage               | BV <sub>EBO</sub>     | 1 <sub>E</sub> =10µA                |                                    |                                         | 6.25 |      | 7.25 | ٧                |

| Collector-Substrate Breakdown<br>Voltage     | BVCS                  |                                     |                                    | (Note 4)                                | 20   |      |      | ٧                |

| Base-Emitter Forward Voltage                 | V <sub>BE</sub>       | I <sub>E</sub>  = 1mA               | V <sub>CE</sub> =5V                | •                                       | 0.67 |      | 0.79 | v                |

| Matching of Base-Emitter Forward<br>Voltages | ΔV <sub>BE</sub>      | I <sub>E</sub>  =lmA                | V <sub>CE</sub> =5V                | (Note 5)                                |      | ±2   | ±6   | πV               |

| Temperature Coefficient of V <sub>BE</sub>   | ΔV <sub>BE</sub> /ΔT  | I <sub>E</sub>  = 1 mA              | V <sub>CE</sub> =5V                |                                         |      | -1.8 |      | mV/ <sup>O</sup> |

| Collector-Emitter Saturation                 | V <sub>CE</sub> (SAT) | I <sub>C</sub> =1mA                 | Transist                           | or with Clamp(Notes 3,6)                |      | 0.45 | 0.55 | V                |

| Voltage                                      | CE (SAI)              | (I <sub>C</sub> /I <sub>B</sub> )=1 | 0 Transist                         | or without Clamp<br>(Notes 3,6)         |      | 0.2  | 0.3  | '                |

| Maximum Collector Current                    | I <sub>C</sub> (MAX)  | P <sub>D</sub> (MAX)=2              | 200mW                              |                                         |      |      | 20   | πA               |

Information furnished by Hi-Tech Linear is believed to be accurate and reliable. However, no responsibility is assumed by HTL for its use, nor for any infringements of pattents or other rights which may result from its use. HTL reserves the right to make changes at any time without notice.

HISTECH LINEAR COMPONENT DAT

## SMALL SCHOTTKY CLAMPED NPN TRANSISTOR (CONTINUED)

| PARAMETER                       | SYMBOL          | CONDIT                     | IONS                 | •                             | MIN | ТҮР | MAX | UNITS |

|---------------------------------|-----------------|----------------------------|----------------------|-------------------------------|-----|-----|-----|-------|

|                                 | 1.              |                            | Transist             | or with Clamp                 |     | 300 |     | MHz   |

| Cutoff Frequency                | fT              | IC=5mA VCE=5               | Transist             | or without Clamp              |     | 400 |     | PUIZ  |

|                                 |                 |                            |                      | Transistor with<br>Clamp      |     | 3   |     |       |

| CA Time                         | _               | $(I_C/I_B)=10 R_B=75$      | 1 <sub>C</sub> =1mA  | Transistor with-<br>out Clamp |     | 5   |     | ns    |

| Storage Time                    | ¹s ·            | i d'CuBiero WBeig          |                      | Transistor with<br>Clamp      |     | 25  |     |       |

|                                 | <u> </u>        |                            | I <sub>C</sub> =10mA | Transistor with-<br>out Clamp |     | 80  |     | 1     |

| Emitter-Base Capacitance        | C <sub>EB</sub> | V <sub>EB</sub> =0V        |                      | (Note 7)                      |     | 0.8 |     | pF    |

|                                 |                 | Transi                     | stor with            | Clamp (Note 7)                |     | 1.5 |     | pF    |

| Collector-Base Capacitance      | ССВ             | V <sub>CB</sub> =0V Transi | stor witho           | ut Clamp(Note 7)              |     | 1   |     | pr    |

| Collector-Substrate Capacitance | c <sub>cs</sub> | V <sub>CS</sub> =0V        |                      | (Note 7)                      |     | 3   |     | pF    |

- $h_{FE}$  matching is satisfied by  $1-2 \left| \frac{h_{FE}(MAX)}{100\%} \right|$ 1)  $h_{\text{FE}(1)}$  and  $h_{\text{FE}(2)}$  are any two current gains chosen from a population of like transistors on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit 2) much higher leakage currents due to external surface leakage.

- In an array design, the MPN transistor can be used without the clamp, the transistor 3) and the diode can be separated.

- It is not advisable to operate Schottky transistors in the breakdown mode as 4) parameter degradation may occur.

- Matching of  $V_{BE}$  is satisfied by  $|V_{BE(2)}^{-1} V_{BE(1)}| < 2|\Delta V_{BE(MAX)}|$  where  $V_{BE(1)}$ 5) and  $V_{BE(2)}$  are any two base-emitter voltages chosen from a population of like transistors on chip.

- The base collector Schottky clamp prevents deep saturation of the transistor. 6)

- Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction 7) under test.

## HI-TECH LINEAR COMPONENT DATA SHEET

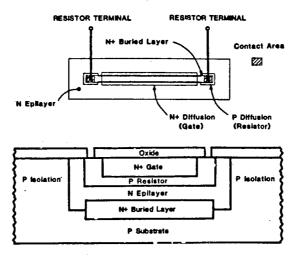

Layout and Cross-Section of Small 10mA Schottky Clamped NPN Transistor (Not to Scale)

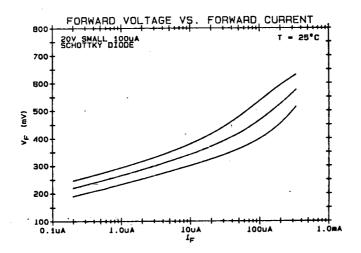

## SMALL 100µA SCHOTTKY DIODE (Note 1)

### ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE TA=25°C (Unless otherwise noted)

| PARAMETER                                 | SYMBOL               |                       | CONDITIONS                        |            | MIN  | ТҮР  | MAX  | UNITS |

|-------------------------------------------|----------------------|-----------------------|-----------------------------------|------------|------|------|------|-------|

|                                           |                      | I <sub>F</sub> =10µA  |                                   |            | 0.27 |      | 0.47 | V     |

| Forward Voltage Drop                      | V <sub>F</sub>       | I <sub>F</sub> =100μA |                                   |            | 0.42 |      | 0.62 | ] '   |

| Temperature Coefficient of V <sub>F</sub> | ΔV <sub>F</sub> /ΔT  | I <sub>F</sub> =100μA |                                   |            |      | -0.9 |      | mV/°C |

| Lankana Cumant                            | ,                    | V =20V                | T <sub>A</sub> =25 <sup>0</sup> C | (Note 2)   |      | 10   |      | nΑ    |

| Leakage Current                           | 10                   | V <sub>R</sub> =20V   | T <sub>A</sub> =125°C             | (Note 2)   |      | 1    |      | .µA   |

| Breakdown Voltage                         | BVD                  | <u> </u>              |                                   | ' (Note 3) | 20   |      |      | ٧     |

| Maximum Usable Current                    | I <sub>F (MAX)</sub> |                       |                                   |            |      |      | 0.5  | mA    |

- In an array design, the NPN transistor can be used without the clamp, the transistor and the diode can be separated.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- It is not advisable to operate Schottky diodes in the breakdown mode as parameter degradation may occur.

## histech Linear component data sheet

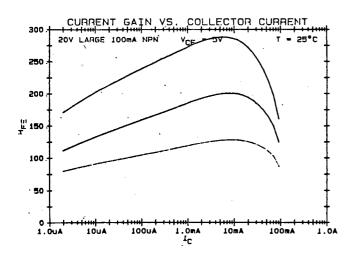

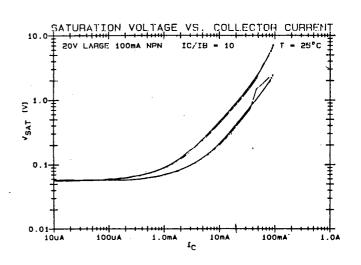

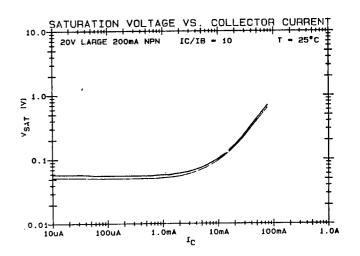

## 20V LARGE NPN TRANSISTOR 100ma Dual Emitter

#### **GENERAL DESCRIPTION**

The large 50mA (per emitter) dual-emitter NPN transistor has two emitters in a common base region with three seperate base contacts. The collector has two seperate N+ diffusion regions with two contacts in each. Normally, all collector contacts are connected together to reduce the series collector resistance as well as the saturation voltage, unless, the collector region is used as a crossunder, or layout considerations restrict the connection of the collector contacts. Also, both emitters should be connected together unless the design calls for a dual emitter transistor, in which case each emitter is capable of

handling half of the maximum transistor current. This transistor is available in two versions, with and without a deep N+ diffusion in the collector area. The deep N+ diffusion reduces the saturation voltage and increases the current handling capability.

#### **FEATURES**

Two Seperate Emitters for Increased Emitter Area and Emitter Efficiency

Quad Collector Contacts

Three Base Contacts

#### TYPICAL APPLICATIONS

Motor Drivers Relay Drivers Lamp and LED Drivers Voltage Regulators Power Darlingtons

## LARGE 50mA (PER EMITTER) DUAL-EMITTER NPN TRANSISTOR (EACH EMITTER)

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE T<sub>A</sub>=25.0C (Unless otherwise noted)

|                                              |                      | Α                     | •                                 |                                    |      |      |      |        |

|----------------------------------------------|----------------------|-----------------------|-----------------------------------|------------------------------------|------|------|------|--------|

| PARAMETER                                    | SYMBOL               |                       | CONDITION                         | S                                  | MIN  | ТҮР  | MAX  | UNIT   |

| DC Current Gain                              | h <sub>FE</sub>      | I <sub>C</sub> =50mA  | V <sub>CE</sub> =5V               | (Note 1)                           | 80   |      | 300  |        |

| Matching of DC Current Gains                 | ۵ħ <sub>FE</sub>     | 1 <sub>C</sub> =50mA  | V <sub>CE</sub> =5V               | (Note 2)                           |      | ±5   | ±10  | *      |

| Temperature Coefficient of h <sub>FE</sub>   | Δh <sub>FE</sub> /ΔT | I <sub>C</sub> =50mA  | -55°C < T                         | A < 125°C                          |      | 0.5  |      | %/     |

| Collector-Base Leakage Current               | ,                    | V -20V                | T <sub>A</sub> =25°C              | (Note 3)                           |      | 0.05 | 0.5  |        |

| Collector-base Leakage Current               | <sup>I</sup> CBO     | V <sub>CB</sub> =20V  | T <sub>A</sub> =125°C             | · (Note 3)                         |      | 5    | 50   | nA     |

| Callantan Faitten Laukan Command             | •                    | V -20V                | T <sub>A</sub> =25 <sup>0</sup> C | (Note 3)                           |      | 0.5  | 5    | nA     |

| Collector-Emitter Leakage Current            | ICEO                 | V <sub>CE</sub> =20V  | TA=125°C                          | (Note 3)                           |      | 0.5  | 5    | μA     |

| Collector-Emitter Breakdown Voltage          | LVCEO                | I <sub>C</sub> ≐1mA   |                                   |                                    | 20   |      |      | ٧      |

| Collector-Base Breakdown Voltage             | BA <sup>CBO</sup>    | I <sub>C</sub> =100µA |                                   | <del> </del>                       | 30   |      |      | V      |

| Emitter-Base Breakdown Voltage               | BV <sub>EBO</sub>    | I <sub>E</sub> =10μΑ  |                                   |                                    | 6.25 |      | 7.25 | V      |

| Collector-Substrate Breakdown<br>Voltage     | BV <sub>CS</sub>     | I <sub>C</sub> =10µA  |                                   |                                    | 20   |      |      | ٧      |

|                                              |                      |                       | I <sub>F</sub>  =5mA              | One Emitter                        | 0.68 |      | 0.8  |        |

| Base-Emitter Forward Voltage                 | v                    | V ~6V                 | ٠                                 | Two Emitters Connected in Parallel | 0.66 |      | 0.78 | ]<br>, |

| sase-Emitter Forward Voltage                 | V <sub>BE</sub>      | V <sub>CE</sub> =5V   | I <sub>F</sub>  =50mA             | One Emitter                        | 0.8  |      | 0.92 | ] '    |

|                                              |                      | -                     |                                   | Two Emitters Connected in Parallel | 0.74 |      | 0.86 |        |

| datching of Base-Emitter Forward<br>Voltages | ΔV <sub>BE</sub>     | I <sub>E</sub>  =5mA  | V <sub>CE</sub> =5V               | (Note 4)                           |      | ±2   | ±6   | mV     |

| Temperature Coefficient of V <sub>BE</sub>   | ΔV <sub>BE</sub> /ΔT | I <sub>F</sub>  =5mA  | V <sub>CE</sub> =5V               |                                    |      | -1.8 |      | mV/    |

Information furnished by Hi-Tech Linear is believed to be accurate and reliable. However, no responsibility is assumed by HTL for its use, nor for any infringements of pattents or other rights which may result from its use. HTL reserves the right to make changes at any time without notice.

## hi etech Linear Component Data

#### LARGE NPN TRANSISTOR (CONTINUED)

| PARAMETER                               | SYMBOL                |                                                              | CONDITIONS                               |                                                                  | MIN | ТҮР       | MAX  | UNITS |

|-----------------------------------------|-----------------------|--------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------|-----|-----------|------|-------|

|                                         | ·                     |                                                              |                                          | One Collector Contact (One Diffusion Region) (Note 5)            | ·   | 0.42      | 0.6  |       |

|                                         |                       |                                                              | One Emitter                              | Two Collector<br>Contacts<br>(Two Diffusion<br>Regions) (Note 5) |     | 0.2       | 0.4  |       |

|                                         | ·                     | I <sub>C</sub> =5mA                                          | . •                                      | Four Collector<br>Contacts<br>(Two Diffusion<br>Regions)         |     | 0.17      | 0.22 |       |

| •                                       | -                     | (Ĭ <sub>C</sub> /I <sub>B</sub> )=10                         | ·                                        | One Collector<br>Contact<br>(One Diffusion<br>Region) (Note 5)   |     | 0.25      | 0.35 |       |

| Collector-Emitter Saturation<br>Voltage | V <sub>CE</sub> (SAT) |                                                              | Two Emitters<br>Connected<br>in Parallel | Two Collector<br>Contacts<br>(Two Diffusion<br>Regions) (Note 5) |     | 0.12      | 0.22 | ٧     |

|                                         |                       |                                                              |                                          | Four Collector<br>Contacts<br>(Two Diffusion<br>Regions)         |     | 0.11      | 0.15 |       |

|                                         |                       |                                                              |                                          | One Collector<br>Contact<br>(One Diffusion<br>Region) (Note 5)   |     | 2.4       |      | ·     |

|                                         | -                     | I <sub>C</sub> =50mA<br>(I <sub>C</sub> /I <sub>B</sub> )=10 | Two Emitters<br>Connected<br>in Parallel | Two Collector<br>Contacts<br>(Two Diffusion<br>Regions) (Note 5) |     | 1         | 1.4  |       |

| .3                                      |                       |                                                              |                                          | Four Collector<br>Contacts<br>(Two Diffusion<br>Regions)         |     | 0.9       | 1.3  |       |

| Maximum Collector Current               | I <sub>C</sub> (MAX)  | PD(MAX)=50                                                   | OmW Two Emitt                            | ers Connected                                                    |     |           | 200  | mA .  |

| Cutoff Frequency                        | f <sub>T</sub>        | I <sub>C</sub> =50mA                                         | V <sub>CE</sub> =5V Two E                | imitters Connected arallel (Note 1)                              |     | 500       |      | MHz   |

| Storage Time                            | ₹S                    | (I <sub>C</sub> /I <sub>B</sub> )=10<br>R <sub>B</sub> =75Ω  | Two Emitters<br>Connected<br>in Parallel | I <sub>C</sub> =5mA<br>I <sub>C</sub> =50mA                      |     | 15<br>120 |      | ns    |

| Emitter-Ba - Capacitance                | - C <sub>EB</sub>     | V <sub>EB</sub> =OV                                          |                                          | (Note 6)                                                         |     | 2         |      | pF    |

| Collector-Base Capacitance              | ССВ                   | V <sub>CB</sub> =OV                                          |                                          | (Note 6)                                                         |     | 3         |      | pF    |

| Collector-Substrate Capacitance         | c <sub>cs</sub>       | V <sub>CS</sub> =0V                                          |                                          | (Note 6)                                                         |     | 6         |      | pF    |

#### Notes:

All collector contacts connected in parallel. 1)

h<sub>FE</sub> matching is satisfied by 2)

$^{h}_{\text{FE(1)}}$  and  $^{h}_{\text{FE(2)}}$  are any two current gains chosen from a population of like transistors on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- Matching of  $V_{BE}$  is satisfied by  $|V_{BE(2)} V_{BE(1)}| < 2|\Delta V_{BE(MAX)}|$  where  $V_{BE(1)}$ and VBE(2) are any two base-emitter voltages chosen from a population of like transistors on chip.

## tech linear component data shee

- It is not recommended to operate the transistor in the saturation mode when only one collector contact or two collector contacts on the same N+ diffusion region are used, since a high saturation voltage is inevitable, especially at increased collector currents. 5)

- 6) Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction under test.

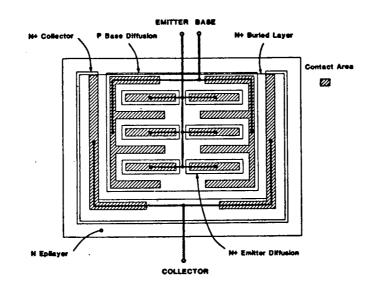

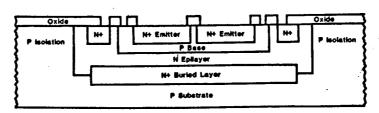

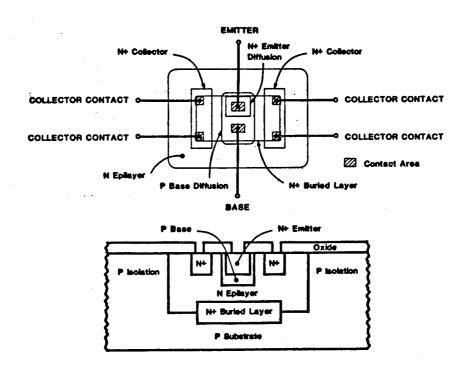

Layout and Cross-Section of Large 50mA (Per Emitter) Dual-Emitter NPN Transistor (Not to Scale)

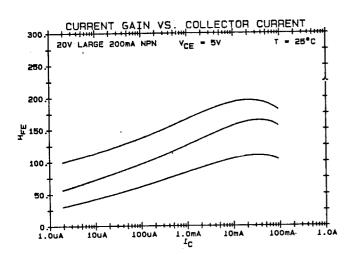

## **20V LARGE NPN TRANSISTOR** 200mA HEX EMITTER

#### **GENERAL DESCRIPTION**

The large 200mA NPN Transistor has a large emitter constructed with six fingers, in a double-comb shape, placed in a single base region. The base region has two base contacts in it and is serounded with a wrap-around N+ collector diffusion which also includes two collector contacts. This multiple contact structive permits a degree of flexibility in the layout process. However, best results are obtained when all collector contacts are connected together and all base contacts connected together respectively. This transistor is available in two versions, with and without a deep N+ diffusion in the collector region. The N+ diffusion reduces the saturation voltage and increases the current handling capability.

#### **FEATURES**

Six-finger Emitter Structure **Dual Base Contacts Dual Collector Contacts** TYPICAL APPLICATIONS Motor Drivers Relay Drivers Lamp and LED Drivers Voltage Regulators **Power Darlingtons**

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE T<sub>x</sub>=25°C (Unless otherwise noted)

| PARAMETEŔ                                    | SYMBOL                |                                      | CONDITIO                           | NS .                                  |          | MIN  | ТҮР  | MAX  | UNITS             |

|----------------------------------------------|-----------------------|--------------------------------------|------------------------------------|---------------------------------------|----------|------|------|------|-------------------|

| DC Current Gain                              | h <sub>FE</sub>       | 1 <sub>C</sub> =100mA                | V <sub>CE</sub> =5V                |                                       | (Note 1) | 80   |      | 300  |                   |

| Matching of DC Current Gains                 | Δħ <sub>FE</sub>      | I <sub>C</sub> =100mA                | V <sub>CE</sub> =5V                |                                       | (Note 2) |      | ±5   | ±10  | 2                 |

|                                              |                       |                                      | -55 <sup>0</sup> C <               | T <sub>A</sub> < 25 <sup>0</sup> C    |          |      | 0.5  |      |                   |

| Temperature Coefficient of h <sub>FE</sub>   | Δħ <sub>FE</sub> /ΔΤ  | I <sub>C</sub> =100mA                | 25 <sup>0</sup> C < T              |                                       |          |      | ±0.3 |      | %/ <sup>0</sup> ( |

|                                              |                       |                                      | 75 <sup>0</sup> C < T              | 4 < 125 <sup>0</sup> C                |          |      | -0.5 |      | <u> </u>          |

|                                              |                       | V - 20V                              | TA=25°C                            |                                       | (Note 3) |      | 0.05 | 0.5  | nA.               |

| Collector-Base Leakage Current               | I CBO                 | V <sub>CB</sub> =20V                 | T <sub>A</sub> =125°C              |                                       | (Note 3) |      | 5    | 50   | ] IIA             |

|                                              |                       |                                      | TA=25°C                            |                                       | (Note 3) |      | 0.5  | 5    | nA                |

| Collector-Emitter Leakage Current            | I <sub>CEO</sub>      | V <sub>CE</sub> =20V                 | T <sub>Á</sub> =125 <sup>0</sup> C |                                       | (Note 3) |      | 1    | 10   | μA                |

| Collector-Emitter Breakdown Voltage          | LVCEO                 | I <sub>C</sub> =1mA                  |                                    |                                       |          | 20   |      |      | ٧                 |

| Collector-Base Breakdown Voltage             | вусво                 | I <sub>C</sub> =100µA                | •                                  | · .                                   |          | 30   |      |      | ٧                 |

| Emitter-Base Breakdown Voltage               | BV <sub>EBO</sub>     | I_E=10μA                             | •                                  |                                       |          | 6.25 |      | 7.25 | ٧                 |

| Collector-Substrate Breakdown<br>Voltage     | BVCS                  | 1 <sub>C</sub> =10μA                 |                                    |                                       |          | 20   |      |      | ٧                 |

|                                              |                       |                                      | I <sub>E</sub>  =10m/              | 4                                     |          | 0.65 |      | 0.77 | V                 |

| Base-Emitter Forward Voltage                 | V <sub>BE</sub>       | V <sub>CE</sub> =5V                  | I <sub>E</sub>   = 100r            | πA                                    |          | 0.73 |      | 0.85 | ] "               |

| Matching of Base-Emitter Forward<br>Voltages | ΔVBE                  | I <sub>E</sub>   = 10mA              | V <sub>CE</sub> =5V                |                                       | (Note 4) |      | ±2   | ±6   | mV                |

| Temperature Coefficient of V <sub>RF</sub>   | ΔV <sub>BE</sub> /ΔT  | !I <sub>E</sub>                      | V <sub>CE</sub> =5V                |                                       |          |      | -1.8 |      | my/º              |

|                                              |                       |                                      |                                    | One Collector                         |          |      | 0.16 | 0.24 |                   |

|                                              |                       |                                      | I <sub>C</sub> =10mA               | Two Collector<br>(One Diffusion       | Contacts |      | 0.12 | 0.17 | 1                 |

| Collector-Emitter Saturation<br>Voltage      | V <sub>CE</sub> (SAT) | (I <sub>C</sub> /I <sub>B</sub> )=10 |                                    | One Collector<br>(One Diffusion       | Contact  |      | 1.4  | 2    | 7 "               |

|                                              |                       |                                      | I <sub>C</sub> =100mA              | Two Collector<br>(One Diffusion       | Contacts |      | 0.9  | 1.2  |                   |

| Maximum Collector Current                    | I <sub>C(MAX)</sub>   | P <sub>D(MAX)</sub> =70              | OmW                                |                                       |          |      |      | 300  | mА                |

| Cutoff Frequency                             | f <sub>T</sub>        | I <sub>C</sub> =50mA                 | V <sub>CE</sub> =5V                | · · · · · · · · · · · · · · · · · · · |          | ·    | 500  |      | MHz               |

Information furnished by HI-Tech Linear is believed to be accurate and reliable. However, no responsibility is assumed by HTL for its use, nor for any infringements of pattents or other rights which may result from its use. HTL reserves the right to make changes at any time without notice.

## ECH LINEAR SCOMPONENT DATAS SHEETS

#### LARGE NPN TRANSISTOR (CONTINUED)

| PARAMETER                       | SYMBOL          | CI                                   | OITIDMO | NS                    |       | :  | MIN | ТҮР  | MAX         | UNITS |

|---------------------------------|-----------------|--------------------------------------|---------|-----------------------|-------|----|-----|------|-------------|-------|

|                                 |                 | / / / / / / /                        | 0 75-   | I <sub>C</sub> =10mA  | , ·   | -  |     | 30   | <del></del> |       |

| Storage Time                    | ¹s s            | (I <sub>C</sub> /I <sub>B</sub> )=10 | KB=/51  | I <sub>C</sub> =100mA |       |    |     | 150  |             | ns    |

| Emitter-Base Capacitance        | CEB             | V <sub>EB</sub> *0V                  |         |                       | (Note | 5) |     | 13.5 |             | pF    |

| Collector-Base Capacitance      | ССВ             | V <sub>CB</sub> =0V                  | .,      |                       | (Note | 5) |     | 9    |             | рF    |

| Collector-Substrate Capacitance | c <sub>ćs</sub> | V <sub>CS</sub> =0V                  |         |                       | (Note | 5) |     | 16.5 |             | pF    |

#### Notes:

All collector contacts connected in parallel.

- $1-2\left|\frac{^{\Delta h}FE\,(MAX)}{100\%}\right| < \frac{^{h}FE\,(2)}{^{h}FE\,(1)} < 1+2\left|\frac{^{\Delta h}FE\,(MAX)}{100\%}\right| \text{ where}$ h<sub>FE</sub> matching is satisfied by 2)  $h_{\text{FE}(1)}$  and  $h_{\text{FE}(2)}$  are any two current gains chosen from a population of like transistors on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- Matching of  $V_{BE}$  is satisfied by  $\|V_{BE(2)}^{-V}\|_{BE(1)}\| < 2\|\Delta V_{BE(MAX)}\|$  where  $V_{BE(1)}$  and  $V_{BE(2)}$  are any two mase-emitter voltages chosen from a population of like transistors on chip.

- Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of 1pF for each bonding pad which is related to the specific junction under test.

Layout and Cross-Section of Large 200mA NPN Transistor (Not to Scale)

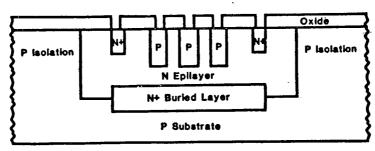

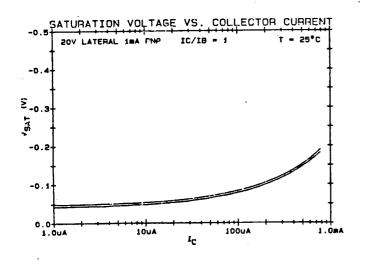

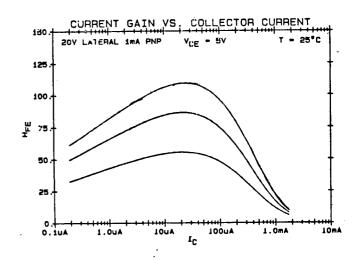

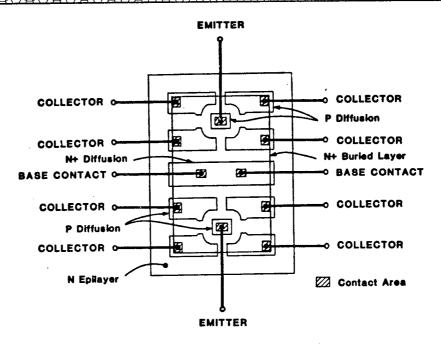

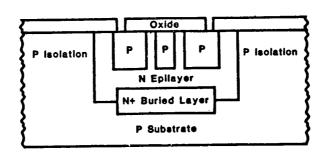

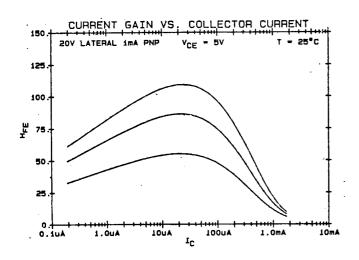

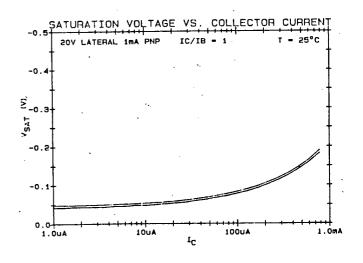

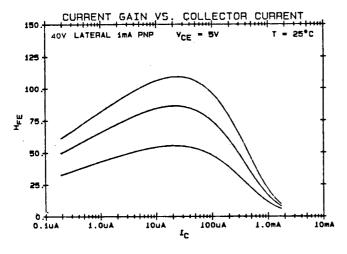

## **20V LATERAL PNP TRANSISTOR** 1mA QUAD COLLECTOR

#### **GENERAL DESCRIPTION**

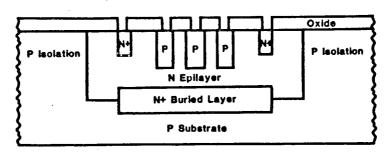

The lateral PNP transistor has an oval-shaped, P-type emitter, surrounded by four P-type collector diffusions in a single epi base region. The base is made with an N+ diffusion with two base contacts in it. All four collectors should be connected together when a single collector transistor is required. When current ratios are important, such as for multiple current sources, the collectors can be used individually. Unused collectors must be connected to the substrate or any other potential that will ensure that the transistor does not saturate.

#### **FEATURES**

**Quad Collectors** Matched  $v_{\mbox{\footnotesize{BE}}}$  and  $h_{\mbox{\footnotesize{FE}}}$  Transistor Parameters TYPICAL APPLICATIONS **Current Sources Active Loads** Level Shifters Biasing Stages **Amplifiers**

#### O.25mA (PER COLLECTOR) QUAD-COLLECTOR LATERAL PNP TRANSISTOR (EACH COLLECTOR)

ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE TA=25°C (Unless otherwise noted)

| PARAMETER                                    | SYMBOL               | 1                      | CONDITIONS -                  |                                                        | MIN   | ТҮР   | MAX   | UNITS              |

|----------------------------------------------|----------------------|------------------------|-------------------------------|--------------------------------------------------------|-------|-------|-------|--------------------|

| FARANCIER                                    | 311000               |                        | T CONDITIONS                  |                                                        | FILM  | 111   | FIAA  | 01113              |

|                                              |                      |                        | I <sub>C</sub> =-25μA         | One Collector<br>(Note 1)                              | 5     |       | 37.5  |                    |

| DC Current Gain                              | h <sub>FE</sub>      | V <sub>CE</sub> =-5V   | Ic(TOTAL)*-50µA               | Two Collectors<br>Connected<br>in Parallel<br>(Note 1) | 10    |       | 75    |                    |

|                                              |                      |                        | I <sub>C(TOTAL)</sub> =-100µA | Four Collectors<br>Connected<br>in Parallel            | 20    | -     | 150   |                    |

| Matching of DC Current Gains                 | ۵h <sub>FE</sub>     | 1 <sub>C</sub> =-100µA | V <sub>CE</sub> =-5V          | (Note 2)                                               |       | ±5    | ±15   | *                  |

| Temperature Coefficient of h <sub>FE</sub>   | Δh <sub>FE</sub> /ΔT | I <sub>C</sub> =-100μA | -55°C < T <sub>A</sub> < 125  | °c                                                     |       | -0.1  |       | 1/°C               |

| Collector-Base Leakage Current               | 1 =                  | V <sub>CB</sub> =-20V  | TA=25°C                       | (Note 3)                                               |       | -0.01 | -0.1  | nA                 |

|                                              | I CBO                | CB204                  | TA=125°C                      | (Note 3)                                               |       | -1    | -10   | 110                |

| Collector-Emitter Leakage Current            |                      | V <sub>CE</sub> =-20V  | TA=25°C                       | (Note 3)                                               |       | -0.05 | -0.5  | nA                 |

| Corrector - Emitter Leakage Current          | ICEO                 | CE                     | TA=125°C                      | (Note 3)                                               |       | -25   | -250  | ''^                |

| Collector-Emitter Breakdown Voltage          | BVCEO                | I <sub>C</sub> =-100μA |                               |                                                        | -20   |       |       | ٧                  |

| Collector-Base Breakdown Voltage             | вусво                | 1 <sub>C</sub> =-100μA |                               |                                                        | -30   |       |       | ٧                  |

| Emitter-Base Breakdown Voltage               | BV <sub>EBO</sub>    | 1 <sub>E</sub> =-100μA |                               |                                                        | -30   |       |       | ٧                  |

| Base-Substrate Breakdown<br>Voltage          | BVBS                 | I <sub>B</sub> =10μA   |                               |                                                        | 20    |       |       | ٧                  |

| Base-Emitter Forward Voltage                 | V <sub>BE</sub>      | 1 <sub>E</sub> =100μA  | V <sub>CE</sub> =-5V          |                                                        | -0.61 |       | -0.73 | ٧                  |

| Matching of Base-Emitter Forward<br>Voltages | ΔV <sub>BE</sub>     | 1 <sub>E</sub> =100µA  | V <sub>CE</sub> =-5V          | (Note 4)                                               |       | ±2    | ±6    | mV                 |

| Temperature Coefficient of V <sub>BE</sub>   | ΔV <sub>BE</sub> /ΔT | I <sub>E</sub> =100µA  | V <sub>CE</sub> =-5V          |                                                        |       | 1.8   |       | mV/ <sup>O</sup> C |

Information furnished by Hi-Tech Linear is believed to be accurate and reliable. However, no responsibility is assumed by HTL for its use, nor for any infringements of pattents or other rights which may result from its use. HTL reserves the right to make changes at any time without notice.

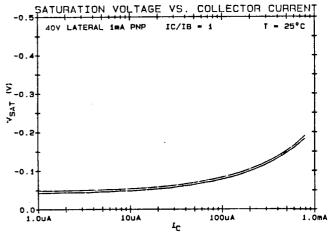

#### QUAD-COLLECTOR LATERAL PNP TRANSISTOR (CONTINUED)

| PARAMETER                               | SYMBOL                | CONDITION                                    | S                                                                                                                                                                                                                 | MIN | ТҮР  | MAX   | UNITS |

|-----------------------------------------|-----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|-------|

| Collector-Emitter Saturation<br>Voltage | V <sub>CE</sub> (SAT) | (I <sub>C(TOTAL)</sub> /I <sub>B</sub> )=1   | I <sub>C</sub> =-25µA  One Collector (Notes 1,5)  I <sub>C</sub> (TOTAL) =-50µA  Two Collectors Connected in Parallel (Notes 1,5)  I <sub>C</sub> (TOTAL) =-100µA  Four Collectors Connected in Parallel (Note 5) |     | -0.1 | -0.18 | ٧     |

| Maximum Usable Collector Current        | I <sub>C(MAX)</sub>   | (Per Collector)                              |                                                                                                                                                                                                                   |     |      | -0,5  | mA    |

| Cutoff Frequency                        | f <sub>T</sub>        | 1 <sub>C(TOTAL)</sub> =-100µA V <sub>C</sub> | Four Collectors<br>E=-5V Connected<br>in Parallel                                                                                                                                                                 |     | 5    |       | MHz   |

|                                         |                       | (I <sub>C(TOTAL)</sub> /I <sub>B</sub> )=1   | I <sub>C</sub> (TOTAL)=-100µA<br>Four Collectors<br>Connected in<br>Parallel                                                                                                                                      |     | 75   |       |       |

| Storage Time                            | <sup>*</sup> S        | R <sub>B</sub> ≖750Ω                         | IC(TOTAL)=-lmA Four Collectors Connected in Parallel                                                                                                                                                              |     | 130  |       | ns    |

| Emitter-Base Capacitance                | CEB                   | V <sub>EB</sub> =OV                          | (Note 6)                                                                                                                                                                                                          |     | 0.2  |       | pF    |

| Collector-Base Capacitance              | ССВ                   | V <sub>CB</sub> =OV                          | (Note 6)                                                                                                                                                                                                          |     | 0.4  |       | pF    |

| Base-Substrate Capacitance              | c <sub>BS</sub>       | V <sub>BS</sub> =0V                          | (Note 6)                                                                                                                                                                                                          |     | 3.5  |       | pF    |

#### Notes:

1) With the other collectors grounded.

$h_{FE}$  matching is satisfied by  $1-2\left|\frac{\Delta h_{FE}(MAX)}{100\%}\right| < \frac{h_{FE}(2)}{h_{FE}(1)} < 1+2\left|\frac{\Delta h_{FE}(MAX)}{100\%}\right|$  where  $\mathbf{h}_{\mathsf{FE}(1)}$  and  $\mathbf{h}_{\mathsf{FE}(2)}$  are any two current gains chosen from a population of like transistors on chip.

- Device leakage current is specified. Mishandled packaged devices may exhibit much higher leakage currents due to external surface leakage.

- Matching of  $V_{BE}$  is satisfied by  $\|V_{BE(2)} V_{BE(1)}\| \le 2\|\Delta V_{BE(MAX)}\|$  where  $V_{BE(1)}$  and  $V_{BE(2)}$  are any two base-emitter voltages chosen from a population of like transistors on chip.

- It is not advisable to operate the lateral PNP transistor in the saturation mode since the parasitic vertical substrate transistor (related to the lateral transistor) becomes heavily active.

- Junction capacitance is specified. An average capacitance of 0.5pF must be added to include the effect of the package. Also included must be a capacitance of lpF for each bonding pad which is related to the specific junction under test.

## ECH LINEAR COMPONENT DATA SHEE

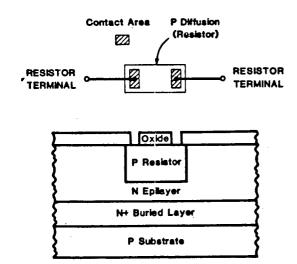

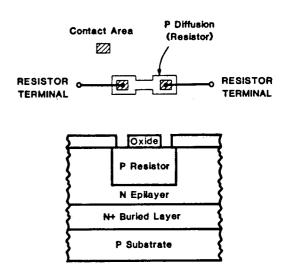

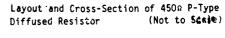

Layout and Cross-Section of O.25mA (Per Collector) Quad-Collector Lateral PNP Transistor (Not to Scale)

#### LATERAL PHP DIODE (EMITTER-BASE JUNCTION OF TRANSISTOR)

## ELECTRICAL CHARACTERISTICS AT AMBIENT TEMPERATURE $T_A$ =25 $^{\rm O}$ C (Unless otherwise noted)

| PARAMETER                                 | SYMBOL              |                       | CONDITIONS                        |          | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|---------------------|-----------------------|-----------------------------------|----------|------|------|------|-------|

|                                           |                     | I <sub>F</sub> =100µA |                                   |          | 0.61 |      | 0.73 |       |

| Forward Voltage Drop                      | ٧ <sub>F</sub>      | I <sub>F</sub> =]mA   |                                   |          | 0.73 |      | 0.85 | ٧     |

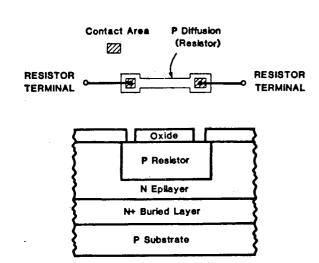

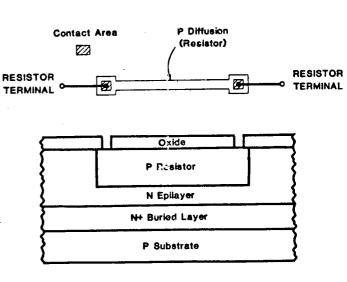

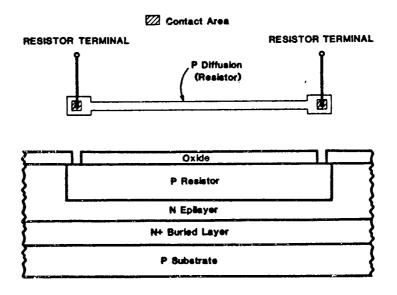

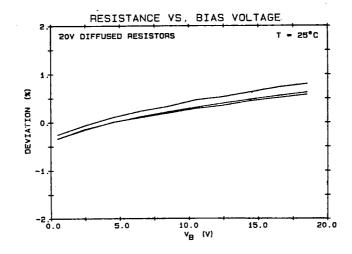

|                                           |                     | I <sub>F</sub> =10mA  |                                   | (Note 1) |      | 1.1  |      |       |