# **DL6000<sup>™</sup> Family**

## Fast Field Programmable Gate Array™

#### **Features**

- System Clock Rates Up To 200 MHz

- 9,000 to 105,000 Usable Gates

- Synchronous Dual-port RAM with 8 ns Access Time

- 2 Analog PLLs For Clock Multiplication, Division and Locking

- LV-TTL and GTL Interface Levels

- Up to 10 LVDS Compatible Inputs

- Up to 10 Differential or Single-Ended LV-PECL Inputs

- 1.3 ns Input Register Setup Time

- 33/66 MHz PCI Compatible

- Partial Reconfiguration

- 10 Clock Trees with 150 ps Skew

- 3.3 Volt Operation

- 5 Volt Tolerant I/O

- Patented Active Repeater Architecture

- In-System Reprogrammability (ISP)

- JTAG Support

- Output Slew Rate Control

- Fully Automatic Implementation With DynaTool<sup>TM</sup>

### **Applications Examples**

- Telecommunication

- Datacommunication

- High Speed Graphics

- DSP

- ASIC Emulation

### Introduction

The DL6000 is DynaChip's second generation Fast Field Programmable Gate Array family. Built on a deep sub-micron CMOS process, this family supports applications with system clock rates up to 200 MHz.

The DL6000 family features DynaChip's patented Active Repeater Architecture. This results in extremely short routing delays allowing these devices to run at system frequencies well above conventional FPGAs.

To support the fast data rates of high-speed applications, every I/O pin can be programmed to LV-TTL or GTL interface levels.

DL6000 family devices contain synchronous RAM with 8 ns access time. These flexible RAM structures operate in true dual and single port modes and are ideal for applications that require fast access to memory.

High operating frequencies, on-chip RAM, fast I/O and PCI compatibility make these devices ideal for high-speed telecommunications, datacommunications, graphics and emulation applications.

The DL6000 features SRAM-based programming allowing the devices to be configured in-circuit and reprogrammed on-the-fly. They support dynamic single-block reconfiguration enabling a portion of the device to be reprogrammed without affecting operation of the remaining logic.

| Device | Gates   | Logic<br>Blocks | Max User<br>RAM Bits | Flip Flops | Clock Trees | I/O Blocks |

|--------|---------|-----------------|----------------------|------------|-------------|------------|

| DL6009 | 9,000   | 256             | 8,192                | 768        | 10          | 128        |

| DL6020 | 20,000  | 576             | 18,432               | 1,536      | 10          | 192        |

| DL6035 | 35,000  | 1,024           | 32,768               | 2,560      | 10          | 254        |

| DL6055 | 55,000  | 1,600           | 51,200               | 3,840      | 10          | 320        |

| DL6080 | 80,000  | 2,304           | 73,728               | 5,376      | 10          | 384        |

| DL6105 | 105,000 | 3,136           | 100,352              | 7,168      | 10          | 448        |

Table 1: DL6000 Family

Datasheet September 1998

## **Table of Contents**

| Features                                             |                 |

|------------------------------------------------------|-----------------|

| Applications Examples                                | . 1             |

| Introduction                                         | . 1             |

| Performance Examples                                 |                 |

| High Performance Active Repeater Technology          |                 |

| Top-Level Architecture                               | . 5             |

| Routing Architecture                                 | . 5             |

| Input/Output Blocks                                  |                 |

| LVDS                                                 |                 |

| Logic Block                                          |                 |

| RAM                                                  |                 |

| Clock Distribution.                                  |                 |

| Phase Lock Loops                                     |                 |

| Power Consumption                                    |                 |

| Configuration                                        |                 |

| Configuration Modes                                  |                 |

| Serial Configuration Modes                           |                 |

| Microprocessor Configuration Modes                   |                 |

| Dynamic Reconfiguration Using Full Chip Reset        |                 |

| Partial Reprogramming                                | 21              |

| Readback                                             | 22              |

| Configuration Clock Frequencies                      | 22              |

| Mode Pin Settings                                    | 22              |

| Flip Flop Initialization                             | 23              |

| Configuration Schematics                             | $\frac{-2}{23}$ |

| Serial PROM Configuration Mode                       |                 |

| Microprocessor Configuration Mode                    |                 |

| Programming Chains                                   |                 |

| Bitstream Size                                       | 26              |

| Configuration Pins                                   |                 |

| JTAG°                                                |                 |

| Product Specifications                               |                 |

| Maximum Ratings                                      |                 |

| Operating Conditions                                 |                 |

| DC Characteristics Over Operating Conditions         |                 |

| Clock and Set/Reset Buffer Switching Characteristics | 32              |

| Clock and Set/Reset Buffer Switching Characteristics | 34              |

| Three-state Buffer Characteristics                   | 34              |

| Logic Block Switching Characteristics                | 36              |

| RAM Switching Characteristics                        | 37              |

| Programmable Interconnect Characteristics            | 38              |

| Pin Description                                      |                 |

| 352-pin SBGA - DL6035                                | 39              |

| 208-pin QFP - DL6035.                                |                 |

| 352-pin SBGA - DL6020                                |                 |

| 352-pin SBGA - DL6009                                |                 |

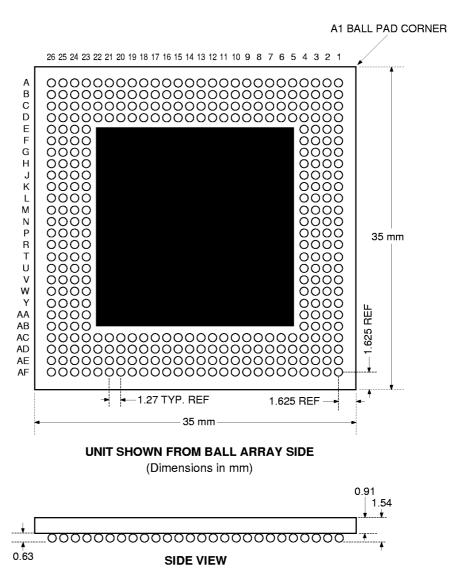

| Package Drawings                                     |                 |

| 352-pin SBGA                                         |                 |

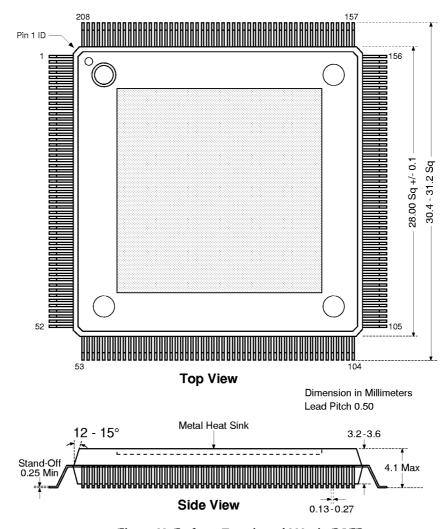

| 208-pin Thermal Enhanced PQFP (PQ208)                |                 |

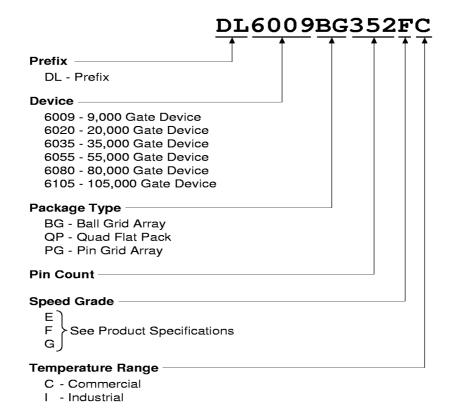

| Ordering Information                                 |                 |

| Oracinia miomianom                                   | 55              |

## Performance Examples

The DL6000 family with DynaChip's patented Active Repeater Architecture supports high-speed applications with clock rates up to 200 MHz.

The following table shows the performance of various size functions implemented in the DL6035\*.

| Circuit                                       | DL6035 - G | Logic Block Count |

|-----------------------------------------------|------------|-------------------|

| 8-bit Fully Synchronous, Loadable Up Counter  | 145 MHz    | 9                 |

| 16-bit Fully Synchronous, Loadable Up Counter | 140 MHz    | 20                |

| 32-bit Fully Synchronous, Loadable Up Counter | 125 MHz    | 42                |

| 64-bit Fully Synchronous, Loadable Up Counter | 100 MHz    | 86                |

| 32x32 RAM-based FIFO                          | 100 MHz    | 49                |

| 128x32 RAM-based FIFO                         | 80 MHz     | 145               |

| 64-bit Shift Register                         | 160 MHz    | 64                |

| Maximum chip-to-chip performance**            | 250 MHz    | -                 |

**Table 2: Performance of Various Applications**

## High Performance Active Repeater Technology

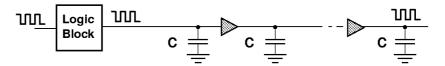

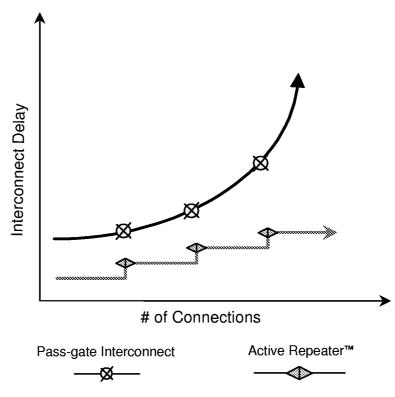

The enabling technology behind DynaChip's Fast Field Programmable Gate Arrays is the Active Repeater. Conventional FPGA devices use pass gates to create programmable interconnections. These pass gates act like a series of resistors with distributed capacitance to ground. Nets formed out of these pass gates slow down dramatically as the number of programmable connections increases.

This results in long, unpredictable delays, especially for nets that have to travel a long distance or drive a large number of loads.

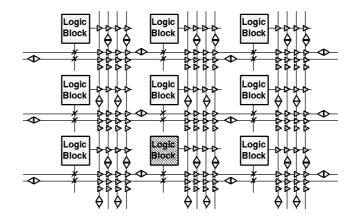

In contrast, DynaChip uses Active Repeaters to create programmable interconnections. As shown in figure 1, these repeaters buffer the signal at every interconnection point and isolate the capacitance of the rest of the net.

The result is fast, predictable performance even for long, high fanout nets.

Figure 1: DynaChip's Active Interconnect

<sup>\*</sup> Based on -G speed grade over commercial voltage and temperature range.

<sup>\*\*</sup> With 10 pF load and fast slew rate.

In FPGA devices that use pass-gate based interconnect, net delays increase quadratically with the number of programmable interconnect points, as shown in figure 2. This results in a performance bottleneck that is especially troublesome for nets that have to travel a long distance or drive a large number of loads.

In devices that use Active Repeaters for interconnect, net delays are linear and are not affected by fanout. The result is much higher performance and greater predictability.

Figure 2: Active Repeater<sup>TM</sup> vs. Pass Gate Delays

Page 4 DynaChip

### **Top-Level Architecture**

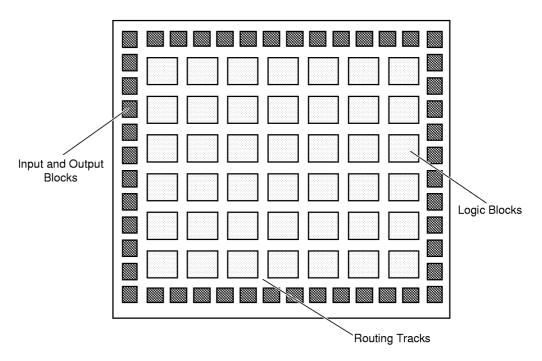

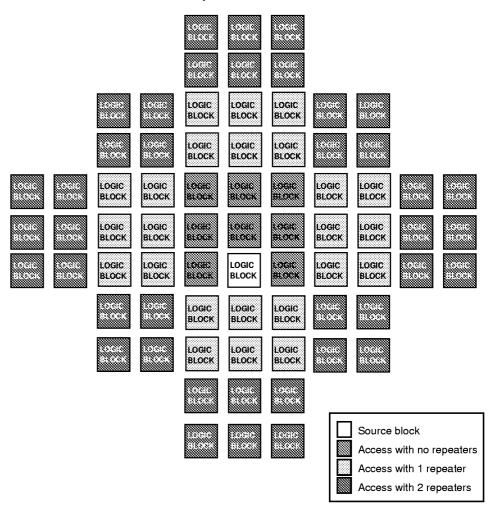

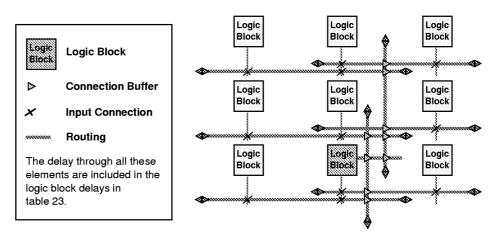

At the very top level, DynaChip devices look a lot like conventional FPGA devices. As shown in figure 3, input/output blocks surround the edges of the device, an array of logic blocks fill the interior and routing tracks are distributed between the rows and columns of logic blocks.

The difference in DynaChip's architecture lies in the routing resources.

Figure 3: High Level View of Architecture

### **Routing Architecture**

DynaChip's architecture is optimized for Active Repeater technology.

As shown in figure 4, interconnect resources consist of a series of vertical and horizontal wires that make up a routing region. Buffers that drive these wires can be turned on and off to create the required connections. Since every buffer drives a fixed load, it has been carefully optimized to provide maximum performance. The fixed load nature of the interconnect results in completely predictable performance since the delay through the buffer is fixed.

Routing regions are connected with Active Repeaters. After passing through an Active Repeater, signals are available throughout the next routing region.

In the DL6000 family, each routing region is 3 columns wide by 3 rows tall. The location of the Active Repeaters are staggered so that each logic block has its own 3 x 3 region.

Each vertical line shown represents 9 actual vertical lines Each horizontal line shown represents 15 actual horizontal lines

#### Figure 4: Routing Architecture

This architecture results in completely deterministic performance within a routing region. The logic block delays specified in this datasheet include the delay of the connection buffers and all the routing within a region (refer to table 24 for logic block delays).

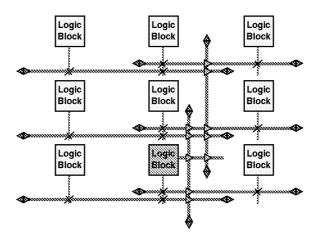

As shown in figure 5, this architecture allows a logic block to drive all 9 blocks in the 3 column by 3 row routing region with no additional routing delays. This allows even high fanout nets to have extremely high performance.

Figure 5: Routing Region With No Interconnect Delay

For signals that drive blocks in the next region, the fixed delay through an Active Repeater is added to the logic block delay. These Active Repeater delays are the only routing delays in the device and their performance is completely specified in this datasheet (refer to table 27 for Active Repeater delays).

Page 6 DynaChip

As shown in figure 6, a logic block output can drive 33 logic blocks with just 1 Active Repeater delay. This allows structures with up to 660 gates of logic or 1,056 bits of RAM to be implemented with just 800 ps routing delay. With 2 Active Repeater delays, a logic block output can drive 73 logic blocks. This allows up to 1,460 gates of logic or 2,336 bits of RAM with just 1.6 ns routing delay. All routing delays in the device are fixed and are not affected by the fanout on the net.

Figure 6: Logic Block Reached With 2 Repeaters

### Input/Output Blocks

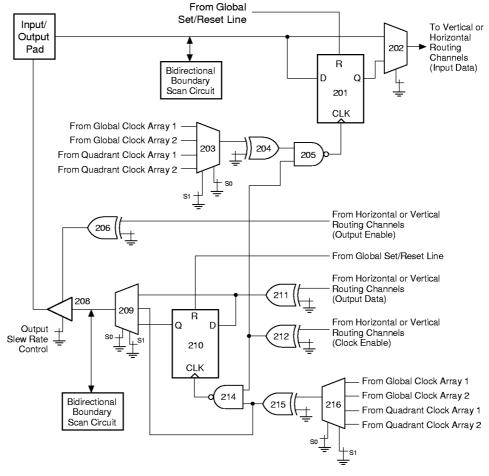

Every input/output block in the DL6000 can be independently set to TTL and GTL interface levels. The 10 clock inputs can also be set to single-ended or differential LV-PECL levels. When set to differential LV-PECL, the inputs are compatible with LVDS. If any of these 10 inputs are not used for clock signals, they can be used as general purpose inputs.

When set to TTL mode, input/output blocks are 100% compliant with 33Mhz and 66 MHz PCI busses.

Each input/output block can be configured for input, output or bi-directional signals. Each block has 2 flip flops that can be used to register input and output signals. Each flip flop has a clock enable input. Clock signals for flip flops in the input/output blocks are sourced from either of the 2 global clock pins and either of the 2 quadrant clock pins for that region.

Each output has individual slew rate control and 3-state capability. The 3-state enable for each output can be controlled individually.

Each input/output block contains dedicated JTAG Boundary Scan logic compatible with IEEE specifications.

Figure 7: Input/Output Block

Page 8 DynaChip

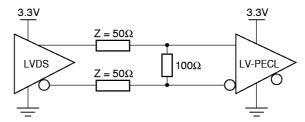

### **LVDS**

When set to differential LV-PECL levels, the 10 clock inputs can interface to LVDS levels using a 100 ohm shunt resistor as shown in the following figure. If these inputs are not used for clock signals, they can be used as general purpose inputs.

Figure 8: Interfacing LVDS to LV-PECL

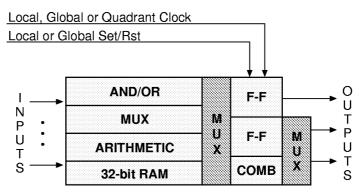

### Logic Block

The logic block in the DL6000 is extremely flexible and can implement a wide variety of functions. Each block has 18 inputs. One of the inputs is dedicated for clocking and one is for a set or reset signal. The remaining 16 are general purpose inputs to the logic block.

Each logic block contains combinatorial logic, RAM and two flip flops. The combinatorial section contains flexible building blocks optimized for high utilization. Structures like multiplexers, AND/OR gates, comparators and arithmetic functions are automatically mapped to these resources by the DynaChip Development System.

A multiplexer allows the outputs of the combinatorial logic to exit the block directly or to serve as inputs to the two flip flops.

Figure 9: Logic Block

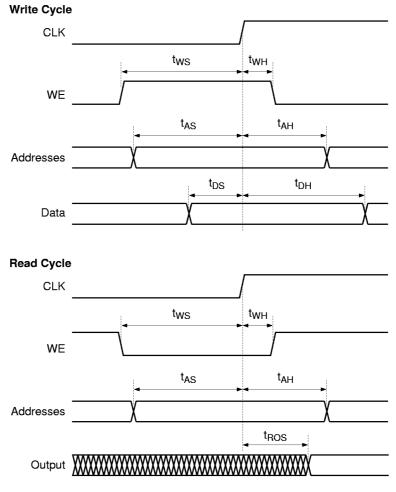

Figure 10 shows a detailed diagram of the logic block in the DL6000.

The logic block contains sections that are optimized for AND/OR logic, multiplexers, arithmetic logic and RAM. All logic block inputs have polarity control allowing signals to be inverted as they enter the block.

Each logic block contains two storage elements that can be configured as D-type or T (toggle) flip flops. The flip flops share a common clock that can be driven by the

device's global or quadrant clocks or by local interconnect. The clock input to each logic block has polarity control allowing the flip flops to be triggered from either clock edge.

The flip flops also share a common set/reset signal that is driven by the device's global set/reset or by local interconnect. Each flip flop can be configured to have either a set or reset capability. The set/reset input to each logic block has polarity control allowing active high or active low operation.

Each logic block has 3 outputs that are driven by the combinatorial logic, RAM or flip flops.

Page 10 DynaChip

Figure 10: Logic Block Resources

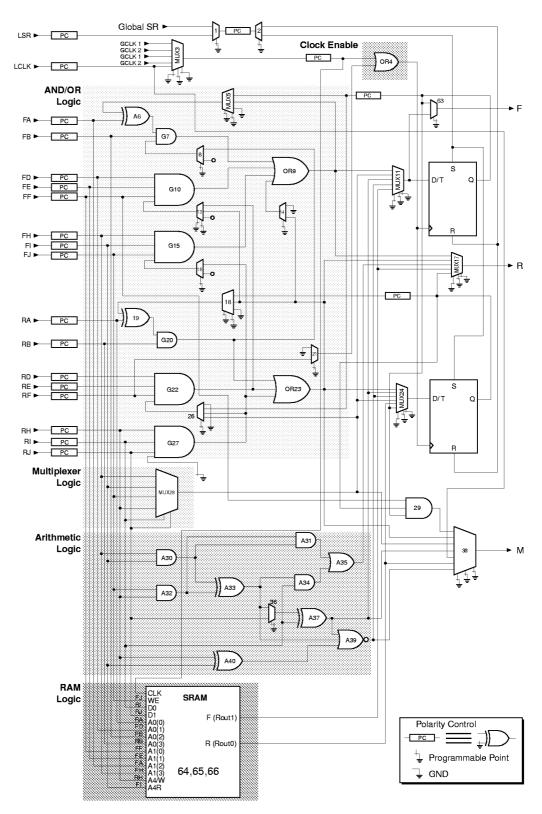

### **RAM**

Each logic block in DL6000 family devices contain a 32-bit fully synchronous configurable RAM. The RAM can be configured as a 32x1 dual port RAM, a 32x1 single port RAM or two 16x1 RAMs with independent data and addresses. The RAM is "self-timed" which makes both read and write operations fully synchronous. The user only needs to be concerned with maintaining setup and hold times for all inputs with respect to the clock. This includes the WE, data and address inputs. There is no need for standard RAM timing parameters such as 'WE pulse width', 'write cycle' or 'read cycle'. From a timing standpoint, the RAM can be treated just like a flip-flop.

The RAM includes a clock generator cell and latches data on its inputs and outputs. Upon receipt of a LOW-to-HIGH transition on the clock input, the clock generator creates a set of internal signals for the RAM. During a write cycle, the clock generator creates a pulse to latch the write enable, data and address inputs. During a read cycle a pulse is generated to latch the addressed data in the output latches. Both read and write operations are completed upon a single low-to-high transition of the clock. This is true for both single and dual port modes. Timing diagrams for the 2 operations are shown in figure 11.

Figure 11: Read/Write Cycle Timing

Page 12 DynaChip

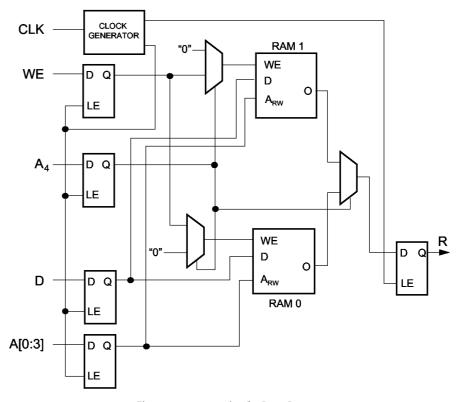

Figure 12: 32x1 Single Port RAM

Figure 12 shows the configuration for the 32x1 Single Port RAM. There are 5 bits for address (A0 - A4), a data input (D), a write enable (WE) and a clock input. All 7 inputs are totally synchronous to the clock. Just like an edge triggered flip flop, the only timing requirement is that all setup and hold times must be obeyed. When WE is HIGH, the RAM is in the write mode. Data presented on the D input will be written to the location specified by addresses A0 - A4. During a write cycle, the output of the RAM is in an unknown state. When WE is LOW, the RAM is in the read mode. The data stored in the location specified by A0 - A4 appears on the output after the rising edge of the clock. This is a single clock operation. The WE and A0 - A4 are setup before the rising edge of the clock and the data stored in the RAM appears after the rising edge of the clock.

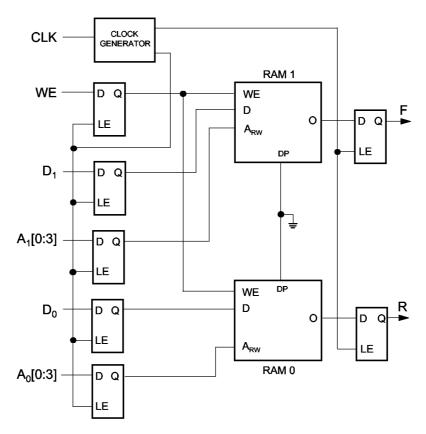

Figure 13: Dual 16X1 Single Port RAM

Figure 13 shows the configuration for the dual 16X1 single port RAM. The cell contains 2 separate 16X1 RAMs where each has their own address and data pins. The dual RAM has 12 inputs. There are 4 bits of address (A00 - A03) and a data input (D0) for RAM 0 and 4 separate bits of address (A10 - A13) and a separate data input (D1) for RAM 1. Both RAMs share the same write enable (WE) and clock input. All 11 inputs are totally synchronous to the clock. Just like an edge triggered flip flop, the only timing requirement is that all setup and hold times are obeyed. Operation of the RAMs is identical to that of the 32X1 single port. When WE is HIGH, the RAMs are in the write mode. Data presented on the D0 input will be written to the location specified by addresses A00 - A03 while data presented on the D1 input will be written to the location specified by addresses A10 - A13. During a write cycle, the outputs of the RAMs are in an unknown state. When WE is LOW, the RAMs are in the read mode. After the rising edge of the clock, the data stored in the location specified by A00 - A03 appears on the output of RAM 0 and the data stored in the location specified by A10 - A13 appears on the output of RAM 1. This is a single clock operation.

Page 14 DynaChip

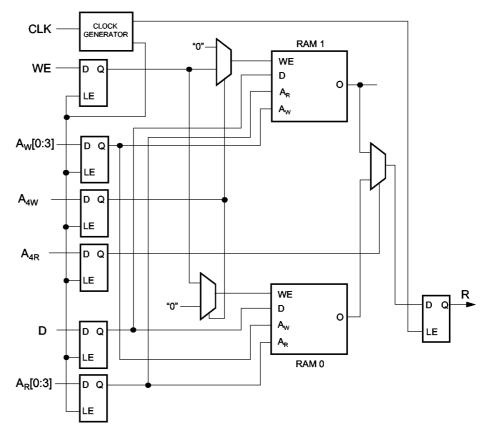

Figure 14: 32x1 Dual Port RAM

Figure 14 shows the configuration for the 32x1 Dual Port RAM. This is a true dual port RAM with separate read and write addresses. The RAM has 5 bits of read address (A0R - A4R), 5 bits of write address (A0W - A4W), a data input (D), a write enable (WE) and a clock input. All 12 inputs are totally synchronous to the clock. Just like an edge triggered flip flop, the only timing requirement is that all setup and hold times are obeyed. The operation of the dual port RAM is slightly different than that of the single port RAMs. When WE is HIGH, the RAM is in the write mode. Data presented on the D input will be written to the location specified by addresses A0W - A4W.

The dual port RAM is always in read mode. The state of WE is unimportant thus WE can either be a "0" or a "1". The data stored in the location specified by A0R - A4R will appear on the output after the rising edge of the clock. This is a single clock operation.

There is one exception to the rule that the RAM is always in read mode. If the read and write addresses are equal and WE is HIGH, the write function takes precedence over the read. As a result, when reading and writing to the same location, only the write function is enabled and the output will be at an unknown state. Note that if WE is LOW, the dual port RAM is in read mode and there will never be a conflict when the read and write addresses are identical.

### **Clock Distribution**

DL6000 family devices have 10 low-skew clock distribution networks. These networks are driven by dedicated pins on the device, internal logic or by the internal PLLs.

Two of the clock networks are global clocks that can drive every flip flop in the device. Eight of the networks are quadrant clocks. The quadrant clocks can drive all the logic block flip flops in one quarter of the device and the I/O flip flops adjacent to these logic blocks.

When driven by input pins, each of the 10 clocks are programmable to LV-TTL, GTL or LV-PECL interface levels. When set to LV-PECL, clock inputs can be single-ended or differential.

Any I/O pin can be used to drive a clock signal out of the device for use elsewhere in the system.

### **Phase Lock Loops**

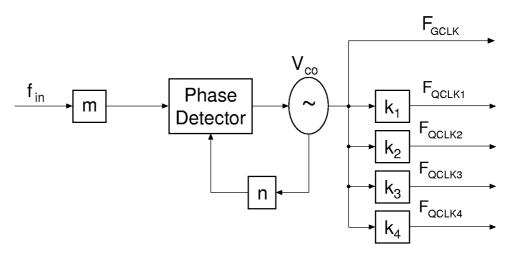

Devices in the DL6000 family contain 2 analog phase lock loop (PLL) circuits that are used for clock multiplication, division and phase locking.

The output clock from the PLL has a duty cycle of 50% + /-5% and a lock time of 1 ms.

As shown in figure 15, the output of each PLL can drive 1 global clock and 4 quadrant clock trees. The multipliers and dividers for each quadrant can be set independently. This allows each PLL to generate up to 5 derivative frequencies from the incoming clock.

Figure 15: PLL

Frequencies for quadrant clock outputs can be divided or multiplied according to the following formula.

$$f_{QCLKx} = fin*n / k_x*m$$

Frequencies for global clock outputs can be multiplied according to the following formula.

$$f_{GCLK} = fin*n / m$$

Page 16 DynaChip

Values for k, m, and n can be programmed as shown in table 3.

| Variable | Allowable Values |  |  |

|----------|------------------|--|--|

| k        | 2,3,4,6 or 8     |  |  |

| m        | 1 or 2           |  |  |

| n        | 2,3,4,6 or 8     |  |  |

Table 3: PLL Variables

The following tables show the available multipliers and dividers for different frequencies.

| Fin Min | Fin Max | GCLK Multiplier | QCLK Multiplier | QCLK Dividers |

|---------|---------|-----------------|-----------------|---------------|

| 14.4    | 20.6    | 8               | 4               | •••••         |

|         |         |                 | 2 2/3           |               |

|         |         |                 | 2<br>1 1/3      |               |

|         |         |                 | 1 (Lock)        |               |

| 19.2    | 27.5    | 6               | 3               | 3/4           |

| 19.2    | 27.5    | 1 (Lock)        | 2               | 3/4           |

|         |         | (LOCK)          | 1 1/2           |               |

|         |         |                 | 1 (Lock)        |               |

| 28.8    | 41.3    | 4               | 2               | 2/3           |

| 20.0    | 11.0    | 1 (Lock)        | 1 1/3           | 1/2           |

|         |         | (,              | 1 (Lock)        |               |

| 38.3    | 55.0    | 3               | 1 1/2           | 3/4           |

|         |         | 1 (Lock)        | 1 (Lock)        | 1/2           |

|         |         |                 |                 | 3/8           |

| 57.5    | 82.5    | 2               | 1 (Lock)        | 2/3           |

|         |         | 1 (Lock)        |                 | 1/2           |

|         |         |                 |                 | 1/3           |

|         |         |                 |                 | 1/4           |

| 76.7    | 110.0   | 1 1/2           |                 | 1/2           |

|         |         | 1 (Lock)        |                 | 3/4           |

|         |         |                 |                 | 3/8           |

|         |         |                 |                 | 1/4           |

|         |         |                 |                 | 3/16          |

| 115.0   | 200.0   | 1 (Lock)        |                 | 1/2           |

|         |         |                 |                 | 1/3<br>1/4    |

|         |         |                 |                 | 1/4           |

|         |         |                 |                 | 1/8           |

|         |         |                 |                 | 1/0           |

Table 4: Multipliers and Dividers for PLL1

### Notes:

<sup>(1)</sup> PLL1 is located in the top left corner and drives GCLK1, QCLK1TL, QCLK1TR, QCLK1BL, and QCLK1BR.

<sup>(3)</sup> Some frequencies require an external resistor connected to the PLL1REST pin.

| Fin Min | Fin Max | GCLK Multiplier | QCLK Multiplier             | QCLK Dividers                    |

|---------|---------|-----------------|-----------------------------|----------------------------------|

| 10.3    | 14.4    | 8               | 4<br>2 2/3<br>2             |                                  |

|         |         |                 | 1 1/3<br>1 (Lock)           |                                  |

| 13.8    | 19.2    | 6               | 3<br>2<br>1 1/2<br>1 (Lock) | 3/4                              |

| 20.6    | 28.8    | 4<br>1 (Lock)   | 2<br>1 1/3<br>1 (Lock)      | 2/3<br>1/2                       |

| 27.5    | 38.3    | 3<br>1 (Lock)   | 1 1/2<br>1 (Lock)           | 3/4<br>1/2<br>3/8                |

| 41.3    | 57.5    | 2<br>1 (Lock)   | 1 (Lock)                    | 2/3<br>1/2<br>1/3<br>1/4         |

| 55.0    | 76.7    | 1.5<br>1 (Lock) |                             | 3/4<br>1/2<br>3/8<br>1/4<br>3/16 |

| 82.5    | 115.0   | 1 (Lock)        |                             | 1/2<br>1/3<br>1/4<br>1/6<br>1/8  |

Table 5: Multipliers and Dividers for PLL2

### Notes:

- (1) PLL2 is located in the top right corner and drives GCLK2, QCLK2TL, QCLK2TR, QCLK2BL, and QCLK2BR.

- (3) Some frequencies require an external resistor connected to the PLL2REST pin.

| GCLK Frequency | Jitter                |

|----------------|-----------------------|

| 14 to 80 MHz   | 3% of clock period    |

| 81 to 165 MHz  | 350 ps <sup>(1)</sup> |

| T-1.1. 6. D    | OT T Tillar           |

Table 6: PLL Jitter

#### Note:

(1) Requires input clock jitter  $\leq$  100 ps.

Page 18 DynaChip

## Power Consumption

Power consumption for a specific design implemented in a DL6000 family device depends on the following factors.

- Number of logic blocks used

- Operating frequency

- Number of outputs used

- I/O interface level setting (TTL or GTL)

- Output slew rate selection

- Number of global and quadrant clocks used

- Operating supply voltage

The following table shows typical power consumption for various components of a DL6035 operating at 100 MHz.

| DL6035 Component                                       | Typical Power Consumption at 100 MHz |

|--------------------------------------------------------|--------------------------------------|

| Logic Block (including interconnect)                   | 4.6 m <b>W</b>                       |

| I/O Block set to TTL mode (excluding off-chip current) | 910 μW                               |

| I/O Block set to GTL mode (excluding off-chip current) | 7.5 mW                               |

| Each Global Clock                                      | 600 mW                               |

| Each Quadrant Clock                                    | 150 mW                               |

**Table 7: Typical Power Consumption**

# Configuration

Memory cells in DynaChip FPGAs store configuration bits that control all the programmable elements in the device. These configuration bits are called a bitstream and they are loaded automatically from a PROM at power-up or under user control through a microprocessor.

Systems that contain more than one DynaChip device can be set up in a programming chain to simplify connections.

### **Configuration Modes**

The DL6000 supports 6 configuration modes. Five are for loading a bitstream into the device and one is for reading a bitstream out of a programmed device. The state of three special pins called mode pins sets the configuration mode of the DL6000 device.

### **Serial Configuration Modes**

There are 3 serial configuration modes as described in table 8.

| Senial Configuration Works | Description                                                                                                                                                                                    |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Internal Last       | This mode is used in 2 situations.                                                                                                                                                             |

|                            | 1) To program a single device from a serial PROM. In this mode, the DL6000 generates a clock signal to drive the serial PROM.                                                                  |

|                            | 2) For the last device in a programming chain that uses a serial PROM. In this mode, the DL6000 generates a clock signal to drive the serial PROM and the other DynaChip devices in the chain. |

| Serial External Not Last   | This mode is used for each device except the last device in a programming chain that uses a serial PROM.                                                                                       |

| Serial External Last       | This mode is used to program a single device using a serial bitstream and a user supplied clock.                                                                                               |

|                            | It is also used for the last device in a programming chain that is programmed using a serial bitstream and a user supplied clock.                                                              |

**Table 8: Serial Configuration Modes**

Page 20 DynaChip

### **Microprocessor Configuration Modes**

There are 2 microprocessor configuration modes as described in table 9.

| Precioente de la contraction d |                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Microprocessor Last                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | This mode is used in 2 situations.                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | To program a single device from a mi-<br>croprocessor.                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | For the last device in a programming chain that uses a microprocessor.                                      |

| Microprocessor Not Last                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This mode is used for each device except the last device in a programming chain that uses a microprocessor. |

**Table 9: Microprocessor Configuration Modes**

### **Dynamic Reconfiguration Using Full Chip Reset**

Full Chip Reset enables the user to completely reset the device without turning off the power. It is typically used to prepare a device for a complete reconfiguration after initial configuration. When full chip reset is asserted, all the configuration bits and flip flops in the device are reset. This is similar to the internal reset that occurs when the device is first powered-up.

Full chip reset is activated by setting the mode pins to '111' and then asserting the RESET pin (active low) for a minimum of 10 ms. The mode pins must be set before the reset is asserted.

To reprogram the device after a full chip reset, set the mode pins to their appropriate values (refer to table 10, page 22) and apply another RESET pulse of at least 10 ms.

As an alternative to using full chip reset, the device can be reprogrammed using a complete bitstream that programs every element. Contact the factory for availability of a complete bitstream.

#### Partial Reprogramming

After the device has been powered-up and programmed, the user can reprogram a portion of the device on the fly without affecting the existing application.

To dynamically reprogram a portion of the device, set the mode pins to their appropriate value (refer to table 10, page 20), and then assert RESET (active low). The mode pins must be set before the RESET is asserted.

The portion of the device that is not affected by the partial reprogramming operates normally during reconfiguration.

Special bitstreams must be used for partial reconfiguration to insure that unused logic and interconnect from the previous function are deleted. Contact the factory for more information on availability of these special bitstreams.

Some of the non-dedicated configuration I/O do not function as user I/O during dynamic reprogramming as indicated below:

#### In Serial Mode:

- Pins M0, M1, M2 and D0, become dedicated for programming.

- The DONE pin becomes dedicated for programming when the device is used in a programming chain.

- The DOUT pin becomes dedicated for programming if readback is required.

- The rest of the I/O's remain operational.

#### In Processor Mode:

- Pins M0, M1, M2, D0, D1-D7, WE and RDY become dedicated for programming.

- The DONE pin becomes dedicated for programming when the device is used in a programming chain.

- The DOUT pin becomes dedicated for programming if readback is required.

- The rest of the I/O's remain operational.

#### Readback

Once the device has been programmed, a configuration mode called readback can be used to read the program bitstream out of the device to determine if it was loaded properly.

### **Configuration Clock Frequencies**

In Serial Internal Last mode, the DL6000 generates a 2.5 MHz clock that is used to drive the serial PROM.

In Serial External Last mode, an external clock up to 25 MHz can be supplied to the DL6000.

### **Mode Pin Settings**

The state of three pins on the DL6000 device named M0, M1 and M2 determine the loading mode. The settings for each mode are shown in table 10.

| Configuration(Mode       | 3.5 |   | 1010 |

|--------------------------|-----|---|------|

| Serial Internal Last     | 0   | 0 | 0    |

| Serial External Not Last | 1   | 0 | 0    |

| Serial External Last     | 0   | 0 | 1    |

| Microprocessor Last      | 1   | 0 | 1    |

| Microprocessor Not Last  | 1   | 1 | 0    |

| Readback                 | 0   | 1 | 1    |

| Full Chip Reset          | 1   | 1 | 1    |

**Table 10: Mode Pin Settings**

#### Note:

If the mode pins are not connected, they are pulled down to a logic '0'.

Page 22 DynaChip

### Flip Flop Initialization

After configuration, flip flops are in an unknown state. All flip flops can be initialized by applying a global reset signal to the device.

Upon assertion of the global reset, I/O and logic block flip flops are either set or reset depending on their definition in the design.

### **Configuration Schematics**

The following schematics show typical connections to the DL6000 for each loading mode.

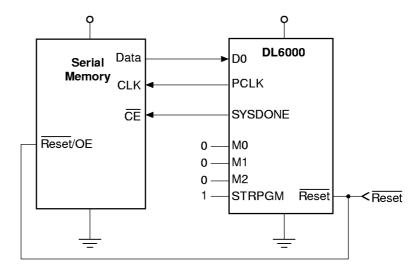

### **Serial PROM Configuration Mode**

In the serial PROM configuration mode, the device automatically loads itself from a serial PROM when the system is powered up. The PROM provides serial data and responds to a clock signal generated by the DL6000 device.

Systems using this loading mode should be connected as shown in figure 16.

Figure 16: Serial PROM Configuration Schematic

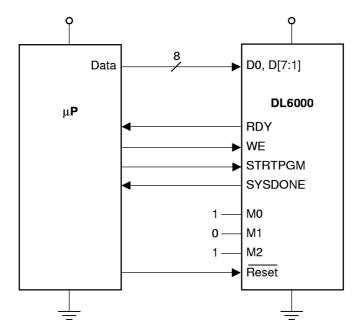

### Microprocessor Configuration Mode

In the microprocessor configuration mode, the device is loaded under user control from a microprocessor interface. Data is loaded into the DL6000 device byte-wide in response to the rising edge of a write enable signal. The DL6000 device generates a ready signal that indicates it is ready for the next byte of data.

Systems using the microprocessor configuration mode should be connected as shown in figure 17.

Figure 17: Microprocessor Configuration

A microprocessor can also be used to load the DL6000 family device in serial external mode. In this configuration, the microprocessor supplies a clock and serial data to the DL6000 family device.

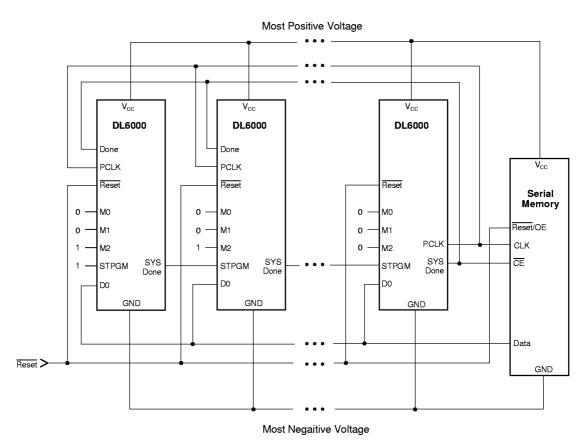

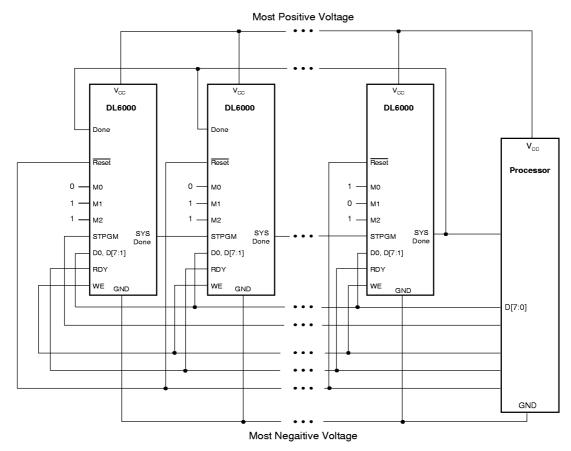

### **Programming Chains**

Programming chains simplify connections for systems that use more than one DL6000 family device. Using programming chains, one DL6000, called the last device, connects to the source of the configuration data. The remaining DL6000 devices connect in a chain using their serial configuration pins.

Systems using programming chains with a serial PROM should be connected as shown in figure 18. Systems using programming chains with a microprocessor should be connected as shown in figure 19.

Page 24 DynaChip

Figure 18: Programming Chain Using Serial Memory

Figure 19: Programming Chain Using Microprocessor

### **Bitstream Size**

The size of the programming bitstream for a DL6000 family device depends on the number of logic blocks that are used in the design. The following table shows the maximum number of programming bits for each device in the DL6000 family.

| Device | Maximum Number of Programming Bits |

|--------|------------------------------------|

| DL6009 | 140,000                            |

| DL6020 | 270,000                            |

| DL6035 | 450,000                            |

| DL6055 | 670,000                            |

| DL6080 | 940,000                            |

| DL6105 | 1,300,000                          |

**Table 11: Maximum Number of Programming Bits**

Page 26 DynaChip

## **Configuration Pins**

Two types of pins are used in the configuration process. Permanently dedicated pins are always dedicated to configuration functions. User pins that can have special functions become user I/O pins after device configuration

|               |     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCKI/<br>PCKO | Yes | This pin has 3 different functions depending on the programming mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |     | <ol> <li>If the device is the only device to be programmed or is<br/>last in a programming chain and an external clock is<br/>not being used, this pin is an output that sends the<br/>master clock to all other devices and the serial PROM.</li> </ol>                                                                                                                                                                                                                                                                                                                                                      |

|               |     | 2) If the device is in a programming chain and is not the last device, this is an input pin that receives the master clock from the last device.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               |     | 3) If an external, user supplied clock controls the configuration process, this pin is the input for that clock. When not in programming, this pin defaults to an input.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| STRPGM        | Yes | This pin should be connected as shown in the configuration schematics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET         | Yes | This reset is used for dynamic reprogramming. It is asserted by setting the mode pins to any value except '111' and asserting the RESET pin (active low) for a minimum of 10 ms. Note that the mode pins must be set before the RESET is asserted. All non-dedicated configuration I/O's assume states based on the function defined by the programming mode.                                                                                                                                                                                                                                                 |

|               |     | If dynamic reprogramming is not required, the RESET pin should be connected as shown in the configuration schematics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SYS<br>DONE   | Yes | This output pin is dedicated for programming. Once configuration has been completed, this pin goes from low to high and stays high until either the power is turned off or a reset signal is applied. If the device is the last or only device to be programmed, this pin signals the device that configuration has been completed and to start normal operation. Also, if the device is the last in a programming chain, this pin signals all other devices that programming has been completed and to return to normal operation. This signal also controls the enabling and disabling of a serial PROM(s). |

| M0 - M2       | No  | These pins are inputs during programming. They are used to tell the device(s) which mode will be used for configuration. The list of settings for each configuration mode is shown in table 10. These pins become I/O's during normal operation. If the mode pins are not connected, they are pulled down to a logic '0'.                                                                                                                                                                                                                                                                                     |

|         |    | Function                                                                                                                                                                                                                                                                                                                                                        |

|---------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DONE    | No | This is an input pin during programming that is only used in a multiple device configuration mode. If the device is not last, the DONE pin is tied to the SYSDONE pin of the last device. A low to high on this pin signals that programming has been completed and the device begins normal operation. This pin can be used as an I/O during normal operation. |

| D0      | No | This is an input pin during programming. It accepts serial data from a memory source or another device. It can also accept the LSB from a byte wide memory source for microprocessor configuration mode. This pin can be used as an I/O during normal operation.                                                                                                |

| D1 - D7 | No | These are data input pins for the microprocessor configuration mode. They are only activated after the reset signal has been applied. They accepts bits 1 - 7 of data loaded from a parallel source. Can be used as I/Os during normal operation.                                                                                                               |

| WE      | No | This is a input pin during microprocessor configuration mode. It is only activated after the reset signal has been applied. This pin is used by the processor to signal the DL6000 that 8-bits have been placed on the D[7:0] pins for loading. This pin becomes an I/O during normal operation.                                                                |

| RDY     | No | This is an output pin for microprocessor configuration mode. It signals an external processor that 8 bits have been loaded and the device is ready to receive the next 8 bits. This pin can be used as an I/O during normal operation.                                                                                                                          |

| DOUT    | No | This outputs pin supplies the bitstream during readback mode. This pin can be used as an I/O during normal operation.                                                                                                                                                                                                                                           |

Page 28 DynaChip

## JTAG

All devices in the DL60000 family provide JTAG Boundary Scan. Completely compatible with IEEE specifications, this feature simplifies testing of boards with surface mount packages or closely spaced pins.

Four JTAG instructions are supported as shown in table 12.

| JTAG Instructions | Register | Opcode |

|-------------------|----------|--------|

| SAMPL/PRE         | BSC      | 1000   |

| EXTEST            | BSC      | 0000   |

| BYPASS            | BYPASS   | 1111   |

| IDCODE            | ID       | 1101   |

**Table 12: JTAG Instructions**

The JTAG ID register is read when the DL6000 is reset and when Opcode 1101 is loaded. On power-up, the opcode defaults to 1101. Internal pull-up resistors are provided on the TDI and TMS pins.

The DL6000 JEDEC ID number is 331-300-6100-0.

## Product Specifications

### **Maximum Ratings**

|                    | brendinin                                | Verific :                     |   |

|--------------------|------------------------------------------|-------------------------------|---|

| V <sub>CC</sub>    | V <sub>CC</sub> Pin Potential to GND Pin | -0.5 to +5.0                  | ٧ |

| V <sub>IN</sub>    | Input Voltage                            | -0.5 to V <sub>CC</sub> + 0.5 | ٧ |

| V <sub>TS</sub>    | Voltage applied to 3-state output        | -0.5 to V <sub>CC</sub> + 0.5 | ٧ |

| T <sub>STORE</sub> | Storage temperature                      | -65 to +150                   | С |

| TJ                 | Junction Temperature                     | +150                          | С |

**Table 13: Absolute Maximum Rating**

#### Note:

Permanent damage to the device may occur if the Absolute Maximum ratings are exceeded. This is a stress rating only. Functional operation of the device at these or any other conditions other than those listed under the Recommended Operating Conditions is not implied.

Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

### **Operating Conditions**

|                                | Description                             | 2000 |      |   |

|--------------------------------|-----------------------------------------|------|------|---|

| V <sub>CC</sub> <sup>(1)</sup> | Supply voltage relative to GND          |      |      |   |

|                                | Commercial 0 C to 85 C junction         | 3.14 | 3.47 | ٧ |

|                                | Industrial –40 C to 100 C junction      | 3.0  | 3.6  | V |

| V <sub>TT</sub>                | GTL terminating voltage relative to GND |      |      |   |

|                                | Commercial 0 C to 85 C junction         | 1.14 | 1.26 | ٧ |

|                                | Industrial –40 C to 100 C junction      | 1.08 | 1.32 | ٧ |

**Table 14: Recommended Operating Conditions**

#### Notes:

- (1) 0.25 $\mu$  devices require a core supply voltage of 2.5V +/- 5% and an I/O supply voltage of 3.3V +/- 5%.

- (2) All junction temperatures above those listed as Operating conditions are illegal.

Page 30 DynaChip

### **DC Characteristics Over Operating Conditions**

|                                  | Parameter                            |                           |                           |    | Test Conditions                                     |

|----------------------------------|--------------------------------------|---------------------------|---------------------------|----|-----------------------------------------------------|

| V <sub>IMAX</sub> <sup>(5)</sup> | Max. voltage applied to input        | -                         | 5.5                       | ٧  |                                                     |

| V <sub>CMAX</sub> <sup>(6)</sup> | Max. voltage applied to clock inputs | -                         | 3.63                      | V  |                                                     |

| V <sub>IH(TTL)</sub>             | High-level Input Voltage             | 2.0                       | V <sub>CC</sub> +<br>0.3  | V  |                                                     |

| $V_{IL(TTL)}$                    | Low-level input voltage              | 0.0                       | 0.8                       | ٧  |                                                     |

| V <sub>IH(CMOS)</sub>            | High-level Input Voltage             | 0.7V <sub>CC</sub>        | V <sub>CC</sub>           | ٧  |                                                     |

| V <sub>IL(CMOS)</sub>            | Low-level input voltage              | 0.0                       | 0.3V <sub>CC</sub>        | ٧  |                                                     |

| V <sub>IH(GTL)</sub>             | High-level Input Voltage             | V <sub>REF</sub> +<br>0.2 | V <sub>TT</sub>           | ٧  |                                                     |

| V <sub>IL(GTL)</sub>             | Low-level input voltage              | 0.0                       | V <sub>REF</sub> -<br>0.2 | V  |                                                     |

| V <sub>IH(LVPECL)</sub>          | High-level input voltage             | 2.135                     | 2.420                     | ٧  | When V <sub>CC</sub> = 3.3V                         |

| V <sub>IL(LVPECL)</sub>          | Low-level input voltage              | 1.490                     | 1.825                     | ٧  | When V <sub>CC</sub> = 3.3V                         |

| V <sub>OH (TTL)</sub>            | High level output voltage            | 2.4                       |                           | ٧  | V <sub>CC</sub> min, See note 2 for I <sub>OH</sub> |

| $V_{OL(TTL)}$                    | Low level output voltage (1,2)       | -                         | 0.4                       | V  | $ m V_{CC}$ min, See note 2 for $ m I_{OL}$         |

| V <sub>OH(GTL)</sub>             | High level output voltage (3,4)      | -                         | ۷π                        | V  |                                                     |

| V <sub>OL(GTL)</sub>             | Low level output voltage (3)         | -                         | 0.4                       | ٧  | $I_{OL}$ = 20 mA, $V_{TT}$ max                      |

| lcc                              | Quiescent current                    | -                         | 10                        | mA | V <sub>CC</sub> = MAX; All I/O's open               |

| I <sub>IL</sub>                  | Leakage Current                      | -10                       | +10                       | μΑ |                                                     |

| C <sub>IN</sub>                  | Input capacitance                    | -                         | 8.5                       | pF |                                                     |

**Table 15: DC Electrical Characteristics**

#### Notes:

- (1) With 50% of the outputs simultaneously sinking 16 mA each.

- (2) Sink/Source current in TTL mode varies with slew rate setting: Fast slew rate: sink/source current = 16 mA (at V<sub>CC</sub> min) Medium slew rate: sink/source current = 11 mA (at V<sub>CC</sub> min) Slow slew rate: sink/source current = 5 mA (at V<sub>CC</sub> min)

- (3) Sink current in GTL mode = 24 mA. Source current is provided by external pull-up resistor.

- (4)  $V_{REF} = 2/3 V_{TT}$

- (5) All I/O pins except clock inputs are 5 volt tolerant.

- (6) The maximum voltage applied to the following clock input pins should not exceed this value, even if they are used as non-clock I/O. QCLK1TL, QCLK1TLN, QCLK2TL, QCKL2TLN, QCKL1BLN, QCKL1BLN, QCKL2BLN, QCKL2BLN, QCKL1BRN, QCLK1BRN, QCLK2BRN, QCKL1TRN, QCKL2TRN, QCKL2TRN, GCLK1, GCLK1N, GCLK2, GCLK2N, PLLIREST, PLL2REST

### **Clock and Set/Reset Buffer Switching Characteristics**

| Secretion                                       | Symposis          |     |     |     | i de de |

|-------------------------------------------------|-------------------|-----|-----|-----|---------|

|                                                 |                   |     |     |     |         |

| Clock buffer delay with PLL                     | T <sub>CPLL</sub> | 1.1 | 1.0 | 0.9 | ns      |

| Global clock delay without PLL <sup>(1)</sup>   | T <sub>GCKD</sub> | 6.7 | 5.6 | 5.0 | ns      |

| Global clock skew                               | T <sub>GCKS</sub> | .15 | .15 | .15 | ns      |

| Quadrant clock delay without PLL <sup>(1)</sup> | T <sub>QCKD</sub> | 5.5 | 5.0 | 4.5 | ns      |

| Quadrant clock skew                             | T <sub>QCKS</sub> | .15 | .15 | .15 | ns      |

| Clock min pulse width high                      | T <sub>MPH</sub>  | 2.4 | 2.2 | 2.0 | ns      |

| Clock min pulse width low                       | T <sub>MPL</sub>  | 2.4 | 2.2 | 2.0 | ns      |

| Global Set/Reset delay                          | T <sub>GSR</sub>  | 33  | 30  | 27  | ns      |

Table 16: Clock Buffer AC Characteristics (Input Set to TTL)

#### Notes:

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip flop clock input.

- (2) All delays are specified over commercial voltage and temperature range.

- (3) Clock delays are also referred to as latency.

| Controller                                      |                   |     |     |     |    |

|-------------------------------------------------|-------------------|-----|-----|-----|----|

|                                                 |                   |     |     |     |    |

| Clock buffer delay with PLL                     | T <sub>CPLL</sub> | 1.9 | 1.7 | 1.6 | ns |

| Global clock delay without PLL <sup>(1)</sup>   | T <sub>GCKD</sub> | 7.6 | 6.1 | 5.5 | ns |

| Global clock skew                               | T <sub>GCKS</sub> | .15 | .15 | .15 | ns |

| Quadrant clock delay without PLL <sup>(1)</sup> | T <sub>QCKD</sub> | 6.4 | 5.9 | 5.4 | ns |

| Quadrant clock skew                             | T <sub>QCKS</sub> | .15 | .15 | .15 | ns |

| Clock min pulse width high                      | T <sub>MPH</sub>  | 2.4 | 2.2 | 2.0 | ns |

| Clock min pulse width low                       | T <sub>MPL</sub>  | 2.4 | 2.2 | 2.0 | ns |

| Global Set/Reset delay                          | T <sub>GSR</sub>  | 34  | 31  | 28  | ns |

Table 17: Clock Buffer AC Characteristics (Input Set to GTL)

#### Notes:

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip flop clock input.

- (2) All delays are specified over commercial voltage and temperature range.

- (3) Clock delays are also referred to as latency.

Page 32 DynaChip

| Security                                        |                   |     |     |     | la de la companya de |

|-------------------------------------------------|-------------------|-----|-----|-----|----------------------------------------------------------------------------------------------------------------|

|                                                 |                   |     |     |     |                                                                                                                |

| Clock buffer delay with PLL                     | T <sub>CPLL</sub> | 1.9 | 1.7 | 1.6 | ns                                                                                                             |

| Global clock delay without PLL (1)              | T <sub>GCKD</sub> | 7.6 | 6.1 | 5.5 | ns                                                                                                             |

| Global clock skew                               | T <sub>GCKS</sub> | .15 | .15 | .15 | ns                                                                                                             |

| Quadrant clock delay without PLL <sup>(1)</sup> | T <sub>QCKD</sub> | 6.4 | 5.9 | 5.4 | ns                                                                                                             |

| Quadrant clock skew                             | T <sub>QCKS</sub> | .15 | .15 | .15 | ns                                                                                                             |

| Clock min pulse width high                      | T <sub>MPH</sub>  | 2.4 | 2.2 | 2.0 | ns                                                                                                             |

| Clock min pulse width low                       | T <sub>MPL</sub>  | 2.4 | 2.2 | 2.0 | ns                                                                                                             |

| Global Set/Reset delay                          | T <sub>GSR</sub>  | 34  | 31  | 28  | ns                                                                                                             |

Table 18: Clock Buffer AC Characteristics (Input Set to LV-PECL)

#### Notes:

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip flop clock input.

- (2) All delays are specified over commercial voltage and temperature range.

- (3) Clock delays are also referred to as latency.

| Description                                     |                   |       |     |     |    |

|-------------------------------------------------|-------------------|-------|-----|-----|----|

|                                                 |                   | 16.00 |     |     |    |

| Clock buffer delay with PLL                     | T <sub>CPLL</sub> | 1.9   | 1.7 | 1.6 | ns |

| Global clock delay without PLL (1)              | T <sub>GCKD</sub> | 7.6   | 6.1 | 5.5 | ns |

| Global clock skew                               | T <sub>GCKS</sub> | .15   | .15 | .15 | ns |

| Quadrant clock delay without PLL <sup>(1)</sup> | T <sub>QCKD</sub> | 6.4   | 5.9 | 5.4 | ns |

| Quadrant clock skew                             | T <sub>QCKS</sub> | .15   | .15 | .15 | ns |

| Clock min pulse width high <sup>(4)</sup>       | T <sub>MPH</sub>  | 2.4   | 2.2 | 2.0 | ns |

| Clock min pulse width low                       | $T_{MPL}$         | 2.4   | 2.2 | 2.0 | ns |

| Global Set/Reset delay                          | T <sub>GSR</sub>  | 34    | 31  | 28  | ns |

Table 19: Clock Buffer AC Characteristics (Input Set to Differential LV-PECL)

### Notes:

- (1) Global and quadrant clock delays are measured from the input pin on the device to the flip flop clock input.

- (2) All delays are specified over commercial voltage and temperature range.

- (3) Clock delays are also referred to as latency.

- (4) For RAM operation, see clock min pulse width high in table 25.

### Input and Output Block Switching Characteristics

| Description.                                                             | Symple              |     |     |     |    |

|--------------------------------------------------------------------------|---------------------|-----|-----|-----|----|

|                                                                          |                     | 4.6 |     | 0.0 |    |

| Input buffer combinatorial delay                                         | T <sub>INPD</sub>   | 4.3 | 3.2 | 2.6 | ns |

| Input Register Set-up Time (global clock)                                | T <sub>INIS1</sub>  | 2.1 | 1.6 | 1.3 | ns |

| Input Register Hold Time (global clock)                                  | T <sub>INIH1</sub>  | 0   | 0   | 0   | ns |

| Input Register Clock to Output (global clock)                            | T <sub>INCO1</sub>  | 3.5 | 2.6 | 2.1 | ns |

| Output buffer combinatorial delay (no load) <sup>(2,3)</sup>             | T <sub>OUTIS1</sub> | 6.0 | 4.6 | 3.5 | ns |

| Output Register Set-up Time (global clock)                               | T <sub>OUTIS2</sub> | 3.5 | 2.6 | 1.9 | ns |

| Output Register Hold Time (global clock)                                 | T <sub>OUTIH1</sub> | 0   | 0   | 0   | ns |

| Output Register Clock to Output (global clock, no load) <sup>(2,3)</sup> | Тоитсо1             | 3.6 | 2.9 | 2.3 | ns |

| I/O Register Clock Enable Setup Time                                     | T <sub>CES1</sub>   | 2.7 | 2.0 | 1.4 | ns |

| I/O Register Clock Enable Hold Time                                      | T <sub>CEH1</sub>   | 0   | 0   | 0   | ns |

| Input Register GSR set/reset delays                                      | T <sub>GSRI</sub>   | 3.4 | 2.6 | 2.1 | ns |

| Output Register GSR set/reset delays                                     | T <sub>GSRO</sub>   | 3.7 | 3.0 | 2.4 | ns |

| Input Register GSR set/reset setup time                                  | T <sub>GSRIS1</sub> | 0.5 | 0.4 | 0.3 | ns |

| Output Register GSR set/reset setup time                                 | T <sub>GSROS1</sub> | 0.5 | 0.4 | 0.3 | ns |

Table 20: Input and Output Buffer Parameters (I/O Set to TTL)

#### Notes:

- (1) All delays are specified over commercial voltage and temperature range.

- (2) Output delays are specified with no load. Add the following delays to adjust for loading.

Fast Slew Rate: 40 ps/pf Medium Slew Rate: 60 ps/pf Slow Slew Rate: 95 ps/pf

(3) The maximum loading for outputs switching at the same time in the same direction is shown below. Significant ground bounce may occur if these guidelines are violated.

Fast Slew Rate: 200 pf between each power/ground pair Medium Slew Rate: 300 pf between each power/ground pair Slow Slew Rate: 400 pf between each power/ground pair

(4) Each output pin has individual slew rate control.

#### Three-state Buffer Characteristics

| nescriptor                                       | Sympos             |     |     |     |    |

|--------------------------------------------------|--------------------|-----|-----|-----|----|

| 3-state to Pad Active (no load) <sup>(2,3)</sup> | T <sub>3SOE</sub>  | 4.5 | 3.7 | 3.3 | ns |

| 3-state to Pad Hi-Z (no load) (2,3)              | T <sub>INIS1</sub> | 4.5 | 3.7 | 3.3 | ns |

Table 21: Three-state Buffer Delays

#### Notes:

- (1) All delays are specified over commercial voltage and temperature range.

- (2) Output delays are specified with no load. Add the following delays to adjust for loading.

Fast Slew Rate: 40 ps/pf Medium Slew Rate: 60 ps/pf Slow Slew Rate: 95 ps/pf

(3) Each output pin has individual slew rate control.

Page 34 DynaChip

| Paristi viki                                                           |                     |     |     |     |    |  |  |

|------------------------------------------------------------------------|---------------------|-----|-----|-----|----|--|--|

|                                                                        |                     |     |     |     |    |  |  |