## WANCHESTER ENCODER/DECODER WODULES

Data sates from 1 Mb/s to 50 Mb/s; very low usage current.

Catalog #118B

T-75-57

### Features:

- Available with data rates up to 50 Mb/s, or any data rate down to 1 Mb/s.

- \* 35-55 mA usage current.

- Independent Manchester II encoder/decoder operation.

- On-chip divide-by-two clock circuit.

- Compact 16-pin dual in-line package.

- \* TTL-compatible +5V operation.

- Military temperature range available.

## **Applications:**

- Local Area Network (LAN) interface.

- Controller/transceiver interfacing at standard or custom data rates.

- IEEE 802.3 LAN (Ethernet) interface.

- HDLC/SDLC communication.

- · Fiber-optic data link,

- Multidrop bus interface.

## **Description:**

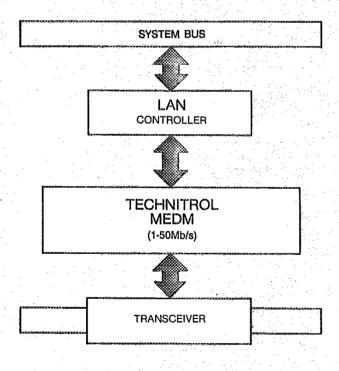

A high-speed serial data communications device, the Technitrol Manchester II encoder/decoder module (MEDM<sup>TM</sup>) serves as a complete Manchester interface between a local area network (LAN) controller and a LAN transceiver (Figure 1).

An important specification for these communication systems is rate of data transmission, in bits per second. Widely used data rates are 1 Mb/s (primarily military), 2.5 Mb/s (IEEE LAN), and 10 Mb/s (IEEE 802.3/Ethernet). Other data rates are often selected for several designer advantages.

Figure 1 LAN communications system including a Technitrol MEDM.

The Technitrol MEDM is available at any dedicated data rate, from 1 Mb/s to 50 Mb/s. It offers independent Manchester II encoding and decoding and has self-test capability. The module is designed with three independent sections: the encoder, the decoder, and a 50%-duty-cycle on chip transmit clock oscillator.

### Manchester code:

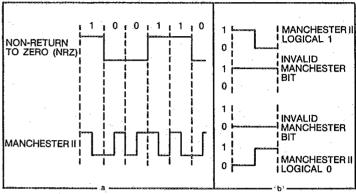

Applications that employ Manchester code generally require very reliable data transmission and interfacing, and high noise immunity. Manchester II code has a 50% duty cycle and contains a data transition in the middle of every bit cell. The first half of the bit cell contains the true value of the binary data. The second half contains the complement of the data. Binary 0 is a low-to-high transition. Binary 1 is a high-to-low transition (Figure 2).

Figure 2 Basic Manchester Code.

# Technitrol MEDM™operation:

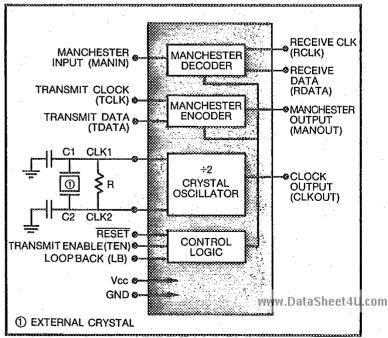

The encoder of the Technitrol MEDM accepts TTL non-return-todb/s zero (NRZ) transmit data (TDATA), transmit clock (TCLK), and transmit enable (TEN) signals, and encodes Manchester II biphase DataSheeputput (MANOUT) to interface with the transceiver.

The decoder of the Technitrol MEDM accepts TTL-level Manchester II encoded input (MANIN) from the LAN transceiver and generates a TTL-level synchronized received-clock (RCLK) signal and a NRZ received-data (RDATA) signal to interface with the LAN controller.

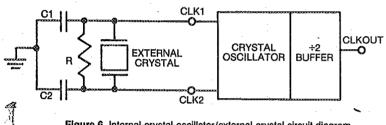

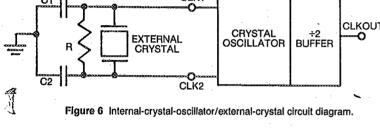

The clock-oscillator circuit requires an additional crystal with 2X the clock frequency to generate a 50%-duty-cycle clock signal. This signal can be used for TCLK input and/or system clock signal. The control logic block interfaces with and controls the functions common to all blocks. It provides master-reset and transmit-enable functions.

A loopback (LB) function is provided for self-testing.

Figure 3 Technitrol MEDM circuit diagram.

# he encoder: From NRZ data to Manchester II code.

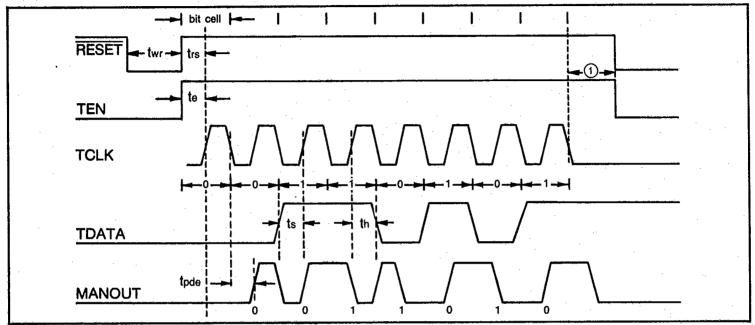

The encoder employs a TCLK signal at data-rate frequency, 50% duty cycle. This TCLK signal can be from an available system clock or from the clock oscillator of the MEDM in combination with an external crystal. When shifting NRZ-TTL data from the LAN controller to the MEDM, the data shifts on the beginning transition (falling edge) of the clock signal (TCLK), and is accepted into the module as TDATA. The MEDM then samples TDATA on mid-transition (rising edge) of the clock signal, permitting ½-bit settling time of TDATA before sampling. The sampling of very stable TDATA permits very reliable encoding.

The transmit-enable input (TEN), when high, permits the encoder to transmit (MANOUT). If TEN goes low, transmission stops. Likewise, RESET must remain high for the full duration of NRZ serial data transmission. Low on RESET will terminate encoder activity and bring all outputs to known state or origin.

Encoder cycle begins when RESET and TEN go high, enabling NRZ serial data presented at TDATA to be sampled into the MEDM and encoded into TTL Manchester II biphase data (MANOUT),

which contains both data and clock information.

(1) Reset must remain high until last information bit is transmitted.

Figure 4 Encoder timing diagram.

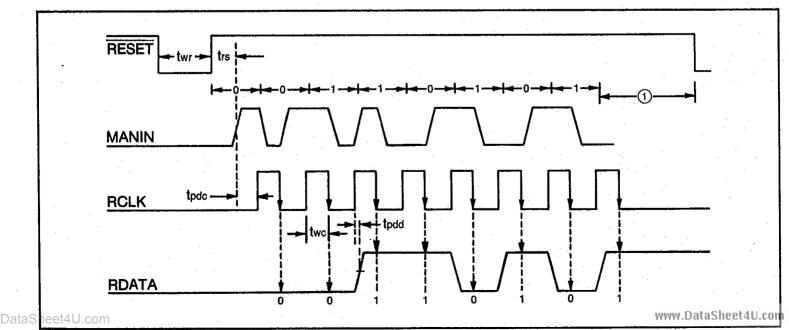

# The decoder: From Manchester II code to NRZ data.

The decoder of the Technitrol MEDM is free running. It has a very wide jitter tolerance and functions without error for MANIN signals with ±10% time skew.

The decoder accepts TTL Manchester II encoded signal (MANIN) from the LAN transceiver and generates both a NRZ-TTL signal (RDATA) and a clock signal that permit direct interfacing to the LAN controller. RDATA is sampled into the LAN controller on the falling edge of RCLK (not a true 50/50 clock signal).

Binary 0 on the first bit synchronizes the decoder to the MANIN signal if the idle state of MANIN is low. Likewise, binary 1 on the first bit synchronizes the decoder to MANIN if its idle state is high.

Generally, binary 0 followed by binary 1 or 1 followed by 0 guarantees decoder synchronization and reliable data transmission by the second bit of MANIN.

Low level on RESET terminates decoder operation and returns all output to known state or origin.

(1) Reset must remain high until last information bit is transmitted.

Figure 5 Decoder timing diagram.

## Self-test loopback:

The self-test feature of the Technitrol MEDM is performed by a loopback function. A high-level on LB input internally gates the encoder output (MANOUT) to decoder input (MANIN) and disables MANOUT and MANIN signals.

When LB is activated, NRZ data presented on the

TDATA line is encoded in the encoder section, then decoded in the decoder section, and then presented back as NRZ RDATA. This data will exhibit the propagation delay of the encoder and decoder (tpde + tpdc), but otherwise should correspond to TDATA.

#### Clock oscillator:

The clock-oscillator circuit of the MEDM can supply the encoder transmit-clock input (TCLK) when used with an external crystal operating at 2X the data rate (f<sub>D</sub>). Often a 50/50 system clock is already available and is used as the TCLK signal source.

Figure 6 shows a Pierce IC oscillator with a ÷2 buffered output. Recommended feedback resistor(R) is  $5k\Omega$  to  $10k\Omega$ for crystal frequencies of 1 MHz to 40 MHz respectively. Capacitors C1 and C2 are 15 pF or may vary depending on type and make of the crystal. Increasing the value of C2 can adjust the duty cycle (ideally 50/50); however, too much capacitance will cause startup problems.

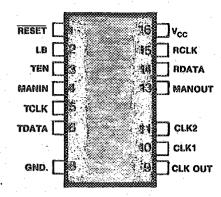

Pin detail:

| Figure | 8 | Pin | configuration |

|--------|---|-----|---------------|

|--------|---|-----|---------------|

| SYMBOL                                                                           | PIN<br>NO. |                                                                                                                                                                                                                                                                                         |  |

|----------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| to a known state. A low<br>a master reset. This sign<br>terminates device activi |            | Reset (INPUT) The reset input line is used to initialize the MEDM to a known state. A low level on this input performs a master reset. This signal asynchronously terminates device activity. The MEDM assumes an idle state until the line is brought high.                            |  |

| LB                                                                               | 2          | Loopback (INPUT) The loopback input line is used to perform a' self-test diagnostic function. A high level on this input internally gates the Manchester output signal back to the Manchester input signal. The MANIN input and MANOUT output signals are disabled when LR is asserted. |  |

|     |   | disabled when LB is asserted.                                                                                                                                                                                                                                                    |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEN | 3 | Transmit Enable (INPUT) The transmit enable input is used to control the Manchester encoder output. A high level on this input enables the encoders output data path. At the end of a message, a low level on the TEN input line is used to terminate the last bit of a message. |

| MAIVIIV 4      |   | The Manchester input line is used to transfer serial Manchester data into the MEDM from a LAN transceiver.                                                                                                      |  |

|----------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TCLK<br>4U.com | 5 | Transmit Clock (INPUT) The transmit clock input line is used to drive the Manchester Encoder circuit. The MEDM Encoder requires a 50% duty cycle to syncronize the incoming serial bit stream and shift out the |  |

|       |   | encoded Manchester data.                                                                                                    |

|-------|---|-----------------------------------------------------------------------------------------------------------------------------|

| TDATA | 6 | Transmit Data (INPUT) The transmit data Input line is used to transfer serial NRZ data into the MEDM from a LAN controller. |

|       |   |                                                                                                                             |

| GND.      | 8 | Ground (INPUT) 0.0 V reference ground                                                                                                                                                                                         |  |

|-----------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK OUT 9 |   | Clock Output (OUTPUT) The clock output line is a divide by two buffered output derived directly from the crystal oscillator. The clock output line is designed to drive the MEDM TCLK input line and other system components. |  |

|           |   |                                                                                                                                                                                                                               |  |

| CLK1/CLK2 | 10/11 | Crystal Inputs CLK1 and CLK2 (INPUTS) The oscillator is controlled by an external, parallel resonant crystal connected between the CLK1 and CLK2 input lines. If the MEDM is clocked by an external clock, CLK1 should be clocked using a 74S series device. |

|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEADLOLIT | 40    | Manahastar Output (OUTPUT)                                                                                                                                                                                                                                   |

|       |    | The Manchester output line contains the<br>Manchester encoded serial transmit data. This<br>output signal is used to transfer the Manchester<br>data to a LAN tranceiver. |

|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDATA | 14 | Receive Data (OUTPUT) The receive data output line contains the serial                                                                                                    |

|      | _  | Manchester data.                                                                                                                                                                |

|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK | 15 | Receive Clock (OUTPUT) The receive clock output line contains a 1X clock recovered from the incoming Manchester data. Receive data is sampled on the falling edge of the clock. |

| Acc | 16 | VCC (INPUT)<br>+5 volt power supply |

|-----|----|-------------------------------------|

|     |    |                                     |

Mechanical: **(EE)** 田 83 竪 **33** 83 83 3 1923 Off, 14 243048 010. £ 027.= Pigara 7 Mechanical details. (All specifications subject to change will out notice.)

www.DataSheet4U.com

## Electrical characteristics over operating range:

| Maximum ratings                                                   | MEDM5XXX               | MEDM2XXX               |

|-------------------------------------------------------------------|------------------------|------------------------|

| Supply voltage V <sub>cc</sub><br>Input or output voltage applied | +7.0 Vdc<br>5 to +5.5V | +9.0 Vdc<br>3 to +5.5V |

| Storage temperature                                               | -65°C to +150°C        |                        |

| Operating conditions           | Commercial | Military        |

|--------------------------------|------------|-----------------|

| Supply voltage V <sub>cc</sub> | 5.0 ±.25V  | 5.0 ±.5V        |

| Operating temperature ranges:  | 0 to 70°C  | -55°C to +125°C |

| DC characteristics                    |                                                                                                                                                                                                                                     |                                                 | MEDMSXXX               |                                                        |                                                                                                                                                    | MEDM2XXX                                |                                                          |                                                                                                                  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Symbol                                | Parameter                                                                                                                                                                                                                           | Unit                                            | MIN.                   | MAX.                                                   | Test Conditions                                                                                                                                    | MIN.                                    | MAX.                                                     | Test Conditions                                                                                                  |

| VIH VIL LU VOH VOL Lccop L OS VIK CIN | Logical "1" input voltage Logical "0" input voltage Input-low current Input-high current Logical "1" output voltage Logical "0" output voltage Supply Input High Current Output short current Input clamp voltage Input Capacitance | V<br>V<br>μΑ<br>μΑ<br>V<br>mA<br>μΑ<br>mA<br>PF | 2.0<br>2.4<br>-15<br>- | 0.8<br>-200<br>20<br>0.4<br>55<br>-200<br>-100<br>-1.5 | $V_{I} = .5V$ $V_{I} = 2.4V$ $I_{OH} = 3.3 \text{mA}$ $I_{OL} = 10 \text{mA}$ $V_{cc} = 5.25V$ $V_{cc} = 5.5V$ $V_{O} = 0V$ $I_{I} = 18 \text{mA}$ | 2.0<br>-2.0<br>-2.0<br>2.4<br>-2.0<br>- | 0.8<br>+2.0<br>+2.0<br>-4<br>35<br>+2.0<br>-<br>-<br>4.0 | $V_{i} = 0V$ $V_{i} = V_{cc}$ $I_{OH} = 3.4 \text{ mA}$ $I_{OL} = 3.4 \text{ mA}$ $V_{cc} = 5.25$ $V_{i} = 5.25$ |

#### **Encoder timing**

| f <sub>T</sub>    | Encoder transmit-clock frequency and data rate          | MHz | 0  | 50 |                      | . 0 | 15 |                       |

|-------------------|---------------------------------------------------------|-----|----|----|----------------------|-----|----|-----------------------|

| tr/tf             | Encoder-clock rise & fall time                          | NS  |    | 5  | C <sub>L</sub> =10pf |     | 8  | C <sub>L</sub> = 10pf |

| twr               | Reset pulse width                                       | NS  | 15 |    |                      | 100 |    |                       |

| t.                | Serial data setup (data to TCLK rising edge)            | NS  | 10 |    |                      | 10  |    | -                     |

| t <sub>h</sub>    | Serial data hold (TCLK rising edge to data transition)  | NS  | 5  | -  |                      | 5   |    |                       |

| T <sub>e</sub>    | Transmit-enable setup (TEN rising to clock rising edge) | NS  | 50 |    |                      | 50  |    |                       |

| t <sub>pde</sub>  | Transmit clock failing edge to MANOUT delay             | NS  |    | 30 |                      |     | 68 |                       |

| t <sub>rs</sub> . | RESET setup (RESET rising edge to clock rising edge)    | NS  | 50 |    |                      | 100 |    |                       |

#### **Decoder timing**

| f <sub>d</sub>                                     | Decoder data rate & receive clock frequency                   | MHz<br>NS         | 1.0                | 50.0<br>8.0 | See note II C. =10pf   | 1                  | 15<br>8 | See note ① C, =10pf    |

|----------------------------------------------------|---------------------------------------------------------------|-------------------|--------------------|-------------|------------------------|--------------------|---------|------------------------|

| t <sub>ia</sub> /t <sub>ia</sub><br>t <sub>w</sub> | Receive-clock rise & fall time RESET pulse width              | NS                | 15                 |             | Ψ[ΨP.                  | 100                |         |                        |

| t <sub>rs</sub>                                    | RESET setup (RESET rising to first MANIN transition)          | NS                | 10                 |             |                        | 50                 |         | ٠                      |

| et4U. <b>k</b> em                                  | MANIN first transition to receive-clock rising-edge delay     | <sub>Ns</sub> Dat | aSheet4l           | J.com       | • .                    | 12                 | 68      |                        |

| t <sub>edd</sub>                                   | Receive-clock to receive data delay Receive-clock pulse width | NS<br>NS          | 300/f <sub>D</sub> | 10.0        | f <sub>p</sub> in Mb/s | 300/f <sub>D</sub> | 10      | f <sub>D</sub> in Mb/s |

① Guaranteed to work with  $f_D \pm 10\%$  from nominal value. @ TA = 25°C  $V_{cc} = 5.0 \pm .01V$

### Ordering and package information:

| Standard Part Number (MEDM5XXX) | Data Rate | Standard Part Number (MEDM2XXX) | Data Rate |

|---------------------------------|-----------|---------------------------------|-----------|

| MEDM5500                        | 50 Mb/s   | MEDM2150                        | 15 Mb/s   |

| MEDM5400                        | 40 Mb/s   | MEDM2120                        | 12 Mb/s   |

| MEDM5300                        | 30 Mb/s   | MEDM2100                        | 10 Mb/s   |

| MEDM5250                        | 25 Mb/s   | MEDM2050                        | 5 Mb/s    |

| MEDM5200                        | 20 Mb/s   | MEDM2020                        | 2 Mb/s    |

| MEDM5186                        | 18.6 Mb/s | MEDM2010                        | 1 Mb/s    |

MX

To order, specify part number as explained in the following example:

#### Example: MEDM-5203—MX MEDM-5 1. Prefix:-Technitrol MEDM, CMOS LOGIC FAMILY MEDM2 Technitrol MEDM. LOW-POWER SCHOTTKY LOGIC MEDM5 2. Data rate description:

203 20.3 Mb/s

010 1.0 Mb/s (1-15 Mb/s data rates for MEDM 2XXX) (1-50 Mb/s data rates for MEDM 5XXX)

3. Design level:

Standard part; no special customer requirements no digit necessary. A-Z Custom part. Letter assigned at factory. Simply specify a dash (as above) until this letter is assigned.

4. Temperature range and screening:-

Standard part; commercial temperature range of 0-70°C.

Commercial part with in-house burn-in and thermal shock per customer requirements.

Military operating temperature range, -55° to +125°C.

IC screened to MIL-STD-883B.

MX unit with additional burn-in and thermal shock.

ΜZ M unit with in-house burn-in and thermal shock.

# Technitrol

#### WARRANTY

Technitrol warrants for a period of 90 days from the date of shipment that, under normal use and service, its prod-ucts will be free from defects in workmanship and ucts will be free from defects in workmanship and material. Technitrol's sole responsibility under this warranty is, at its option, to repair or replace, without charge, any defective product or part, or to credit buyer for the purchase price of such defective product, provided:

1. Buyer promptly notifies Technitrol of the defect in writing within the warranty period, and

2. The defective product or part is returned to Technitrol with transportation charges prepaid by Buyer, and

Technitrol's examination of such product shall disclose to its satisfaction that said defect exists and has not been caused by misuse, neglect, improper

installation, repair or alteration, or accident.

EXCEPT FOR THE ABOVE WARRANTY AND THE IMPLIED WARRANTY OF TITLE, TECHNITROL MAKES

NO OTHER WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING ANY IMPLIED WARRANTY OF MER-CHANTABILITY OF MEACHANTABILITY OF INPLED WARRANTY OF MEAPURPOSE, TECHNITROL WILL NOT BE LIABLE FOR

INCIDENTIAL OR CONSEQUENTIAL DAMAGES

UNDER ANY CIRCUMSTANCES. DATAS HEEL 4 U. CON