www.DataSheet4U.com

# Technical Manual

# ARM966E-S Microprocessor Core

June 2001 Preliminary

www.DataSheet4U.com

This document is preliminary. As such, it contains data derived from functional simulations and performance estimates. LSI Logic has not verified either the functional descriptions, or the electrical and mechanical specifications using production parts.

Document DB14-000111-00, First Edition (June 2001)

This document describes LSI Logic Corporation's ARM966E-S Microprocessor Core and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1999–2001 by LSI Logic Corporation. All rights reserved.

### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design. G10, GigaBlaze, CoreWare, FlexStream, and Right-First-Time are trademarks or registered trademarks of LSI Logic Corporation.ARM is a registered trademark of ARM Ltd., used under license. All other brand and product names may be trademarks of their respective companies.

EΗ

ii

# Preface

www.DataSheet4U.com

This book is the primary reference and Technical Manual for the ARM966E-S Microprocessor core. It contains a complete functional description of the core and describes the main features of the microarchitecture.

### Audience

This document assumes that you have some familiarity with microprocessors and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the processor for possible use in a system

- Engineers who are designing the processor into a system

# Organization

This document has the following chapters:

- Chapter 1, Introduction, provides an overview of the ARM966E-S Microprocessor core and the LSI Logic CoreWare<sup>®</sup> program.

- Chapter 2, Signal Descriptions, describes all of the external interface signals.

- Chapter 3, Programmer's Model, discusses the memory model and operating modes of the ARM966E-S, and describes its register set.

- Chapter 4, Exception Processing, describes the events that cause the ARM966E-S exceptions and discusses how the ARM966E-S handles them.

- Chapter 5, AHB Interface Unit, describes the operation of the Advanced High-performance Bus Interface Unit.

- Chapter 6, Write Buffer, describes the internal Write Buffer.

- Chapter 7, System Controller, describes the internal-w.DataSheet4U.com Coprocessor 15 block, which the CPU uses to control the Write Buffer and Instruction and Data RAMs.

- Chapter 8, **Tightly Coupled RAM**, describes the two built-in RAMs: the Instruction RAM and the Data RAM.

- Chapter 9, External Coprocessor Interface, describes the external coprocessor interface through which additional on-chip coprocessors connect.

- Chapter 10, Debug, describes the operation of the ARM966E-S debug interface, which is based on the IEEE Std. 1149.1-1990.

- Chapter 11, Test Methodology, discusses the available test methods.

- Appendix A, **ARM9E-S Enhanced Instructions**, describes the enhancements to the ARM9E-S instruction set.

### **Related Publications**

ARM946E-S Microprocessor Core with Cache Technical Manual, Document No. DB14-000104-00

Standard Test Access Port and Boundary Scan Architecture, IEEE Standard 1149.1-1990

ARM940T Datasheet, ARM Ltd., Document No. ARM DDI 0092A-04

ARM9 Architecture Reference Manual, ARM Ltd., Document No. ARM DDI 0100

ARM9E-S Technical Reference Manual, ARM Ltd., Document No. ARM DDI 0165

ARM Hurricane Engineering Specification

AHB Specification (Rev. 2.0), ARM Ltd., Document No. ARM IHI 0011

### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word assert means to drive a signal true or active. The word deassert means to drive a signal false or inactive. www.DataSheet4U.com

Hexadecimal numbers are indicated by the prefix "0x" ---for example, 0x32CF. Binary numbers are indicated by the prefix "0b" - for example, 0b0011.0010.1100.1111.

www.DataSheet4U.com

# Contents

| Chapter 1 | Intro | duction    |                                     |      |

|-----------|-------|------------|-------------------------------------|------|

|           | 1.1   | Overvie    | W                                   | 1-1  |

|           | 1.2   | Block D    | Diagram Description                 | 1-2  |

|           |       | 1.2.1      | ARM9E-S Processor Core              | 1-3  |

|           |       | 1.2.2      | System Controller                   | 1-4  |

|           |       | 1.2.3      | CP15 System Control Coprocessor     | 1-4  |

|           |       | 1.2.4      | Address Decoders                    | 1-4  |

|           |       | 1.2.5      | Instruction and Data RAMs           | 1-4  |

|           |       | 1.2.6      | DMA Interface                       | 1-5  |

|           |       | 1.2.7      | AHB Interface Unit and Write Buffer | 1-5  |

|           |       | 1.2.8      | External Coprocessor Interface      | 1-5  |

|           |       | 1.2.9      | JTAG and Debug Port                 | 1-5  |

|           |       | 1.2.10     | Embedded Trace Module Interface     | 1-6  |

|           | 1.3   | Feature    | Summary                             | 1-6  |

|           | 1.4   | CoreWa     | are Program                         | 1-6  |

| Chapter 2 | Sigr  | al Desci   | riptions                            |      |

|           | 2.1   | AHB In     | terface                             | 2-3  |

|           | 2.2   | Coproc     | essor Interface                     | 2-8  |

|           | 2.3   | Instruct   | ion RAM Signals                     | 2-10 |

|           | 2.4   | Data R     | AM Signals                          | 2-10 |

|           | 2.5   | DMA S      | ignals                              | 2-12 |

|           | 2.6   | Debug      | Signals                             | 2-14 |

|           | 2.7   | ETM In     | terface Signals                     | 2-16 |

|           | 2.8   | Miscella   | aneous Signals                      | 2-20 |

|           | 2.9   | Initializa | ation Control Signals               | 2-21 |

|           | 2.10  | ATPG S     | Scan Control Signals                | 2-21 |

| Chapter 3 | Pro  | grammei  | 's Model                                        |                   |

|-----------|------|----------|-------------------------------------------------|-------------------|

|           | 3.1  | -        | he Programmer's Model                           | ieet4U.com<br>3-1 |

|           | 3.2  |          | bort Model                                      | 3-2               |

|           | 3.3  | Data T   | /pes                                            | 3-2               |

|           | 3.4  |          | sor Modes                                       | 3-3               |

|           | 3.5  | CP15 I   | nstruction Format                               | 3-4               |

|           | 3.6  | Memor    | у Мар                                           | 3-5               |

|           | 3.7  | Registe  | ers                                             | 3-5               |

|           |      | 3.7.1    | CPU Registers                                   | 3-6               |

|           |      | 3.7.2    | CP15 Registers                                  | 3-9               |

| Chapter 4 | Exce | ption Pr | ocessing                                        |                   |

|           | 4.1  | Overvie  | 9W                                              | 4-1               |

|           | 4.2  | Except   | ion Flow                                        | 4-2               |

|           | 4.3  | Except   | ion Descriptions                                | 4-4               |

|           |      | 4.3.1    | Reset Exception                                 | 4-4               |

|           |      | 4.3.2    | Undefined Instruction Execution                 | 4-4               |

|           |      | 4.3.3    | Software Interrupt Exception                    | 4-5               |

|           |      | 4.3.4    | Prefetch Abort (Instruction Fetch Memory Abort) | 4-5               |

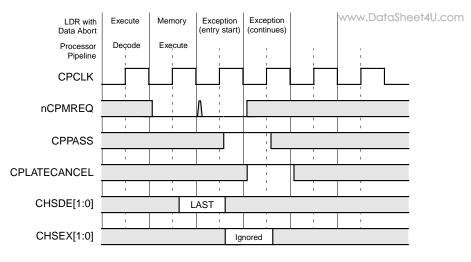

|           |      | 4.3.5    | Data Abort (Data Access Memory Abort)           | 4-6               |

|           |      | 4.3.6    | IRQ (Interrupt Request) Exception               | 4-7               |

|           |      | 4.3.7    | FIQ (Fast Interrupt Request) Exception          | 4-7               |

| Chapter 5 | AHB  | Interfac | e Unit                                          |                   |

|           | 5.1  | Overvie  | 9W                                              | 5-1               |

|           | 5.2  | AHB In   | terface Signals                                 | 5-2               |

|           |      | 5.2.1    | Transfer Types                                  | 5-3               |

|           |      | 5.2.2    | Burst Types                                     | 5-4               |

|           |      | 5.2.3    | Control Signals                                 | 5-5               |

|           |      | 5.2.4    | Data Buses                                      | 5-8               |

|           |      | 5.2.5    | Endianess                                       | 5-10              |

|           | 5.3  | AHB C    | locking                                         | 5-11              |

|           | 5.4  |          | peration                                        | 5-11              |

|           | 5.5  | Basic 7  | ransfers                                        | 5-12              |

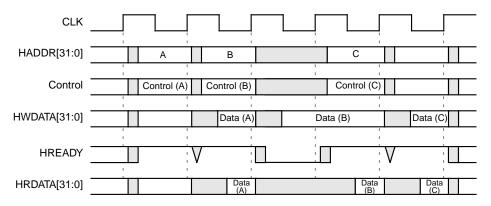

|           | 5.6  | Burst C  | Operations                                      | 5-15              |

|           |      | 5.6.1    | Early Burst Termination                         | 5-15              |

|           |       | 5.6.2 Burst Operation Example                          | 5-15 |

|-----------|-------|--------------------------------------------------------|------|

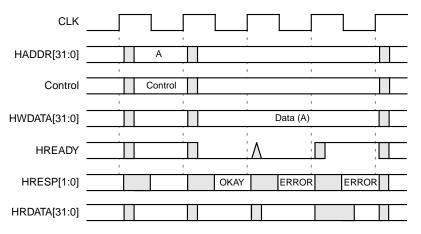

|           | 5.7   | Slave Transfer Responses                               | 5-16 |

|           |       | 5.7.1 Two-Cycle Response                               | 5-17 |

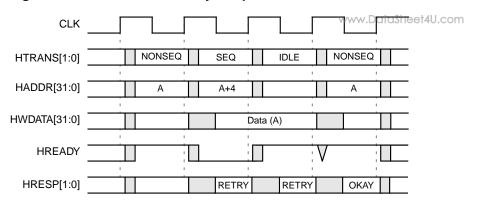

|           |       | 5.7.2 Error Response                                   | 5-18 |

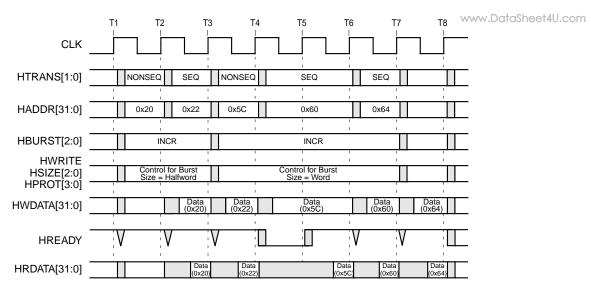

|           |       | 5.7.3 Retry Responses                                  | 5-19 |

|           |       | 5.7.4 Split Responses                                  | 5-19 |

| Chapter 6 | Write | e Buffer                                               |      |

|           | 6.1   | Introduction                                           | 6-1  |

|           | 6.2   | Normal Operation                                       | 6-2  |

|           | 6.3   | Full Write Buffer                                      | 6-2  |

|           | 6.4   | Unbuffered Writes                                      | 6-3  |

|           | 6.5   | Read-Lock-Write                                        | 6-3  |

|           | 6.6   | Read to Write-Posted Address                           | 6-3  |

|           | 6.7   | Write Buffer Nonrecoverable Error and Abort Conditions | 6-3  |

| Chapter 7 | Syst  | em Controller                                          |      |

|           | 7.1   | Operation                                              | 7-1  |

|           | 7.2   | Clock Control                                          | 7-2  |

| Chapter 8 | Tigh  | tly Coupled RAM                                        |      |

|           | 8.1   | Tightly Coupled Memory (TCM) Overview                  | 8-1  |

|           | 8.2   | ARM966E-S SRAM Requirements                            | 8-1  |

|           | 8.3   | Enabling the SRAM                                      | 8-2  |

|           |       | 8.3.1 Using INITRAM to Enable SRAM                     | 8-2  |

|           |       | 8.3.2 Using CP15 Control Register to Enable SRAM       | 8-3  |

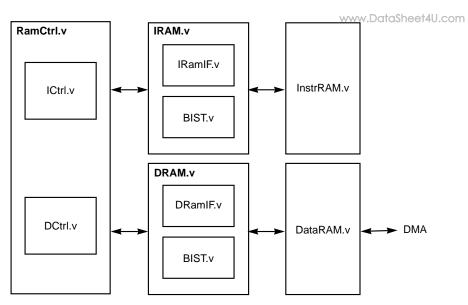

|           | 8.4   | ARM966E-S SRAM Wrapper                                 | 8-5  |

|           | 8.5   | Example SRAM Interfaces                                | 8-6  |

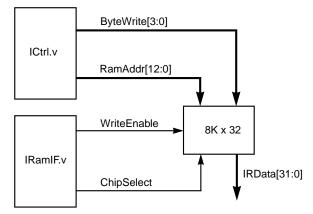

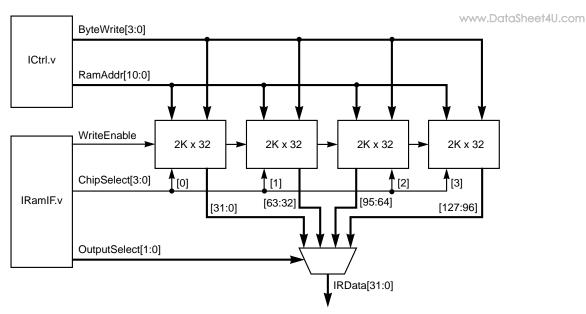

|           |       | 8.5.1 ONESEGX32                                        | 8-7  |

|           |       | 8.5.2 FOURSEGX32                                       | 8-7  |

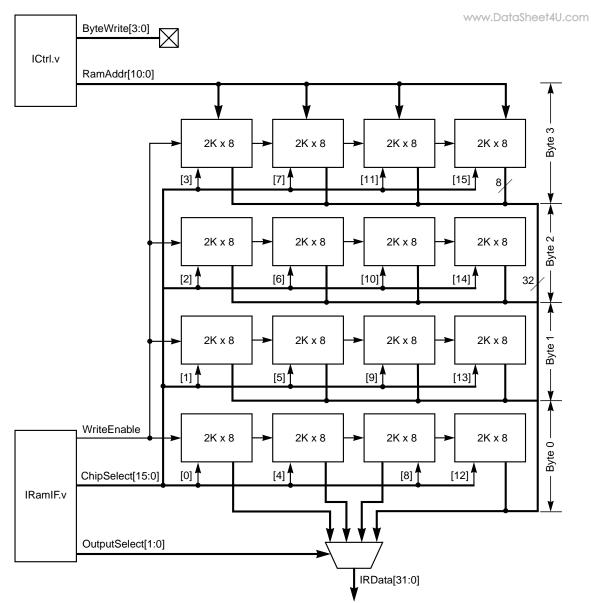

|           |       | 8.5.3 FOURSEGX8                                        | 8-8  |

| Chapter 9 | Exte  | rnal Coprocessor Interface                             |      |

| -         | 9.1   | Overview                                               | 9-1  |

|           |       |                                                        | ~ ~  |

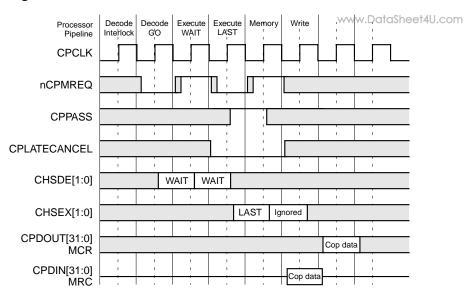

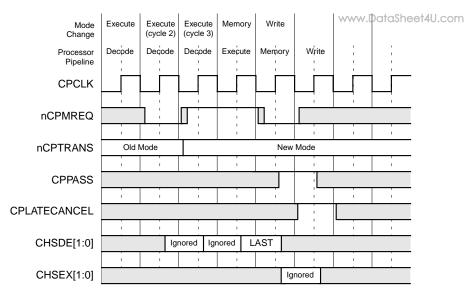

|           | 9.2   | Coprocessor Instruction Execution                      | 9-2  |

www.DataSheet4U.com

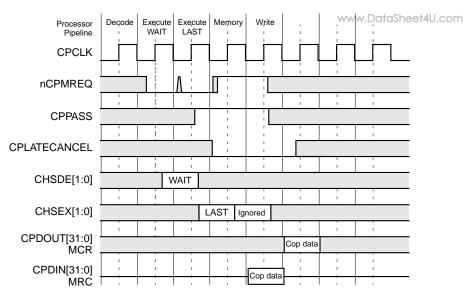

|            |       | 9.2.2    | MCR/MRC Instructions                        | 9-5           |

|------------|-------|----------|---------------------------------------------|---------------|

|            |       | 9.2.3    | Interlocked MCRs                            | DataSheet4U.c |

|            |       | 9.2.4    | CDP Instructions                            | 9-7           |

|            | 9.3   | Privileg | ed Instructions                             | 9-8           |

|            | 9.4   | Stalling | and Interrupts                              | 9-9           |

| Chapter 10 | Debu  | g        |                                             |               |

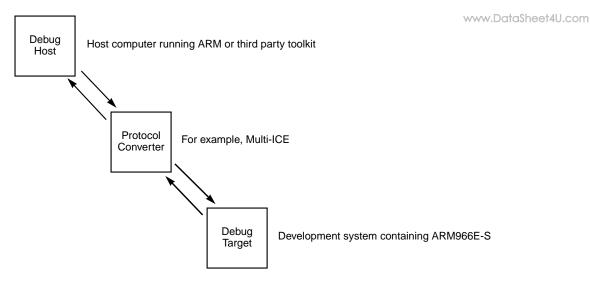

|            | 10.1  | Debug    | Systems                                     | 10-1          |

|            |       | 10.1.1   | The Debug Host                              | 10-2          |

|            |       | 10.1.2   | The Protocol Converter                      | 10-2          |

|            |       | 10.1.3   | Debug Target                                | 10-3          |

|            | 10.2  | About t  | he Debug Interface                          | 10-4          |

|            |       | 10.2.1   | Stages of Debug                             | 10-5          |

|            |       | 10.2.2   | Clocks                                      | 10-5          |

|            | 10.3  | Scan C   | hain 15                                     | 10-6          |

|            | 10.4  | Breakpo  | pints, Watchpoints, and External Debug Requ | ests 10-8     |

|            |       | 10.4.1   | Entry into Debug State on Breakpoint        | 10-9          |

|            |       | 10.4.2   | Breakpoints and Exceptions                  | 10-10         |

|            |       | 10.4.3   | Watchpoints                                 | 10-11         |

|            |       | 10.4.4   | Watchpoints and Exceptions                  | 10-13         |

|            |       | 10.4.5   | Debug Request                               | 10-13         |

|            |       | 10.4.6   | Actions of the ARM9E-S Core in Debug Sta    | ate 10-13     |

|            | 10.5  | ARM9E    | -S Clock Domains                            | 10-14         |

|            | 10.6  | Determ   | ining the Core and System States            | 10-14         |

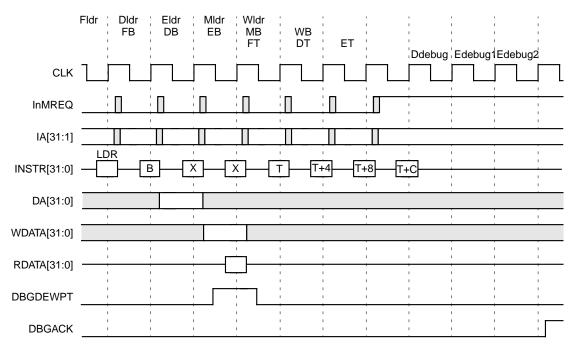

|            | 10.7  | About t  | he EmbeddedICE-RT Logic                     | 10-14         |

|            | 10.8  | Disablir | ng the EmbeddedICE-RT Logic                 | 10-16         |

|            | 10.9  | The De   | bug Communications Channel                  | 10-16         |

|            |       | 10.9.1   | Debug Communication Channel Registers       | 10-17         |

|            |       | 10.9.2   | Debug Communications Channel Status         |               |

|            |       |          | Register                                    | 10-17         |

|            |       | 10.9.3   | Communications Channel Monitor Mode         |               |

|            |       |          | Debug Status Register                       | 10-18         |

|            |       | 10.9.4   | Using the Communications Channel            | 10-19         |

|            | 10.10 | Real-Ti  | me Debug                                    | 10-20         |

Chapter 11

Test Methodology

11.1 Scan Insertion

11-1

<del>www.DataSheet4U.c</del>om

| Appendix A | ARM9E-S Enhanced Instructions |                                                 |      |  |  |

|------------|-------------------------------|-------------------------------------------------|------|--|--|

|            | Inde                          | x                                               |      |  |  |

|            | Cust                          | omer Feedback                                   |      |  |  |

| Figures    |                               |                                                 |      |  |  |

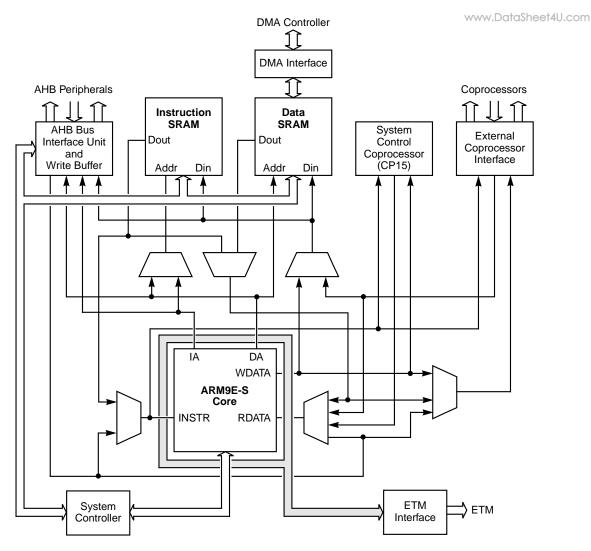

|            | 1.1                           | ARM966E-S Block Diagram                         | 1-3  |  |  |

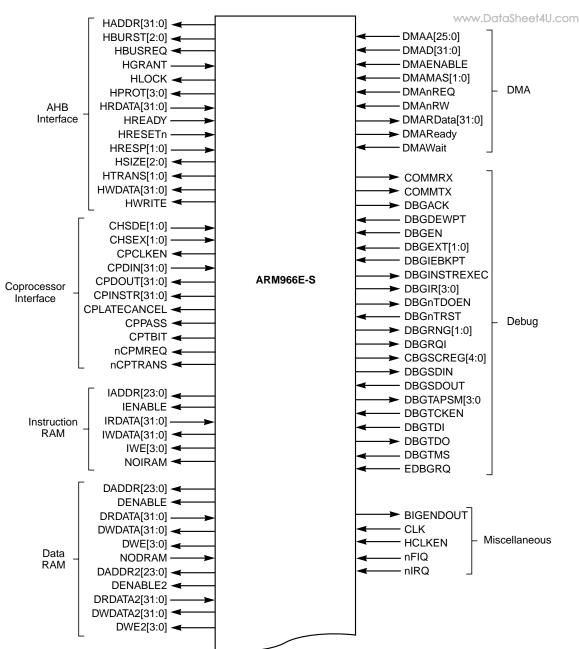

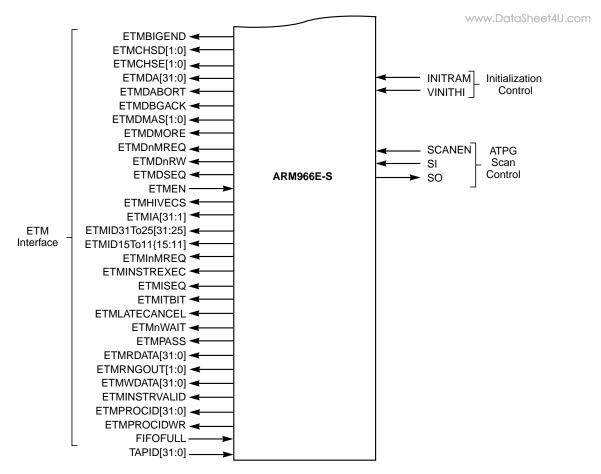

|            | 2.1                           | ARM966E-S Signal Diagram                        | 2-2  |  |  |

|            | 3.1                           | Coprocessor Instruction Format                  | 3-4  |  |  |

|            | 3.2                           | ARM966E-S Memory Map                            | 3-5  |  |  |

|            | 3.3                           | CPU Register Organization                       | 3-6  |  |  |

|            | 3.4                           | Program Status Registers (CPSR and SPSR) Format | 3-8  |  |  |

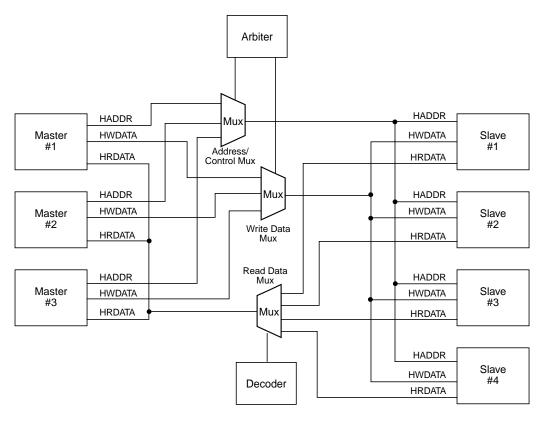

|            | 5.1                           | Multiplexer Interconnection                     | 5-2  |  |  |

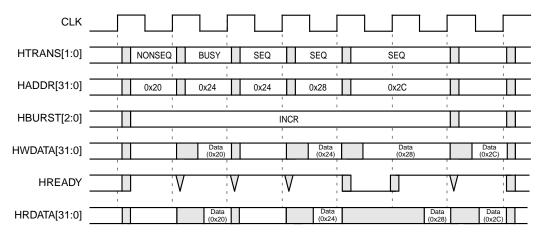

|            | 5.2                           | Transfer Type Examples                          | 5-4  |  |  |

|            | 5.3                           | AHB Clock Relationships                         | 5-11 |  |  |

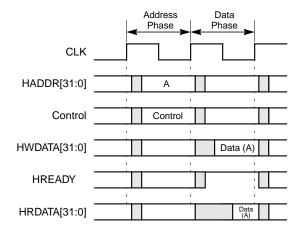

|            | 5.4                           | Simple Transfer                                 | 5-13 |  |  |

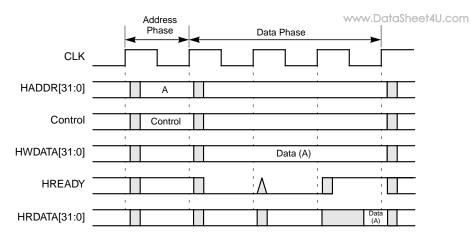

|            | 5.5                           | Transfer with Wait States                       | 5-14 |  |  |

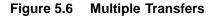

|            | 5.6                           | Multiple Transfers                              | 5-14 |  |  |

|            | 5.7                           | Incrementing Bursts with Undefined Lengths      | 5-16 |  |  |

|            | 5.8                           | Transfer with Retry Response                    | 5-18 |  |  |

|            | 5.9                           | Error Response                                  | 5-18 |  |  |

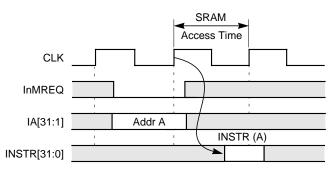

|            | 8.1                           | SRAM Read Cycle                                 | 8-2  |  |  |

|            | 8.2                           | ARM966E-S SRAM Hierarchy                        | 8-6  |  |  |

|            | 8.3                           | ONESEGX32 Interface                             | 8-7  |  |  |

|            | 8.4                           | FOURSEGX32 Interface                            | 8-8  |  |  |

|            | 8.5                           | FOURSEGX8 Interface                             | 8-10 |  |  |

|            | 9.1                           | CLK and CPCLKEN Timing                          | 9-2  |  |  |

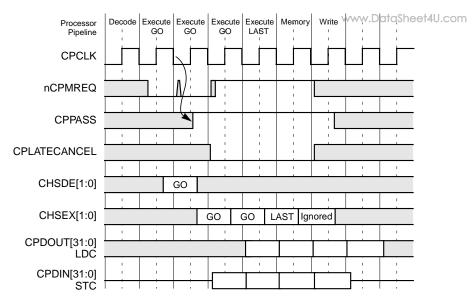

|            | 9.2                           | LDC/STC Cycle Timing                            | 9-3  |  |  |

|            | 9.3                           | MCR/MRC Cycle Timing                            | 9-6  |  |  |

|            | 9.4                           | Interlocked MCR                                 | 9-7  |  |  |

|            | 9.5                           | Late Cancelled CDP                              | 9-8  |  |  |

|            | 9.6                           | Privileged Instructions                         | 9-9  |  |  |

|            | 9.7                           | Stalling and Interrupts                         | 9-10 |  |  |

| 10.1         | Typical Debug System                              | 10-2                              |

|--------------|---------------------------------------------------|-----------------------------------|

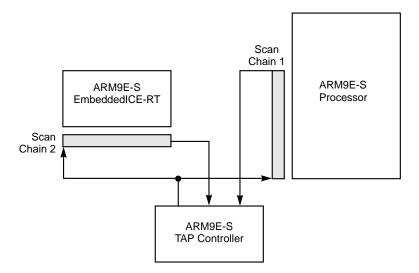

| 10.2         | ARM9E-S Processor and Debug Logic                 | <mark>10-3</mark><br>aSheet4U.com |

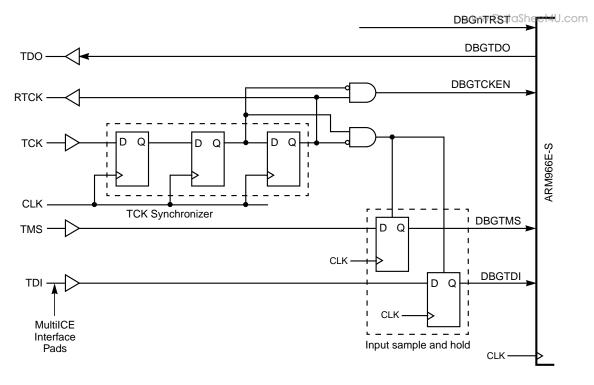

| 10.3         | Clock Synchronization Logic                       | 10-6                              |

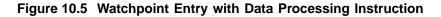

| 10.4         | Breakpoint Timing                                 | 10-10                             |

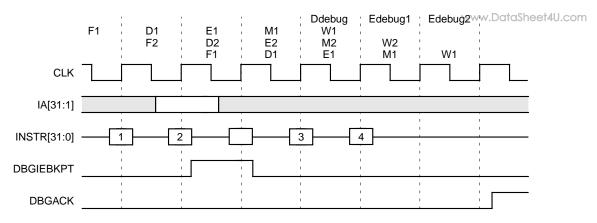

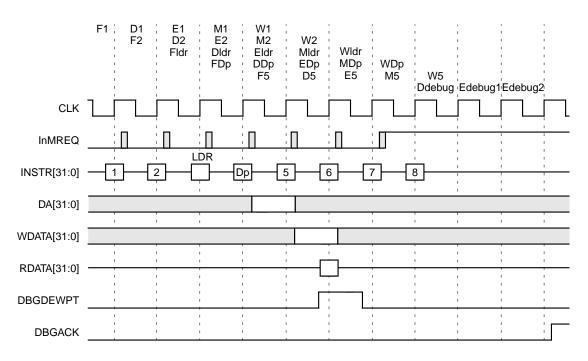

| 10.5         | Watchpoint Entry with Data Processing Instruction | 10-11                             |

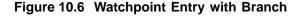

| 10. <b>6</b> | Watchpoint Entry with Branch                      | 10-12                             |

| 10.7         | The ARM9E-S, TAP Controller, and EmbeddedICE-RT   | 10-15                             |

| 10.8         | Debug Communications Channel Status Register      | 10-17                             |

| 10.9         | Coprocessor 14 Debug Status Register Format       | 10-18                             |

# Tables

| 3.1  | Supported Data Types                                  | 3-2   |

|------|-------------------------------------------------------|-------|

| 3.2  | ARM9E-S Processor Modes                               | 3-3   |

| 3.3  | Instruction Format Field Descriptions                 | 3-4   |

| 3.4  | Mode Bits                                             | 3-9   |

| 3.5  | CP15 Register Map                                     | 3-9   |

| 3.6  | Core Control Instructions                             | 3-12  |

| 3.7  | Register 13, Trace Process Identifier                 | 3-14  |

| 3.8  | CP15 RAMBIST Register Map                             | 3-14  |

| 4.1  | Exception Processing Modes                            | 4-2   |

| 4.2  | Exception Priority Order                              | 4-2   |

| 5.1  | Transfer Type Encoding                                | 5-3   |

| 5.2  | Burst Signal Encoding                                 | 5-5   |

| 5.3  | Size Encoding                                         | 5-6   |

| 5.4  | Protection Signal Encoding                            | 5-7   |

| 5.5  | Active Byte Lanes for a 32-Bit Little-Endian Data Bus | 5-9   |

| 5.6  | Active Byte Lanes for a 32-Bit Big-Endian Data Bus    | 5-10  |

| 10.1 | Scan Chain 15 Addressing Mode Bit Order               | 10-6  |

| 10.2 | Mapping of Scan Chain 15 Address Field to CP15        |       |

|      | Registers                                             | 10-7  |

| 10.3 | Debug State Figure Notations                          | 10-9  |

| 10.4 | CP14 Register Map                                     | 10-17 |

# Chapter 1 Introduction

This chapter introduces the ARM966E-S microprocessor core. This chapter contains the following sections:

- Section 1.1, "Overview"

- Section 1.2, "Block Diagram Description"

- Section 1.3, "Feature Summary"

- Section 1.4, "CoreWare Program"

# 1.1 Overview

The ARM966E-S microprocessor core is a synthesizable macrocell that integrates the ARM9E-S 32-bit processor, an instruction RAM, a data RAM, a write buffer, and an AHB bus interface.

The ARM966E-S implements the ARM architecture v5T, which supports both the 32-bit ARM and 16-bit Thumb instruction sets, allowing you to trade off between high performance and high code density. Additionally the ARM9E-S processor core provides an ARM9E-S instruction extension and an enhanced multiplier for increased DSP performance.

The AHB bus interface eases connection to cached and SRAM-based memory systems.

The ARM966E-S supports the ARM debug architecture and includes logic to assist in both hardware and software debug. It supports nonstopping hardware debug, which allows critical exception handlers to execute while debugging the system. The ARM966E-S provides real-time trace and supports external coprocessors.

# 1.2 Block Diagram Description

Figure 1.1 shows a block diagram of the ARM966E-S. The main functional blocks are:

- ARM9E-S Processor Core

- System Controller

- CP15 System Control Coprocessor

- Instruction RAM

- Data RAM

- DMA Interface to Data RAM

- Address Decoders

- Write Buffer

- AHB Interface

- External Coprocessor Interface

- JTAG and Debug Port

- Embedded Trace Module Interface

These modules are briefly described following the block diagram. They are described in more detail in the subsequent chapters of this manual.

# 1.2.1 ARM9E-S Processor Core

The ARM9E-S processor core has a Harvard bus architecture with separate instruction and data interfaces. This design allows concurrent instruction and data accesses, and greatly reduces the cycles per instruction of the processor. For optimal performance, single-cycle memory accesses for both interfaces are required, although the core can be stalled for nonsequential accesses or slower memory systems.

The processor is implemented using a five-stage pipeline:

• Instruction Fetch (F)

www.DataSheet4U.com

- Instruction Decode (D)

- Execute (E)

- Data Memory Access (M)

- Register Write (W)

ARM implementations are fully interlocked, so that software functions identically across different implementations without concern for how the pipeline is affected.

# 1.2.2 System Controller

The System Controller oversees the interactions between the Instruction RAM, Data RAM, and the Bus Interface Unit. It controls internal arbitration between the blocks and stalls the appropriate blocks when required.

# 1.2.3 CP15 System Control Coprocessor

The processor core uses a set of registers in the CP15 Coprocessor to control the functionality of the RAMs and the Write Buffer. These registers are accessed using the coprocessor instructions MCR and MRC.

# 1.2.4 Address Decoders

The address decoders determine whether a memory request accesses the internal RAM or the Advanced High-Performance Bus (AHB) interface. The address decoders provide a hit/miss indication to the System Controller, which then either stalls the core if an AHB read or unbuffered write access is required or allows execution to continue if the access hits the RAM or is a buffered write.

# 1.2.5 Instruction and Data RAMs

The ARM966E-S incorporates internal instruction and data memories to allow high-speed operation without incurring the performance penalty of accessing the system bus or the die size penalty of a cached processor. The Instruction and Data RAMs each consist of blocks of ASIC library compiled RAM. The RAM sizes can be of any size up to 64 Mbytes. The instruction and data memories can have unique sizes.

# 1.2.6 DMA Interface

The Direct Memory Access (DMA) interface allows an external device direct access to the ARM966E-S Data RAM. If a single-port Data RAM is used, then the DMA interface stalls the ARM966E-S microprocessor core during the DMA transfer. If a dual-port Data RAM is used, then the DMA interface does not stall the ARM966E-S during the DMA transfer.

# 1.2.7 AHB Interface Unit and Write Buffer

The AHB is a new generation of AMBA bus, which meets the requirements of high-performance synthesizable designs. The AHB Interface Unit arbitrates between the external bus transaction sources within the ARM966E-S. It stalls all other accesses until the current request has been completed. The AHB Interface Unit supports the following types of transactions: burst transfers, split transactions, single-cycle bus master handovers, single clock edge operations, and non-3-state implementations.

The Write Buffer is a 12-entry FIFO. It increases system performance.

# 1.2.8 External Coprocessor Interface

The ARM966E-S supports the connection of coprocessors through the external coprocessor interface. All types of ARM coprocessor instructions are supported. Coprocessors determine the instructions they need to execute using a pipeline follower in the coprocessor.

# 1.2.9 JTAG and Debug Port

The ARM966E-S debug interface is based on IEEE Std. 1149.1-1990. It can stop the processor core on a given instruction fetch (breakpoint), data access (watchpoint), or external debug request. The JTAG-style serial interface can serially insert instructions into the pipeline of the core without using the external data bus.

www.DataSheet4U.com

# 1.2.10 Embedded Trace Module Interface

This interface connects to an external Embedded Trace Module (ETM). The ETM provides a high-speed port for tracing of the processor core in real time.

# 1.3 Feature Summary

This section lists the key features of the ARM966E-S microprocessor core:

- ARM9E-S processor core

- Instruction and Data RAMs with independent sizes up to 64 Mbytes

- DMA Interface to Data RAM

- ARM Advanced High-Performance Bus (AHB) interface unit with write buffer

- Write buffer depth: 16 words at up to four addresses

- Burst transfers

- Split transactions

- External coprocessor interface

- System controller arbitrates between instruction and data memories and AHB

- Embedded trace module provides a real-time trace capability

# 1.4 CoreWare Program

An LSI Logic core is a fully defined, optimized, and reusable block of logic. It supports industry-standard functions and has predefined timing and layout. The core is also an encrypted RTL simulation model for a wide range of VHDL and Verilog simulators.

The CoreWare library contains an extensive set of complex cores for the storage, communications, consumer, and computer markets. The library consists of high-speed interconnect functions such as the GigaBlaze<sup>®</sup> G10<sup>®</sup> Core, DSPs, MPEG-2 decoders, a PCI core, and many more.

The library also includes megafunctions or building blocks, which provide useful functions for developing a system on a chip. Through the CoreWare program, you can create a system on a chip uniquely suited to your applications.

Each core has an associated set of deliverables, including:

- Encrypted RTL or C simulation models for both Verilog and VHDL environments

- A System Verification Environment (SVE) for RTL-based simulation

- Netlists for full timing simulation

- Complete documentation

- LSI Logic FlexStream<sup>®</sup> design support

The LSI Logic FlexStream design solution provides seamless connectivity between products from leading Electronic Design Automation (EDA) vendors and the LSI Logic manufacturing environment. Standard interfaces for formats and languages such as VHDL, Verilog, Waveform Generation Language (WGL), Physical Design Exchange Format (PDEF), and Standard Delay Format (SDF) allow a wide range of tools to interoperate within the LSI Logic FlexStream design environment. In addition to design capabilities, full scan Automatic Test Pattern Generation (ATPG) tools and LSI Logic's specialized test solutions can be combined to provide high-fault coverage test programs that assure a fully functional design.

Because your design requirements are unique, LSI Logic is flexible in working with you to develop your system-on-a-chip CoreWare design. Three different work relationships are available:

- You provide LSI Logic with a detailed specification and LSI Logic performs all design work.

- You design some functions while LSI Logic provides you with the cores and megafunctions, and LSI Logic completes the integration.

- You perform the entire design and integration, and LSI Logic provides the core and associated deliverables.

Whatever the work relationship, LSI Logic's advanced CoreWare methodology and ASIC process technologies consistently produce Right-First-Time<sup>™</sup> silicon.

www.DataSheet4U.com

# Chapter 2 Signal Descriptions

This chapter describes the external signals of the ARM966E-S microprocessor core. The descriptions are categorized according to the interface. The signal descriptions are listed alphabetically by mnemonic within each interface.

In the descriptions that follow, the verb *assert* means to drive TRUE or active. The verb *deassert* means to drive FALSE or inactive.

This chapter contains the following sections:

- Section 2.1, "AHB Interface"

- Section 2.2, "Coprocessor Interface"

- Section 2.3, "Instruction RAM Signals"

- Section 2.4, "Data RAM Signals"

- Section 2.5, "DMA Signals"

- Section 2.6, "Debug Signals"

- Section 2.7, "ETM Interface Signals"

- Section 2.8, "Miscellaneous Signals"

- Section 2.9, "Initialization Control Signals"

- Section 2.10, "ATPG Scan Control Signals"

Figure 2.1 provides a signal summary for the ARM966E-S.

## Figure 2.1 ARM966E-S Signal Diagram

# Figure 2.1 ARM966E-S Signal Diagram (cont.)

# 2.1 AHB Interface

HADDR[31:0] Address Bus Out The ARM966E-S drives the AHB address on HADDR[31:0].

# HBURST[2:0] Burst Type

Output

Input

This output indicates whether the transfer forms part of a burst. The ARM966E-S generates burst types of SINGLE and INCR only.

| HBURST[2:0] | Burst Type | Description                                 |

|-------------|------------|---------------------------------------------|

| 000         | SINGLE     | Single transfer                             |

| 001         | INCR       | Incrementing burst of<br>unspecified length |

| 010–111     | Reserved   | Not supported                               |

HBUSREQ Bus Request Output HBUSREQ is a signal from the ARM966E-S to the bus arbiter. A HIGH in this output indicates that the core requires the bus.

# HGRANT Bus Grant

A HIGH on this signal indicates the ARM966E-S is currently the highest priority master. Ownership of the address/control signals changes at the end of a transfer when HREADY is HIGH. A master gets access to the bus when both HREADY and HGRANT are HIGH.

# HLOCK Locked Transfer Output When HLOCK is HIGH, it indicates that the ARM966E-S requires locked access to the bus, and that no other masters should be granted the bus until HLOCK is LOW. HLOCK is asserted when the ARM966E-S is executing the SWAP instruction.

HPROT[3:0] Protection Control Output This output provides additional information about a bus access. HPROT[3:0] are primarily intended for use by any module that implements some level of protection.

www.DataSheet4U.com

The signals indicate whether the transfer is an opcode fetch or data access, and whether the transfer is a supervisor mode access or user mode access.

| HPROT3<br>Cacheable | HPROT2<br>Bufferable | HPROT1<br>Supervisor | HPROT0<br>Data/Opcode | e Description     |

|---------------------|----------------------|----------------------|-----------------------|-------------------|

| _                   | -                    | -                    | 0                     | Opcode Fetch      |

| _                   | -                    | -                    | 1                     | Data Access       |

| _                   | -                    | 0                    | _                     | User Access       |

| _                   | -                    | 1                    | _                     | Supervisor Access |

| -                   | 0                    | -                    | _                     | Not Bufferable    |

| -                   | 1                    | -                    | _                     | Bufferable        |

| 0                   | -                    | -                    | _                     | Not Cacheable     |

Note that for the ARM966E-S, HPROT3 is forced LOW (noncacheable).

### HRDATA[31:0] Read Data Bus

This bus transfers data from the bus slaves to the ARM966E-S during read operations. The ARM966E-S has a 32-bit wide data bus. The width can be easily extended outside the core to allow for higher bandwidth operation.

# **HREADY** Transfer Done Input When HIGH, the HREADY signal indicates the transfer on the bus has finished. Drive this signal LOW to extend a transfer.

Note: Slaves on the bus require HREADY to be both an input and an output.

# HRESETn Reset

This input is the active-LOW system reset.

### HRESP[1:0] Transfer Response Input HRESP[1:0] provide additional information on the status of a transfer. When a slave must insert a number of wait

Input

Input

states prior to decoding what response to give, then it must drive the response to OKAY.

|            | Transfer | <b>-</b>                                                                                                                                                                                                                                                                         |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HRESP[1:0] | Response | Description                                                                                                                                                                                                                                                                      |

| 00         | OKAY     | When HREADY is HIGH, the transfer has completed.                                                                                                                                                                                                                                 |

| 01         | ERROR    | This response shows an error<br>has occurred. The error<br>condition must be signaled to th<br>bus master so that it is aware th<br>transfer was unsuccessful.                                                                                                                   |

|            |          | A two-cycle response is require for an Error condition.                                                                                                                                                                                                                          |

| 10         | RETRY    | The Retry response shows the<br>transfer is not complete, so the<br>bus master should retry the<br>transfer. The master will continu<br>to retry the transfer until it<br>completes.                                                                                             |

|            |          | A two-cycle RETRY response i required.                                                                                                                                                                                                                                           |

| 11         | SPLIT    | The Split response indicates th<br>transfer has not yet completed<br>successfully. The bus master<br>must retry the transfer when it i<br>next granted access to the bus<br>The slave will request access t<br>the bus on behalf of the master<br>when the transfer can complete |

|            |          | A two-cycle SPLIT response is required.                                                                                                                                                                                                                                          |

## HSIZE[2:0] Transfer Size Output This output indicates the size of the transfer, which is typically byte (8 bits), halfword (16 bits), or word (32 bits).

| HSIZE[2:0] | Transfer Size | Description |

|------------|---------------|-------------|

| 000        | 8 bits        | Byte        |

| 001        | 16 bits       | Halfword    |

| 010        | 32 bits       | Word        |

| 011–111    | Reserved      |             |

# HTRANS[1:0] Transfer Type Out

Output

This output indicates the current transfer type.

|             |               | www.Datasheet4u.                                                                                                                                                                                                                                                                                                                                                              |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HTRANS[1:0] | Transfer Type | Description                                                                                                                                                                                                                                                                                                                                                                   |

| 00          | Idle          | No data transfer required.                                                                                                                                                                                                                                                                                                                                                    |

| 01          | Busy          | Used to insert an idle cycle<br>in the middle of a burst of<br>transfers.                                                                                                                                                                                                                                                                                                     |

| 10          | Nonsequential | Indicates first transfer of a burst or single transfer.                                                                                                                                                                                                                                                                                                                       |

| 11          | Sequential    | The control information is<br>identical to the previous<br>transfer. The address is<br>equal to the address of the<br>previous transfer plus the<br>size (in bytes). For<br>wrapping bursts, the<br>address of the transfer<br>wraps at the address<br>boundary equal to the size<br>(in bytes) multiplied by the<br>number of beats in the<br>transfer (either 4, 8, or 16). |

### HWDATA[31:0]

### Output

Write Data Bus This bus transfers data from the master to the bus slaves during write operations. The width can be extended external to the core to allow for higher bandwidth operation.

#### HWRITE **Transfer Direction Out** Output When HWRITE is HIGH, the transfer is a write. When HWRITE is LOW, the transfer is a read.

# 2.2 Coprocessor Interface

www.DataSheet4U.com

#### CHSDE[1:0] Coprocessor Handshake Decode Input These inputs are the handshake signals from the decode stage of the coprocessor's pipeline follower.

| CHSDE[1:0] | Encoding |

|------------|----------|

| 10         | ABSENT   |

| 00         | WAIT     |

| 01         | GO       |

| 11         | LAST     |

#### CHSEX[1:0] **Coprocessor Handshake Execute** Input

These inputs are the handshake signals from the execute stage of the coprocessor's pipeline follower.

| CHSEX[1:0] | Encoding |

|------------|----------|

| 10         | ABSENT   |

| 00         | WAIT     |

| 01         | GO       |

| 11         | LAST     |

|            |          |

# Output

**Coprocessor Clock Enable** This clock enable controls the timing of the coprocessor interface. It is used in conjunction with CLK to effectively run the coprocessor at a higher frequency than the data bus.

CPDIN[31:0] **Coprocessor Data In** Input This 32-bit bus is the coprocessor data bus for transferring MRC and STC data from the coprocessor to the ARM966E-S.

# CPDOUT[31:0]

CPCLKEN

### **Coprocessor Data Out**

Output

This 32-bit bus is the coprocessor data bus for transferring data to the coprocessor.

# **CPINSTR[31:0]**

# **Coprocessor Instruction**

Output

This 32-bit bus is the coprocessor instruction data bus for transferring instructions to the pipeline follower in the coprocessor.

# **CPLATECANCEL**

## Output

**Coprocessor Late Cancel** When CPLATECANCEL is HIGH during the first memory cycle of a coprocessor instruction execution, the coprocessor instruction must be cancelled without updating any internal state.

This signal is asserted only in cycles where the previous instruction accessed memory and a data abort occurred.

#### **CPPASS Coprocessor Pass** Output A HIGH on this signal indicates that there is a coprocessor instruction in the execute stage of the pipeline that should be executed.

- **CPTBIT** Coprocessor Interface in Thumb State Output When CPTBIT is HIGH, the coprocessor interface is in Thumb state (16-bit instructions); otherwise the interface supports 32-bit instruction execution.

- nCPMREQ Not Coprocessor Memory Request Output When nCPMREQ is LOW on a rising CLK edge and CPCLKEN is HIGH, the instruction on CPINSTR must enter the coprocessor pipeline follower's decode stage, and the instruction previously in the pipeline follower's decode stage should enter its execute stage.

- **nCPTRANS** Not Coprocessor Translate Output When nCPTRANS is LOW, the coprocessor interface is in a nonprivileged state. When nCPTRANS is HIGH, the coprocessor interface is in a privileged state. The coprocessor should sample this signal on every cycle when determining the coprocessor response. Refer to Section 3.4, "Processor Modes," for a description of the privileged and nonprivileged (User) modes.

# 2.3 Instruction RAM Signals

Instruction RAM Address IADDR[23:0] Output This 24-bit bus contains the Instruction RAM address. Addressing is performed on word boundaries. IENABLE Word-Based Instruction Chip Enable Output The ARM966E-S asserts this output HIGH to indicate the Instruction RAM data bus is enabled. IRDATA[31:0] Instruction RAM Read Data Input This 32-bit bus contains data read from the Instruction RAM. IWDATA[31:0] Instruction RAM Write Data Output This 32-bit bus contains write data for the Instruction RAM. **Byte-Based Instruction Write Enable** IWE[3:0] Output The ARM966E-S asserts these outputs HIGH to enable writes to the Instruction RAM. IWE Bit Function IWE3 Write enable for IWDATA[31:24] IWE2 Write enable for IWDATA[23:16] IWE1 Write enable for IWDATA[15:8] IWE0 Write enable for IWDATA[7:0] NOIRAM Instruction RAM Present Input The ARM966E-S asserts NOIRAM HIGH to indicate the Instruction RAM is not present and thus Instruction RAM decoding is disabled. NOIRAM asserted LOW indicates

# 2.4 Data RAM Signals

The Data RAM interface supports both single-port and dual-port RAMs. When single-port RAMs are used, the ARM966E-S stalls during DMA transfers. When dual-port RAMs are used, the ARM966E-S does not need to be stalled during DMA transfers.

RAM decoding.

Instruction RAM is present, which enables Instruction

www.DataSheet4U.com

Signal Descriptions

The ARM966E-S uses the signals described below to access the Data RAM for both single-port and dual-port RAM implementations. The DMA Interface shares these signals with the ARM966E-S for single-port RAM implementations.

| DADDR[23:0]                                                                                    | This 24-bit bu                                                                                                       | <b>ddress</b><br>us contains the Data RAM address.<br>s performed on word boundaries. | Output |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|

| DENABLE                                                                                        | Word Based Data Chip EnableOutputThe ARM966E-S asserts this output HIGH to indicate theData RAM data bus is enabled. |                                                                                       |        |

| DRDATA[31:0] Data RAM Read Data Input<br>This 32-bit bus contains data read from the Data RAM. |                                                                                                                      |                                                                                       |        |

| DWDATA[31:0]Data RAM Write DataOutputThis 32-bit bus provides write data to the Data RAM.      |                                                                                                                      |                                                                                       |        |

| DWE[3:0]                                                                                       | Byte Based Data Write EnableOutputThe ARM966E-S asserts these outputs HIGH to enablewrites to the Data RAM.          |                                                                                       |        |

|                                                                                                | DWE Bit                                                                                                              | Function                                                                              |        |

|                                                                                                | DWE3                                                                                                                 | Write enable for DWDATA[31:24]                                                        |        |

|                                                                                                | DWE2                                                                                                                 | Write enable for DWDATA[23:16]                                                        |        |

|                                                                                                | DWE1                                                                                                                 | Write enable for DWDATA[15:8]                                                         |        |

|                                                                                                | DWE0                                                                                                                 | Write enable for DWDATA[7:0]                                                          |        |

| NODRAM                                                                                         |                                                                                                                      | r <b>esent</b><br>E-S asserts NODRAM HIGH to ind<br>not present and thus Data RAM de  |        |

The DMA Interface uses the signals described below to access only the second port of a dual-port RAM.

is present, which enables Data RAM decoding.

# DADDR2[23:0]

# Data RAM Address

Output

This 24-bit bus contains the Data RAM address. Addressing is performed on word boundaries.

is disabled. NODRAM asserted LOW indicates Data RAM

#### DENABLE2 Word-Based Data Chip Enable Output The ARM966E-S asserts this output HIGH to indicate the DataSheet4U.com Data RAM data bus is enabled.

# DRDATA2[31:0]

## Data RAM Read Data

### Input

This 32-bit bus contains data read from the Data RAM.

# DWDATA2[31:0]

**Data RAM Write Data** Output This 32-bit bus provides write data to the Data RAM.

DWE2[3:0] Byte Based Data Write Enable Output

| DW/E2 Bit Eurotion                                 |

|----------------------------------------------------|

| writes to the Data RAM.                            |

| The ARM966E-S asserts these outputs HIGH to enable |

|      | Function                       |

|------|--------------------------------|

| DWE3 | Write enable for DWDATA[31:24] |

| DWE2 | Write enable for DWDATA[23:16] |

| DWE1 | Write enable for DWDATA[15:8]  |

| DWE0 | Write enable for DWDATA[7:0]   |

|      |                                |

# 2.5 DMA Signals

| DMAA[25:0] | <b>DMA Address</b><br>This 26-bit address contains the byte address for<br>transfers. Tie all unused address bits LOW. | <b>Input</b><br>DMA  |

|------------|------------------------------------------------------------------------------------------------------------------------|----------------------|

| DMAD[31:0] | <b>DMA Write Data</b><br>This 32-bit bus contains the DMA write data to the<br>RAM.                                    | <b>Input</b><br>Data |

| DMAENABLE  | <b>DMA Port Enable</b><br>DMAENABLE must be asserted HIGH for a DMA tr                                                 |                      |

to proceed. Asserting DMAENABLE LOW can be used to save power when the DMA interface is not being used. Tie DMAENABLE LOW if the DMA Interface is not used in the implementation.

# DMAMAS[1:0] DMA Memory Access Size

Input

DMAMAS[1:0] encodes the size of DMA writes. DMA reads are always one word wide.

|             | DMAMAS[1:0]                                                                                                                                                                                                        | Memory Access Size                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 00                                                                                                                                                                                                                 | Byte                                                                                                                                                                                                                                      |

|             | 01                                                                                                                                                                                                                 | Halfword                                                                                                                                                                                                                                  |

|             | 10                                                                                                                                                                                                                 | Word                                                                                                                                                                                                                                      |

|             | 11                                                                                                                                                                                                                 | Reserved                                                                                                                                                                                                                                  |

| DMAnREQ     | DMA Request Inpu<br>DMAnREQ is an active-LOW DMA transfer request. Tie<br>this input HIGH if the DMA interface is not used.                                                                                        |                                                                                                                                                                                                                                           |

| DMAnRW      | DMA Write not ReadInputDMAnRW is the DMA Read/Write signal.                                                                                                                                                        |                                                                                                                                                                                                                                           |

|             | DMAnRW                                                                                                                                                                                                             | Function                                                                                                                                                                                                                                  |

|             | 0                                                                                                                                                                                                                  | Read                                                                                                                                                                                                                                      |

|             | 1                                                                                                                                                                                                                  | Write                                                                                                                                                                                                                                     |

| DMARData[31 | DMA Read D                                                                                                                                                                                                         | Data Output<br>us contains DMA Data read from the Data                                                                                                                                                                                    |

| DMAReady    | DMA Ready Output<br>DMAReady is asserted HIGH when the ARM966E-S is<br>stalled due to a DMA Wait request. DMAReady must be<br>sampled HIGH before a DMA transfer to/from a<br>single-port Data RAM can take place. |                                                                                                                                                                                                                                           |

| DMAWait     | before proceet<br>single-port Da<br>DMAReady in<br>Only use this                                                                                                                                                   | asserted HIGH to stall the ARM966E-S<br>eding with a DMA transfer to/from a<br>ata RAM implementation. A HIGH on<br>indicates when the ARM966E-S is stalled.<br>signal for single-port Data RAM<br>ons. Tie it LOW for dual-port Data RAM |

|             |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                           |

# 2.6 Debug Signals

www.DataSheet4U.com

| 0           | www.DdldSi                                                                                                                                                                                                                                                                                                 | 100140.00              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| COMMRX      | Communications Channel ReceiveOWhen HIGH, this signal indicates that the CommsChannel Receive Buffer has data that the ARM9Eprocessor core can read.                                                                                                                                                       |                        |

| СОММТХ      | Communications Channel TransmitCWhen HIGH, this signal indicates the Comms ChaTransmit Buffer is empty.                                                                                                                                                                                                    | <b>Dutput</b><br>annel |

| DBGACK      | Debug Acknowledge When HIGH, DBGACK indicates that the ARM9E-processor core is in debug mode.                                                                                                                                                                                                              | <b>Dutput</b><br>S     |

| DBGDEWPT    | <b>Debug Watchpoint</b><br>This input can halt the processor for debug purpose<br>HIGH at the end of a data memory request cycle,<br>input causes the ARM9E-S processor core to enter<br>debug state.                                                                                                      | this                   |

| DBGEN       | <b>Debug Enable</b><br>A LOW on this input disables the debug features of<br>ARM966E-S. Tie this input LOW when debugging<br>required.                                                                                                                                                                     |                        |

| DBGEXT[1:0] | <b>Breakpoint/Watchpoint External Condition</b><br>These inputs to the EmbeddedICE logic make<br>breakpoints/watchpoints dependent on external<br>conditions.                                                                                                                                              | Input                  |

| DBGIEBKPT   | <b>Processor Execution Breakpoint</b><br>When this input is asserted, processor execution is<br>for debug purposes. If DBGIEBKPT is HIGH at the<br>of an instruction fetch, the ARM9E-S processor co<br>enters the debug state if that instruction reaches t<br>execute stage of the processor's pipeline. | e end<br>pre           |

# DBGINSTREXEC

# **Instruction Executed**

Output When this output is asserted HIGH, the instruction in the execute stage of the processor's pipeline was executed.

DBGIR[3:0] Tap Controller Instruction Register Output These outputs reflect the current instruction loaded into the TAP controller instruction register. They change when the TAP state machine is in the UPDATE\_IR state on the rising edge of CLK when DBGTCKEN is asserted.

# DBGnTDOEN DBGTDO 3-State Enable

When LOW, this signal indicates there is serial data on the DBGTDO output. DBGnTDOEN can be used as the output enable on a packaged part's DBGTDO pin.

Output

Output

# DBGnTRST Not Test Reset Input This active-LOW input is the internally synchronized reset signal for the EmbeddedICE internal state.

# DBGRNG[1:0] Watchpoint Register Match

These outputs indicate that the corresponding EmbeddedICE Watchpoint register has matched the conditions currently present on the address, data, and control buses. These signals are independent of the state of the watchpoint's enable control bit.

## DBGRQI Internal Debug Request Output This signal is the debug request signal presented to the processor core's debug logic. It is the ANDing of EDBGRQ as presented to the ARM966E-S and bit 1 of the Debug Control Register.

# DBGSCREG[4:0]

|         | Scan Chain Register Out                                                                                                                                                                                                        | out |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|         | These outputs reflect the ID number of the scan chain<br>currently selected by the TAP controller. They change<br>when the TAP state machine is in the UPDATE_DP state<br>on the rising edge of CLK when DBGTCKEN is asserted. |     |

|         |                                                                                                                                                                                                                                |     |

| DBGSDIN | Boundary Scan Serial Input Data Output<br>This output contains the serial data for an external scan<br>chain.                                                                                                                  |     |

DBGSDOUT Boundary Scan Serial Output Data Input DBGSDOUT is the serial data input from an external scan chain. When an external scan chain is not implemented, tie this signal LOW.

| DBGTAPSM[ | <b>3:0]</b><br><b>TAP Controller State Machine</b><br>This bus reflects the current state of the TAP constant state machine. The TAP controller follows the<br>IEEE 1149.1 Test Access Port protocol. | Output<br>Sheal4U.com<br>introller |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| DBGTCKEN  | <b>Test Clock Enable</b><br>This input is the synchronous enable for the tes                                                                                                                          | Input<br>t clock.                  |

| DBGTDI    | <b>Test Data In</b><br>DBGTDI contains data input from the boundary logic.                                                                                                                            | <b>Input</b><br>scan               |

| DBGTDO    | <b>Test Data Out</b><br>The ARM966E-S outputs test data on DBGTDO<br>boundary scan logic.                                                                                                             | Output<br>from its                 |

| DBGTMS    | <b>Test Mode Select</b><br>DBGTMS is the JTAG test mode select signal.<br>mode follows the IEEE 1149.1 Test Access Port                                                                               |                                    |

| EDBGRQ    | External Debug Request<br>An external debugger asserts this signal to force<br>processor to enter the debug state.                                                                                    | Input<br>e the                     |

# 2.7 ETM Interface Signals

These signals are part of the Trace module interface. All ETM outputs are registered from the corresponding core internal signals.

ETMBIGEND Endian Mode Output When this signal is HIGH, the endian mode is big endian; when ETMBIGEND is LOW, the mode is little endian.

# ETMCHSD[1:0]

ETM Coprocessor Handshake Decode Output These outputs are the handshake signals from the decode stage of the coprocessor's pipeline follower.

| Encoding |

|----------|

| ABSENT   |

| WAIT     |

| GO       |

| LAST     |

|          |

## ETMCHSE[1:0]

#### ETM Coprocessor Handshake Execute Output

These outputs are the handshake signals from the execute stage of the coprocessor's pipeline follower.

| ETMCHSE[1:0] End | coding |

|------------------|--------|

|------------------|--------|

| 10 | ABSENT |  |

|----|--------|--|

| 00 | WAIT   |  |

| 01 | GO     |  |

| 11 | LAST   |  |

|    |        |  |

#### ETMDA[31:0] ETM Data Address

# This 32-bit bus contains the ETM data address.

## **ETMDABORT ETM Data Abort**

#### Output The ARM966E-S asserts this signal to indicate a data abort to the ARM9E-S processor core.

#### ETMDBGACK ETM Debug Mode Indication Output

When HIGH, this signal indicates that the processor is in the debug state.

#### ETMDMAS[1:0]ETM Data Size Indicator

# These signals indicate the data size of the ETM. They

become valid in the same cycle as the data address bus:

| DMAS[1:0] | Transfer Size |

|-----------|---------------|

| 00        | Byte          |

| 01        | Halfword      |

| 10        | Word          |

| 11        | Reserved      |

|           |               |

Output

Output

# ETMDMORE ETM Sequential Data Indication

The ETMDMORE signal is active during load and store multiple instructions and only goes HIGH when ETMDnMREQ is LOW. This signal effectively gives the same information as ETMDSEQ, but a cycle ahead. This information is provided to allow external logic more time to decode sequential cycles.

Output

# ETMDnMREQ ETM Data Memory Request Output This signal is asserted HIGH when the ARM966E-S is making a request to the ETM data memory.

# ETMDnRW ETM Data R/W Output If this signal is LOW at the end of the cycle, then any data memory access in the following cycle is a read. If this signal is HIGH, then the access is a write.

# **ETMDSEQ ETM Sequential Data Indication Output** If this signal is HIGH at the end of the cycle, then any data memory access in the following cycle is sequential from the last data memory access.

#### ETMEN ETM Enable Input When this signal is HIGH, the ETM is enabled and the ARM966E-S interface signals are driven out of this module, pipelined by one clock stage.

# **ETMHIVECS Exception Vector Location Output** When this output is LOW, the ARM966E-S exception vectors start at address 0x0000.0000. When this signal is HIGH, the ARM966E-S exception vectors start at address 0xFFFF.0000. This output is a static configuration signal.

# ETMIA[31:1] ETM Instruction Address Bus Output This 31-bit bus contains the address for the ETM.

# ETMID31To25[31:25]

# Bits [31:25] of Instruction Data Output

These outputs reflect the status of bits [31:25] of the instruction data read by the ARM966E-S.

# ETMID15To11[15:11]

# Bits [15:11] of Instruction Data Output

These outputs reflect the status of bits [15:11] of the instruction data read by the ARM966E-S.

. Copyright © 1999-2001 by LSI Logic Corporation. All rights reserved.

. . . .

# ETMINMREQ ETM Instruction Memory Request Output The ARM966E-S drives this output LOW to indicate that an instruction fetch will take place.

## **ETMINSTREXEC**

- **ETM Instruction Execute Indicator Output** The ARM966E-S asserts this output HIGH to indicate that the instruction in the execute stage of the processor pipeline has been executed.

- ETMISEQ ETM Sequential Instruction Output The ETMISEQ signal indicates whether the fetch is sequential (HIGH) or nonsequential (LOW) to the previous access.

- **ETMITBIT ETM Thumb Indication Output** When this signal is LOW, the processor is in ARM state and it fetches 32-bit instructions. When ETMITBIT is HIGH, the processor is in Thumb state and it fetches 16-bit instructions.

# ETMLATECANCEL

**ETM Coprocessor Late Cancel Indicator Output** If this output is HIGH during the first memory cycle of a coprocessor instruction, then the coprocessor should cancel the instruction without changing any internal state. This signal is only asserted in cycles where the previous instruction accessed memory and a data abort occurred.

- ETMnWAIT ETM Clock Stall Output Driving this output LOW stalls the ETM.

- ETMPASS ETM Coprocessor Instruction Execute Indicator

#### Output

A HIGH on this signal indicates that there is a coprocessor instruction in the execute stage of the pipeline, which should be executed.

# ETMRDATA[31:0]

## ETM Read Data

#### Output

This 32-bit bus contains ETM read data.

# ETMRNGOUT[1:0]

# ETM Watchpoint Register Match Output

This output indicates that corresponding EmbeddedICE Watchpoint register has matched the conditions currently

ETM Process ID Write Output

This output is asserted when ETMPROCID is written.

#### FIFOFULL ETM FIFO FULL Input This input is asserted when the ETM FIFO is full. Tie this signal LOW if an ETM is not used.

TAPID[31:0] **Boundary Scan ID Code** Input This bus specifies the ID Code value shifted out on DBGTDO when the IDCODE instruction enters the TAP Controller.

# 2.8 Miscellaneous Signals

2-20

|     | When this output is HIGH, the ARM966E-S is in big-endian mode (byte 0 is the most-significant bit). Whe this output is LOW, the ARM966E-S is in little-endian mode.            | 'n |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | This output is a static configuration signal. It must remain<br>at one value from reset or be changed using a carefull<br>constructed code sequence to avoid software problems | y  |

| CLK | System Clock Inp<br>CLK is the ARM966E-S system clock. CLK can be<br>stretched in either state (held HIGH or LOW).                                                             | ut |

ETMWDATA[31:0]

## ETM Write Data

enable control bit.

This 32-bit bus contains ETM write data.

#### **ETMINSTRVALID**

**ETM Instruction Valid** Output The ARM966E-S asserts this output HIGH to indicate the current instruction is valid for the ETM.

present on the address, data, and control buses. This signal is independent of the state of the watchpoint's

#### ETMPROCID[31:0]

#### ETM Process ID This 32-bit output contains the Process ID for the ETM.

## ETMPROCIDWR]

**BIGENDOUT** Big Endian

Output

www.DataSheet4U.com

Output

Output

Sheet4U.com

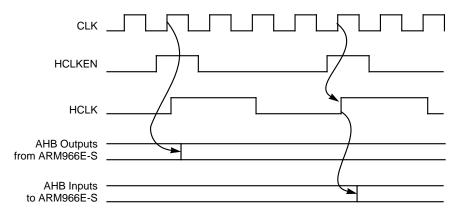

| HCLKEN | HCLK Enable<br>HCLKEN is used in conjunction with CLK to effer<br>run the ARM966E-S at a higher frequency than the<br>system bus. HCLKEN is HIGH for a single CLK p<br>and signifies the rising edge of the AHB clock, HC<br>AHB outputs transition on the CLK rising edge in<br>HCLKEN is asserted. | ne AHB<br>period<br>CLK. All |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| nFIQ   | <b>Not Fast Interrupt</b><br>This active-LOW input is the ARM Fast interrupt r<br>The ARM966E-S supports synchronous interrupt                                                                                                                                                                       | •                            |

| nIRQ   | <b>Not Interrupt Request</b><br>This active-LOW input is the ARM interrupt reque<br>ARM966E-S supports synchronous interrupts on                                                                                                                                                                     |                              |

# 2.9 Initialization Control Signals

| INITRAM | RAM Enable ConfigurationInputWhen INITRAM is HIGH, the Instruction and Data RAMsare enabled at the end of reset. When it is LOW, theInstruction and Data RAMs are disabled coming out ofreset. |