### **EVALUATION KIT AVAILABLE** МІХІМ

### Power IC with Integrated MOSFETs for Isolated IEEE 802.3af PD and Telecom Power-Supply Applications

### **General Description**

The MAX5074 isolated PWM power IC features integrated switching power MOSFETs connected in a voltageclamped, two-transistor, power-circuit configuration. This device can be used in both forward and flyback configurations with a wide input voltage range from 11V to 76V and up to 15W of output power.

The voltage-clamped power topology enables full recovery of stored magnetizing and leakage inductive energy for enhanced efficiency and reliability. A lookahead signal for driving secondary-side synchronous rectifiers can be used to increase efficiency.

A wide array of protection features includes UVLO, overtemperature shutdown, and short-circuit protection with hiccup current limit for enhanced performance and reliability. Operation up to 500kHz allows smaller external magnetics and capacitors.

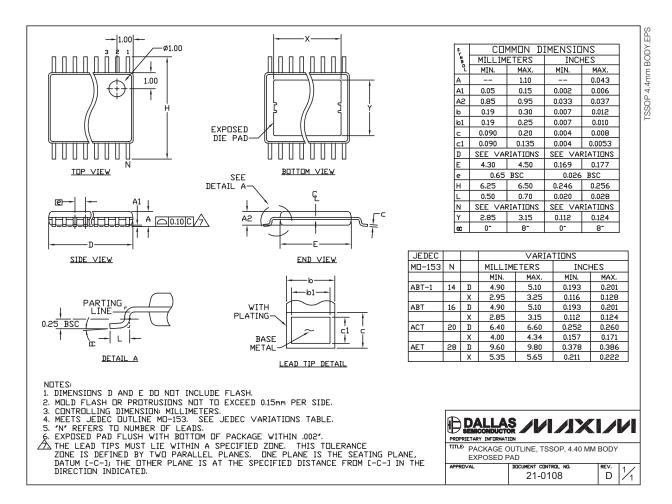

The MAX5074 is rated for operation over the -40°C to +125°C temperature range and is available in a 20-pin TSSOP package.

Warning: The MAX5074 is designed to work with high voltages. Exercise caution.

### **Applications**

IEEE 802.3af PD Power Supplies Isolated IP Phone Power Supplies High-Efficiency Telecom/Datacom Power Supplies 48V Input, Isolated Power-Supply Modules WLAN Access-Point Power Supplies **ADSL Line Cards ADSL Line-Driver Power Supplies** Distributed Power Systems with 48V Bus

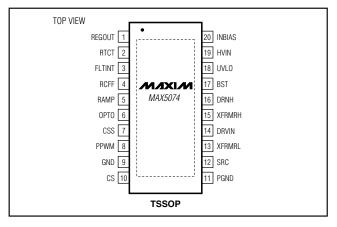

### **Pin Configuration**

#### **Features**

- ♦ Clamped, Two-Switch Power IC for High Efficiency

- ♦ No Reset Winding Required

- ♦ Up to 15W Output Power

- ♦ Bias Voltage Regulator with Automatic High-**Voltage Supply Turn-Off**

- ♦ 11V to 76V Wide Input Voltage Range

- ♦ Integrated High-Voltage 0.4Ω Power MOSFETs

- **♦** Feed-Forward Voltage-Mode Control For Fast **Input Transient Rejection**

- ♦ Programmable Brownout Undervoltage Lockout

- **♦** Internal Overtemperature Shutdown

- **♦ Indefinite Short-Circuit Protection With Programmable Fault Integration**

- ♦ Integrated Look-Ahead Signal for Secondary-Side Synchronous Rectification

- ♦ >90% Efficiency with Synchronous Rectification

- ♦ Up to 500kHz Switching Frequency

- ♦ High-Power (1.74W), Small-Footprint 20-Pin Thermally Enhanced TSSOP Package

### **Ordering Information**

| PART       | TEMP RANGE      | PIN-PACKAGE  |  |  |

|------------|-----------------|--------------|--|--|

| MAX5074AUP | -40°C to +125°C | 20-TSSOP-EP* |  |  |

<sup>\*</sup>EP = Exposed pad.

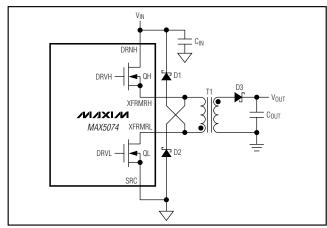

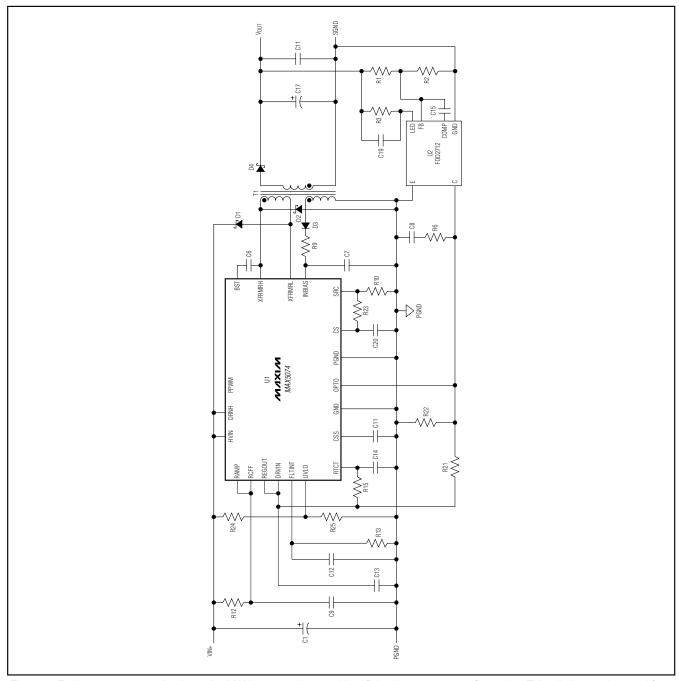

### Simplified Application Circuit

NIXIN

Maxim Integrated Products 1

#### ABSOLUTE MAXIMUM RATINGS

| HVIN, INBIAS, DRNH, XFRMRH,          |               |

|--------------------------------------|---------------|

| XFRMRL to GND                        | 0.3V to +80V  |

| BST to GND                           | 0.3V to +95V  |

| BST to XFRMRH                        | 0.3V to +12V  |

| PGND to GND                          | 0.3V to +0.3V |

| UVLO, RAMP, CSS, OPTO, FLTINT, RCFF, |               |

| RTCT to GND                          | 0.3V to +12V  |

| SRC, CS to GND                       | 0.3V to +6V   |

| REGOUT, DRVIN to GND                 | 0.3V to +12V  |

| REGOUT to HVIN                       | 80V to +0.3V  |

| REGOUT to INBIAS                     | 80V to +0.3V  |

| REGOUT Current                       | 50mA          |

| PPWM to GND0.3V to (REGOUT + CPWM Current ±2) DRNH, XFRMRH, XRFMRL, SRC Continuous Current (Avera TJ = +125°C TJ = +150°C        | 0mÁ<br>age)<br>0.9A |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}$ C)<br>20-Pin TSSOP-EP (derate 21.7mW/ $^{\circ}$ C above +70 $^{\circ}$ C)1.7 | 30//                |

| 20-Pin TSSOP-EP (θJA)                                                                                                            |                     |

| Operating Temperature Range40°C to +12                                                                                           |                     |

| Maximum Junction Temperature+15 Storage Temperature Range60°C to +15                                                             |                     |

| Lead Temperature (soldering, 10s)+30                                                                                             |                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{HVIN} = 12V, C_{INBIAS} = 1\mu F, C_{REGOUT} = 2.2\mu F, R_{RTCT} = 25k\Omega, C_{RTCT} = 100pF, C_{BST} = 0.22\mu F, V_{CSS} = V_{CS} = 0V, V_{RAMP} = V_{UVLO} = 3V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                  | SYMBOL              | CONDITIONS                                         | MIN               | TYP  | MAX  | UNITS |

|--------------------------------------------|---------------------|----------------------------------------------------|-------------------|------|------|-------|

| Input Supply Range                         | V <sub>HVIN</sub>   |                                                    | 11                |      | 76   | V     |

| OSCILLATOR (RTCT)                          | •                   |                                                    | •                 |      |      |       |

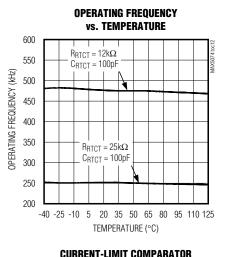

| PWM Frequency                              | fs                  | $R_{RTCT} = 25k\Omega$ , $C_{RTCT} = 100pF$        |                   | 256  |      | kHz   |

| Maximum PWM Duty Cycle                     | DMAX                | $R_{RTCT} = 25k\Omega$ , $C_{RTCT} = 100pF$        |                   | 47   |      | %     |

| Maximum RTCT Frequency                     | fRTCTMAX            | (Note 2)                                           | 1                 |      |      | MHz   |

| RTCT Peak Trip Level                       | V <sub>TH</sub>     |                                                    | 0.51 x<br>VREGOUT |      |      | V     |

| RTCT Valley Trip Level                     |                     |                                                    | 0.04 x<br>Vregout |      |      | V     |

| RTCT Input Bias Current                    |                     |                                                    |                   | ±1   |      | μΑ    |

| RTCT Discharge MOSFET RDS(ON)              |                     | Sinking 20mA                                       |                   | 30   | 60   | Ω     |

| RTCT Discharge Pulse Width                 |                     |                                                    |                   | 50   |      | ns    |

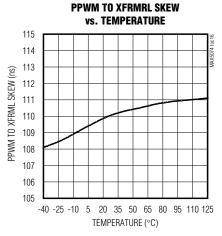

| LOOK-AHEAD LOGIC (PPWM)                    |                     |                                                    |                   |      |      |       |

| PPWM to XFRMRL Output<br>Propagation Delay | tppwm               | PPWM rising to XFRMRL falling                      | 110               |      |      | ns    |

| PPWM Output High                           | VoH                 | Sourcing 2mA                                       | 7.0 11.0          |      | 11.0 | V     |

| PPWM Output Low                            | V <sub>OL</sub>     | Sinking 2mA                                        |                   |      | 0.4  | V     |

| PWM COMPARATOR (OPTO, R                    | AMP, RCFF)          |                                                    |                   |      |      |       |

| Common-Mode Range                          | V <sub>CM-PWM</sub> |                                                    | 0                 |      | 5.5  | V     |

| Input Offset Voltage                       |                     |                                                    |                   | 10   |      | mV    |

| Input Bias Current                         |                     |                                                    | -2                |      | +2   | μΑ    |

| RAMP to XFRMRL Propagation Delay           |                     | From RAMP (50mV overdrive) rising to XFRMRL rising | 100               |      | ns   |       |

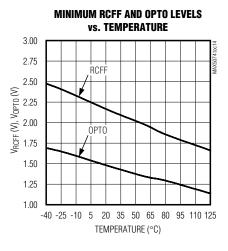

| Minimum OPTO Voltage                       |                     | V <sub>CSS</sub> = 0V, OPTO sinking 2mA            |                   | 1.47 |      | V     |

| Minimum RCFF Voltage                       |                     | RCFF sinking 2mA                                   |                   | 2.18 |      | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{HVIN}=12V,C_{INBIAS}=1\mu F,C_{REGOUT}=2.2\mu F,R_{RTCT}=25k\Omega,C_{RTCT}=100pF,C_{BST}=0.22\mu F,V_{CSS}=V_{CS}=0V,V_{RAMP}=V_{UVLO}=3V,T_{A}=T_{J}=-40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A}=+25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                           | SYMBOL CONDITIONS   |                                                                                                                    | MIN TY |     | MAX  | UNITS |

|-----------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------|--------|-----|------|-------|

| REGOUT LDO (REGOUT)                                 | •                   |                                                                                                                    |        |     |      |       |

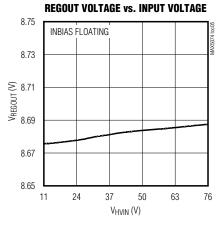

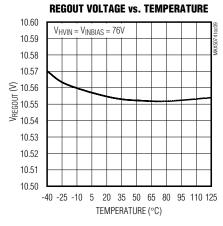

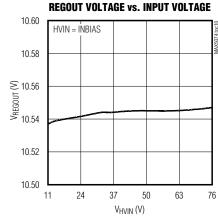

| DECOLITY II. O. D. C.                               |                     | INBIAS floating, V <sub>HVIN</sub> = 11V to 76V                                                                    | 8.3    |     | 9.2  |       |

| REGOUT Voltage Set Point                            | VREGOUT             | VINBIAS = VHVIN = 11V to 76V                                                                                       | 9.5    |     | 11.0 | V     |

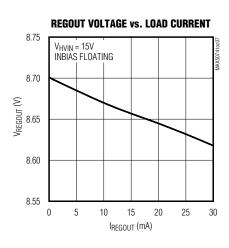

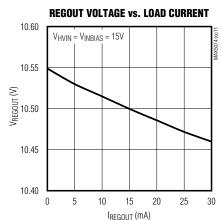

| DECOUT Load Degulation                              |                     | INBIAS floating, V <sub>HVIN</sub> = 15V, I <sub>REGOUT</sub> = 0 to 30mA                                          |        |     | 0.25 | V     |

| REGOUT Load Regulation                              |                     | VINBIAS = VHVIN = 15V, IREGOUT = 0 to 30mA                                                                         |        |     | 0.25 | V     |

| DECOLIT Draw out Voltage                            |                     | INBIAS floating, IREGOUT = 30mA                                                                                    |        |     | 1.25 | V     |

| REGOUT Dropout Voltage                              |                     | VINBIAS = VHVIN, IREGOUT = 30mA                                                                                    |        |     | 1.25 | V     |

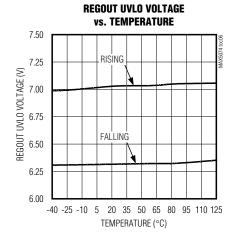

| REGOUT Undervoltage Lockout Threshold               |                     | REGOUT rising                                                                                                      | 6.6    |     | 7.4  | V     |

| REGOUT Undervoltage Lockout<br>Threshold Hysteresis |                     | REGOUT falling                                                                                                     |        | 0.7 |      | V     |

| SOFT-START (CSS)                                    | •                   |                                                                                                                    | •      |     |      |       |

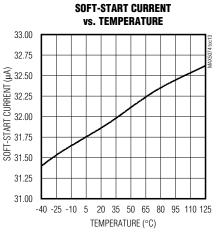

| Soft-Start Current                                  | Icss                |                                                                                                                    |        | 33  |      | μA    |

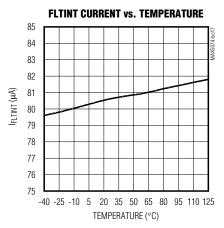

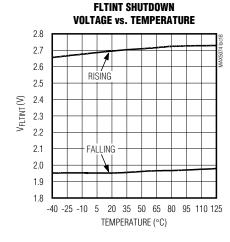

| INTEGRATING FAULT PROTECT                           | ION (FLTINT         | ·)                                                                                                                 | •      |     |      | •     |

| FLTINT Source Current                               | I <sub>FLTINT</sub> |                                                                                                                    |        | 80  |      | μA    |

| FLTINT Trip Point                                   |                     | FLTINT rising                                                                                                      |        | 2.7 |      | V     |

| FLTINT Hysteresis                                   |                     |                                                                                                                    |        | 0.8 |      | V     |

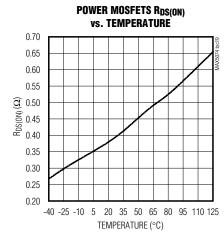

| INTERNAL POWER MOSFETs (S                           | ee Figure 1, (      | QH and QL)                                                                                                         |        |     |      |       |

| On-Resistance                                       | R <sub>DS(ON)</sub> | V <sub>DRVIN</sub> = V <sub>BST</sub> = 9V,<br>V <sub>XFRMRH</sub> = V <sub>SRC</sub> = 0V, I <sub>DS</sub> = 50mA |        | 0.4 | 0.8  | Ω     |

| Off-State Leakage Current                           |                     |                                                                                                                    | -5     |     | +5   | μΑ    |

| Total Gate Charge Per FET                           |                     |                                                                                                                    |        | 15  |      | nC    |

| HIGH-SIDE DRIVER                                    | ·I                  |                                                                                                                    |        |     |      | l .   |

| Low-to-High Delay                                   |                     | Driver delay until FET V <sub>GS</sub> reaches 0.9 x (V <sub>BST</sub> - V <sub>XFRMRH</sub> ) and is fully on     |        | 80  |      | ns    |

| High-to-Low Delay                                   |                     | Driver delay until FET VGS reaches 0.1 x (VBST - VXFRMRH) and is fully off                                         | 40     |     | ns   |       |

| Driver Output Voltage                               |                     | BST to XFRMRH with high side on                                                                                    |        | 8   |      | V     |

| LOW-SIDE DRIVER                                     | ·I                  |                                                                                                                    |        |     |      | l .   |

| Low-to-High Delay                                   |                     | Driver delay until FET V <sub>GS</sub> reaches 0.9 x V <sub>DRVIN</sub> and is fully on                            |        | 80  |      | ns    |

| High-to-Low Delay                                   |                     | Driver delay until FET V <sub>GS</sub> reaches 0.1 x V <sub>DRVIN</sub> and is fully off                           |        | 40  |      | ns    |

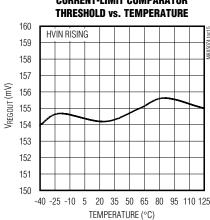

| CURRENT-LIMIT COMPARATOR                            | (CS)                |                                                                                                                    |        |     |      |       |

| Current-Limit Threshold Voltage                     | V <sub>ILIM</sub>   |                                                                                                                    | 140    | 156 | 172  | mV    |

| Current-Limit Input Bias Current                    | I <sub>BILIM</sub>  | 0 < V <sub>CS</sub> < 0.3V                                                                                         | -2     |     | +2   | μΑ    |

|                                                     | •                   |                                                                                                                    | •      |     |      | •     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{HVIN} = 12V, C_{INBIAS} = 1\mu F, C_{REGOUT} = 2.2\mu F, R_{RTCT} = 25k\Omega, C_{RTCT} = 100pF, C_{BST} = 0.22\mu F, V_{CSS} = V_{CS} = 0V, V_{RAMP} = V_{UVLO} = 3V, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                         | SYMBOL             | CONDITIONS                                                                            | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------|--------------------|---------------------------------------------------------------------------------------|------|------|------|-------|

| Propagation Delay to XFRMRL       | talLIM             | From CS rising (10mV overdrive) to XFRMRL rising                                      |      | 160  |      | ns    |

| <b>BOOST VOLTAGE CIRCUIT</b> (See | e Figure 1, QB     | )                                                                                     |      |      |      |       |

| Driver Output Delay               | tppwmd             |                                                                                       |      | 200  |      | ns    |

| One-Shot Pulse Width              | tpwqb              |                                                                                       |      | 300  |      | ns    |

| QB R <sub>DS(ON)</sub>            |                    | Sinking 20mA                                                                          |      | 30   | 60   | Ω     |

| THERMAL SHUTDOWN                  |                    |                                                                                       |      |      |      |       |

| Shutdown Temperature              | T <sub>SH</sub>    | Temperature rising                                                                    |      | +160 |      | °C    |

| Thermal Hysteresis                | T <sub>HYST</sub>  |                                                                                       |      | 15   |      | °C    |

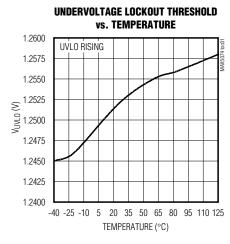

| UNDERVOLTAGE LOCKOUT (U           | VLO)               |                                                                                       |      |      |      |       |

| UVLO Threshold                    | V <sub>U</sub> VLO | V <sub>UVLO</sub> rising                                                              | 1.14 |      | 1.38 | V     |

| UVLO Hysteresis                   | V <sub>HYST</sub>  |                                                                                       |      | 140  |      | mV    |

| UVLO Input Bias Current           | IBUVLO             | $V_{UVLO} = 3V$                                                                       | -100 |      | +100 | nA    |

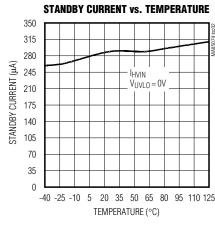

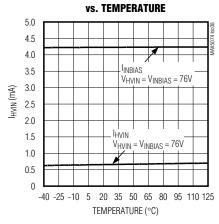

| SUPPLY CURRENT                    |                    |                                                                                       |      |      |      |       |

|                                   |                    | From V <sub>HVIN</sub> = 11V to 76V, V <sub>CSS</sub> = 0V, V <sub>INBIAS</sub> = 11V |      | 0.7  | 2    |       |

| Supply Current                    |                    | From V <sub>INBIAS</sub> = 11V to 76V, V <sub>CSS</sub> = 0V, V <sub>HVIN</sub> = 76V |      | 4.4  | 6.0  | mA    |

|                                   |                    | From V <sub>HVIN</sub> = 76V                                                          |      | 7    |      |       |

| Standby Supply Current            |                    | $V_{UVLO} = 0V$                                                                       |      |      | 1    | mA    |

Note 1: All limits at -40°C are guaranteed by design and not production tested.

Note 2: Output switching frequency is half of oscillator frequency.

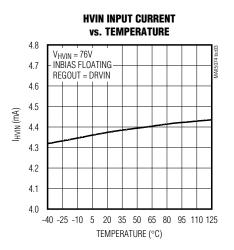

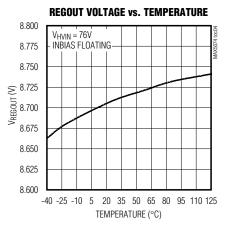

### Typical Operating Characteristics

$(V_{HVIN}=48V,\,V_{INBIAS}=15V,\,C_{INBIAS}=1\mu F,\,C_{REGOUT}=2.2\mu F,\,R_{RTCT}=25k\Omega,\,C_{RTCT}=100pF,\,C_{BST}=0.22\mu F,\,V_{CSS}=V_{CS}=0V,\,V_{RAMP}=V_{UVLO}=3V,\,T_A=T_J=-40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ , unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{HVIN}=48V,\ V_{INBIAS}=15V,\ C_{INBIAS}=1\mu F,\ C_{REGOUT}=2.2\mu F,\ R_{RTCT}=25k\Omega,\ C_{RTCT}=100pF,\ C_{BST}=0.22\mu F,\ V_{CSS}=V_{CS}=0V,\ V_{RAMP}=V_{UVLO}=3V,\ T_A=T_J=-40^{\circ}C\ to\ +125^{\circ}C,\ unless\ otherwise\ noted.)$

**HVIN AND INBIAS INPUT CURRENT**

### **Typical Operating Characteristics (continued)**

$(V_{HVIN} = 48V, V_{INBIAS} = 15V, C_{INBIAS} = 1\mu F, C_{REGOUT} = 2.2\mu F, R_{RTCT} = 25k\Omega$ ,  $C_{RTCT} = 100pF$ ,  $C_{BST} = 0.22\mu F, V_{CSS} = V_{CS} = 0V$ ,  $V_{RAMP} = V_{UVLO} = 3V$ ,  $V_{LS} = V_{LS} = 0.22\mu F$ ,  $V_{LS} =$

### **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | REGOUT | Regulator Output. Always present as long as HVIN is powered with a voltage above UVLO threshold. Bypass REGOUT to GND with a minimum 2.2µF ceramic capacitor.                                                                                                                                                                                   |

| 2   | RTCT   | Oscillator Frequency Set Input. Connect a resistor from RTCT to REGOUT and a capacitor from RTCT to GND to set the oscillator frequency.                                                                                                                                                                                                        |

| 3   | FLTINT | Fault Integration Input. During persistent current-limit faults, a capacitor connected to FLTINT is charged with an internal 80µA current source. Switching is terminated when V <sub>FLTINT</sub> reaches 2.7V. An external resistor connected in parallel discharges the capacitor. Switching resumes when V <sub>FLTINT</sub> drops to 1.9V. |

| 4   | RCFF   | Feed-Forward Input. To generate the PWM ramp, connect a resistor from RCFF to HVIN and a capacitor from RCFF to GND.                                                                                                                                                                                                                            |

| 5   | RAMP   | PWM Ramp Sense Input. Connect RAMP to RCFF.                                                                                                                                                                                                                                                                                                     |

| 6   | OPTO   | PWM Comparator Inverting Input. Connect the collector of the optotransistor to OPTO and a pullup resistor to REGOUT.                                                                                                                                                                                                                            |

| 7   | CSS    | Soft-Start and Reference. Connect a 10nF or greater capacitor from CSS to GND.                                                                                                                                                                                                                                                                  |

| 8   | PPWM   | PWM Pulse Output. PPWM leads the internal power MOSFET pulse by approximately 100ns.                                                                                                                                                                                                                                                            |

| 9   | GND    | Signal Ground. Connect GND to PGND.                                                                                                                                                                                                                                                                                                             |

| 10  | CS     | Current-Sense Input. The current-limit threshold is internally set to 156mV relative to PGND. The device has an internal noise filter. If necessary, connect an external RC filter for additional filtering.                                                                                                                                    |

| 11  | PGND   | Power Ground. Connect PGND to GND.                                                                                                                                                                                                                                                                                                              |

| 12  | SRC    | Internal Low-Side Power MOSFET Source. Connect SRC to PGND with a low-value resistor for current limiting.                                                                                                                                                                                                                                      |

| 13  | XFRMRL | Low-Side Connection for the Isolation Transformer                                                                                                                                                                                                                                                                                               |

| 14  | DRVIN  | MOSFET Gate-Driver Supply Input. Bypass DRVIN with at least 0.1µF to PGND. Connect DRVIN to REGOUT.                                                                                                                                                                                                                                             |

| 15  | XFRMRH | High-Side Connection for the Isolation Transformer                                                                                                                                                                                                                                                                                              |

| 16  | DRNH   | Drain Connection of the Internal High-Side PWM Power MOSFET. Connect DRNH to the most positive rail of the input supply. Bypass DRNH appropriately to handle the heavy switching current through the transformer.                                                                                                                               |

| 17  | BST    | Boost Input. BST is the boost connection point for the high-side MOSFET driver. Connect a minimum 0.1µF capacitor from BST to XFRMRH with short and wide PC board traces.                                                                                                                                                                       |

| 18  | UVLO   | Undervoltage Lockout Input. Connect a resistive divider from HVIN to UVLO and from UVLO to GND to set the UVLO threshold.                                                                                                                                                                                                                       |

| 19  | HVIN   | High-Voltage Input. Connect HVIN to the most positive input supply rail.                                                                                                                                                                                                                                                                        |

| 20  | INBIAS | Input from the Rectified Bias Winding. INBIAS is an input to the internal linear voltage regulator (REGOUT).                                                                                                                                                                                                                                    |

|     | EP     | Exposed Paddle. EP is internally connected to GND. Connect the exposed paddle to a copper pad to improve power dissipation.                                                                                                                                                                                                                     |

### **Detailed Description**

The MAX5074 PWM power IC is the primary-side controller for voltage-mode, isolated forward or flyback power converters. This device provides a high degree of integration aimed at reducing the cost and printed circuit board area of isolated output power supplies. Use the MAX5074 primarily in 48V power bus applications.

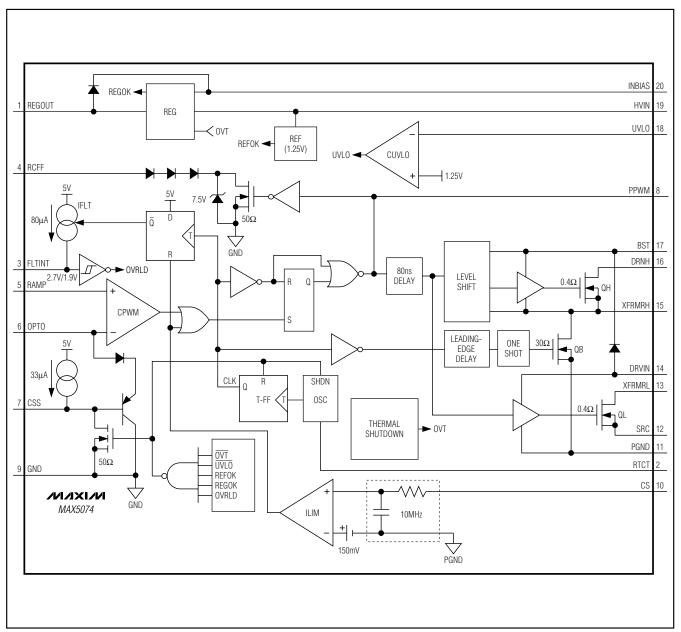

The MAX5074 is a complete power IC capable of delivering up to 15W of output power. This device contains PWM circuitry and integrated power MOSFETs. Figure 1 shows the MAX5074's block diagram. The MAX5074 includes undervoltage lockout, overtemperature shutdown, and short-circuit protection for enhanced performance and reliability. Operation up to 500kHz allows the use of small external magnetics and capacitors.

Figure 1. Block Diagram

#### **Power Topology**

The two-switch forward converter topology offers outstanding robustness against faults and transformer saturation while affording efficient use of the integrated 0.4 $\Omega$  power MOSFETs. Voltage-mode control with feed-forward compensation allows the rejection of input supply disturbances within a single cycle similar to that of current-mode controlled topologies.

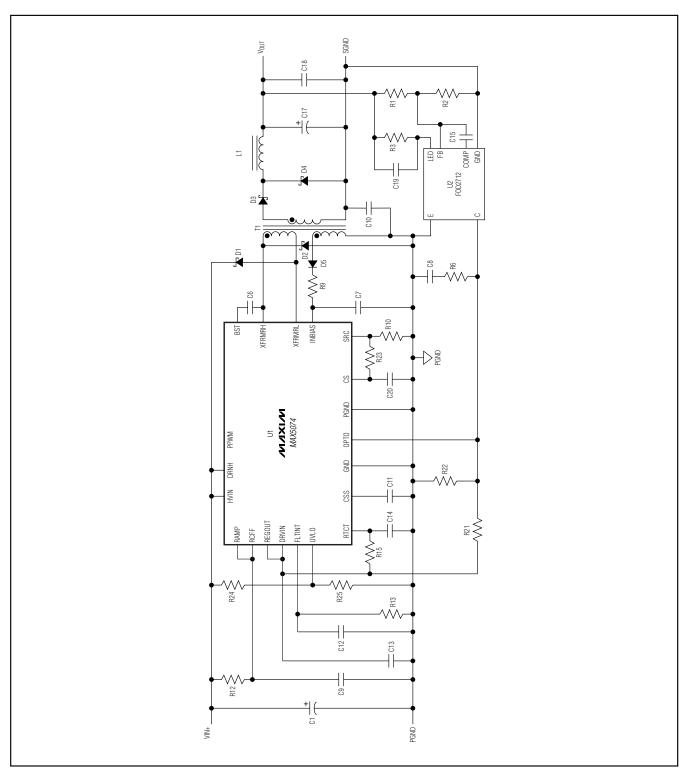

The two-switch power topology recovers energy stored in both the magnetizing and the parasitic leakage inductances of the transformer. The *Typical Application Circuit*, forward converter (Figure 3) shows the schematic diagram of a 48V input and 5V, 3A output isolated power supply. Figure 4 shows the schematic diagram of a flyback converter using the MAX5074.

#### **Undervoltage Lockout (UVLO)**

The UVLO block monitors the input voltage HVIN through an external resistive divider (R24 and R25) connected to UVLO (see Figure 3). Use the following equation to calculate R24 and R25:

$$V_{UVLOIN} = V_{UVLO} \times \left(1 + \frac{R24}{R25}\right)$$

where  $V_{UVLOIN}$  is the desired input voltage lockout level and  $V_{UVLO}$  is the undervoltage lockout threshold (1.25V, typ).

#### **Internal Regulators**

As soon as power is provided to HVIN, internal power supplies power the UVLO detection circuitry. REGOUT is used to drive the internal power MOSFETs. Bypass REGOUT with a minimum 2.2µF ceramic capacitor. The HVIN LDO steps down V<sub>HVIN</sub> to a nominal output voltage (REGOUT) of 8.75V. A second parallel LDO powers REGOUT from INBIAS. A tertiary winding connected through a diode to INBIAS powers up REGOUT once switching commences. This will bring REGOUT to 10.5V (typ) and shut off the current flowing from HVIN to REGOUT. This results in a lower on-chip power dissipation and higher efficiency.

#### Soft-Start

Program the MAX5074 soft-start with an external capacitor between CSS and GND. When the device turns on, the soft-start capacitor (C<sub>CSS</sub>) charges with a constant current of 33µA, ramping up to 7.3V. During this time, the feedback pin (OPTO) is clamped to V<sub>CSS</sub> + 0.6V. This initially holds the duty cycle lower than the value the regulator tries to impose, thus preventing voltage overshoot at the output. When the MAX5074 turns off, the soft-start capacitor internally discharges to GND.

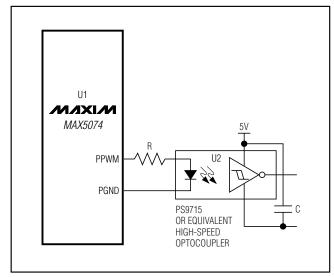

Figure 2. Secondary-Side Synchronous Rectifier Driver Using a High-Speed Optocoupler

### **Secondary-Side Synchronization**

The MAX5074 provides convenient synchronization for optional secondary-side synchronous rectifiers. Figure 2 shows the connection diagram with a high-speed opto-coupler. Choose an optocoupler with a propagation delay of less than 80ns. The synchronizing pulse is generated approximately 110ns ahead of the main pulse that drives the two power MOSFETs.

#### **Voltage-Mode Control and the PWM Ramp**

For voltage-mode control, the feed-forward PWM ramp is generated at RCFF. From RCFF, connect a capacitor to GND and a resistor to HVIN. The ramp generated is applied to the noninverting input of the PWM comparator at RAMP and has a minimum voltage of approximately 2V. The slope of the ramp is determined by the voltage at HVIN and affects the overall loop gain. The ramp peak must remain below the dynamic range of RCFF of 5.5V. Assuming the maximum duty cycle approaches 50% at a minimum input voltage (PWM UVLO turn-on threshold), use the following formula to calculate the minimum value of either the ramp capacitor or resistor:

$$R_{RCFF}C_{RCFF} \ge \frac{V_{UVLOIN}}{2f_{S}V_{R(P-P)}}$$

where fs is the switching frequency,  $V_{R(P-P)}$  is the peak-to-peak ramp voltage (2V, typ).

Maximize the signal-to-noise ratio by setting the ramp peak as high as possible. Calculate the low-frequency, small-signal gain of the power stage (the gain from the inverting input of the PWM comparator to the output) using the following formula:

GPS = NSP x RRCFF x CRCFF x fs

where NSP is the secondary to primary power transformer turns ratio.

#### **Oscillator**

The MAX5074 oscillator is externally programmable through a resistor connected from RTCT to REGOUT and a capacitor connected from RTCT to GND. The PWM frequency will be 1/2 the frequency at RTCT with a 50% duty cycle. Use the following formula to calculate the oscillator components:

$$R_{RTCT} \cong \frac{1}{2f_{S}(C_{RTCT} + C_{PCB})In\left(\frac{V_{REGOUT}}{V_{REGOUT} - V_{TH}}\right)}$$

where C<sub>PCB</sub> is the stray capacitance on the PC board (14pF, typ), V<sub>TH</sub> is the RTCT peak trip level, and fs is the switching frequency.

#### **Integrating Fault Protection**

The integrating fault protection feature allows the MAX5074 to ignore transient overcurrent conditions for a programmable amount of time, giving the power supply time to behave like a current source to the load. This can happen, for example, under load-current transients when the control loop requests maximum current to keep the output voltage from going out of regulation. Program the ignore time externally by connecting a capacitor to FLTINT. Under sustained overcurrent faults, the voltage across this capacitor ramps up toward the FLTINT shutdown threshold (typically 2.7V). When FLTINT reaches the threshold, the power supply shuts down. A highvalue bleed resistor connected in parallel with the FLTINT capacitor allows the capacitor to discharge toward the restart threshold (typically 1.9V). Crossing the restart threshold soft-starts the supply again.

The ILIM comparator provides cycle-by-cycle current limiting with a typical threshold of 156mV. The fault integration circuit works by forcing an  $80\mu A$  current into

FLTINT for one clock every time the current-limit comparator ILIM (Figure 1) trips. Use the following formula to calculate the approximate capacitor needed for the desired shutdown time:

$$C_{FLTINT} \cong \frac{I_{FLTINT}t_{SH}}{1.4}$$

where  $I_{FLTINT}$  is typically  $80\mu A$ , and  $t_{SH}$  is the desired ignore time during which current-limit events from the current-limit comparator are ignored.

This is an approximate formula; some testing may be required to fine tune the actual value of the capacitor.

Calculate the approximate bleed resistor needed for the desired recovery time using the following formula:

$$R_{FLTINT} \cong \frac{t_{RT}}{C_{FLTINT} \ln \left(\frac{2.7}{1.9}\right)}$$

where tRT is the desired recovery time.

Choose at least  $t_{RT} = 10 \times t_{SH}$ . Typical values for  $t_{SH}$  range from a few hundred microseconds to a few milliseconds.

#### Shutdown

Shut down the MAX5074 by driving UVLO to GND using an open-collector or open-drain transistor connected to GND. The IC will be internally shut down if REGOUT is below its UVLO level. The MAX5074 also features internal thermal shutdown using a temperature sensor that monitors the high-power area. A thermal fault arises from excessive dissipation in the power MOSFETs or in the regulator. When the temperature limit is reached (+160°C), the temperature sensor terminates switching and shuts down the regulator. The integration of thermal shutdown and the power MOSFETs results in a very robust power circuit.

### \_Applications Information

### **Isolated Telecom Power Supply**

Figure 3 shows a typical application circuit of an isolated power supply with a 30V to 60V input. This power supply is fully protected and can sustain a continuous short circuit at its output terminals.

Figure 3. Typical Application Circuit (48V Power Supply, Evaluation Kit Available)

Figure 4. For lower power applications, the MAX5074 can be used in a flyback converter configuration. This eliminates the need for an output inductor and simplifies the design of multiple output power supplies.

Chip Information

TRANSISTOR COUNT: 7043

PROCESS: BICMOS

N/IXI/N

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.