Mosaic Semiconductor Inc.

1,048,576 bit CMOS High Speed Static RAM

#### **Features**

Ultra Fast access times of 30/35/45/55/70 ns.

Configurable as 32 / 16 / 8 bit wide output.

Operating Power 2640 / 1375 / 770 mW (maximum)

Standby Power 11 mW (maximum)

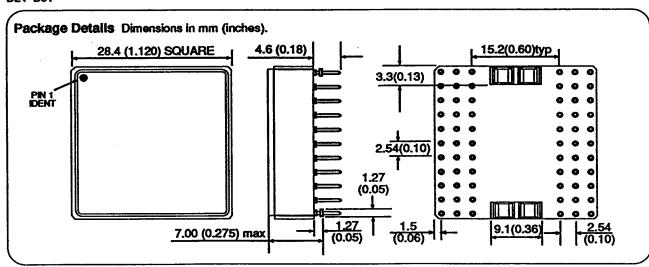

Pin grid array gives 2:1 improvement over DIL.

Package Suitable for Thermal Ladder Applications.

On board decoupling capacitors.

Battery back-up capability.

May be processed to MIL-STD-883, method 5004 non-compliant.

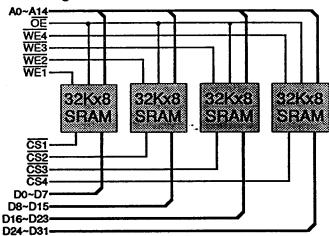

#### **Block Diagram**

## 32K x 32 SRAM

### PUMA 2S1010-030/35/45/55/70

Issue 2.0 : May 1992

## **PRELIMINARY**

### **Pin Definition**

| 1 12 23                                 |                       | 34 45 56                              |

|-----------------------------------------|-----------------------|---------------------------------------|

| ○ 55 ○ 50 ○ 50 ○ 50 ○ 50 ○ 50 ○ 50 ○ 50 | VIEW<br>FROM<br>ABOVE | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

| 11 22 33                                |                       | 44 00 00                              |

### **Pin Functions**

| A0 -A14   | Address Inputs      |

|-----------|---------------------|

| D0-D31    | Data Inputs/Outputs |

| CS1-4     | Chip Select         |

| <b>OE</b> | Output Enable       |

| WE1-4     | Write Enable        |

| NC        | No Connect          |

| Vcc       | Power (+5V)         |

| GND       | Ground              |

### Absolute Maximum Ratings (1)

| Voltage on any pin relative to V <sub>ss</sub> <sup>(2)</sup> | $V_{\tau}$       | -0.5V to +7 | ٧        |

|---------------------------------------------------------------|------------------|-------------|----------|

| Power Dissipation                                             | $P_{T}$          | 1           | W        |

| Storage Temperature                                           | T <sub>sta</sub> | -55 to +150 | <b>℃</b> |

- Notes (1) Stresses above those listed may cause permanent damageto the module. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- (2) Pulse width: 2.5V for less than 10ns.

| Recommended Operating Conditions |              |      |     |                  |   |  |  |  |  |  |

|----------------------------------|--------------|------|-----|------------------|---|--|--|--|--|--|

|                                  |              | min  | typ | max              |   |  |  |  |  |  |

| Supply Voltage                   | $V_{\infty}$ | 4.5  | 5.0 | 5.5              | V |  |  |  |  |  |

| Input High Voltage               | V            | 2.2  | -   | $V_{\infty}+0.5$ | V |  |  |  |  |  |

| Input Low Voltage                | V            | -0.5 | -   | 0.8              | V |  |  |  |  |  |

Operating Temperature  $T_A$  0 - 70 °C  $T_{AL}$  -40 - 85 °C (suffix I)

T<sub>AM</sub> -55 - 125 °C (suffix **M**, **MB**)

## DC Electrical Characteristics (V<sub>cc</sub> = 5V±10%,T<sub>A</sub> = -55°C to +125°C)

|                         |                    |                   |                                                                                                     | 03  | 0/35 | 45/5       | 55/70 |      |

|-------------------------|--------------------|-------------------|-----------------------------------------------------------------------------------------------------|-----|------|------------|-------|------|

| Parameter               | Sy                 | /mbol             | Test Condition                                                                                      | min | max  | min        | max   | Unit |

| I/P Leakage Current A0- | -14, <del>OE</del> | l, H              | V <sub>M</sub> =0V to V <sub>cc</sub>                                                               | -   | 8    | <b>-</b> · | 8     | μΑ   |

|                         | 2, <u>CS</u> (2)   |                   | $V_{\rm m} = 0 \text{V to } V_{\rm cc}$                                                             | -   | 2    | -          | 2     | μΑ   |

| Output Leakage Current  |                    |                   | $\overline{CS}^{(2)} = V_{H} \text{ or } \overline{OE} = V_{H'} V_{VO} = 0V \text{ to } V_{\infty}$ | -   | 2    | -          | 2     | μΑ   |

| Operating Supply Curren | t 32 bit           | i                 | CS <sup>(2)</sup> =V <sub>a</sub> , inputs static                                                   | -   | 250  | -          | 250   | mΑ   |

| Average Supply Current  |                    |                   | $\overline{CS}^{(2)} = V_{\mu}$ , Min. cycle, $I_{\mu o} = 0$ mA                                    | -   | 480  | -          | 380   | mA   |

|                         | 16 bit             | I <sub>CC16</sub> | As above                                                                                            | -   | 250  | -          | 200   | mΑ   |

|                         | 8 bit              |                   | As above                                                                                            | -   | 140  | -          | 115   | mΑ   |

| Standby Supply Current  | TTL                |                   | CS <sup>(2)</sup> =V <sub>H</sub> , minimum cycle.                                                  | -   | 30   | -          | 30    | mΑ   |

| • • • • •               | CMOS               | <sub>S81</sub>    | $\overline{\text{CS}}^{(2)} \ge V_{\infty}$ -0.2V, 0.2V $\ge V_{\text{N}} \ge V_{\infty}$ -0.2V     | -   | 2    | -          | 2     | mΑ   |

| Output Voltage Low      |                    | Val               | l <sub>ot</sub> = 8.0mA                                                                             | -   | 0.4  | -          | 0.4   | V    |

| Output Voltage High     |                    |                   | l <sub>OH</sub> = -4.0mA                                                                            | 2.4 | -    | 2.4        | •     | ٧    |

- Notes (1) Typical values are at  $V_{cc} = 5.0V$ ,  $T_A = 25^{\circ}C$  and specified loading.

- (2) CS and WE above are accessed through CS1-4 and WE1-4 respectively. These inputs must be operated simultaneously for 32 bit mode, in pairs for 16 bit mode and singly for 8 bit mode.

| Capacitance | (V <sub>cc</sub> =5\ | /±10%,T | <sub>A</sub> =25°C) |

|-------------|----------------------|---------|---------------------|

|-------------|----------------------|---------|---------------------|

| Parameter         |                     | Symbol            | Test Condition      | typ | max | Unit |

|-------------------|---------------------|-------------------|---------------------|-----|-----|------|

| Input Capacitance | Address, OE         | C <sub>IN1</sub>  | V <sub>N</sub> =0V  | •   | 34  | pF   |

|                   | WE1-4, CS1-4        | ****              | V <sub>N</sub> =0V  | • - | 22  | pF   |

| I/O Capacitance:  | 32 bit mode         | C <sub>IO32</sub> | V <sub>IO</sub> =0V | -   | 17  | pF   |

|                   | 16 bit mode         | Cions             | V <sub>vo</sub> =0V | -   | 24  | pF   |

|                   | 8 bit mode          |                   | V <sub>IO</sub> =0V | -   | 38  | pF   |

| Note: This parar  | neter is calculated |                   |                     |     |     |      |

### **Operating Modes**

The Table below shows the logic inputs required to control the operating modes of each of the SRAMs on the PUMA 2S1010.

| Mode CS OE   |   | CS OE WE |   | V <sub>cc</sub> Current           | I/O Pin          | Reference Cycle  |

|--------------|---|----------|---|-----------------------------------|------------------|------------------|

| Not Selected | 1 | х        | Х | I <sub>se</sub> ,I <sub>se1</sub> | High Z           | -                |

| Read         | 0 | 0        | 1 | I <sub>cc</sub>                   | D <sub>out</sub> | Read Cycle 1,2,3 |

| Write        | 0 | 1        | 0 | l <sub>cc</sub>                   | D <sub>IN</sub>  | Write Cycle 1    |

| Write        | 0 | 0        | 0 | Iœ                                | D <sub>IN</sub>  | Write Cycle 2    |

$$1 = V_{H}$$

,  $0 = V_{L}$ ,  $X = Don't Care$

Note:  $\overline{\text{CS}}$  is accessed through  $\overline{\text{CS1-4}}$ , and  $\overline{\text{WE}}$  is accessed through  $\overline{\text{WE1-4}}$ . For correct operation,  $\overline{\text{CS1-4}}$  must operate simultaneously for 32 bit operation, in pairs for 16 bit operation, or singly for 8 bit operation.  $\overline{\text{WE1-4}}$  must also be operated in the same manner.

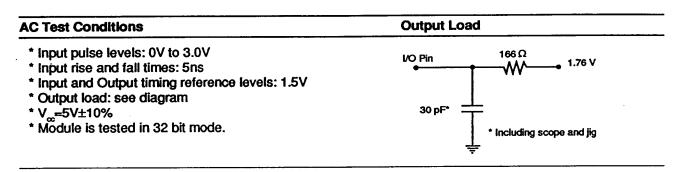

# Electrical Characteristics & Recommended AC Operating Conditions

| Read | Cycle |

|------|-------|

|      |       |

|                                                     | -30               |     | ٦,  | 35  |     |      |  |

|-----------------------------------------------------|-------------------|-----|-----|-----|-----|------|--|

| Parameter                                           | Symbol            | min | max | min | max | Unit |  |

| Read Cycle Time                                     | t <sub>RC</sub>   | 30  | -   | 35  | -   | ns   |  |

| Address Access Time                                 | t                 | • - | 30  | -   | 35  | ns   |  |

| Chip Select Access Time                             | t <sub>ACS</sub>  | -   | 30  | -   | 35  | ns   |  |

| Output Enable to Output Valid                       | to∈               | -   | 12  | -   | 15  | ns   |  |

| Output Hold from Address Change                     | t <sub>oH</sub>   | 3   | -   | 3   | -   | ns   |  |

| Chip Selection to Output in Low Z <sup>(5)</sup>    | taz               | 3   | -   | 3   | -   | ns   |  |

| Output Enable to Output in Low Z <sup>(5)</sup>     | toz               | 0   | -   | 0   | -   | ns   |  |

| Chip Deselection to Output in High Z <sup>(5)</sup> | t <sub>cHZ</sub>  | 0   | 12  | 0   | 15  | ns   |  |

| Output Disable to Output in High Z <sup>(5)</sup>   | t <sub>oriz</sub> | 0   | 12  | 0   | 15  | ns   |  |

|                                                     |                  |     | 45 · |            | -55        | -7  | ro  |      |

|-----------------------------------------------------|------------------|-----|------|------------|------------|-----|-----|------|

| Parameter                                           | Symbol           | min | max  | min        | max        | min | max | Unit |

| Read Cycle Time                                     | t <sub>ec</sub>  | 45  | •    | <b>5</b> 5 | -          | 70  | -   | ns   |

| Address Access Time                                 | t                | -   | 45   | -          | 55         | -   | 70  | ns   |

| Chip Select Access Time                             | tacs             | -   | 45   | -          | <b>5</b> 5 | -   | 60  | ns   |

| Output Enable to Output Valid                       | toE              | -   | 20   | -          | 25         | -   | 30  | ns   |

| Output Hold from Address Change                     | t <sub>oH</sub>  | 3   | -    | 3          | -          | 3   | -   | ns   |

| Chip Selection to Output in Low Z <sup>(5)</sup>    | t <sub>cız</sub> | 3   | -    | 3          | -          | 3   | -   | ns   |

| Output Enable to Output in Low Z <sup>(5)</sup>     | toz              | 0   | -    | 0          | -          | 0   | -   | ns   |

| Chip Deselection to Output in High Z <sup>(5)</sup> |                  | 0   | 20   | 0          | 25         | 0   | 30  | ns   |

| Output Disable to Output in High Z <sup>(5)</sup>   | t <sub>oHZ</sub> | 0   | 20   | 0          | 25         | 0   | 30  | ns   |

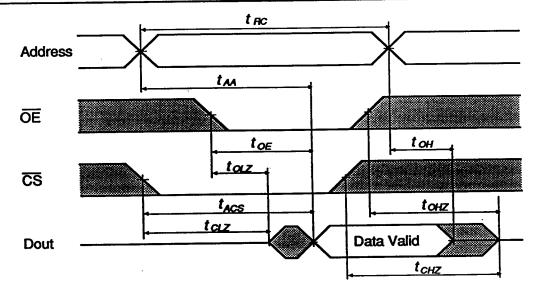

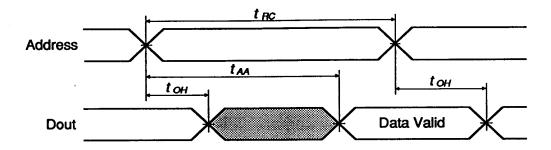

# Read Cycle 1 Timing Waveform(1)

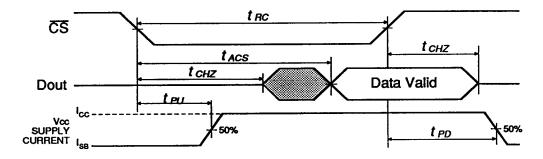

### Read Cycle 2 Timing Waveform (1) (2) (4)

## Read Cycle 3 Timing Waveform(1) (3) (4)

Notes: (1) WE is High for Read Cycle.

- (2) Device is continuously selected, CS=V<sub>L</sub>.

- (3) Address valid prior to or coincident with CS transition Low.

- (4) <del>OE</del>=V<sub>µ</sub>.

- (5) t<sub>cre</sub> and t<sub>cre</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. These parameters are sampled and not 100% tested.

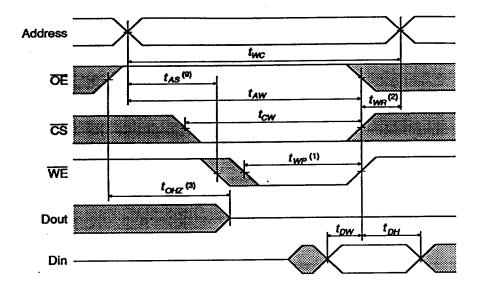

### Write Cycle 1 Timing Waveform (OE Clock)

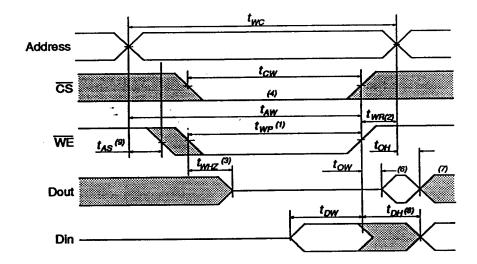

## Write Cycle 2 Timing Waveform (OE Low Fixed)

### **AC Write Characteristics Notes**

- (1) A write occurs during the overlap (two) of a low CS and a low WE.

- (2) t<sub>un</sub> is measured from the earlier of CS or WE going high to the end of write cycle.

- (3) During this period, I/O pins are in the output state. Input signals out of phase must not be applied.

- (4) If the CS low transition occurs simultaneously with the WE low transition or after the WE low transition, outputs remain in a high impedance state.

- (5)  $\overline{OE}$  is continuously low. ( $\overline{OE}$ =V<sub>a</sub>)

- (6) Dout is in the same phase as written data of this write cycle.

- (7) Dout is the read data of next address.

- (8) If CS is low during this period, I/O pins are in the output state. Input signals out of phase must not be applied to I/O pins.

- (9) WE must be high during all address transitions except when the device is deselected with CS.

- (10) t<sub>wiz</sub> and t<sub>ouz</sub> are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. These parameters are sampled and not 100% tested.

| Parameter                            | Symbol             | Test Condition                                                       | min             | n   | nax | Unit |

|--------------------------------------|--------------------|----------------------------------------------------------------------|-----------------|-----|-----|------|

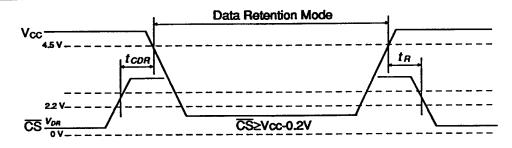

| V <sub>cc</sub> for Data Retention   | V <sub>DB</sub>    | <u>CS</u> ≥ V <sub>∞</sub> -0.2V                                     | 2.0             | -   | -   | ٧    |

| Data Retention Current               | CCDR1              | $V_{cc} = 3.0V$ , $\overline{CS} \ge V_{cc} - 0.2V$ , $T_{cp} = T_A$ | -               | 8   | 200 | μА   |

|                                      |                    | $V_{cc} = 3.0V, \overline{CS} \ge V_{cc} - 0.2V, T_{op} = T_{N}$     |                 | TBA |     | μА   |

|                                      | I <sub>CCDR3</sub> | $V_{cc} = 3.0V, \overline{CS} \ge V_{cc} - 0.2V, T_{op} = T_{AM}$    | -               | -   | 450 | μΑ   |

| Chip Deselect to Data Retention Time | t <sub>con</sub>   | See Retention Waveform                                               | 0               | -   | -   | ns   |

| Operation Recovery Time              | t <sub>R</sub>     | See Retention Waveform                                               | t <sub>RC</sub> | -   | -   | ns   |

## **Data Retention Waveform**

PUMA 2S1010-030/35/45/55/70 ISSUE 2.0 : MAY 1992

### **Military Screening Procedure**

MultiChip Screening Flow for high reliability non-compliant product pocessed to Mil-Std-883 Method 5004 shown below.

| MB MULTICHIP MODULE SCREENING FLOW |                                                               |        |

|------------------------------------|---------------------------------------------------------------|--------|

| SCREEN                             | TEST METHOD                                                   | LEVEL  |

| Visual and Mechanical              |                                                               |        |

| Internal visual                    | 2010 Condition B or manufacturers equivalent                  | 100%   |

| Temperature cycle                  | 1010 Condition C (10 Cycles, -65°C to +150°C)                 | 100%   |

| Constant acceleration              | 2001 Condition B (Y <sub>1</sub> only) (10,000g)              | 100%   |

| Burn-in                            |                                                               |        |

| Pre-Burn-in electrical             | Per applicable device specifications at T <sub>4</sub> =+25°C | 100%   |

| Bum-in                             | Method 1015,Condition D,T <sub>A</sub> =+125°C,160hrs min     | 100%   |

| Final Electrical Tests             | Per applicable Device Specification                           |        |

| Static (dc)                        | a) @ T <sub>x</sub> =+25°C and power supply extremes          | 100%   |

|                                    | b) @ temperature and power supply extremes                    | 100%   |

| Functional                         | a) @ T <sub>4</sub> =+25°C and power supply extremes          | 100%   |

|                                    | b) @ temperature and power supply extremes                    | 100%   |

| Switching (ac)                     | a) @ T <sub>A</sub> =+25°C and power supply extremes          | 100%   |

|                                    | b) @ temperature and power supply extremes                    | 100%   |

| Percent Defective allowable (PDA)  | Calculated at post burn-in at T <sub>A</sub> =+25°C           | 10%    |

| Hermeticity                        | 1014                                                          |        |

| Fine                               | Condition A                                                   | 100%   |

| Gross                              | Condition C                                                   | 100%   |

| Quality Conformance                | Per applicable Device Specification                           | Sample |

| External Visual                    | 2009 Per vendor or customer specification                     | 100%   |

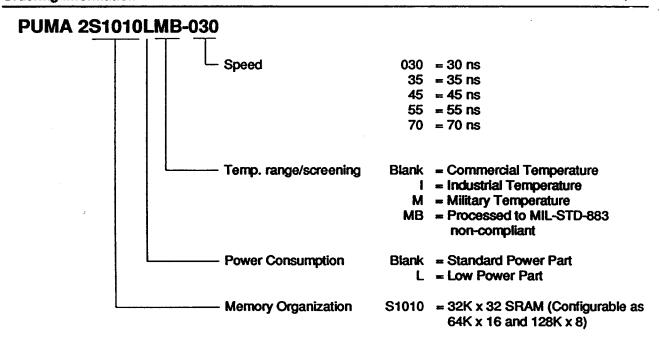

### **Ordering Information**

The policy of the company is one of continuous development and while the information presented in this data sheet is believed to be accurate, no liability is assumed for any data contained within. The company reserves the right to make changes without notice at any time.

© 1988 This design is the property of Mosaic Semiconductor, Inc.

OCT 0 5 1992

032037 🗸 \_ 🚶