# AK491024S / AK491024G 1,048,576 Word x 9 Bit CMOS Dynamic Random Access Memory

## **DESCRIPTION**

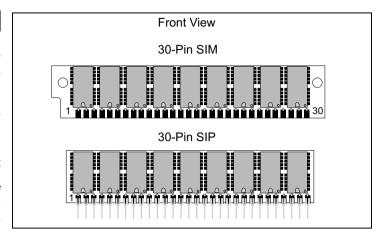

The Accutek AK491024 high density memory module is a random access memory organized in 1 Meg x 9 bit words. The assembly consists of nine standard 1 Meg x 1 DRAMs in plastic leaded chip carriers (SOJ) mounted on the front side of a printed circuit board. The module can be configured as a leadless 30 pad SIM or a leaded 30 pin SIP. This packaging approach provides a 6 to 1 density increase over standard DIP packaging.

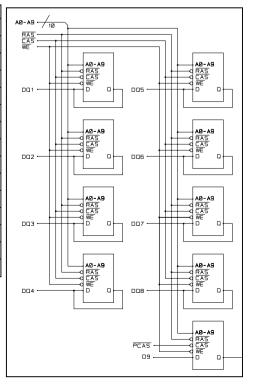

The operation of the AK491024 is identical to nine 1 Meg x 1 DRAMs. For the lower eight bits data input is tied to the data output and brought out separately for each device, with common  $\overline{RAS}$ ,  $\overline{CAS}$  control. This common I/O feature dictates the use of early-write cycles to prevent contention of D and Q. Since the Write-Enable ( $\overline{WE}$ ) signal must always go low before  $\overline{CAS}$  in a write cycle, Read-Write and Read-Modify-Write operation is not possible. For the ninth bit, the data input (D<sub>9</sub>) and the data output (Q<sub>9</sub>) pins are brought out separately and controlled by a separate  $\overline{PCAS}$  for that bit. Bit nine is generally used for parity.

# FEATURES

- 1,048,576 x 9 bit organization

- Optional 30 Pad leadless SIM (Single In-Line Module) or 30 Pin leaded SIP (Single In-Line Package)

- · JEDEC standard pinout

- Common CAS and RAS control for the lower eight bits

- Separate PCAS control for D<sub>9</sub> and Q<sub>9</sub>

- CAS-before-RAS refresh

- Power

3.465 Watt Max Active (80 nSEC)

2.97 Watt Max Active (100 nSEC)

2.475 Watt Max Active (120 nSEC)

49.5 mW Max Standby

- Operating free air temperature 0<sup>0</sup>C to 70<sup>0</sup>C

- · Upward compatible with AK594096 and AK5916384

- Downward compatible with AK49256

## **PIN NOMENCLATURE**

| DQ <sub>1</sub> - DQ <sub>8</sub> | Data In / Data Out    |

|-----------------------------------|-----------------------|

| D <sub>9</sub>                    | Data In 9             |

| Q9                                | Data Out 9            |

| A <sub>0</sub> - A <sub>9</sub>   | Address Inputs        |

| CAS, PCAS                         | Column Address Strobe |

| RAS                               | Row Address Strobe    |

| WE                                | Write Enable          |

| Vcc                               | 5v Supply             |

| Vss                               | Ground                |

| NC                                | No Connect            |

|                                   |                       |

| N | Л | О | D | U | L | Ε | О | Р | Т | I | O | К | V | S |  |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

Leadless SIM: AK491024S Leaded SIP: AK491024G

## **PIN ASSIGNMENT**

| PIN# | SYMBOL | PIN# | SYMBOL |

|------|--------|------|--------|

| 1    | Vcc    | 16   | DQ5    |

| 2    | CAS    | 17   | A8     |

| 3    | DQ1    | 18   | A9     |

| 4    | A0     | 19   | NC     |

| 5    | A1     | 20   | DQ6    |

| 6    | DQ2    | 21   | WE     |

| 7    | A2     | 22   | Vss    |

| 8    | A3     | 23   | DQ7    |

| 9    | Vss    | 24   | NC     |

| 10   | DQ3    | 25   | DQ8    |

| 11   | A4     | 26   | Q9     |

| 12   | A5     | 27   | RAS    |

| 13   | DQ4    | 28   | PCAS   |

| 14   | A6     | 29   | D9     |

| 15   | A7     | 30   | Vcc    |

## **FUNCTIONAL DIAGRAM**

### ORDERING INFORMATION

## PART NUMBER CODING INTERPRETATION

Position 1 2 3 4 5 6 7 8

#### 1 Product

#### AK = Accutek Memory

- 2 Type

- 4 = Dynamic RAM

- 5 = CMOS Dynamic RAM

- 6 = Static RAM

#### 3 Organization/Word Width

- $1 = by 1 \quad 16 = by 16$

- 4 = by 4 32 = by 32

- $8 = by 8 \quad 36 = by 36$

- 9 = by 9

- 4 Size/Bits Depth

#### 5 Package Type

- G = Single In-Line Package (SIP)

- S = Single In-Line Module (SIM)

- D = Dual In-Line Package (DIP)

- W = .050 inch Pitch Edge Connect

- Z = Zig-Zag In-Line Package (ZIP)

#### 6 Special Designation

- P = Page Mode

- N = Nibble Mode

- K = Static Column Mode

- W = Write Per Bit Mode

- V = Video Ram

#### 7 Separator

- = Commercial  $0^{\circ}$ C to + $70^{\circ}$ C

- M = Military Equivalent Screened

- (-55<sup>0</sup>C to +125<sup>0</sup>C)

- I = Industrial Temperature Tested

- (-45<sup>0</sup>C to +85<sup>0</sup>C)

#### X = Burned In

8 Speed (first two significant digits)

| DRAMS |   |       | SRAM | S     |

|-------|---|-------|------|-------|

| 50    | = | 50 nS | 8 =  | 8 nS  |

| 60    | = | 60 nS | 10 = | 10 nS |

| 70    | = | 70 nS | 12 = | 12 nS |

| 80    | = | 80 nS | 15 = | 15 nS |

The numbers and coding on this page do not include all variations available but are show as examples of the most widely used variations. Contact Accutek if other information is required.

#### **EXAMPLES:**

#### AK491024SP-80

1 Meg x 9, 80 nSEC DRAM 30 pin SIM Configuration, Page Mode

#### AK491024GN-70

1 Meg x 9, 70 nSEC Dram 30 pin SIP Configuration, Nibble Mode

## ACCUTEK MICROCIRCUIT CORPORATION

BUSINESS CENTER at NEWBURYPORT 2 NEW PASTURE ROAD, SUITE 1 NEWBURYPORT, MA 01950-4054

VOICE: 978-465-6200 FAX: 978-462-3396 Email: accutek@seacoast.com

Internet: www.accutekmicro.com

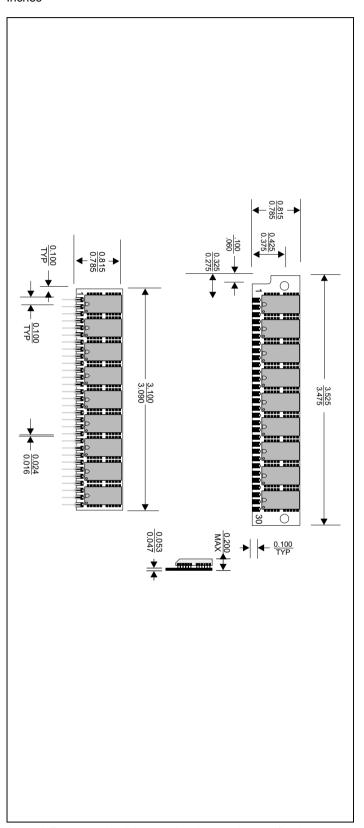

## **MECHANICAL DIMENSIONS**

Inches

Accutek Reserves the right to make changes in specifications at any time and without notice. Accutek does not assume any responsibility for the use of any circuitry described; no circuit patent licenses are implied. Preliminary data sheets contain minimum and maximum limits based upon design objectives, which are subject to change upon full characterization over the specific operating conditions.