DUAL DSX-1 LINE INTERFACE

#### <u>FEATURES</u>

- Integrates two duplex DSX-1 compatible line interface circuits in a single monolithic device.

- Provides clock recovery and line performance monitoring in the receivers.

- Provides jitter attenuation and programmable line build out in the transmitters.

- Utilizes digital phase-locked loops for receive and transmit clock derivation without use of tuned circuits.

- Provides a crystal oscillator and clock doubler for optional on-chip generation of all required clock signals using either a 37.056 MHz or 18.528 MHz master clock.

- Provides a generic microprocessor interface for initial configuration, ongoing control, and status monitoring.

- Generates an interrupt upon detection of any of various alarms, events, or changes in status. Identification of interrupt sources, masking of interrupt sources, and acknowledgement of interrupts is provided via internal registers.

- Low power CMOS technology, 800 mW maximum power dissipation processing all ones signals.

- 84-pin PLCC package.

#### Each receiver section

- Supports reception of DSX-1 compatible signals using only an external 1:2 turns ratio transformer and passive attenuator components.

- Minimum sensitivity of 75 mV with a 1:2 turns ratio transformer allows for terminating or bridged performance monitoring applications.

- Recovers a 1.544 MHz clock and DS-1 data using a digital phase-locked loop to achieve high jitter accommodation.

- Accommodates up to 0.4 UI peak-to-peak, high frequency jitter as required by AT&T TR 64211.

- Optionally outputs either dual rail recovered line pulses or a single rail DS-1 signal.

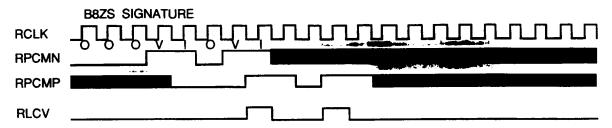

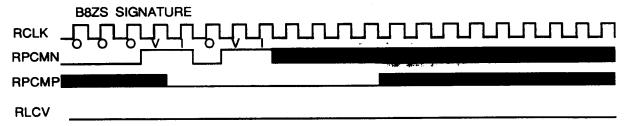

- Optionally performs B8ZS decoding when processing a single rail DS-1 signal.

**DUAL DSX-1 LINE INTERFACE**

- Detects line code violations (LCVs), B8ZS signatures, 8 successive zeros, and 16 successive zeros.

- Accumulates up to 4095 line code violations (LCVs), for performance monitoring purposes, over accumulation intervals defined by the period between software write accesses to the LCV register.

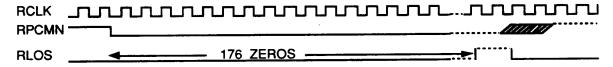

- Detects loss of signal (LOS), which is defined as 176 successive zeros.

- Detects both programmable inband loopback activate and deactivate code sequences received in the DS-1 data stream when they are present for 5 seconds.

- Detects any pair of arbitrary inband codes from three to eight bits in length.

- The inband code detection algorithm operates in the presence of a 10-2 bit error rate.

- Programmable to detect CSU (Channel Service Unit), network, and far-end loopback codes.

- Detects in-band code sequences in both framed and unframed DS-1 streams.

#### Each transmitter section

- Generates DSX-1 compatible pulses with programmable pulse shape using only an external 1:1.36 turns ratio transformer.

- Selectable line length and line type for transmit pulse build out.

- Accommodates standard cable types such as ABAM or PIC.

- Includes special universal, square, and long line build out settings.

- Allows bipolar violation (BPV) transparent operation for error restoring regenerator applications.

- Supports all ones transmission for alarm indication signal (AIS) generation.

- Provides a digital phase-locked loop for generation of jitter reduced transmit output timing. The DPLL utilizes a 37.056 MHz master clock.

- Digital phase-locked loop locks 1.544 MHz output timing to the average frequency of the 1.544 MHz jittered transmit input clock.

- Provides a 2 x 48 bit FIFO for jitter attenuation in the transmit path.

- Provides up to 55 dB of jitter attenuation as per AT&T TR 62411.

**DUAL DSX-1 LINE INTERFACE**

- Digital phase-locked loop introduces minimal phase jitter; ± 0.042 UI peak to peak.

- · Provides FIFO overrun and underrun indicators.

- Inhibits FIFO overrun and underrun for excessive jitter amplitudes.

- Generates a programmable inband loopback code sequence in the PCM voice channel data stream of a DS1 signal.

- Programmable to transmit repetitions of any arbitrary code from three to eight bits in length.

- Supports transmission of unframed loopback code sequences.

- Optionally inputs either dual rail transmit line pulses or a single rail DS-1 signal.

- Optionally performs B8ZS encoding when processing a single rail DS-1 signal.

## **APPLICATIONS**

- Electronic DSX-1 Cross-connects (EDSX)

- Digital Access and Cross-connect Systems (DACS)

- Multiplexers

- Channel Service Units (CSUs)

- DSX-1 Repeaters

- Test Equipment

**DUAL DSX-1 LINE INTERFACE**

#### REFERENCES

- American National Standard for Telecommunications, ANSI T1.102-1987 -"Digital Hierarchy - Electrical Interfaces."

- American National Standard for Telecommunications, ANSI T1.107-1988 "Digital Hierarchy Formats Specifications."

- American National Standard for Telecommunications, ANSI T1.403-1989 -"Carrier to Customer Installation, DS1 Metallic Interface Specification."

- American National Standards for Telecommunications, ANSI Draft Standard T1X1.6/89-019R2 "Jitter Measurement Methodology."

- American National Standards for Telecommunications, ANSI Draft Standard T1E1.2/88-079R8 "Jitter Measurement Methodology."

- American Telephone and Telegraph Company Compatibility Bulletin No. 119 -"Interconnection Specification for Digital Cross Connects," Issue 3, October, 1979.

- Bell Communications Research, "TR-TSY-000009, Asynchronous Digital Multiplexes Requirements and Objectives," Issue 1, May 1986.

- Bell Communications Research, TR-TSY-000170 "Digital Cross-Connect System (DCS) Requirements and Objectives," Issue 1, November, 1985.

- Bell Communications Research "Integrated Digital Loop Carrier System Generic Requirements, Objectives, and Interface," TR-TSY-000303, Issue 1, Rev. 1, December 1987.

- Bell Communications Research "Functional Criteria for the DS1 Interface Connector," TR-TSY-000312, Issue 1, March 1988.

- Bell Communications Research, TR-TSY-0000499, "Transport Systems Generic Requirements (TSGR): Common Requirements," Issue 2, December 1988

- AT&T, PUB 43801, "Digital Channel Bank Requirements and Objectives", November 1982.

- AT&T, PUB 43802 "Digital Multiplexers Requirements and Objectives.", July 1982.

- AT&T, TR 62411 Accunet T1.5 "Service Description and Interface Specification" December, 1988.

**DUAL DSX-1 LINE INTERFACE**

Telecom Canada, ISBN 0-920267-00-9 - "Technical Planning and Standards -Digital Network Notes," 1983.

#### **DESCRIPTION**

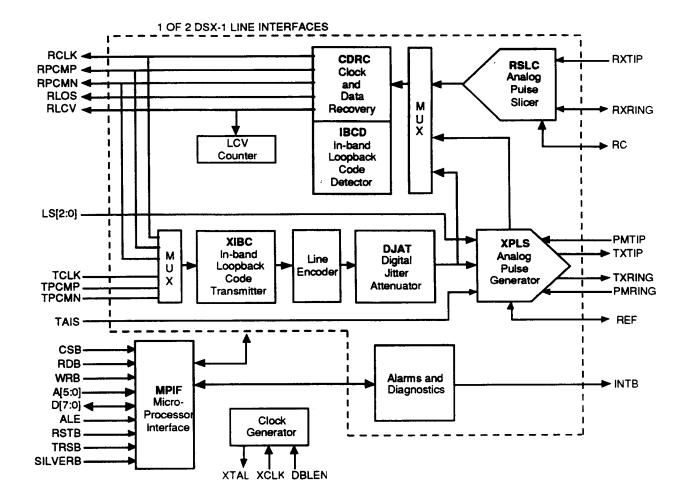

The PM4312 DDSX Dual DSX-1 Line Interface is a monolithic integrated circuit that supports DSX-1 compatible transmit and receive interfaces for two 1.544 Mbit/s data streams.

In the incoming direction, DSX-1 signals for each half of the DDSX are first processed by a receive data slicer. The receive data slicer converts the line signal received via a coupling transformer to dual rail RZ digital pulses. Adaptation for attenuation is achieved using an integral peak detector that sets the slicing levels. Through use of passive external attenuation circuitry, either terminated or bridge monitored DSX-1 signal levels can be accommodated. The low signal level condition or signal squelch may be enabled to generate interrupts. Clock and data are recovered from the dual rail RZ digital pulses using a digital phase-locked loop that provides excellent high frequency jitter accommodation. The recovered data is decoded using AMI, or optionally, B8ZS line code rules and is presented either as a DS-1 stream or presented in an undecoded dual rail NRZ format. Loss of signal and line code violations are detected as well as 8 successive zeros, 16 successive zeros, and the B8ZS signature. The presence of either of two programmable inband loopback codes is also detected. These various events or changes in status may be enabled to generate interrupts. Additionally, loss of signal and line code violations are also indicated on outputs.

In the outgoing direction, each half of the DDSX may accept either a DS-1 stream to be encoded using AMI, or optionally B8ZS, line code rules, or it may accept pre-encoded data in dual rail NRZ format. Jitter attenuation is provided by passing outgoing data through a FIFO. A low jitter clock is generated by an integral digital phase-locked loop and is used to read data from the FIFO. FIFO overrun or underrun may be enabled to generate interrupts. Alarm indication signal (all ones) may be substituted for the FIFO data. The digital data is converted to high drive, dual rail RZ pulses that drive the DSX-1 interface through a coupling transformer. The shape of the pulses is programmable to ensure that the DSX-1 pulse template is met after the signal is passed through various lengths of cable. Driver performance monitoring is provided and may be enabled to generate interrupts upon driver failure.

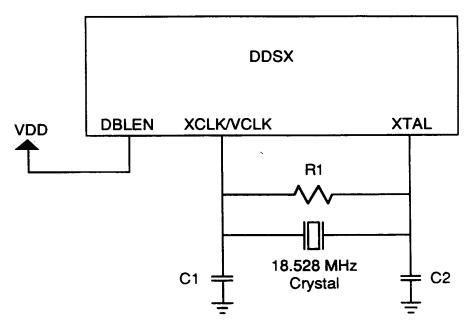

Internal high speed timing for both halves of the DDSX is provided by a common 37.056 MHz master clock. Support is provided for an external crystal. An 18.528 MHz crystal or clock source may be utilized by enabling an integral clock doubler circuit.

Diagnostic loopback is provided and the loopback may be invoked past the analog transmit outputs using the driver performance monitors or invoked prior to the

#### TELECOM STANDARD PRODUCT

## PM4312 DDSX

PRELIMINARY INFORMATION

**DUAL DSX-1 LINE INTERFACE**

conversion to analog. Line loopback with jitter attenuation is provided and may be enabled for automatic operation based on detected inband loopback codes.

The DDSX may insert inband loopback code sequences into an outgoing unframed PCM data stream. These codes consist of continuous repetitions of specific bit sequences. Any arbitrary code from three to eight bits in length is programmable by writing to configuration registers.

The DDSX operates in conjunction with external line coupling transformers, resistors, and capacitors. An external crystal may be used for high speed timing generation. The DDSX is configured, controlled, and monitored using registers that are accessed via a generic microprocessor interface.

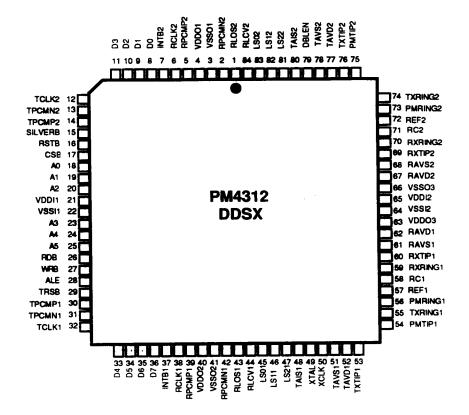

## **PINOUT**

The DDSX is packaged in an 84-pin PLCC package.

## **BLOCK DIAGRAM**

## PIN DESCRIPTION

| Connector<br>Name  | Type             | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                              |

|--------------------|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XCLK/<br>VCLK      | Input            | 50         | The system clock (XCLK) provides timing for DDSX internal operation. XCLK may be driven externally or connected to an appropriate crystal. XCLK may be a 37.056 MHz or 18.528 MHz, 50% duty cycle clock, as selected by the DBLEN input. The test vector clock (VCLK) signal is used during DDSX production testing to verify internal functionality. |

| XTAL               | Output           | 49         | The crystal output (XTAL) may be connected to a crystal in conjunction with XCLK to form a crystal oscillator. When not used, XTAL should be left unconnected.                                                                                                                                                                                        |

| DBLEN              | Input            | 79         | The clock doubler enable (DBLEN) signal determines whether an internal clock doubler circuit is active. When DBLEN is low, the clock doubler is disabled and XCLK must be a 37.056 MHz clock for proper operation. When DBLEN is high, the clock doubler is enabled and XCLK must be a 18.528 MHz clock.                                              |

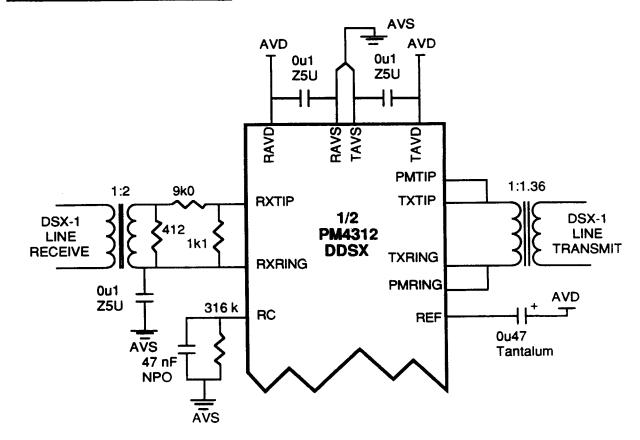

| TXTIP1<br>TXTIP2   | Analog<br>Output | 76         | The transmit tip (TXTIP) signals drive the line through line coupling transformers associated with the corresponding DS-1 signal. These outputs can drive 54 $\Omega$ loads. Use of a 1:1.36 step up transformer is required.                                                                                                                         |

| TXRING1<br>TXRING2 | Analog<br>Output | 1 71       | The transmit ring (TXRING) signals drive the line through line coupling transformers associated with the corresponding DS-1 signal. These outputs can drive 54 $\Omega$ loads. Use of a 1:1.36 step up transformer is required.                                                                                                                       |

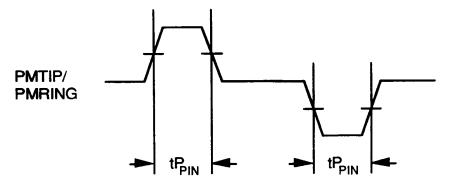

| PMRING1<br>PMRING2 | Analog<br>Input  | 56<br>73   | The driver performance monitor ring (PMRING) inputs are used for driver performance monitoring. Each PMRING input can be connected to either its corresponding TXRING output, or an adjacent channel's TXRING output.                                                                                                                                 |

| PMTIP1<br>PMTIP2                    | Analog<br>Input | 54<br>75 | The driver performance monitor tip (PMTIP) inputs are used for driver performance monitoring. Each PMTIP input can be connected to either its corresponding TXTIP output, or an adjacent channel's TXTIP output.                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

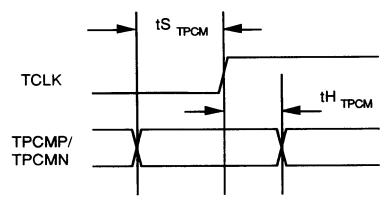

| TCLK1<br>TCLK2                      | I/O             | 32<br>12 | The transmit PCM clock (TCLK) inputs provide timing for transmission of the corresponding DS-1 stream. The TCLK signals are nominally 1.544 MHz, 50% duty cycle clocks. The inputs TPCMP, TPCMN, and TAIS are sampled on the rising edge of the corresponding TCLK signal. Note that the TCLK signals may become outputs when SILVERB is low.                                                                                                                                                                         |

| TPCMP1<br>TPCMP2                    | Input           | 30<br>14 | The transmit positive PCM pulse (TPCMP) inputs are sampled on the rising edge of the corresponding TCLK signal. When a TPCMP input is high a positive pulse is generated across the corresponding TXTIP and TXRING outputs; TXTIP sources current and TXRING sinks current. Note that if a pair of TPCMP and TPCMN signals are both high, no pulse is generated. When dual rail interfacing is disabled, the TPCMP inputs carry DS-1 data that is encoded by the DDSX using AMI, or optionally, B8ZS line code rules. |

| TPCMN1<br>TPCMN2/<br>TEXP1<br>TEXP2 | Input           | 31<br>13 | The transmit negative PCM pulse (TPCMN) inputs are sampled on the rising edge of the corresponding TCLK signal. When a TPCMN input is high a negative pulse is generated across the corresponding TXTIP and TXRING outputs; TXRING sources current and TXTIP sinks current. Note that if a pair of TPCMP and TPCMN signals are both high, no pulse is generated. When dual rail interfacing is disabled, the TPCMN inputs are referred to as TEXP or are used to mark the framing bit position.                       |

| TAIS1<br>TAIS2                      | I/O             | 48<br>80 | The transmit alarm indication signal (TAIS) inputs are sampled on the rising edge of the corresponding TCLK signal but may be asynchronous to TCLK. When TAIS is high, an all ones signal (alternating positive and negative pulses) is generated on the corresponding TXTIP and TXRING outputs. Note that the TAIS signals may become outputs when SILVERB is low.                                                                                                                                                   |

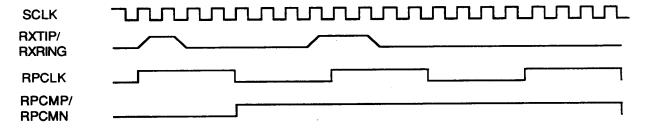

| RXTIP1           | Analog | 60      | The receive tip (RXTIP) inputs connect a line coupling transformer to the receive data slicer that processes the corresponding DS-1 stream. An external passive 20 dB attenuation network is required when interfacing to DSX-1 signal levels using a 1:2 step up transformer. The external attenuation network is not required in performance monitor applications where 20 dB of attenuation inherently occurs while bridging onto the DSX-1 signal. |

|------------------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXTIP2           | Input  | 69      |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

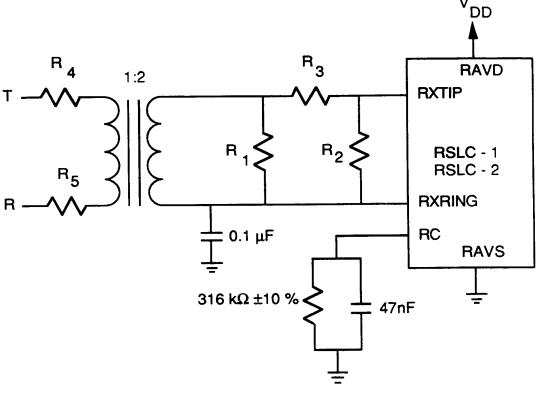

| RXRING1          | Analog | 59      | The receive ring (RXRING) signals provide a bias voltage for the line coupling transformer associated with the corresponding DS-1 stream. These nodes must be decoupled to ground with 0.1 µF capacitors.                                                                                                                                                                                                                                              |

| RXRING2          | I/O    | 70      |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RC1              | Analog | 58      | The external peak detector RC network (RC) signals connect the peak detector of the receive data slicer that processes the corresponding DS-1 stream to an external RC network. The RC network consists of a grounded, parallel resistor and capacitor network, with nominal values of 316K $\Omega$ and 47 nF, respectively.                                                                                                                          |

| RC2              | I/O    | 71      |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

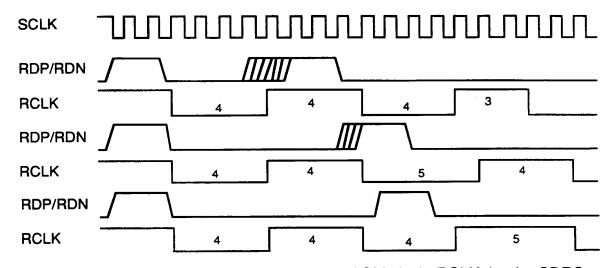

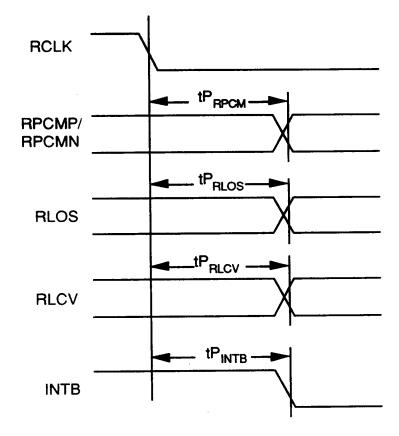

| RCLK1<br>RCLK2   | Output | 38<br>6 | The recovered PCM clock (RCLK) signals are synchronized with the corresponding received 1.544 Mbit/s DS-1 signals. The RCLK signals are generated using digital phase-locked loops that use an 8 x (12.352 MHz) high speed clock. The instantaneous period of each RCLK signal can be seven, eight, or nine high speed clock (12.352 MHz) periods.                                                                                                     |

| RPCMP1<br>RPCMP2 | Output | 39<br>5 | The recovered positive PCM pulse (RPCMP) outputs are updated on the falling edge of the corresponding RCLK signal. When dual rail interfacing is disabled, the RPCMP outputs carry DS-1 data that is decoded by the DDSX assuming AMI, or optionally, B8ZS line code rules.                                                                                                                                                                            |

| RPCMN1<br>RPCMN2 | Output | 42 2    | The recovered negative PCM pulse (RPCMN) outputs are updated on the falling edge of the corresponding RCLK signal. When dual rail interfacing is disabled, the RPCMN outputs carry DS-1 data that is decoded by the DDSX assuming AMI line code rules.                                                                                                                                                                                                 |

| RLOS1<br>RLOS2 | Output        | 43<br>1  | The receiver loss of signal (RLOS) outputs are set high upon detection of 176 consecutive zero bit intervals on the corresponding recovered PCM stream. The PCM streams are examined prior to optional B8ZS decoding. The RLOS outputs are reset low when a non-zero bit interval is detected on the corresponding recovered PCM stream. The RLOS outputs are updated on the falling edge of the corresponding RCLK signal. |

|----------------|---------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RLCV1<br>RLCV2 | Output        | 44<br>84 | The receiver line code violation (RLCV) outputs are set high upon detection of a line code violation on the corresponding recovered PCM stream. Bipolar violations that are part of the B8ZS signature are not flagged as line code violations if optional B8ZS decoding is enabled. The RLCV outputs are updated on the falling edge of the corresponding RCLK signal.                                                     |

| REF1<br>REF2   | Analog<br>I/O | 57<br>72 | The voltage reference signals (REF) provide decoupling to the bias voltage generator in the Transmit Pulse Generator. These signals must be decoupled to TAVD with 470 nF capacitors, and must not be loaded.                                                                                                                                                                                                               |

| LS01<br>LS02   | 1/0           | 45<br>83 | The line length select (LS0) signals select the transmit pulse shape applied to the corresponding DSX-1 interface. The LS0 signal, and the corresponding LS1 and LS2 signals select one of eight transmit pulse shapes. Note that the LS0 signals become outputs when SILVERB is low. The LS0 signals have integral pull up resistors.                                                                                      |

| LS11<br>LS12   | I/O           | 46<br>82 | The line length select (LS1) signals select the transmit pulse shape applied to the corresponding DSX-1 interface. The LS1 signal, and the corresponding LS0 and LS2 signals select one of eight transmit pulse shapes. Note that the LS1 signals become outputs when SILVERB is low. The LS1 signals have integral pull up resistors.                                                                                      |

| LS21<br>LS22   | I/O           | 47<br>81 | The line length select (LS2) signals select the transmit pulse shape applied to the corresponding DSX-1 interface. The LS2 signal, and the corresponding LS0 and LS1 signals select one of eight transmit pulse shapes. Note that the LS2 signals become outputs when SILVERB is low. The LS2 signals have integral pull up resistors.                                                                                      |

| INTB1<br>INTB2                               | Output | <b>37</b> 7                                | The interrupt (INTB) signals go low when any of the various interrupting sources within the DDSX related to the corresponding DS-1 stream is active and is enabled to generate interrupts. The INTB signals go high when the interrupt is acknowledged by reading a status register or masked via the interrupt enable register. The INTB outputs are open drain outputs. Note that when SILVERB is low, the TSB interrupt signals reported on the INTB signals remain inverted. |

|----------------------------------------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

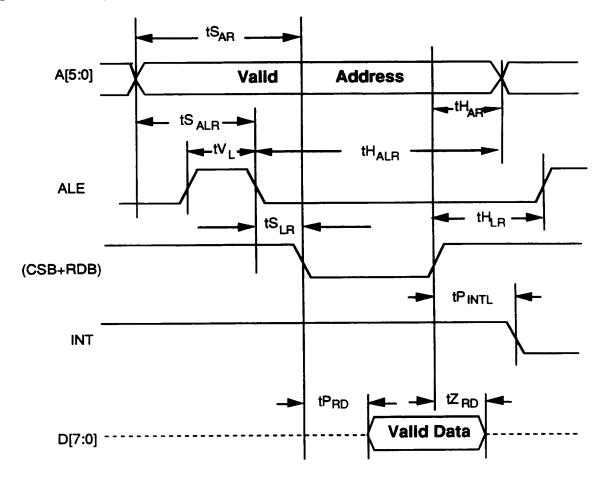

| CSB                                          | Input  | 17                                         | The active low chip select (CSB) signal is low during DDSX register accesses.                                                                                                                                                                                                                                                                                                                                                                                                    |

| RDB                                          | Input  | 26                                         | The active low read enable (RDB) signal is low during a DDSX register read access. The DDSX drives the D7-D0 bus with the contents of the addressed register while RDB and CSB are low.                                                                                                                                                                                                                                                                                          |

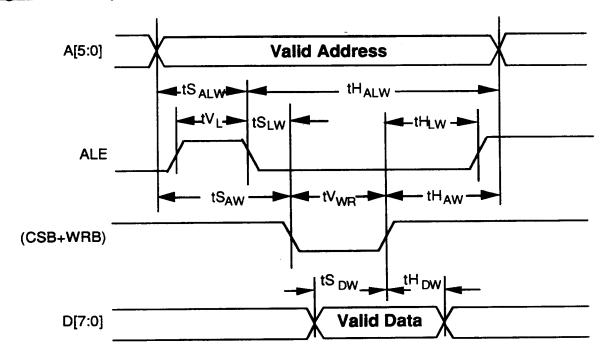

| WRB                                          | Input  | 27                                         | The active low write strobe (WRB) signal is low during a DDSX register write access. The D7-D0 bus contents are clocked into the addressed register on the rising WRB edge while CSB is low.                                                                                                                                                                                                                                                                                     |

| D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | VO     | 8<br>9<br>10<br>11<br>33<br>34<br>35<br>36 | The bidirectional data bus (D7-D0) is used during DDSX register read and write accesses.                                                                                                                                                                                                                                                                                                                                                                                         |

| A0<br>A1<br>A2<br>A3-A5                      | Input  | 18<br>19<br>20<br>23:25                    | The address bus (A5-A0) selects specific registers during DDSX register accesses.                                                                                                                                                                                                                                                                                                                                                                                                |

| RSTB                                         | Input  | 16                                         | The active low reset (RSTB) signal provides an asynchronous DDSX reset. RSTB is a Schmitt triggered input with an integral pull up resistor.                                                                                                                                                                                                                                                                                                                                     |

| ALE                                          | Input  | 28                                         | The address latch enable (ALE) is active high and latches the address bus (A5-A0) and TRSB when low. When ALE is high, the internal address latches are transparent. It allows the DDSX to interface to a multiplexed address/data bus. The ALE input will have an integral pull up resistor.                                                                                                                                                                                    |

| between normal and test mode register accesses. TRSB is low during test mode register accesses, and is high during normal mode register accesses. TRSB has an integral pull up resistor.  SILVERB  Input  15  The active low silicon verification mode select (SILVERB) signal places the DDSX in a mode where constituent TSBs are made visible for test purposes. In this mode, the functions of some of the digital inputs or outputs of the DDSX are redefined. For line interface operation this signal must be held high. SILVERB has an integral pull up resistor.  RAVD1  RAVD2  Power  62  The receive analog power (RAVD) connections each provide power to the receive data slicer in the corresponding DSX-1 interface. Each RAVD pin must be connected to a well decoupled +5 V DC supply.  RAVS1  Ground  61  The receive analog ground (RAVS) connections each provide ground for the receive data slicer in the corresponding DSX-1 interface.  TAVD1  Power  TAVD2  TAVD2  TAVD1  Power  TAVS2  TAVS1  Ground  TAVS2  The transmit analog power (TAVD) connections each provide power for the transmit pulse generator in the corresponding DSX-1 interface.  Each TAVD pin must be connected to a well decoupled +5 V DC supply.  TAVS1  TAVS1  TAVS1  TAVS1  TAVS2  The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  Each TAVD pin must be connected to a well decoupled +5 V DC supply.  TAVS1  TAVS1  TAVS2  The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1  Power  21  The core power (VDDI) pins should be connected to a well decoupled +5 V DC in common with VDDO.  VSSI1  Ground  VSSI1  Ground  The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VSSI.  The pad ring ground (VSSO) pins should be connected to GND in common with VSSI. |         |        |    |                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (SILVERB) signal places the DDSX in a mode where constituent TSBs are made visible for test purposes. In this mode, the functions of some of the digital inputs or outputs of the DDSX are redefined. For line interface operation this signal must be held high. SILVERB has an integral pull up resistor.  RAVD1 Power 62 The receive analog power (RAVD) connections each provide power to the receive data slicer in the corresponding DSX-1 interface. Each RAVD pin must be connected to a well decoupled +5 V DC supply.  RAVS1 Ground 61 The receive analog ground (RAVS) connections each provide ground for the receive data slicer in the corresponding DSX-1 interface.  TAVD1 Power 52 The transmit analog power (TAVD) connections each provide power for the transmit pulse generator in the corresponding DSX-1 interface. Each TAVD pin must be connected to a well decoupled +5 V DC supply.  TAVS1 Ground 51 The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1 Power 21 The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1 Power 21 The core power (VDDI) pins should be connected to a well decoupled +5 V DC in common with VDDO.  VSSI1 Ground 22 The core ground (VSSI) pins should be connected to GND in common with VSSO.  VDDO1 Power 4 The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VSSO.  VSSO1 Ground 3 The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                          | TRSB    | Input  | 29 | TRSB is low during test mode register accesses, and is high during normal mode register accesses.                                                                                                                                                                                              |

| RAVD2  67 each provide power to the receive data slicer in the corresponding DSX-1 interface. Each RAVD pin must be connected to a well decoupled +5 V DC supply.  RAVS1 RAVS2  Ground 61 68 The receive analog ground (RAVS) connections each provide ground for the receive data slicer in the corresponding DSX-1 interface.  TAVD1 TAVD2  TAVD2  TAVD2  The transmit analog power (TAVD) connections each provide power for the transmit pulse generator in the corresponding DSX-1 interface.  Each TAVD pin must be connected to a well decoupled +5 V DC supply.  TAVS1 TAVS2  Ground TAVS2  The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1 VDDI2  Power The core power (VDDI) pins should be connected to a well decoupled +5 V DC in common with VDDO.  VSSI1 VSSI2  Ground The core ground (VSSI) pins should be connected to GND in common with VSSO.  The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VDDI.  VSSO1 VSSO1 Ground The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SILVERB | Input  | 15 | (SILVERB) signal places the DDSX in a mode where constituent TSBs are made visible for test purposes. In this mode, the functions of some of the digital inputs or outputs of the DDSX are redefined. For line interface operation this signal must be held high. SILVERB has an integral pull |

| RAVS2  68  each provide ground for the receive data slicer in the corresponding DSX-1 interface.  TAVD1 TAVD2  Power 52 The transmit analog power (TAVD) connections each provide power for the transmit pulse generator in the corresponding DSX-1 interface.  Each TAVD pin must be connected to a well decoupled +5 V DC supply.  TAVS1 TAVS2  Ground 51 The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1 VDDI2  Power 21 The core power (VDDI) pins should be connected to a well decoupled +5 V DC in common with VDDO.  VSSI1 Ground 22 The core ground (VSSI) pins should be connected to GND in common with VSSO.  The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VDDI.  VSSO1 VSSO1 Ground 3 The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | Power  | _  | each provide power to the receive data slicer in the corresponding DSX-1 interface. Each RAVD pin must be connected to a well decoupled +5 V DC                                                                                                                                                |

| TAVD2  77 each provide power for the transmit pulse generator in the corresponding DSX-1 interface. Each TAVD pin must be connected to a well decoupled +5 V DC supply.  TAVS1 TAVS2  Ground TAVS2  The transmit analog ground (TAVS) connections each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1 VDDI2  Power VDDI2  The core power (VDDI) pins should be connected to a well decoupled +5 V DC in common with VDDO.  VSSI1 VSSI2  Ground The core ground (VSSI) pins should be connected to GND in common with VSSO.  The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VDDI.  VSSO1 VSSO1 VSSO1 Ground The pad ring ground (VSSO) pins should be connected to a well decoupled +5 V DC in common with VDDI.  The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | Ground | -  | each provide ground for the receive data slicer in                                                                                                                                                                                                                                             |

| TAVS2  78 each provide ground for the transmit pulse generator in the corresponding DSX-1 interface.  VDDI1 VDDI2  Power 21 The core power (VDDI) pins should be connected to a well decoupled +5 V DC in common with VDDO.  VSSI1 VSSI2  Ground 22 The core ground (VSSI) pins should be connected to GND in common with VSSO.  VDDO1 VDDO2 VDDO3  Power 4 The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VDDI.  VSSO1 VSSO2  Ground 3 The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | Power  |    | each provide power for the transmit pulse generator in the corresponding DSX-1 interface. Each TAVD pin must be connected to a well                                                                                                                                                            |

| VDDI2  65  to a well decoupled +5 V DC in common with VDDO.  VSSI1  VSSI2  Ground 22  The core ground (VSSI) pins should be connected to GND in common with VSSO.  VDDO1  VDDO2  VDDO3  Power 4  The pad ring power (VDDO) pins should be connected to a well decoupled +5 V DC in common with VDDI.  VSSO1  VSSO1  Ground 3  The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       | Ground | -  | each provide ground for the transmit pulse                                                                                                                                                                                                                                                     |

| VSSI2  VDDO1 VDDO2 VDDO3  Power 4 40 connected to a well decoupled +5 V DC in common with VDDI.  VSSO1 VSSO2  Ground 3 41  The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1       | Power  |    | to a well decoupled +5 V DC in common with                                                                                                                                                                                                                                                     |

| VDDO3  40 connected to a well decoupled +5 V DC in common with VDDI.  VSSO1 VSSO2  Ground 3 The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | :       | Ground |    | The core ground (VSSI) pins should be connected to GND in common with VSSO.                                                                                                                                                                                                                    |

| VSSO2 41 connected to GND in common with VSSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDDO2   | Power  | 40 | connected to a well decoupled +5 V DC in                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VSSO2   | Ground |    | The pad ring ground (VSSO) pins should be connected to GND in common with VSSI.                                                                                                                                                                                                                |

**DUAL DSX-1 LINE INTERFACE**

#### Notes on Pin Description:

- 1. All DDSX inputs and bidirectionals present minimum capacitive loading and operate at TTL logic levels.

- 2. All DDSX digital outputs and bidirectionals have 2 mA drive capability, except the INTB outputs and the D7-D0 bidirectionals, which have 4 mA drive capability.

- 3. The functions of inputs XCLK, DBLEN, TCLK, TCPMP, TPCMN, TAIS, and A5-A2 are redefined for test purposes when SILVERB is low.

- 4. The functions of outputs RCLK, RPCMP, RPCMN, RLOS, RLCV, and INTB are redefined for test purposes when SILVERB is low.

- 5. The VSSO, VSSI, TAVS, and RAVS ground pins are not internally connected together. Failure to connect these pins externally may cause malfunction or damage the DDSX.

- 6. The VDDO, VDDI, TAVD, and RAVD power pins are not internally connected together. Failure to connect these pins externally may cause malfunction or damage the DDSX.

- 7. The drive capability of DDSX T1 line driver outputs is 70 ma.

**DUAL DSX-1 LINE INTERFACE**

#### **FUNCTIONAL DESCRIPTION**

## Receive Data Slicer

The Receive Data Slicer (RSLC) Block provides the first stage of signal conditioning for a DSX-1 serial data stream by converting bipolar line signals to dual rail RZ pulses. Before an RZ output pulse is generated by the RSLC Block, bipolar input signals must rise to 67% of their peak amplitude. This level is the Slicing Level. This threshold criteria insures accurate pulse or mark recognition in the presence of noise.

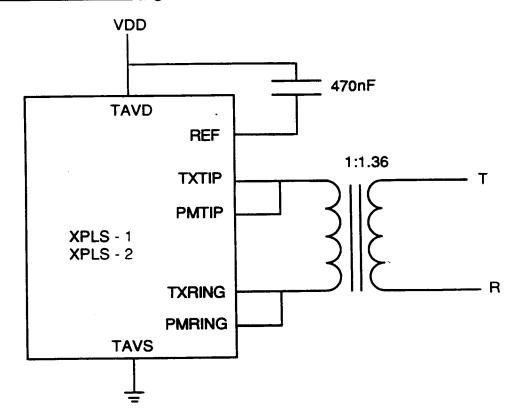

The RSLC Block is configured via an off-chip attenuator pad (see Fig. 1) to operate in one of two modes: normal mode or performance monitor mode. In normal mode, the amplitude of a received pulse at the line-coupling transformer's primary can be in the range from 3.6 V to 0.5 V, depending on the DDSX's distance from the DSX-1 cross-connect. In performance monitor mode, the DDSX is bridged across the line and the expected signal levels are 20 dB lower than standard DSX-1 levels. In each mode the sensitivity below minimum DSX-1 levels is -10 dB. The sensitivity of the receiver is defined as the difference between the worst case DSX-1 signal amplitude (2.4 V) and the squelching level.

The RSLC Block has two signal level alarms that are operational in both normal and performance monitor modes. The first alarm is the low signal level alarm. This alarm occurs when input pulses at the primary of the line-coupling transformer are below the low level threshold but above the squelching level threshold. During a low level alarm, the RSLC Block continues to operate and the LV status bit goes high. The low level signal threshold is 1.5 V for normal mode, and 150 mV for performance monitor mode. The RSLC Block can be configured to generate an interrupt when the LV status bit goes high.

The second alarm occurs when input pulses are below the squelching level threshold. In this state, data is not sliced, which prevents the detection of noise on an idle transmission line. For the normal mode of operation, the squelching threshold is 0.5 V; for performance monitor mode, the squelching threshold is 50 mV. The SQ status bit goes high whenever the RSLC Block is squelching. The block can be configured to generate an interrupt whenever the SQ status bit goes high.

The RSLC Block meets the requirements for receiving a DSX-1 compatible signal as defined in ANSI T1.102 and the other cited references.

## Fig. 1 External Analog Receive Interface Circuit

#### Normal Mode

$$R_1 = 412 \Omega \pm 1\%$$

$R_2 = 1.1 k\Omega \pm 1\%$

$R_3 = 9.0 k\Omega \pm 1\%$

$R_4 = R_5 = \text{Closed Circuit}$

(All capacitors ceramic)

## Clock & Data Recovery

The Clock and Data Recovery (CDRC) Block provides clock and PCM data recovery, B8ZS decoding, bipolar violation detection, and loss of signal detection. The CDRC Block recovers the clock from the incoming RZ data pulses using a digital phase-locked loop and recovers the NRZ data. Loss of signal is indicated after 176 consecutive bit periods of absence of pulses on both the positive and negative pulse inputs. Loss of Signal is cleared after the occurrence of a single line pulse. If enabled, a microprocessor interrupt is generated when a loss of signal is detected and again when the signal returns.

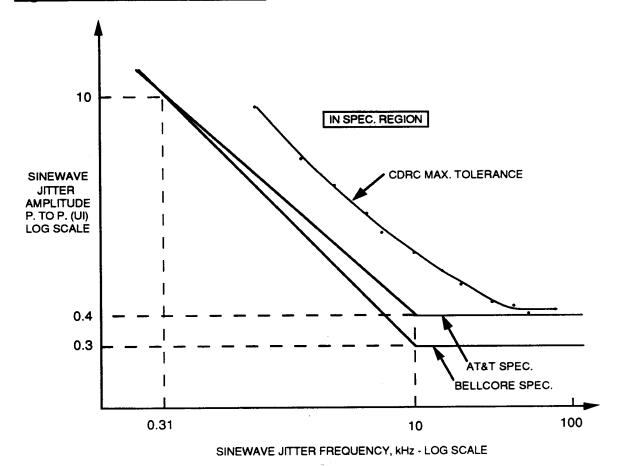

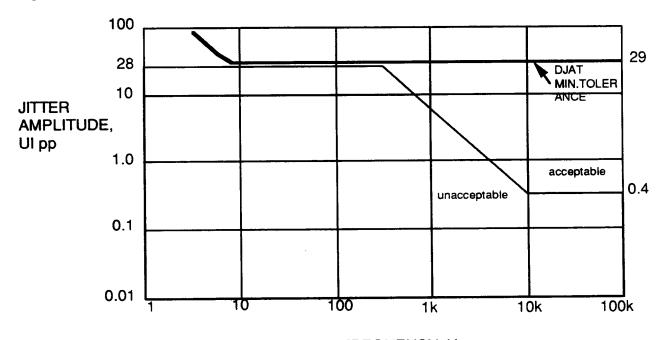

#### Jitter Tolerance

The CDRC Block provides excellent high frequency jitter tolerance. It can accomodate up to 0.4 Ulpp of jitter at jitter frequencies above 10 kHz. For jitter frequencies below 10 kHz, jitter tolerance increases 20 dB per decade reaching 10 Ulpp at 700 Hz. In most applications the CDRC Block will limit jitter tolerance at higher jitter frequencies only. For low frequency jitter, below 10 kHz for example, other factors such as jitter attenuator buffer depth and transfer characteristics or slip buffer hysteresis may limit jitter tolerance and must be considered. The CDRC Block meets the stringent high frequency jitter tolerance requirements of AT&T TR 62411 and Bellcore TR-TSY-000170 and thus allows one to comply with these standards and the other less stringent jitter tolerance standards cited in the references.

Fig. 2 CDRC Jitter Tolerance

#### **Inband Code Detector**

The Inband Code Detector (IBCD) Block detects the presence of either of two programmable inband loopback activate and deactivate code sequences in either

DUAL DSX-1 LINE INTERFACE

framed or unframed received data streams. The code must be present continuously for at least 5.06Sec.  $\pm$  39.8msec. for detection. IBCD operates in the presence of  $10^{-2}$  bit error rate. Inband loopback codes are specified in ANSI T1.403, Bellcore TR-TSY-000312, and TR-TSY-000303.

#### Line Code Violation Counter

The Line Code Violation Counter block (PMON) accumulates the number of line code violations (LCVs) occurring in the incoming PCM stream during one accumulation interval. The counter is 12 bits long and can accumulate up to 4095 LCVs before saturating. This length provides a less than 0.001% probability of the counter saturating at a 10-3 bit error rate (BER) if the accumulation period is one second.

The PMON block contains a counter and a holding register. The current counter value is transferred to the holding register when triggered by a write access to the holding register via the microprocessor interface. Simultaneously, the counter is cleared in such a way that prevents an LCV event occurring during the clearing from being missed. The period between successive writes to the holding register defines the accumulation interval.

## **Digital Jitter Attenuator**

The Digital Jitter Attenuator (DJAT) Block receives jittered T1 data in NRZ format at the positive and negative pulse inputs. The incoming data streams are stored in the FIFO registers on the rising edge of the input clock (ICLK). The positive and negative input data emerges jitter-attenuated from the FIFO on the falling edge of SCO.

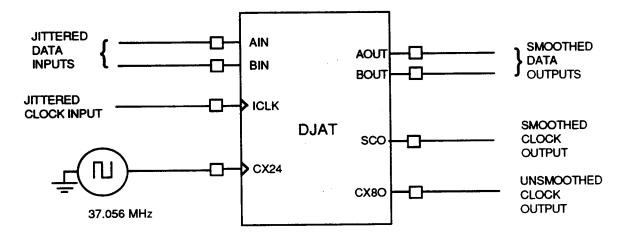

## Fig. 3 DJAT Configuration

**DUAL DSX-1 LINE INTERFACE**

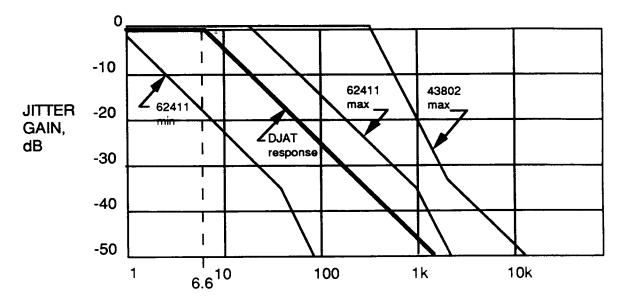

The jitter attenuator generates the 1.544 MHz SCO output by adaptively dividing the 37.056 MHz CX24 system clock according to the phase difference between SCO and ICLK. Jittered fluctuations in the phase of ICLK are attenuated by the phase-locked loop in DJAT so that the frequency of SCO is equal to the average frequency of ICLK. To best fit the jitter attenuation transfer function recommended by TR 62411, phase fluctuations with a jitter frequency above 6.6 Hz are attenuated by 6 dB per octave of jitter frequency. Wandering phase fluctuations with frequencies below 6.6 Hz are tracked by SCO. To provide a smooth flow of output data, SCO is used to shift data out of the FIFO.

Should the FIFO read pointer in DJAT come within one bit of the write pointer, DJAT will track the jitter of ICLK. Permitting the phase jitter to pass through unattenuated in this condition will inhibit the loss of data.

#### **Jitter Tolerance**

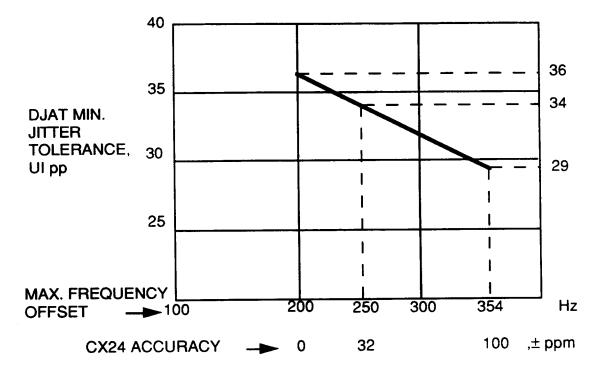

Jitter tolerance is the maximum input phase jitter at a given jitter frequency that a device can accept without exceeding its linear operating range, or corrupting data. For DJAT, the input jitter tolerance is 29 Unit Intervals peak-to-peak (Ulpp) with a worst case frequency offset of 354 Hz. It is 48 Ulpp with no frequency offset. The frequency offset is the difference between the frequency of CX24 divided by 24 (CX24/24) and that of the ICLK clock input.

## Fig. 4 DJAT Jitter Tolerance

JITTER FREQUENCY, Hz

**DUAL DSX-1 LINE INTERFACE**

The accuracy of the system clock frequency and that of the DJAT.REF input have an effect on the minimum jitter tolerance. Given that the frequency of DJAT.REF can be ±200 Hz from 1.544 MHz, figure 5 is a plot of minimum jitter tolerance for various differences between the frequency of DJAT.REF and DJAT.CX24/24.

Fig. 5 DJAT Minimum Jitter Tolerance vs. CX24 Accuracy

#### **Jitter Transfer**

The output jitter for jitter frequencies from 0 to 6.6 Hz will be no more than 0.1 dB greater than the input jitter, excluding the 0.042 UI residual jitter. Jitter frequencies above 6.6 Hz are attenuated at a level of 6 dB per octave.

Fig. 6 DJAT Jitter Transfer

JITTER FREQUENCY, Hz

## Frequency Range

In the non-attenuating mode, that is, when the FIFO is within one UI of overrunning or under running, the tracking range is 1.48 to 1.608 MHz. The guaranteed linear operating range for the jittered input clock is 1.544 MHz  $\pm$  200 Hz with worst case jitter (29 Ulpp) and maximum system clock frequency offset ( $\pm$  100 ppm). The nominal range is 1.544 MHz  $\pm$  963 Hz with no jitter or system clock frequency offset.

#### **Jitter Characteristics**

The DJAT Block provides excellent jitter tolerance and jitter attenuation while generating minimal residual jitter. It can accomodate up to 28 Ulpp of jitter at jitter frequencies above 6 Hz. For jitter frequencies below 6 Hz, more correctly called wander, tolerance increases 20 dB per decade. In most applications the DJAT Block will limit jitter tolerance at lower jitter frequencies only. For high frequency jitter, above 10 kHz for example, other factors such as clock and data recovery circuitry may limit jitter tolerance and must be considered. For low frequency wander, below 10 Hz for example, other factors such as slip buffer hysteresis may limit wander tolerance and must be considered. The DJAT Block meets the stringent low frequency jitter tolerance requirements of AT&T TR 62411 and thus allows one to comply with this standard and the other less stringent jitter tolerance standards cited in the references.

**DUAL DSX-1 LINE INTERFACE**

The DJAT Block exibits negligible jitter gain for jitter frequencies below 6.6 Hz, and attenuates jitter at frequencies above 6.6 Hz by 20 dB per decade. In most applications the DJAT Block will determine jitter attenuation for higher jitter frequencies only. Wander, below 10 Hz for example, will essentially be passed unattenuated through DJAT. Jitter, above 10 Hz for example, will be attenuated as specified, however, outgoing jitter will be dominated by the generated residual jitter of 0.042 Ulpp in cases where incoming jitter is insignicant. This generated residual jitter is directly related to the use of 24X (37.056 MHz) digital phase locked loop for transmit clock generation. The frequency of this generated residual jitter will be below 8 kHz. The DJAT Block meets the jitter attenuation requirements of AT&T TR 62411 and also meets the requirements of AT&T PUB 43802. The DJAT Block allows one to meet the implied jitter attenuation requirements for a TE or NT1 given in ANSI Draft Standard T1E1.2/88-079R8, and the implied jitter attenuation requirements for a type II customer interface given in ANSI T1.403.

## **Inband Code Transmitter**

The Inband Code Transmitter (XIBC) Block generates inband loopback code sequences for insertion into the PCM data stream. These codes consist of continuous repetitions of specific bit sequences. Inband loopback codes are specified in ANSI T1.403, Bellcore TR-TSY-000312, and TR-TSY-000303.

The XIBC supports repetitive transmission of any arbitrary code from three to eight bits in length on the inband code output by programming a control register to set the sequence length and transmit enable output. This programming is done over the Common Bus Interface by an external controller.

## Transmit Pulse Generator

The Transmit Pulse Generator (XPLS) Block converts Non-Return-to-Zero (NRZ) pulses into Alternate Mark Inversion (AMI) line signals suitable for use in the DSX-1 intra-office environment. The dual-rail NRZ pulses are supplied by the DJAT Block. A logic 1 at the Transmit Positive input causes a positive pulse to be transmitted; a similar pulse at the Transmit Negative input causes a negative pulse to be transmitted. If both inputs are logic 0 or 1, no output pulse is transmitted.

The output pulse shape is synthesized digitally with an internal Digital-to-Analog (D/A) converter. The converter is updated at 8 x T1 rate with data stored in a ROM. These words define the output pulse shape. Eight SCLK periods constitute a single output pulse.

AMI signalling is created by exciting either the internal Tip or Ring drivers that drive a line-coupling transformer differentially. This differential driving scheme insures a small positive to negative pulse imbalance. The drivers and the step-up transformer amplify the output pulses to their final levels. The Tip and Ring drivers also supply the high current capability required to drive the low impedance output load.

**DUAL DSX-1 LINE INTERFACE**

The cable length used in the link between the XPLS and the DSX-1 cross-connect greatly affects the resulting pulse shapes. This is compensated for by selecting from one of eight different pulse output shapes built into XPLS. Setting the SM bit in the XPLS Configuration Register selects between the LS bus or ILS bits.

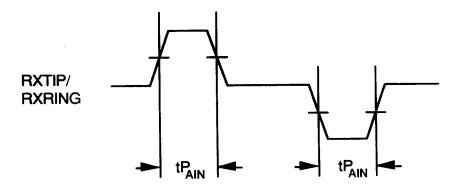

The XPLS includes a driver performance monitor to detect nonfunctional links. Two inputs, PMTIP and PMRING, can be connected to either the XPLS's own outputs or an adjacent link's outputs. If no pulses are detected alternately across inputs PMTIP or PMRING for 63 consecutive TCLK periods, the monitored link is considered failed, until the first correct pulse is received on the monitor inputs.

The XPLS provides outputs that are sliced versions of the analog signal presented to the performance monitor input pins. The DDSX can be programmed to loopback its own analog outputs by writing to the loopback control register, and by connecting PMTIP and PMRING to outputs TXTIP and TXRING, respectively. The PMTIP and PMRING inputs have a nominal slicing level of 2.3 Volts.

The XPLS Block provides Alarm Indication Signalling (AIS) generation capability. XPLS generates alternating mark signals on the link when the TAIS pin is held high, or when programmed via the Common Bus Interface.

The XPLS Block meets the requirements for transmitting a DSX-1 compatible signal as defined in ANSI T1.102 and the other cited references.

**DUAL DSX-1 LINE INTERFACE**

# Fig. 7 External Analog Transmit Interface Circuit

#### **Clock Generator**

## Fig. 8 Typical External Crystal Oscillator Circuit

Figure 7 shows a typical circuit using an external 18.528 MHz crystal for timing generation. Typically, R1 has a value of 1 M $\Omega$  or greater. The values of the two capacitors are dependent upon the specified load capacitance of the crystal. Typically, C1 and C2 each have a value of 10 pF. Both transceivers in DDSX share the same timing source. Alternatively, the DDSX may be driven by a 37.056 MHz clock source connected to XCLK/VCLK. XTAL should be left unconnected, and the internal frequency doubler should be disabled by connecting pin DBLEN to ground.

## **Alarms and Diagnostics**

The Alarms and Diagnostics Block controls the propagation of interrupts generated by the other blocks in the DDSX to the INTB pin. Interrupts can be masked and their current state can be read via accesses through the microprocessor interface.

The three loopback modes in the DDSX are controlled by the Alarm and Diagnostics Block. In the first mode, received data, after clock and data recovery, is retransmitted with jitter attenuated. The two remaining modes loop transmit data back towards the receive side. The loopback data is taken from the output of DJAT in mode two, and from the performance monitor outputs of XPLS in mode three.

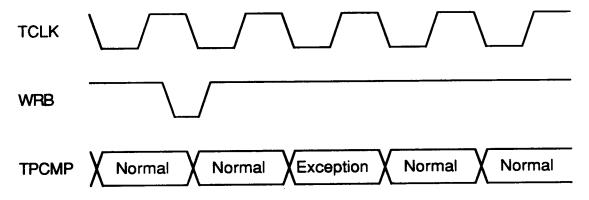

When the DDSX transmitter is in single rail mode, setting the TPCMN/TEXP pin causes a transmission exception. The effect of the exception is controlled by the TBE and TRP bits in the Transmit Control Register. If TBE is set to logic 1, a bit error is generated. If the current bit is a mark, and TRP is set to logic 1, the bit is

**DUAL DSX-1 LINE INTERFACE**

transmitted with reversed polarity. If the bit is a space, the next available mark bit is transmitted with reversed polarity. If both bits are set to logic 1, TRE is applied first, followed by TBV. The table below shows the effects of the TBE and TRP bits for TPCMP being mark and space.

| TPCMP | TRP | TBE | Effects                                                                       |  |

|-------|-----|-----|-------------------------------------------------------------------------------|--|

| Space | 0   | 0   | Bit unchanged                                                                 |  |

| Space | 0   | 1   | Current bit changed to mark                                                   |  |

| Space | 1   | 0   | Next mark bit transmitted with reversed polarity                              |  |

| Space | 1   | 1   | Current bit changed to mark and transmitted with reversed polarity            |  |

| Mark  | 0   | 0   | Bit unchanged                                                                 |  |

| Mark  | 0   | 1   | Current bit changed to space                                                  |  |

| Mark  | 1   | 0   | Current bit transmitted with reversed polarity                                |  |

| Mark  | 1   | 1   | Current bit changed to space Next Mark bit transmitted with reversed polarity |  |

A transmission exception can be triggered in software by setting the TEXP bit in the Transmit Control Register. For each access, the DDSX behaves as though the TEXP pin is set to logic 1 for the bit period after next (See fig. 9). In B8ZS mode, a transmit exception with TRP set will reverse the polarity of one of the pulses in the B8ZS signature.

Fig. 9 Software Induced TEXP Timing

## Microprocessor Interface

The Microprocessor Interface Block provides the logic required to interface the normal mode and test mode registers within the DDSX to a generic microprocessor bus. The normal mode registers are used during normal operation to configure and

**DUAL DSX-1 LINE INTERFACE**

monitor the DDSX while the test mode registers are used to enhance the testability of the DDSX.

## NORMAL MODE REGISTER DESCRIPTION

Normal mode registers are used to configure and monitor the operation of the DDSX. Normal mode registers (as opposed to test mode registers) are selected when TRSB (CBI[13]) is high.

# Notes on Normal Mode Register Bits:

- 1. Writing values into unused register bits has no effect. Reading back unused bits can produce either a logic 1 or a logic 0; hence unused register bits should be masked off by software when read.

- 2. All configuration bits that can be written into can also be read back. This allows the processor controlling the TSB to determine the programming state of the block.

- 3. Writable normal mode register bits are cleared to logic 0 upon reset unless otherwise noted.

- 4. Writing into read-only normal mode register bit locations does not affect TSB operation unless otherwise noted.

# Register Map

| DSX-1   | DSX-2   | REGISTER DESCRIPTION                  |

|---------|---------|---------------------------------------|

| 00H     | 20H     | MASTER CONFIGURATION                  |

| 01H     | 21H     | MASTER INTERRUPT ENABLE               |

| 02H     | 22H     | MASTER INTERRUPT STATUS               |

| 03H     | 23H     | MASTER RESET AND IDENTITY             |

| 04H     | 24H     | TRANSMIT CONTROL                      |

| 05H     | 25H     | Reserved for test                     |

| 06H     | 26H     | LINE CODE VIOLATION COUNT (LSB)       |

| 07H     | 27H     | LINE CODE VIOLATION COUNT (MSB)       |

| 08H     | 28H     | CDRC CONFIGURATION                    |

| 09H     | 29H     | CDRC INTERRUPT ENABLE/STATUS          |

| 0AH     | 2AH     | CDRC STATUS                           |

| 0BH     | 2BH     | Reserved for test                     |

| 0CH     | 2CH     | DJAT INTERRUPT STATUS                 |

| ODH     | 2DH     | DJAT REFERENCE CLOCK DIVISOR (N1)     |

| 0EH     | 2EH     | DJAT OUTPUT CLOCK DIVISOR (N2)        |

| 0FH     | 2FH     | DJAT CONFIGURATION                    |

| 10H     | 30H     | IBCD CONFIGURATION                    |

| 11H     | 31H     | IBCD INTERRUPT ENABLE/STATUS          |

| 12H     | 32H     | IBCD ACTIVATE CODE                    |

| 13H     | 33H     | IBCD DEACTIVATE CODE                  |

| 14H     | 34H     | Reserved for test                     |

| 15H     | 35H     | Reserved for test                     |

| 16H     | 36H     | Reserved for test                     |

| 17H     | 37H     | RSLC INTERRUPT ENABLE/STATUS          |

| 18H     | 38H     | XIBC CONFIGURATION                    |

| 19H     | 39H     | XIBC INBAND CODE                      |

| 1AH-1BH | 3AH-3BH | Reserved for test                     |

| 1CH     | зсн     | XPLS CONFIGURATION                    |

| 1DH     | 3DH     | XPLS CONTROL, INTERRUPT ENABLE/STATUS |