# BIOS and Kernel Developer's Guide for AMD Athlon™ 64 and AMD Opteron™ Processors

Publication # 26094 Revision: 3.06

Issue Date: September 2003

### © 2002, 2003 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

### Trademarks

AMD, the AMD Arrow logo, AMD Athlon, AMD Opteron, and combinations thereof, 3DNow!, and AMD PowerNow! are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Contents**

|       | Revision History                                                                                              | 15 |

|-------|---------------------------------------------------------------------------------------------------------------|----|

| 1     | Introduction and Overview                                                                                     | 17 |

| 1.1   | About This Guide                                                                                              | 17 |

| 1.2   | Related Documents                                                                                             | 18 |

| 1.3   | Conventions and Definitions                                                                                   | 18 |

| 1.3.1 | Notation                                                                                                      | 18 |

| 1.4   | Register Differences in Revisions of the AMD Athlon <sup>TM</sup> 64 and AMD Opteron <sup>TM</sup> processors | 19 |

| 2     | Processor Initialization and Configuration                                                                    | 21 |

| 2.1   | Bootstrap Processor Initialization                                                                            | 21 |

| 2.1.1 | Detecting AP and Initializing Routing Table                                                                   | 21 |

| 2.1.2 | Initializing Noncoherent HyperTransport <sup>TM</sup> Technology Devices                                      | 22 |

| 2.1.3 | Initializing Link Width and Frequency                                                                         | 22 |

| 2.1.4 | Initializing the Memory Controller on All Processor Nodes                                                     | 23 |

| 2.1.5 | Initializing the Address Map Table                                                                            | 23 |

| 2.2   | Application Processor Initialization                                                                          | 23 |

| 2.3   | BIOS Requirement for 64-Bit Operation                                                                         | 24 |

| 2.3.1 | Sizing and Testing Memory above 4 Gbytes                                                                      | 24 |

| 2.3.2 | Using BIOS Callbacks in 64-Bit Mode                                                                           | 24 |

| 3     | Memory System Configuration                                                                                   | 25 |

| 3.1   | Configuration Space Accesses                                                                                  | 25 |

| 3.1.1 | Configuration Address Register                                                                                | 25 |

| 3.1.2 | Configuration Data Register                                                                                   | 26 |

| 3.2   | Memory System Configuration Registers                                                                         | 27 |

| 3.3   | Function 0—HyperTransport <sup>TM</sup> Technology Configuration                                              | 27 |

| 3.3.1 | Device/Vendor ID Register                                                                                     | 29 |

| 3.3.2 | Status/Command Register                                                                                       | 30 |

| 3.3.3  | Class Code/Revision ID Register                              | 30 |

|--------|--------------------------------------------------------------|----|

| 3.3.4  | Header Type Register                                         |    |

| 3.3.5  | Capabilities Pointer Register                                |    |

| 3.3.6  | Routing Table Node i Registers                               | 32 |

| 3.3.7  | Node ID Register                                             | 34 |

| 3.3.8  | Unit ID Register                                             |    |

| 3.3.9  | HyperTransport <sup>TM</sup> Transaction Control Register    |    |

| 3.3.10 | HyperTransport <sup>TM</sup> Initialization Control Register |    |

| 3.3.11 | LDTi Capabilities Register                                   |    |

| 3.3.12 | LDTi Link Control Registers                                  |    |

| 3.3.13 | LDTi Frequency/Revision Registers                            |    |

| 3.3.14 | LDTi Feature Capability Registers                            |    |

| 3.3.15 | LDTi Buffer Count Registers                                  |    |

| 3.3.16 | LDTi Bus Number Registers                                    |    |

| 3.3.17 | LDTi Type Registers                                          |    |

| 3.4    | Function 1—Address Map                                       |    |

| 3.4.1  | Device/Vendor ID Register                                    |    |

| 3.4.2  | Class Code/Revision ID Register                              |    |

| 3.4.3  | Header Type Register                                         |    |

| 3.4.4  | DRAM Address Map                                             |    |

| 3.4.5  | Memory-Mapped I/O Address Map Registers                      | 59 |

| 3.4.6  | PCI I/O Address Map Registers                                | 62 |

| 3.4.7  | Configuration Map Registers                                  | 64 |

| 3.5    | Function 2—DRAM Controller                                   |    |

| 3.5.1  | Device/Vendor ID Register                                    | 67 |

| 3.5.2  | Class Code/Revision ID Register                              | 68 |

| 3.5.3  | Header Type Register                                         | 69 |

| 3.5.4  | DRAM CS Base Address Registers                               | 69 |

| 3.5.5  | DRAM CS Mask Registers                                       | 72 |

| 3.5.6  | DRAM Bank Address Mapping Register                           | 73 |

| 3.5.7  | DRAM Timing Low Register                                             |     |

|--------|----------------------------------------------------------------------|-----|

| 3.5.8  | DRAM Timing High Register                                            |     |

| 3.5.9  | DRAM Configuration Registers                                         |     |

| 3.5.10 | DRAM Delay Line Register                                             |     |

| 3.6    | Function 3—Miscellaneous Control                                     |     |

| 3.6.1  | Device/Vendor ID Register                                            |     |

| 3.6.2  | Class Code/Revision ID Register                                      |     |

| 3.6.3  | Header Type Register                                                 |     |

| 3.6.4  | Machine Check Architecture (MCA) Registers                           |     |

| 3.6.5  | ECC and Chip Kill Error Checking and Correction                      | 108 |

| 3.6.6  | Scrub Control Register                                               |     |

| 3.6.7  | DRAM Scrub Address Registers                                         |     |

| 3.6.8  | XBAR Flow Control Buffers                                            |     |

| 3.6.9  | XBAR-to-SRI Buffer Count Register                                    |     |

| 3.6.10 | Display Refresh Flow Control Buffers                                 |     |

| 3.6.11 | Power Management Control Registers                                   | 120 |

| 3.6.12 | GART Aperture Control Register                                       | 122 |

| 3.6.13 | GART Aperture Base Register                                          |     |

| 3.6.14 | GART Table Base Register                                             | 124 |

| 3.6.15 | GART Cache Control Register                                          | 125 |

| 3.6.16 | Clock Power/Timing Low Register                                      | 125 |

| 3.6.17 | Clock Power/Timing High Register                                     |     |

| 3.6.18 | HyperTransport <sup>TM</sup> FIFO Read Pointer Optimization Register | 128 |

| 3.6.19 | Thermtrip Status Register                                            | 129 |

| 3.6.20 | Northbridge Capabilities Register                                    |     |

| 4      | DRAM Configuration                                                   | 133 |

| 4.1    | Programming Interface                                                |     |

| 4.1.1  | SPD ROM-Based Configuration                                          |     |

| 4.1.2  | Non-SPD ROM-Based Configuration                                      |     |

| 4.1.3  | DRAM Initialization                                                  | 139 |

|        |                                                                      |     |

| 4.2   | DRAM Configuration                                   |     |

|-------|------------------------------------------------------|-----|

| 5     | Machine Check Architecture                           |     |

| 5.1   | Determining Machine Check Support                    | 143 |

| 5.2   | Machine Check Errors                                 | 143 |

| 5.2.1 | Sources of Machine Check Errors                      |     |

| 5.3   | Machine Check Architecture Registers                 |     |

| 5.3.1 | Global Machine Check Model-Specific Registers (MSRs) |     |

| 5.3.2 | Error Reporting Bank Machine Check MSRs              | 149 |

| 5.4   | Error Reporting Banks                                |     |

| 5.4.1 | Data Cache (DC)                                      |     |

| 5.4.2 | Instruction Cache (IC)                               |     |

| 5.4.3 | Bus Unit (BU)                                        |     |

| 5.4.4 | Load Store Unit (LS)                                 |     |

| 5.4.5 | Northbridge (NB)                                     |     |

| 5.5   | Initializing the Machine Check Mechanism             |     |

| 5.6   | Using Machine Check Features                         |     |

| 5.6.1 | Handling Machine Check Exceptions                    | 164 |

| 6     | System Management Mode (SMM)                         |     |

| 6.1   | SMM Overview                                         |     |

| 6.2   | Operating Mode and Default Register Values           |     |

| 6.3   | SMM State Save Definition                            | 169 |

| 6.4   | SMM Initial State                                    |     |

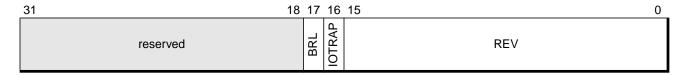

| 6.5   | SMM-Revision Identifier                              |     |

| 6.6   | SMM Base Address                                     |     |

| 6.7   | Auto Halt Restart                                    |     |

| 6.8   | SMM I/O Trap and I/O Restart                         |     |

| 6.8.1 | SMM I/O Trap                                         |     |

| 6.8.2 | SMM I/O Restart Byte                                 |     |

| 6.9   | Exceptions and Interrupts in SMM                     | 176 |

| 6.10  | Protected SMM and ASeg/TSeg                          | 176 |

|       |                                                      |     |

6 Contents

# BIOS and Kernel Developer's Guide for the AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> Processors

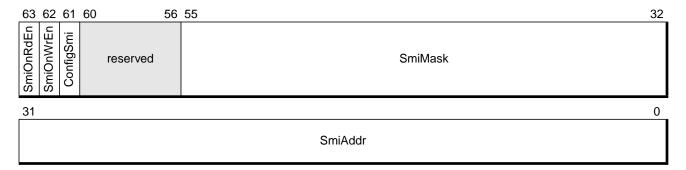

| 6.10.1 | SMM_MASK Register                                                           |     |

|--------|-----------------------------------------------------------------------------|-----|

| 6.10.2 | SMM_ADDR Register                                                           | 178 |

| 6.10.3 | SMM ASeg                                                                    | 178 |

| 6.10.4 | SMM TSeg                                                                    |     |

| 6.10.5 | Closing SMM                                                                 | 180 |

| 6.10.6 | Locking SMM                                                                 | 180 |

| 6.11   | SMM Special Cycles                                                          | 180 |

| 7      | $ Advanced\ Programmable\ Interrupt\ Controller\ (APIC)\ \dots \dots \dots$ | 181 |

| 7.1    | Interrupt Delivery                                                          | 182 |

| 7.2    | Vectored Interrupt Handling                                                 | 182 |

| 7.3    | Spurious Interrupts                                                         | 183 |

| 7.3.1  | Spurious Interrupts Caused by Timer Tick Interrupt                          | 183 |

| 7.4    | Lowest-Priority Arbitration                                                 | 184 |

| 7.5    | Inter-Processor Interrupts                                                  | 185 |

| 7.6    | APIC Timer Operation                                                        | 185 |

| 7.7    | State at Reset                                                              | 185 |

| 7.8    | Register Summary                                                            | 186 |

| 7.8.1  | APIC ID Register                                                            | 187 |

| 7.8.2  | APIC Version Register                                                       | 187 |

| 7.8.3  | Task Priority Register                                                      | 188 |

| 7.8.4  | Arbitration Priority Register                                               | 188 |

| 7.8.5  | Processor Priority Register                                                 | 188 |

| 7.8.6  | End of Interrupt Register                                                   | 189 |

| 7.8.7  | Logical Destination Register                                                | 189 |

| 7.8.8  | Destination Format Register                                                 | 190 |

| 7.8.9  | Spurious Interrupt Vector Register                                          | 190 |

| 7.8.10 | In-Service Registers                                                        | 191 |

| 7.8.11 | Trigger Mode Registers                                                      | 192 |

| 7.8.12 | Interrupt Request Registers                                                 | 193 |

| 7.8.13 | Error Status Register                                                       | 194 |

|        |                                                                             |     |

| 7.8.14 | Interrupt Command Register Low                                                                                                                                                                                                            | 195 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.8.15 | Interrupt Command Register High                                                                                                                                                                                                           | 196 |

| 7.8.16 | Timer Local Vector Table Entry                                                                                                                                                                                                            | 197 |

| 7.8.17 | Performance Counter Local Vector Table Entry                                                                                                                                                                                              | 197 |

| 7.8.18 | Local Interrupt 0 (Legacy INTR) Local Vector Table Entry Register                                                                                                                                                                         | 198 |

| 7.8.19 | Local Interrupt 1 (Legacy NMI) Local Vector Table Entry                                                                                                                                                                                   | 199 |

| 7.8.20 | Error Local Vector Table Entry                                                                                                                                                                                                            | 199 |

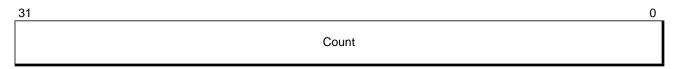

| 7.8.21 | Timer Initial Count Register                                                                                                                                                                                                              | 200 |

| 7.8.22 | Timer Current Count Register                                                                                                                                                                                                              | 200 |

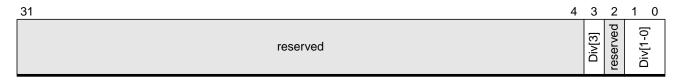

| 7.8.23 | Timer Divide Configuration Register                                                                                                                                                                                                       | 201 |

| 8      | $\textbf{HyperTransport}^{\text{TM}} \ \textbf{Technology} \ \textbf{Configuration} \ \textbf{and} \ \textbf{Enumeration} \ \dots $ | 203 |

| 8.1    | Initial Configuration Steps                                                                                                                                                                                                               | 203 |

| 8.2    | One-Node Coherent HyperTransport <sup>TM</sup> Technology Initialization                                                                                                                                                                  | 204 |

| 8.3    | Two-Node Coherent HyperTransport <sup>TM</sup> Technology Initialization                                                                                                                                                                  | 204 |

| 8.4    | Generic HyperTransport <sup>TM</sup> Technology Configuration                                                                                                                                                                             | 205 |

| 8.4.1  | Algorithm                                                                                                                                                                                                                                 | 207 |

| 9      | Power and Thermal Management                                                                                                                                                                                                              | 215 |

| 9.1    | Stop Grant                                                                                                                                                                                                                                | 216 |

| 9.2    | C-States                                                                                                                                                                                                                                  | 218 |

| 9.2.1  | C1 Halt State                                                                                                                                                                                                                             | 218 |

| 9.2.2  | C2 and C3                                                                                                                                                                                                                                 | 218 |

| 9.3    | Throttling                                                                                                                                                                                                                                | 218 |

| 9.4    | Processor ACPI Thermal Zone                                                                                                                                                                                                               | 219 |

| 9.5    | Processor Performance States                                                                                                                                                                                                              | 219 |

| 9.5.1  | BIOS Requirements for P-State Transitions                                                                                                                                                                                                 | 219 |

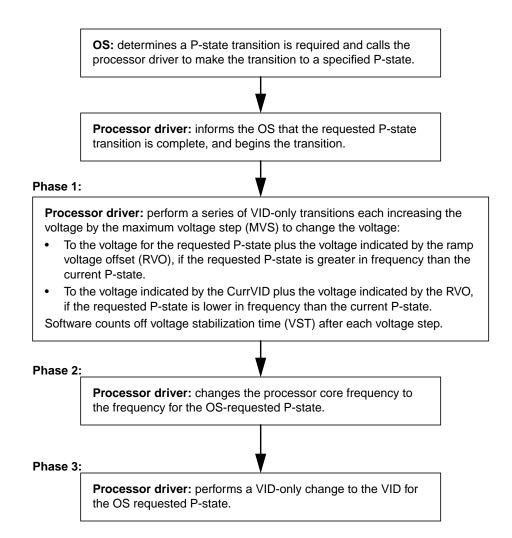

| 9.5.2  | BIOS-Initiated P-State Transitions                                                                                                                                                                                                        | 221 |

| 9.5.3  | BIOS Support for Operating System/CPU Driver-Initiated P-State Transitions                                                                                                                                                                | 221 |

| 9.5.4  | Processor Driver Requirements                                                                                                                                                                                                             | 222 |

| 9.5.5  | P-State Transition Sequence                                                                                                                                                                                                               | 222 |

| 9.6    | ACPI 2.0 Processor P-State Objects                                                                                                                                                                                                        | 230 |

|        |                                                                                                                                                                                                                                           |     |

8 Contents

# BIOS and Kernel Developer's Guide for the AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> Processors

| 9.6.1  | _PCT (Performance Control)                                                            | 230 |

|--------|---------------------------------------------------------------------------------------|-----|

| 9.6.2  | _PSS (Performance-Supported States)                                                   | 231 |

| 9.6.3  | _PPC (Performance Present Capabilities)                                               | 237 |

| 9.6.4  | PSTATE_CNT                                                                            | 239 |

| 9.6.5  | CST_CNT                                                                               | 239 |

| 9.7    | BIOS Support for AMD PowerNow! <sup>TM</sup> Software with Legacy Operating Systems . | 239 |

| 9.8    | System Configuration for Power Management                                             | 241 |

| 9.8.1  | Chipset Configuration for Power Management                                            | 241 |

| 9.8.2  | Processor Configuration for Power Management                                          | 241 |

| 10     | Performance Monitoring                                                                | 245 |

| 10.1   | Performance Counters                                                                  | 245 |

| 10.2   | Performance Event-Select Registers                                                    | 246 |

| 11     | BIOS Checklist                                                                        | 255 |

| 11.1   | CPUID                                                                                 | 255 |

| 11.2   | CPU Speed Detection                                                                   | 255 |

| 11.3   | HyperTransport <sup>TM</sup> Link Frequency Selection                                 | 255 |

| 11.4   | Multiprocessing Capability Detection                                                  | 256 |

| 11.5   | Model-Specific Registers (MSRs)                                                       | 256 |

| 11.6   | Machine Check Architecture (MCA)                                                      | 257 |

| 11.7   | Memory Map                                                                            | 257 |

| 11.7.1 | I/O and Memory Type and Range Registers (IORRs, MTRRs)                                | 257 |

| 11.7.2 | Memory Map Registers (MMRs)                                                           | 258 |

| 11.8   | Cache Testing and Programming                                                         | 258 |

| 11.9   | Memory System Configuration Registers                                                 | 258 |

| 11.10  | XSDT Table                                                                            | 259 |

| 11.11  | Detect Target Operating Mode Callback                                                 | 259 |

| 11.12  | SMM Issues                                                                            | 260 |

| 12     | Processor Configuration Registers                                                     | 261 |

| 12.1   | General Model-Specific Registers                                                      | 261 |

| 12.1.1 | System Software Registers                                                             | 263 |

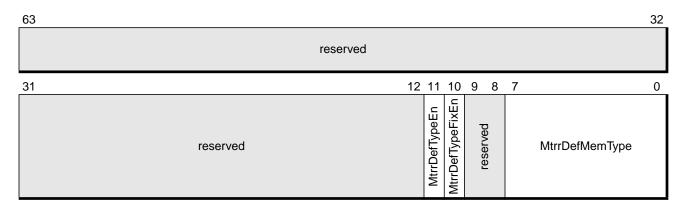

| 12.1.2 | Memory Typing Registers                                                                                | 265 |

|--------|--------------------------------------------------------------------------------------------------------|-----|

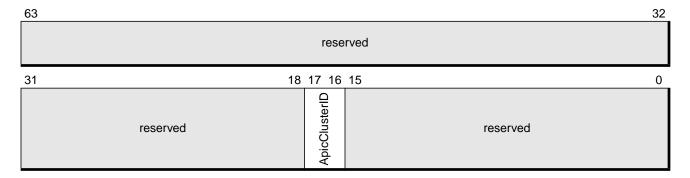

| 12.1.3 | APIC Registers                                                                                         | 282 |

| 12.1.4 | Software Debug Registers                                                                               | 283 |

| 12.1.5 | Performance Monitoring Registers                                                                       | 284 |

| 12.2   | AMD Athlon <sup>TM</sup> 64 processor and AMD Opteron <sup>TM</sup> Processor Model-Specific Registers | 284 |

| 12.2.1 | Feature Registers                                                                                      | 286 |

| 12.2.2 | Identification Registers                                                                               | 292 |

| 12.2.3 | Memory Typing Registers                                                                                | 292 |

| 12.2.4 | I/O Range Registers                                                                                    | 293 |

| 12.2.5 | System Call Extension Registers                                                                        | 295 |

| 12.2.6 | Segmentation Registers                                                                                 | 297 |

| 12.2.7 | Power Management Registers                                                                             | 299 |

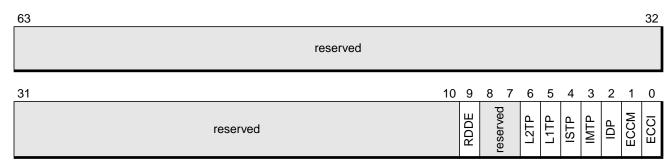

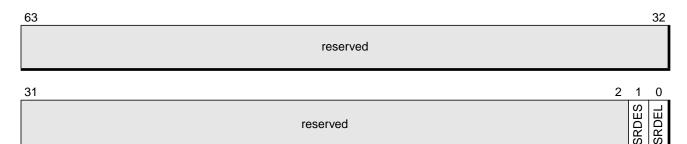

| 12.2.8 | IO and Configuration Space Trapping to SMI                                                             | 302 |

| G      | Glossary                                                                                               | 307 |

| I      | ndex of Register Names                                                                                 | 313 |

10 Contents

# **List of Figures**

| Figure 1. | Interleave Example (IntlvEn Relation to IntlvSel) | 59 |

|-----------|---------------------------------------------------|----|

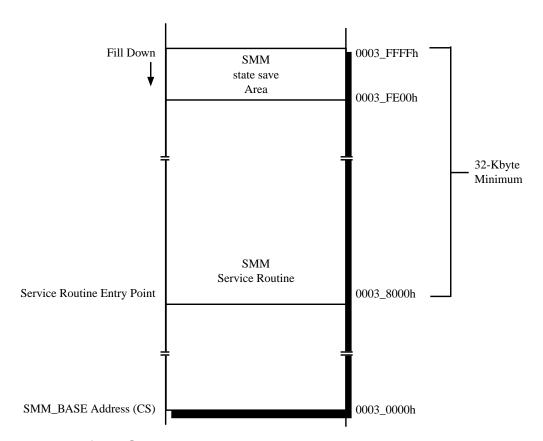

| Figure 2. | Default SMM Memory Map                            |    |

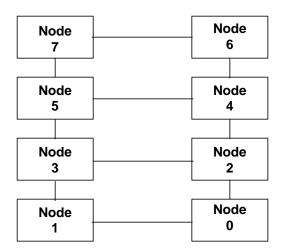

| Figure 3. | An Eight-Node Configuration                       |    |

| Figure 4. | High-Level P-state Transition Flow                |    |

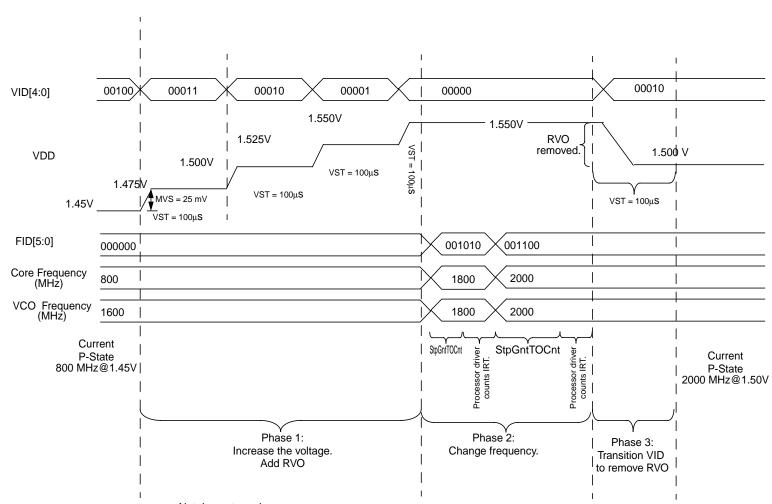

| Figure 5. | Example P-State Transition Timing Diagram         |    |

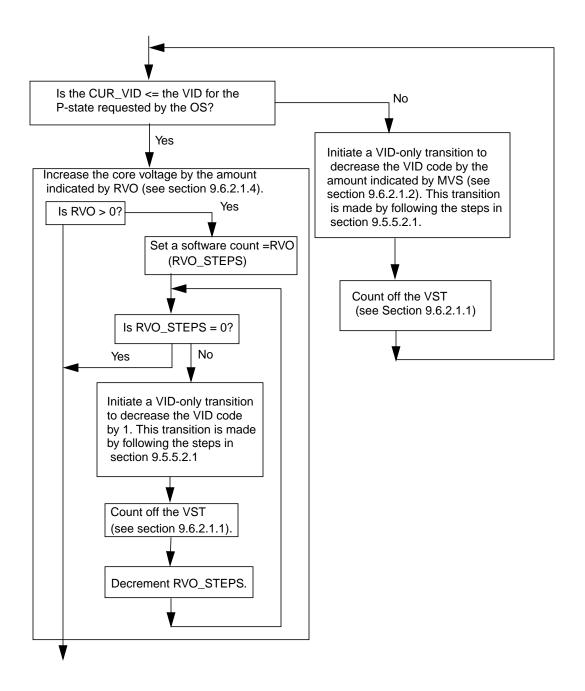

| Figure 6. | Phase 1: Core Voltage Transition Flow             |    |

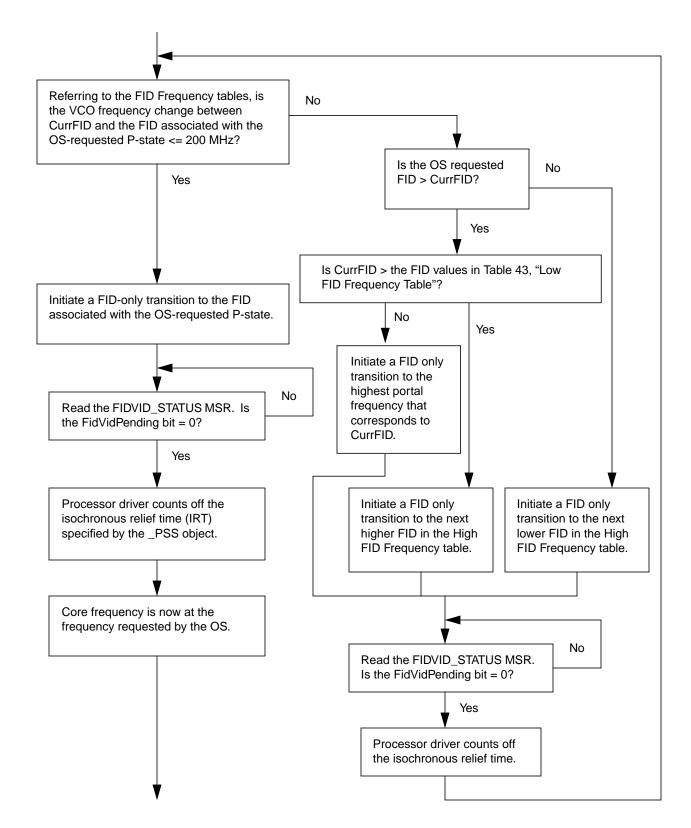

| Figure 7. | <u> </u>                                          |    |

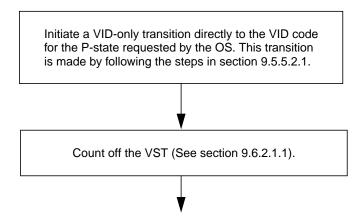

| Figure 8. | Phase 3: Core Voltage Transition Flow             |    |

BIOS and Kernel Developer's Guide for the AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> Processors

26094 Rev. 3.06 September 2003

# **List of Tables**

| Table 1.  | Related Documents                                                      | 18  |

|-----------|------------------------------------------------------------------------|-----|

| Table 2.  | Function 0 Configuration Registers                                     | 27  |

| Table 3.  | Function 1 Configuration Registers                                     | 53  |

| Table 4.  | Function 2 Configuration Registers                                     | 66  |

| Table 5.  | DRAM CS Base Address and DRAM CS Mask Registers                        | 70  |

| Table 6.  | Mapping Host Address Lines to Memory Address Lines (64-Bit Interface)  | 74  |

| Table 7.  | Mapping Host Address Lines to Memory Address Lines (128-Bit Interface) | 75  |

| Table 8.  | Swapped physical address lines for interleaving with 64-bit interface  |     |

| Table 9.  | Swapped physical address lines for interleaving with 128-bit interface | 77  |

| Table 10. | Function 3 Configuration Registers                                     | 89  |

| Table 11. | Error Code Field Formats                                               | 99  |

| Table 12. | Transaction Type Bits (TT)                                             | 99  |

| Table 13. | Cache Level Bits (LL)                                                  | 99  |

| Table 14. | Memory Transaction Type Bits (RRRR)                                    | 99  |

| Table 15. | Participation Processor Bits (PP)                                      | 100 |

| Table 16. | Time-Out Bit (T)                                                       | 100 |

| Table 17. | Memory or I/O Bits (II)                                                | 100 |

| Table 18. | Northbridge Error Codes                                                | 100 |

| Table 19. | Northbridge Error Status Bit Settings                                  |     |

| Table 20. | ECC Syndromes                                                          | 108 |

| Table 21. | Chip Kill ECC Syndromes                                                | 109 |

| Table 22. | Scrub Rate Control Values                                              | 111 |

| Table 23. | XBAR Input Buffers                                                     | 113 |

| Table 24. | Default XBAR Command Buffer Allocation                                 | 114 |

| Table 25. | Default Virtual Channel Command Buffer Allocation                      | 114 |

| Table 26. | An Example of a Non Default Virtual Channel Command Buffer Allocation  | 115 |

| Table 27. | GART PTE Organization                                                  | 124 |

| Table 28. | Trwt Values                                                            | 137 |

| Table 29. | RdPreamble Values                                                      | 138 |

| Table 30. | Sources of Machine Check Errors                                        | 145 |

| Table 31. | Valid MC0_ADDR Bits                                                    | 156 |

| Table 32. | Valid MC1_ADDR Bits                                                    | 158 |

| Table 33. | Valid MC2_ADDR Bits                                                    | 161 |

| Table 34. | SMM Save State (Offset FE00–FFFFh)                                     | 169 |

| Table 35. | SMM Entry State                                                        | 172 |

| Table 36. | SMM ASeg-Enabled Memory Types                                          | 179 |

| Table 37. | SMM TSeg-Enabled Memory Types                                          | 179 |

| Table 38. | APIC Register Summary                                                  |     |

| Table 39. | Valid Combinations of ICR Fields                                       | 196 |

| Table 40. | Power Management Categories                                            | 215 |

| Table 41. | ACPI-State Support by System Class                                                 | 216 |

|-----------|------------------------------------------------------------------------------------|-----|

| Table 42. | Required SMAF Code to Stop Grant Mapping                                           |     |

| Table 43. | Low FID Frequency Table (< 1600 MHz)                                               |     |

| Table 44. | High FID Frequency Table (>= 1600 MHz)                                             |     |

| Table 45. | Sample VST Values                                                                  | 233 |

| Table 46. | MVS Values                                                                         |     |

| Table 47. | RVO Values                                                                         | 235 |

| Table 48. | VID Code Voltages                                                                  | 235 |

| Table 49. | IRT Values                                                                         |     |

| Table 50. | _PSS Status Field                                                                  | 237 |

| Table 51. | Performance State Block Structure                                                  | 240 |

| Table 52. | Configuration Register Settings for Power Management                               | 242 |

| Table 53. | FADT Table Entries                                                                 | 243 |

| Table 54. | Processor Functional Unit Encoding                                                 | 248 |

| Table 55. | Performance Monitor Events                                                         | 248 |

| Table 56. | General MSRs                                                                       | 261 |

| Table 57. | AMD Athlon <sup>TM</sup> 64 Processor and AMD Opteron <sup>TM</sup> Processor MSRs | 285 |

| Table 58. | FID Code Translations                                                              | 300 |

# **Revision History**

| Date           | Rev. | Description                                                                                                                                             |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| September 2003 | 3.06 | Clarified 32ByteEn (Function 2, Offset 90h) programming in "DRAM Configuration" section.                                                                |

|                |      | Removed SleepVIDCnt (Function 3, Offset D4h) and added a programming requirement.                                                                       |

|                |      | Added reference to the <i>AMD Athlon</i> <sup>TM</sup> 64 <i>Data Sheet</i> , order# 24659 for 3 DIMM configuration to "Programming Interface" section. |

|                |      | Corrected requirement for supported DIMMs in "Registered or Unbuffered DIMMs" section.                                                                  |

|                |      | Corrected RdPreamble values for 3 DIMM configuration in "Read Preamble Time" section.                                                                   |

|                |      | Added RdPreamble and Trwt values for registered DDR400.                                                                                                 |

|                |      | Added EnRefUseFreeBuf and DisCohLdtCfg to NB_CFG register (MSR C001_001Fh).                                                                             |

|                |      | Cleanup related to AMD Athlon™ 64 and AMD Opteron™ use.                                                                                                 |

| July 2003      | 3.04 | Added examples to "DRAM Address Mapping in Interleaving Mode" and "DRAM Address Mapping in Non-Interleaving Mode" sections.                             |

|                |      | Added recommendation for setting "HyperTransport™ FIFO Read Pointer Optimization Register".                                                             |

|                |      | Added "Spurious Interrupts Caused by Timer Tick Interrupt" section.                                                                                     |

|                |      | Added "XSDT Table" section.                                                                                                                             |

|                |      | Added "Detect Target Operating Mode Callback" section.                                                                                                  |

|                |      | Modified "Multiprocessing Capability Detection" section.                                                                                                |

|                |      | Added requirements for AMD Cool'n'Quiet <sup>™</sup> technology and BIOS P-state transitions to "Power and Thermal Management" chapter.                 |

|                |      | Added ClkRampHyst (Function 3, Offset D4h) setting to "Power and Thermal Management" chapter.                                                           |

|                |      | General cleanup in "Power and Thermal Management" chapter.                                                                                              |

|                |      | Added "Twtr (Write to Read Delay)" section.                                                                                                             |

|                |      | Added a requirement to "GART Aperture Base Register".                                                                                                   |

|                |      | Added a requirement for GartEn (Function 3, Offset 90h) programming.                                                                                    |

|                |      | Removed recommandation for extended range temperature sensors in DiodeOffset (Function 3, Offset E4h) definition.                                       |

|                |      | Added a requirement for extended configuration space access to "Memory-Mapped I/O Address Map Registers" section.                                       |

| Date       | Rev. | Description                                                                                                                              |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| May 2003   | 3.02 | Added "ECC and Chip Kill Error Checking and Correction" section.                                                                         |

|            |      | Clarified "Scrub Control Register" and "DRAM Scrub Address Registers" sections.                                                          |

|            |      | Clarified LinkFail (Function 0, Offsets 84h, A4h, C4h).                                                                                  |

|            |      | Clarified node interleaving in "DRAM Address Map" section.                                                                               |

|            |      | Clarified and corrected DRAM address interleaving in "DRAM CS Base Address Registers" and "DRAM Bank Address Mapping Register" sections. |

|            |      | Clarified "tCL (CAS Latency)" section.                                                                                                   |

|            |      | Added "piggyback scrubbing" description to "Sources of Machine Check Errors" section.                                                    |

|            |      | Clarified Table 30, "Sources of Machine Check Errors," on page 145.                                                                      |

|            |      | Clarified MCA NB PCI configuration register to MCA MSR mapping in "Northbridge (NB)" section.                                            |

|            |      | Corrected MaxLVTEntry (APIC_VER Register, Offset 30h) default value.                                                                     |

|            |      | General cleanup in "Power and Thermal Management" chapter.                                                                               |

|            |      | Added "HyperTransport™ Link Frequency Selection" section.                                                                                |

| April 2003 | 3.00 | Initial Public release.                                                                                                                  |

# 1 Introduction and Overview

The BIOS and Kernel Developer's Guide for the AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> Processors is intended for programmers involved in the development of low-level BIOS (basic input/output system) functions, drivers, and operating system kernel modules. It assumes previous experience in microprocessor programming, as well as fundamental knowledge of legacy x86 and AMD64 microprocessor architecture. The reader should also have previous experience in BIOS or OS kernel design issues, as related to microprocessor systems, and a familiarity with various platform technologies, such as DDR, HyperTransport<sup>TM</sup> technology, and JTAG.

### 1.1 About This Guide

This guide covers the *implementation-specific* features of AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> processors, as opposed to architectural features. AMD64 architectural features include the AMD64 technology, general-purpose, multimedia, and x87 floating-point registers, as well as other programmer-visible features defined to be constant across all processors. A subset of implementation-specific features are not defined by the processor architectural specifications. These implementation-specific features may differ in various details from one implementation to the next.

*Note:* The term processor in this document refers to AMD Athlon<sup>TM</sup> 64 processor architecture and AMD Opteron<sup>TM</sup> processor architecture. This document covers both classes of devices. For details about differences between them, see the AMD Athlon<sup>TM</sup> 64 Processor Data Sheet, order# 24659 and the AMD Opteron<sup>TM</sup> Processor Data Sheet, order# 23932.

The implementation-specific features covered in the following chapters include:

- Model-specific registers

- Processor initialization

- Integrated memory system configuration

- HyperTransport technology fabric initialization

- Performance monitoring and special debug features

- DRAM configuration

- Machine check error codes

- Thermal and power management

### 1.2 Related Documents

The references listed in Table 1 may prove invaluable towards a complete understanding of the subject matter in this volume.

Table 1. Related Documents

| Title                                                                                              | Order#                        |

|----------------------------------------------------------------------------------------------------|-------------------------------|

| AMD64 Architecture Programmer's Manual, Volume 1, Application Programming                          | 24592                         |

| AMD64 Architecture Programmer's Manual, Volume 2,<br>System Programming                            | 24593                         |

| AMD64 Architecture Programmer's Manual, Volume 3,<br>General-Purpose and System Instructions       | 24594<br>(three-volume kit)   |

| AMD64 Architecture Programmer's Manual, Volume 4, 128-Bit Media Instructions                       |                               |

| AMD64 Architecture Programmer's Manual, Volume 5, 64-Bit Media and x87 Floating-Point Instructions |                               |

| AMD Opteron <sup>TM</sup> Processor Data Sheet                                                     | 23932                         |

| AMD Athlon <sup>TM</sup> 64 Processor Data Sheet                                                   | 24659                         |

| AMD Processor Recognition Application Note                                                         | 20734                         |

| CPUID Guide for AMD Athlon <sup>TM</sup> 64 and AMD Opteron <sup>TM</sup> Processors               | 25481                         |

| Revision Guide for the AMD Athlon <sup>TM</sup> 64 and AMD Opteron <sup>TM</sup> Processors        | 25759                         |

| HyperTransport™ I/O Link Specification, Rev. 1.03                                                  | http://www.hypertransport.org |

# 1.3 Conventions and Definitions

Some of the following definitions assume a knowledge of the legacy x86 architecture. See Table 1 for documents that include information on the legacy x86 architecture.

Additional definitions are provided in the glossary at the end of this book, beginning on page 307. That glossary includes the most important terminology of the AMD64 architecture.

### 1.3.1 Notation

**1011b.** A binary value. In this example, a 4-bit value is shown.

**F0EAh.** A hexadecimal value. In this example, a 2-byte value is shown.

[1,2]. A range that includes the left-most value (in this case, 1) but excludes the right-most value (in this case, 2).

7–4. A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first.

**#GP(0).** Notation indicating a general-protection exception (#GP) with error code of 0.

- **CR0–CR4.** A register range, from register CR0 through CR4, inclusive, with the low-order register first.

- **CR0.PE** = 1. Notation indicating that the PE bit of the CR0 register has a value of 1.

- **DS:rSI.** The contents of a memory location whose segment is DS and whose byte address is located in the rSI register.

- **EFER.LME** = **0.** Notation indicating that the LME bit of the EFER register has a value of 0.

- **FF** /0. Notation indicating that FF is the first byte of an opcode and a sub-opcode field in the MODRM byte has a value of 0.

# 1.4 Register Differences in Revisions of the AMD Athlon™ 64 and AMD Opteron™ processors

Some changes to the register set are introduced with different silicon revisions. Refer to the *Revision Guide for AMD Athlon*<sup>TM</sup> *64 and AMD Opteron*<sup>TM</sup> *Processors*, order# 25759 for information about how to identify different processor revisions. The following summarizes register changes after the initial revision.

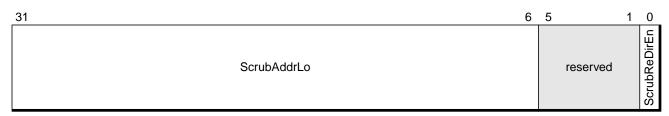

### Revision C.

- MSR C001\_0043h (ThermTrip\_STATUS Register) deleted.

- Function 2, offset 90h, DramEn (bit 10), MemClrStatus (bit 11) added.

- Function 2, offset CCh, DisTscCapture (bit 30) added.

- Function 3, offset 70h, DispRefReq (bits 21-20) added.

- Function 3, offset 74h, DispRefReq (bits 22-20) added.

- MSR C001 001Fh (NB CFG register), DisDatMsk (bit 36), EnRefUseFreeBuf (bit 9) added.

- Function 3, offset 90h, DisGartTblWlkPrb (bit 6) added.

- Function 3, offset D4h, ClkRampHyst (bits 10-8) added.

- MSR C001\_0015 (HWCR register), HLTXSYCEN (bit 12) added.

- MSR C001\_0010 (SYSCFG register), ClVicBlkEn (bit 11) deleted.

- MSRs C001\_0050h, C001\_0051h, C001\_0052h, C001\_0053h (IOTRAP\_ADDRi registers), and MSR C001\_0054h (IOTRAP\_CTL register) added.

BIOS and Kernel Developer's Guide for the AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> Processors

26094 Rev. 3.06 September 2003

# 2 Processor Initialization and Configuration

Each AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> processor based system has one processor with its HyperTransport<sup>TM</sup> link connected to a HyperTransport<sup>TM</sup> I/O hub. When a reset signal is applied, this processor is initialized as the bootstrap processor (BSP). In a multiple processor system, any other processors are initialized as application processors (APs). The BSP begins executing code from the reset vector (0xFFFFFFF0), while each of the APs waits for its Request Disable bit to clear to 0. An AP does not fetch code until its Request Disable bit is cleared. Both BSP and AP operate in 16-bit Real mode after reset. The BSP has the Boot Strap Processor bit set in its APIC\_BASE (001Bh) MSR, and each AP has this bit cleared.

The processor node is addressed by its Node ID on the HyperTransport link and can be accessed with a device number in the PCI configuration space on Bus 0. The Node ID 0 is mapped to Device 24, the Node ID 1 is mapped to Device 25, and so on. The BSP is initialized with Node ID 0 after reset, and all APs are initialized with Node ID 7.

The BSP is ready to access its Northbridge and memory controller after its routing table is enabled. The APs are not accessible from the BSP until the links and the routing table are configured.

The initial processor states are described in the "Processor Initialization State" section of the *AMD64 Architecture Programmer's Manual:* Volume 2, *System Programming*.

# 2.1 Bootstrap Processor Initialization

The BSP is responsible for the execution of the BIOS Power-On Self Test (POST) and initialization of APs. The BSP must perform the following tasks:

- AP detection and routing table initialization

- Noncoherent HyperTransport device initialization

- Link width and frequency initialization

- Memory controller initialization on all processor nodes

- Address map table initialization

### 2.1.1 Detecting AP and Initializing Routing Table

The AMD Opteron<sup>TM</sup> processor has three HyperTransport links; therefore, an AMD Opteron<sup>TM</sup> system can have from one to eight processors. The BSP must detect all APs in the system, starting from its adjacent processor. Since the APs are initialized at Node 7, the BSP must set entry 7 of its Routing Table before the AP can be accessed. The adjacent AP will respond to a PCI configuration

read if it is present. A new Node ID can be assigned to the AP after the routing information is updated in the routing table. Chapter 8, "HyperTransport<sup>TM</sup> Technology Configuration and Enumeration" explains the steps for enumerating and initializing routing tables in one-processor (UP), two-processor (DP), and n processor systems.

The AMD Athlon<sup>TM</sup> 64 processor has one HyperTransport link. Because one link must be connected to the HyperTransport I/O hub, an AMD Athlon<sup>TM</sup> 64 system can only be used in a uniprocessor system.

### 2.1.2 Initializing Noncoherent HyperTransport™ Technology Devices

Once all APs have been detected and the routing tables and link control registers have been initialized, the BSP must initialize noncoherent HyperTransport technology devices.

A noncoherent HyperTransport technology device has either one or two links. A tunnel device has two links and a terminal device has one link. The HyperTransport I/O hub is a typical example of a terminal noncoherent HyperTransport device. The noncoherent HyperTransport device is identified by its Unit ID in a noncoherent HyperTransport link and can be accessed with a device number in the PCI configuration space. The device number in PCI space is the same as the Unit ID assigned to the noncoherent HyperTransport device.

After reset, the Unit ID of each noncoherent HyperTransport technology device is initialized with a value of 0. When a PCI configuration read is performed from the BSP through a noncoherent HyperTransport link, the noncoherent HyperTransport device connected to the port responds. A new non-zero Unit ID value must be assigned to this device. The BIOS continues this process until no device responds at Device 0. The bus number range must be set to the noncoherent HyperTransport link on the BSP and in the address map table prior to the detection. The link control and status registers of a noncoherent device are implemented in the capability register block.

The noncoherent HyperTransport technology devices connected to a port on the AP node can be detected in the same way. Again, the bus number range must be set to the noncoherent HyperTransport link on this AP and in the address map table. The noncoherent device can be detected with the starting bus number, Device 0 on the PCI configuration space.

A noncoherent HyperTransport technology device may use more than one Unit ID. The new ID assigned to a device is its starting ID, the Base Unit ID (BaseUID). The next logic device in this noncoherent HyperTransport device can be identified with BaseUID + 1, and so on. The Unit ID Count field in the Capabilities register indicates how many Unit IDs this device uses.

# 2.1.3 Initializing Link Width and Frequency

The HyperTransport link width and frequency are initialized between the adjacent coherent and/or noncoherent HyperTransport technology devices during the reset sequence. After AP and noncoherent HyperTransport device detection, the link width and frequency can be changed based on the capability of the adjacent devices or the implementation of the system. To make the new link width and frequency take effect, an LDTSTOP\_L needs to be asserted or a warm reset must be

performed. The BIOS must guarantee that LDTSTOP\_L assertion for link width and frequency changes does not occur within 200µs of reset.

### 2.1.4 Initializing the Memory Controller on All Processor Nodes

The BSP is responsible for configuring the memory controller on all processor nodes and for initializing the DRAM map table. Chapter 4, "DRAM Configuration," describes the functionality of the memory controller and the steps required to initialize memory.

After memory configuration, the memory address MSRs must be set accordingly. The Top of Memory MSR is used for the top of DRAM below 4 Gbytes, and TOP\_MEM2 is set to the top of DRAM above 4 Gbytes.

### 2.1.5 Initializing the Address Map Table

Each processor node has an address map table. This table contains the address map for the DRAM area, the address map for PCI memory spaces (MMIO), the address map for PCI I/O spaces, and the bus number range for each noncoherent HyperTransport link. The address map table must be duplicated on all processors in a system.

# 2.2 Application Processor Initialization

The application processor (AP) waits until its request disable bit is cleared to 0. The BIOS may clear this bit for an AP a soon as the AP node detection is completed and the routing tables are initialized, or just before the AP register initialization.

When the request disable bit is cleared, the corresponding AP starts to fetch code from the reset vector (0xFFFFFFF0). The BSP bit in AP APIC\_BASE register is cleared at reset, so it can be used to terminate the AP execution after the initial APIC initialization.

The AP register initialization is the same as that of other AMD x86 processor families, such as the AMD Athlon<sup>TM</sup> processors.

# 2.3 BIOS Requirement for 64-Bit Operation

In general, the BIOS need not be aware of 64-bit mode in POST. There are no additional requirements to support 64-bit mode. The operating system determines whether to enable 64-bit mode after the BIOS invokes the operating system loader in legacy mode. There are two areas that need additional explanation:

- Sizing and testing memory above 4 Gbytes

- Using BIOS callback when in 64-bit mode

### 2.3.1 Sizing and Testing Memory above 4 Gbytes

AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> processors have extended physical address extension (PAE) to support a 40-bit address space. Thus, the BIOS can set up a 32-bit page table that allows it to size and test all physical memory in the system.

### 2.3.2 Using BIOS Callbacks in 64-Bit Mode

A BIOS callback is a mechanism that allows an operating system to call a service routine in the BIOS. BIOS callbacks on an AMD Athlon<sup>TM</sup> 64 processor or an AMD Opteron<sup>TM</sup> processor platform in 64-bit mode are not supported by AMD64 operating systems. An operating system loader must be invoked in legacy mode with paging disabled, so that the loader can use 16/32-bit BIOS callbacks.

ACPI code and operating system drivers are not affected by AMD64 operating systems that do not use a BIOS callback in 64-bit mode. ACPI is coded in ASL, which is not affected by the operating system mode. AMD64 operating system drivers are not allowed to use ROM callbacks.

# 3 Memory System Configuration

# 3.1 Configuration Space Accesses

The AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> processors implement configuration space as defined in the PCI Local Bus Specification, Rev. 2.2, and the HyperTransport<sup>TM</sup> I/O Link Specification, Rev. 1.03.

Both coherent HyperTransport links and the compatibility bus (the bus to the HyperTransport I/O hub) are accessed through Bus 0. Configuration accesses to Bus 0, devices 0 to 23, are transmitted to the compatibility noncoherent HyperTransport bus. Coherent HyperTransport device configuration space is accessed by using Bus 0, devices 24 to 31, where Device 24 corresponds to Node 0 and Device 31 corresponds to Node 7.

All configuration cycles are type 1 on coherent HyperTransport links. When transmitted down a noncoherent HyperTransport chain by the host bridge, configuration cycles are translated to type 0 if they target the noncoherent HyperTransport bus immediately behind the host bridge. If they target a subordinate bus, they remain as type 1.

Accesses to memory system configuration registers are controlled through the Configuration Address register (see "Configuration Address Register" on page 25) and the Configuration Data register (see "Configuration Data Register" on page 26), which can be accessed through I/O reads/writes to addresses 0CF8h and 0CFCh, respectively.

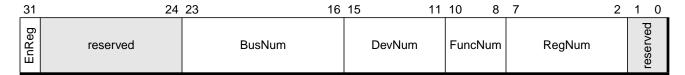

### 3.1.1 Configuration Address Register

Writes to the Configuration Address register specify the target of a configuration access in terms of the bus, device, function, and register. Access to the Configuration Address register must be full doubleword reads or writes.

To access one of the memory system configuration registers defined in this chapter, the bus number should be 0, the device number should be the target processor node number plus 24, and the function and register number should be set based on the register function and offset as specified in this chapter.

When the Enable bit of the Configuration Address register is set, reads and writes to the Configuration Data register access the register specified in the Configuration Address register.

### **Configuration Address Register**

### **0CF8h (doubleword)**

| Bit   | Mnemonic | Function        | R/W |

|-------|----------|-----------------|-----|

| 31    | EnReg    | Enable Register | R/W |

| 30–24 | reserved |                 | R   |

| 23–16 | BusNum   | Bus Number      | R/W |

| 15–11 | DevNum   | Device Number   | R/W |

| 10–8  | FuncNum  | Function Number | R/W |

| 7–2   | RegNum   | Register Number | R/W |

| 1–0   | reserved |                 | R   |

### **Field Descriptions**

**Register Number (RegNum)**—Bits 7–2. Specifies the doubleword offset of the configuration address.

**Function Number (FuncNum)**—Bits 10–8. Specifies the function number of the configuration address.

**Device Number (DevNum)**—Bits 15–11. Specifies the device number of the configuration address.

**Bus Number (BusNum)**—Bits 23–16. Specifies the bus number of the configuration address.

**Enable** (**EnReg**)—Bit 31. When this bit is set, aligned doubleword accesses to the Configuration Data Register result in configuration-space transactions.

- 0 = Configuration transactions disabled.

- 1 = Configuration transactions enabled.

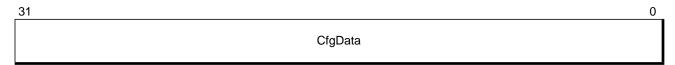

### 3.1.2 Configuration Data Register

Accesses to the Configuration Data Register are translated to configuration-space transactions at the address specified by the Configuration Address Register.

### **Configuration Data Register**

**0CFCh (Doubleword)**

| Bits | Mnemonic | Function           | R/W |

|------|----------|--------------------|-----|

| 31–0 | CfgData  | Configuration Data | R/W |

### **Field Descriptions**

Configuration Data (CfgData)—Bits 31–0.

# 3.2 Memory System Configuration Registers

The AMD Athlon™ 64 and AMD Opteron™ processors implement memory system configuration registers in the "Northbridge" block of the processor. These registers are mapped into the coherent HyperTransport technology configuration space (Bus 0, device numbers 24–31). The number of devices implemented is equal to the number of processor nodes in the system. Configuration space Device 24 corresponds to Node 0 and is normally the bootstrap processor (BSP). Configuration space device numbers 25 through 31 correspond to nodes 1 through 7, which may or may not be implemented.

The processor implements configuration registers in PCI configuration space using the following four headers:

- Function 0: HyperTransport technology configuration (see page 27)

- Function 1: Address map configuration (see page 53)

- Function 2: DRAM configuration (see page 66)

- Function 3: Miscellaneous configuration (see page 88)

Each of these functions are detailed in the following sections.

**Note:** Contents of some fields in the headers and HyperTransport technology capability blocks are maintained through a warm reset. If not specified otherwise, a field is initialized by a warm reset.

# 3.3 Function 0—HyperTransport™ Technology Configuration

Table 2. Function 0 Configuration Registers

| Offset | Register Name         |                  |                      | Reset              | Access     | Description |         |

|--------|-----------------------|------------------|----------------------|--------------------|------------|-------------|---------|

| 00h    | Device ID             |                  | Vendor ID (AMD)      |                    | 1100_1022h | RO          | page 29 |

| 04h    | Status                |                  | Command <sup>1</sup> |                    | 0010_0000h | RO          | page 30 |

| 08h    | Base<br>Class<br>Code | Subclass<br>Code | Program<br>Interface | Revision<br>ID     | 0600_0000h | RO          | page 30 |

| 0Ch    | BIST                  | Header<br>Type   | Latency<br>Timer     | Cache<br>Line Size | 0080_0000h | RO          | page 31 |

| 10h    | Base Address 0        |                  |                      | 0000_0000h         | RO         |             |         |

### Notes:

- 1. The unimplemented registers in the standard PCI configuration space are implemented as read-only and return 0 if read.

- Reads and writes to unimplemented registers in the extended PCI configuration space will result in unpredictable behavior.

Table 2. Function 0 Configuration Registers (Continued)

| Offset | Register Name                         |                   |               | Reset       | Access     | Description |         |

|--------|---------------------------------------|-------------------|---------------|-------------|------------|-------------|---------|

| 14h    | Base Addres                           | ss 1              |               |             | 0000_0000h | RO          |         |

| 18h    | Base Addres                           | ss 2              |               |             | 0000_0000h | RO          |         |

| 1Ch    | Base Addres                           | ss 3              |               |             | 0000_0000h | RO          |         |

| 20h    | Base Addres                           | ss 4              |               |             | 0000_0000h | RO          |         |

| 24h    | Base Addres                           | ss 5              |               |             | 0000_0000h | RO          |         |

| 28h    | Card Bus CI                           | IS Pointer        |               |             | 0000_0000h | RO          |         |

| 2Ch    | Sub-System                            | ı ID              | Sub-Syster    | n Vendor ID | 0000_0000h | RO          |         |

| 30h    | ROM Base                              | Address           |               |             | 0000_0000h | RO          |         |

| 34h    | Capabilities                          | Pointer           |               |             | page 31    | RO          | page 31 |

| 38h    | reserved                              |                   |               |             | 0000_0000h | RO          |         |

| 3Ch    | Max Latency  Min GNT Int Pin Int Line |                   |               | 0000_0000h  | RO         |             |         |

| 40h    | Routing Tab                           | le Node 0         | •             | •           | 0001_0101h | RW          | page 32 |

| 44h    | Routing Tab                           | le Node 1         |               |             | 0001_0101h | RW          | page 32 |

| 48h    | Routing Tab                           | le Node 2         |               |             | 0001_0101h | RW          | page 32 |

| 4Ch    | Routing Tab                           | le Node 3         |               |             | 0001_0101h | RW          | page 32 |

| 50h    | Routing Tab                           | le Node 4         |               |             | 0001_0101h | RW          | page 32 |

| 54h    | Routing Tab                           | le Node 5         |               |             | 0001_0101h | RW          | page 32 |

| 58h    | Routing Tab                           | le Node 6         |               |             | 0001_0101h | RW          | page 32 |

| 5Ch    | Routing Tab                           | le Node 7         |               |             | 0001_0101h | RW          | page 32 |

| 60h    | Node ID                               |                   |               |             | 0000_0000h | RW          | page 34 |

| 64h    | Unit ID                               |                   |               |             | 0000_00E4h | RW          | page 35 |

| 68h    | HyperTransp                           | oort™ Trans       | action Contr  | ol          | 0F00_0000h | RW          | page 36 |

| 6Ch    | HyperTransp                           | oort™ Initial     | ization Contr | ol          | page 40    | RW          | page 40 |

| 80h    | LDT0 Capal                            | oilities          |               |             | page 42    | RO          | page 42 |

| 84h    | LDT0 Link C                           | Control           |               |             | 0011_0000h | RW          | page 43 |

| 88h    | LDT0 Frequency/Revision               |                   | page 47       | RW          | page 47    |             |         |

| 8Ch    | LDT0 Feature Capability               |                   | 0000_0002h    | RO          | page 48    |             |         |

| 90h    | LDT0 Buffer                           | LDT0 Buffer Count |               | page 49     | RW         | page 49     |         |

| 94h    | LDT0 Bus Number                       |                   | 0000_0000h    | RW          | page 51    |             |         |

| 98h    | LDT0 Type                             |                   |               | page 51     | RO         | page 51     |         |

| A0h    | LDT1 Capal                            | oilities          |               |             | page 42    | RO          | page 42 |

| A4h    | LDT1 Link C                           | Control           |               |             | 0011_0000h | RW          | page 43 |

### Notes:

- 1. The unimplemented registers in the standard PCI configuration space are implemented as read-only and return 0 if read

- 2. Reads and writes to unimplemented registers in the extended PCI configuration space will result in unpredictable behavior.

**Table 2. Function 0 Configuration Registers (Continued)**

| Offset | Register Name           | Reset      | Access | Description |

|--------|-------------------------|------------|--------|-------------|

| A8h    | LDT1 Frequency/Revision | page 47    | RW     | page 47     |

| ACh    | LDT1 Feature Capability | 0000_0002h | RO     | page 48     |

| B0h    | LDT1 Buffer Count       | page 49    | RW     | page 49     |

| B4h    | LDT1 Bus Number         | 0000_0000h | RW     | page 51     |

| B8h    | LDT1 Type               | page 51    | RO     | page 51     |

| C0h    | LDT2 Capabilities       | page 42    | RO     | page 42     |

| C4h    | LDT2 Link Control       | 0011_0000h | RW     | page 43     |

| C8h    | LDT2 Frequency/Revision | page 47    | RW     | page 47     |

| CCh    | LDT2 Feature Capability | 0000_0002h | RO     | page 48     |

| D0h    | LDT2 Buffer Count       | page 49    | RW     | page 49     |

| D4h    | LDT2 Bus Number         | 0000_0000h | RW     | page 51     |

| D8h    | LDT2 Type               | page 51    | RO     | page 51     |

### Notes:

- 1. The unimplemented registers in the standard PCI configuration space are implemented as read-only and return 0 if read.

- 2. Reads and writes to unimplemented registers in the extended PCI configuration space will result in unpredictable behavior.

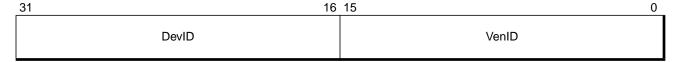

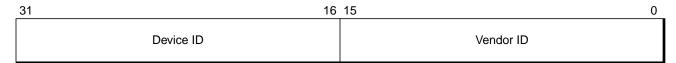

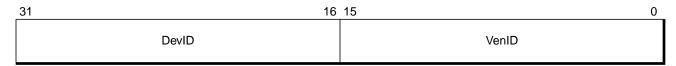

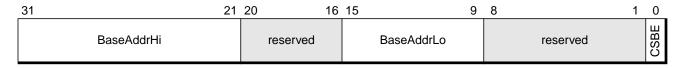

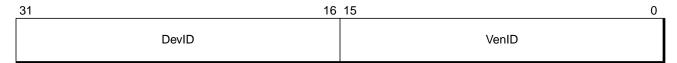

### 3.3.1 Device/Vendor ID Register

This register specifies the device and vendor IDs for the Function 0 registers and is part of the standard PCI configuration header.

### **Device/Vendor ID Register**

| Bits  | Mnemonic | Function  | R/W | Reset |

|-------|----------|-----------|-----|-------|

| 31–16 | DevID    | Device ID | R   | 1100h |

| 15–0  | VenID    | Vendor ID | R   | 1022h |

### **Field Descriptions**

**Vendor ID (VenID)**—Bits 15–0. This read-only value is defined as 1022h for AMD.

**Device ID (DevID)**—Bits 31–16. This read-only value is defined as 1100h for the HyperTransport technology configuration function.

Function 0: Offset 00h

26094 Rev. 3.06 September 2003

Function 0: Offset 04h

Function 0: Offset 08h

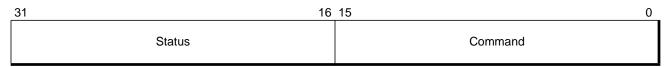

### 3.3.2 Status/Command Register

This register contains status and command information for the Function 0 registers and is part of the standard PCI configuration header.

### **Status/Command Register**

| Bits  | Mnemonic | Function | R/W | Reset |

|-------|----------|----------|-----|-------|

| 31–16 |          | Status   | R   | 0010h |

| 15–0  |          | Command  | R   | 0000h |

### **Field Descriptions**

**Command**—Bits 15–0. This read-only value is defined as 0000h.

**Status**—Bits 31–16. This read-only value is defined as 0010h to indicate that the processor has a capabilities list containing configuration information specific to HyperTransport technology.

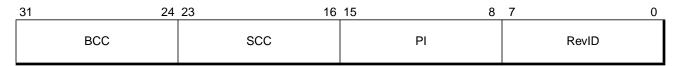

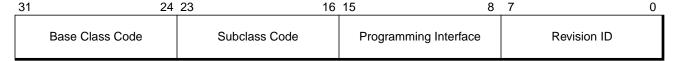

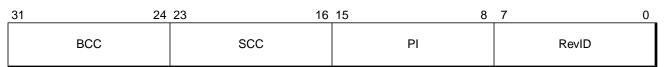

### 3.3.3 Class Code/Revision ID Register

This register specifies the class code and revision for the Function 0 registers and is part of the standard PCI configuration header.

### Class Code/Revision ID Register

| Bits  | Mnemonic | Function              | R/W | Reset |

|-------|----------|-----------------------|-----|-------|

| 31–24 | BCC      | Base Class Code       | R   | 06h   |

| 23–16 | SCC      | Subclass Code         | R   | 00h   |

| 15–8  | PI       | Programming Interface | R   | 00h   |

| 7–0   | RevID    | Revision ID           | R   | 00h   |

### **Field Descriptions**

**Revision ID** (**RevID**)—Bits 7–0.

**Programming Interface (PI)**—Bits 15–8. This read-only value is defined as 00h.

**Sub Class Code (SCC)**—Bits 23–16. This read-only value is defined as 00h.

Function 0: Offset 0Ch

**Base Class Code** (**BCC**)—Bits 31–24. This read-only value is defined as 06h for a host bridge device.

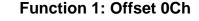

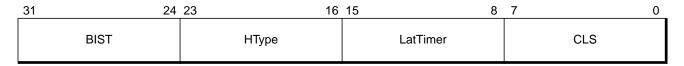

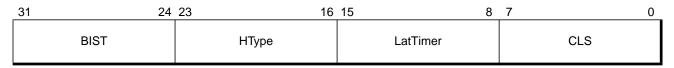

### 3.3.4 Header Type Register

This register specifies the header type for the Function 0 registers and is part of the standard PCI configuration header.

### **Header Type Register**

| 31 24 | 23 16 | 15 8     | 7 0 |

|-------|-------|----------|-----|

| BIST  | НТуре | LatTimer | CLS |

| Bits  | Mnemonic | Function        | R/W | Reset |

|-------|----------|-----------------|-----|-------|

| 31–24 | BIST     | BIST            | R   | 00h   |

| 23–16 | НТуре    | Header Type     | R   | 80h   |

| 15–8  | LatTimer | Latency Timer   | R   | 00h   |

| 7–0   | CLS      | Cache Line Size | R   | 00h   |

### **Field Descriptions**

**CacheLineSize** (CLS)—Bits 7–0. This read-only value is defined as 00h.

**LatencyTimer** (**LatTimer**)—Bits 15–8. This read-only value is defined as 00h.

**HeaderType** (**HType**)—Bits 23–16. This read-only value is defined as 80h to indicate that multiple functions are present in the configuration header and that the header layout corresponds to a device header as opposed to a bridge header. See "Register Differences in Revisions of the AMD Athlon<sup>TM</sup> 64 and AMD Opteron<sup>TM</sup> processors" on page 19 for revision information about this field.

**BIST**—Bits 31–24. This read-only value is defined as 00h.

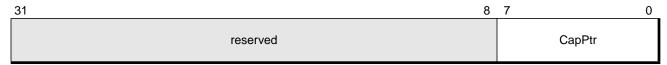

### 3.3.5 Capabilities Pointer Register

This register contains a capabilities pointer to a linked capabilities list of registers specific to HyperTransport technology, with one set for each HyperTransport link. It is part of the standard PCI configuration header.

### **Capabilities Pointer Register**

Function 0: Offset 34h

| Bits | Mnemonic | Function           | R/W | Reset |

|------|----------|--------------------|-----|-------|

| 31–8 | reserved |                    | R   | 0     |

| 7–0  | CapPtr   | Capability Pointer | R   |       |

### **Field Descriptions**

**Capability Pointer (CapPtr)**—Bits 7–0. Points to the first available HyperTransport technology capabilities block. Depending on the specific HyperTransport link configuration physically present on the processor, this will be either 80h (LDT0), A0h (LDT1) or C0h (LDT2).

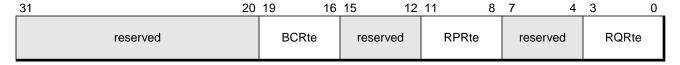

### 3.3.6 Routing Table Node *i* Registers

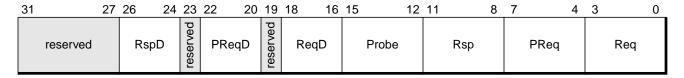

The routing table contains three entries—one for requests RQRoute[7:0], one for responses RPRoute[7:0], and one for broadcasts BCRoute[7:0].

A maximum of eight nodes with three links per node is supported in an AMD Opteron<sup>TM</sup> system.

These table entries can be read and written, and its contents are not maintained through a warm reset. At reset, all table entries are initialized to the value 01h, indicating that packets should be accepted by this node. Care must be exercised when changing table entries after reset to ensure that connectivity is not lost during the process.

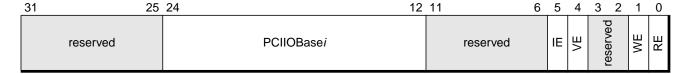

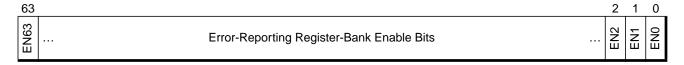

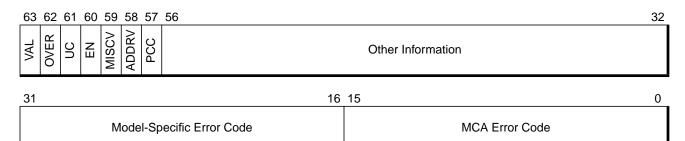

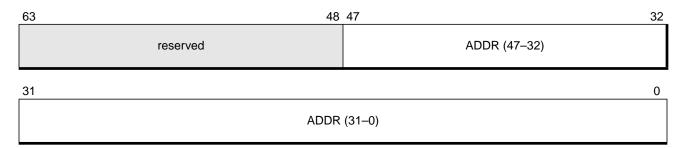

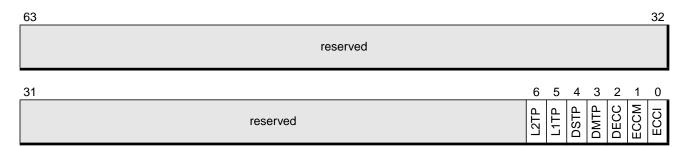

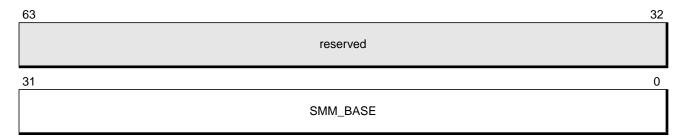

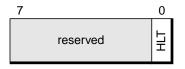

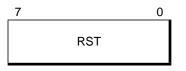

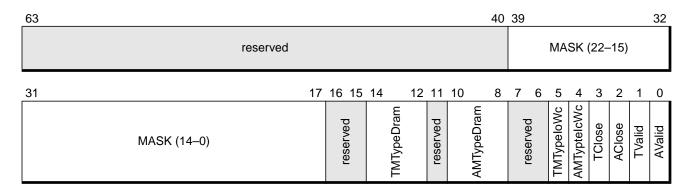

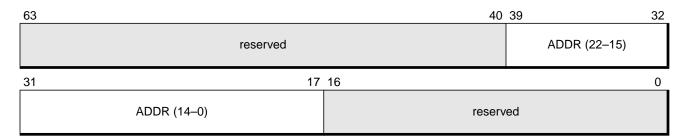

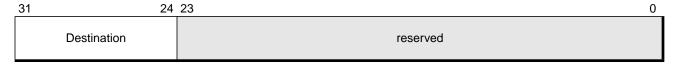

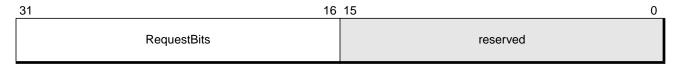

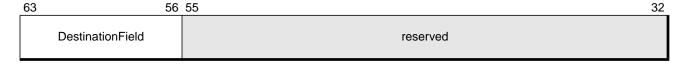

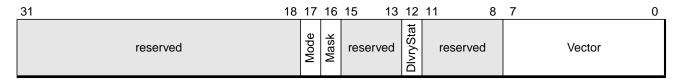

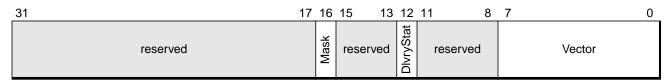

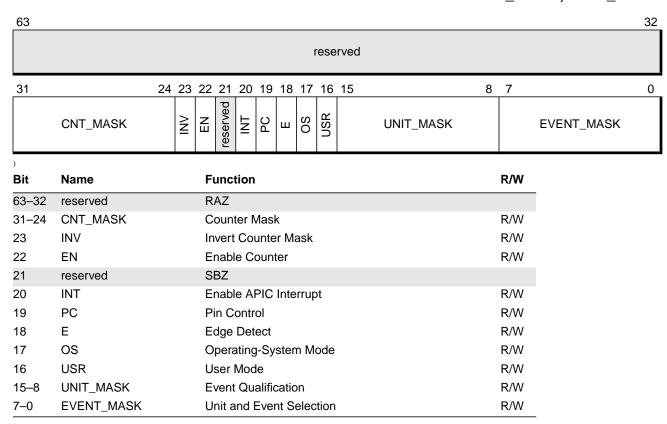

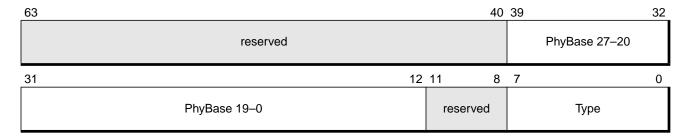

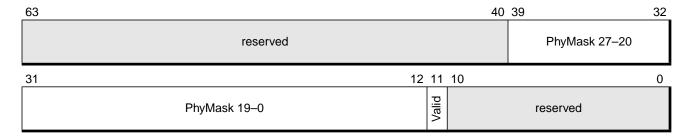

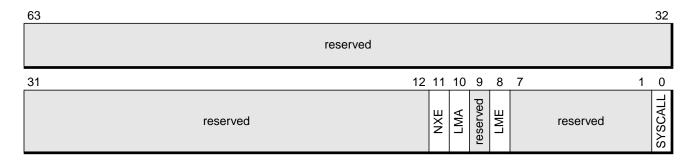

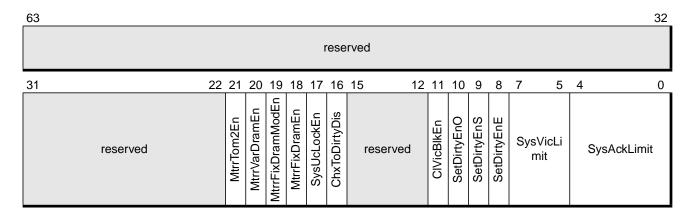

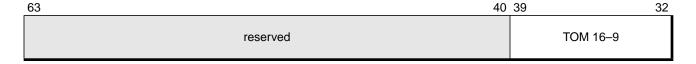

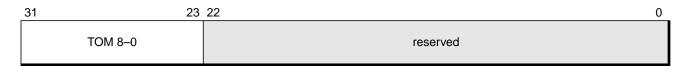

### 3.3.6.1 Request Routing Table