# MOS INTEGRATED CIRCUIT $\mu PD98404$

### ADVANCED ATM SONET FRAMER

#### DESCRIPTION

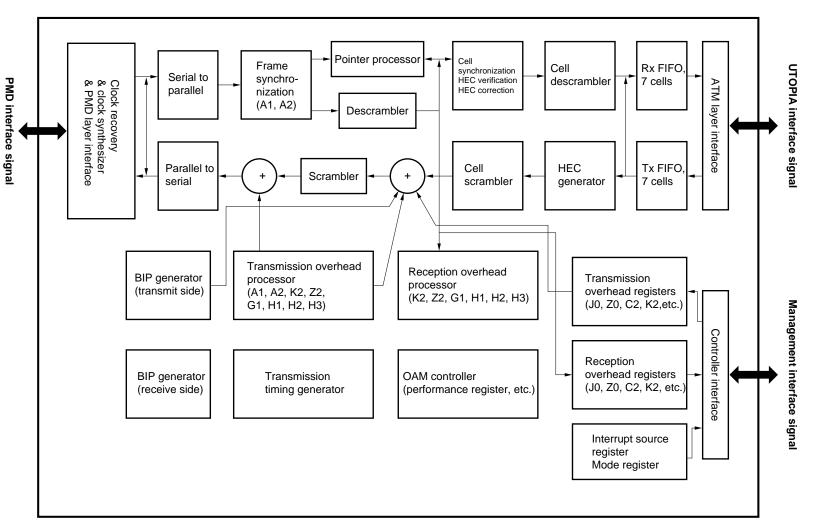

The  $\mu$ PD98404 NEASCOT-P30<sup>TM</sup> is an LSI for ATM applications, which can be used in ATM adapter boards for connecting PCs or workstations to an ATM network and can also be used in ATM hubs and ATM switches. This LSI provides the TC sub-layer functions in the SONET/SDH-base physical layer within the ATM protocol defined by the ATM Forum's UNI3.1 recommendations.

This product's main functions include transmission functions such as mapping of ATM cells sent from the ATM layer to the payload field in a 155 Mbps SONET STS-3c/SDH STM-1 frame and transmission to PMD (Physical Media Dependent) sub-layer in the physical layer. Its reception functions include separation of the overhead from the ATM cells in data streams received from PMD sub-layer and transmission of the ATM cells to the ATM layer. In addition, this LSI includes a clock recovery function that extracts a reception sync clock from bit streams in received data and a clock synthesis function that generates a clock for transmissions.

## Detailed function descriptions are provided in the following user's manuals. Be sure to read them before designing.

#### µPD98404 User's Manual: S11821E

#### FEATURES

- On-chip clock recovery/clock synthesis functions

- Provides TC sub-layer function for the ATM protocol's physical layer

- Supported frame formats include 155 Mbps SONET STS-3c/SDH STM-1

- Conforms to ATM Forum UTOPIA interface Level 2 V1.0 (af-phy-0039.000 June 1995) Supports three UTOPIA interfaces:

- Single PHY octet-level handshaking

- Single PHY cell-level handshaking

- Multi PHY mode

- Selectable to drop/bypass unassigned cells

- On-chip internal loopback functions for PMD layer loopback and ATM layer loopback

- Supports two PMD interfaces: serial and parallel

- · 155.52 Mbps serial interface

- 19.44 MHz parallel interface

- Provides registers for writing/reading overhead information

- SOH (section overhead) :J0 byte, Z0 (first and second) bytes, F1 byte

- LOH (line overhead) :K1 byte, K2 byte

- POH (path overhead) :F2 byte, C2 byte, H4 byte

- Provides pseudo error frame transmit function for various errors

- Supports JTAG boundary scan test function (IEEE 1149.1)

- CMOS technology

- +3.3 V single power supply

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

• Provides abundant OAM (Operation and Maintenance) functions

#### Transmit side

- Transmission of various alarm data

- \* Source-triggered automatic loopback transmission Line RDI, Path RDI Line REI, Path REI

- \* Command-specified transmission Line AIS, Path AIS

- Pseudo error generation frame transmit functions LOS generated frame OOF, LOF generated frame

LOP generated frame

OCD, LCD generated frame

- B1 error generated frame

- B2 error generated frame

- B3 error generated frame

#### Receive side

- Detection of alarm and fault signals LOS (Loss Of Signal)

OOF (Out Of Frame)

LOF (Loss Of Frame)

LOP (Loss Of Pointer)

OCD (Out of Cell Delineation)

LOC (Loss Of Cell delineation)

Line RDI, Path RDI

Line AIS, Path AIS

- Detection and display of quality loss sources B1 error, B2 error, B3 error, Line REI, Path-REI

- On-chip error counters

B1 byte error counter (16-bit)

B2 byte error counter (20-bit)

B3 byte error counter (16-bit)

- Line REI error counter (20-bit)

- Path REI error counter (16-bit)

Rx Frequency justification processing counter (12-bit) HEC error drop cell counter (20-bit) FIFO overflow drop cell counter (20-bit) Idle cell counter (20-bit)

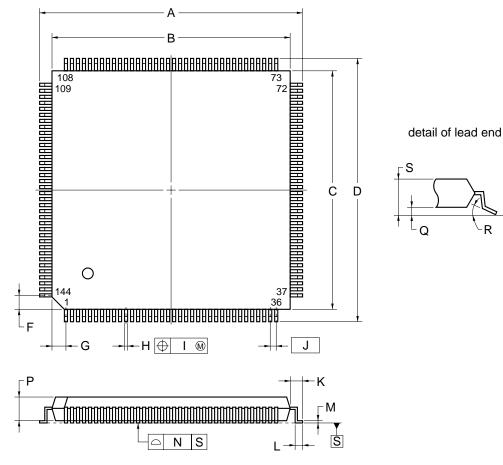

#### **ORDERING INFORMATION**

Part number

$\mu$ PD98404GJ-KEU

Package 144-pin plastic QFP (fine pitch) (20 × 20 mm)

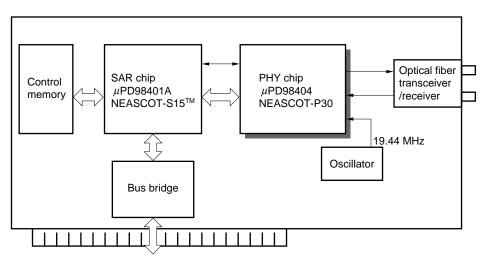

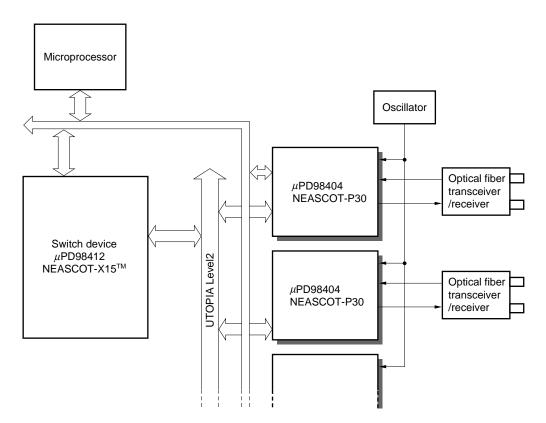

#### SYSTEM CONFIGURATION EXAMPLE

The following is an example of a system configuration using the  $\mu$ PD98404.

#### ATM adapter card application

Hub (terminal side) application

4

μPD98404

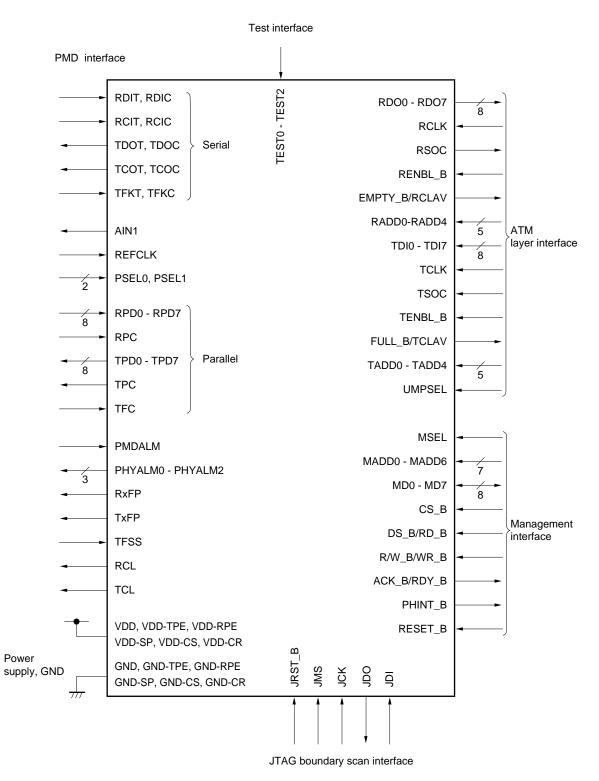

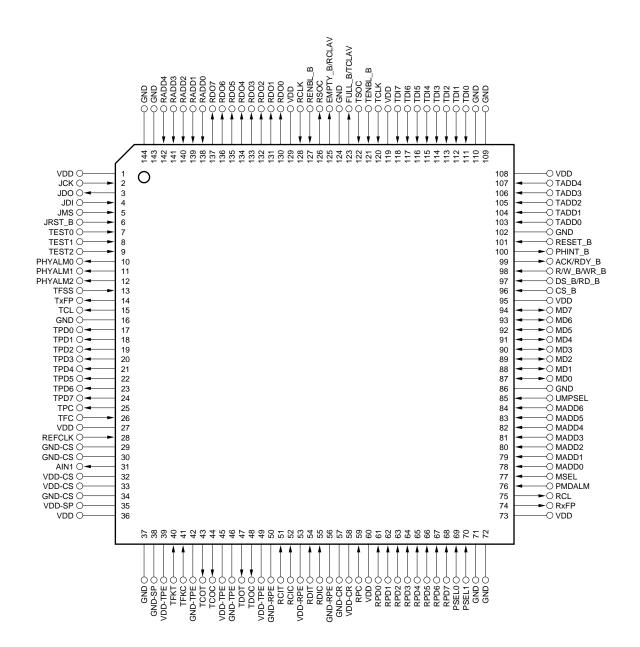

#### **PIN CONFIGURATION**

Remark Active low pins are indicated with the suffix "\_B" in this document.

#### **PIN CONFIGURATION (TOP VIEW)**

144-pin plastic QFP (fine pitch) (20 × 20 mm)

#### **PIN ALLOCATION**

| Number | Pin name | Number | Pin name | Number | Pin name    | Number | Pin name      |

|--------|----------|--------|----------|--------|-------------|--------|---------------|

| 1      | VDD      | 37     | GND      | 73     | VDD         | 109    | GND           |

| 2      | JCK      | 38     | GND-SP   | 74     | RxFP        | 110    | GND           |

| 3      | JDO      | 39     | VDD-TPE  | 75     | RCL         | 111    | TDI0          |

| 4      | JDI      | 40     | TFKT     | 76     | PMDALM      | 112    | TDI1          |

| 5      | JMS      | 41     | TFKC     | 77     | MSEL        | 113    | TDI2          |

| 6      | JRST_B   | 42     | GND-TPE  | 78     | MADD0       | 114    | TDI3          |

| 7      | TEST0    | 43     | TCOT     | 79     | MADD1       | 115    | TDI4          |

| 8      | TEST1    | 44     | TCOC     | 80     | MADD2       | 116    | TDI5          |

| 9      | TEST2    | 45     | VDD-TPE  | 81     | MADD3       | 117    | TDI6          |

| 10     | PHYALM0  | 46     | GND-TPE  | 82     | MADD4       | 118    | TDI7          |

| 11     | PHYALM1  | 47     | TDOT     | 83     | MADD5       | 119    | VDD           |

| 12     | PHYALM2  | 48     | TDOC     | 84     | MADD6       | 120    | TCLK          |

| 13     | TFSS     | 49     | VDD-TPE  | 85     | UMPSEL      | 121    | TENBL_B       |

| 14     | TxFP     | 50     | GND-RPE  | 86     | GND         | 122    | TSOC          |

| 15     | TCL      | 51     | RCIT     | 87     | MD0         | 123    | FULL_B/TCLAV  |

| 16     | GND      | 52     | RCIC     | 88     | MD1         | 124    | GND           |

| 17     | TPD0     | 53     | VDD-RPE  | 89     | MD2         | 125    | EMPTY_B/RCLAV |

| 18     | TPD1     | 54     | RDIT     | 90     | MD3         | 126    | RSOC          |

| 19     | TPD2     | 55     | RDIC     | 91     | MD4         | 127    | RENBL_B       |

| 20     | TPD3     | 56     | GND-RPE  | 92     | MD5         | 128    | RCLK          |

| 21     | TPD4     | 57     | GND-CR   | 93     | MD6         | 129    | VDD           |

| 22     | TPD5     | 58     | VDD-CR   | 94     | MD7         | 130    | RDO0          |

| 23     | TPD6     | 59     | RPC      | 95     | VDD         | 131    | RDO1          |

| 24     | TPD7     | 60     | VDD      | 96     | CS_B        | 132    | RDO2          |

| 25     | TPC      | 61     | RPD0     | 97     | DS_B/RD_B   | 133    | RDO3          |

| 26     | TFC      | 62     | RPD1     | 98     | R/W_B/WR_B  | 134    | RDO4          |

| 27     | VDD      | 63     | RPD2     | 99     | ACK_B/RDY_B | 135    | RDO5          |

| 28     | REFCLK   | 64     | RPD3     | 100    | PHINT_B     | 136    | RDO6          |

| 29     | GND-CS   | 65     | RPD4     | 101    | RESET_B     | 137    | RDO7          |

| 30     | GND-CS   | 66     | RPD5     | 102    | GND         | 138    | RADD0         |

| 31     | AIN1     | 67     | RPD6     | 103    | TADD0       | 139    | RADD1         |

| 32     | VDD-CS   | 68     | RPD7     | 104    | TADD1       | 140    | RADD2         |

| 33     | VDD-CS   | 69     | PSEL0    | 105    | TADD2       | 141    | RADD3         |

| 34     | GND-CS   | 70     | PSEL1    | 106    | TADD3       | 142    | RADD4         |

| 35     | VDD-SP   | 71     | GND      | 107    | TADD4       | 143    | GND           |

| 36     | VDD      | 72     | GND      | 108    | VDD         | 144    | GND           |

#### **PIN NAMES**

| ACK_B                    | : Read/write Cycle Receive Acknowledge | REFCLK      | : System Clock                               |

|--------------------------|----------------------------------------|-------------|----------------------------------------------|

| AIN1                     | : External Filter Connection           | RENBL_B     | : Receive Data Enable                        |

| CS                       | : Chip Select                          | RESET_B     | : System Reset                               |

| DS_B                     | : Data Strobe                          | RPC         | : Receive Parallel Data Clock                |

| EMPTY_B                  | : Output Buffer Empty                  | RPD0-RPD7   | : Receive Parallel Data                      |

| FULL_B                   | : Buffer Full                          | RSOC        | : Receive Start Address of ATM Cell          |

| GND                      | : Ground                               | RxFP        | : Receive Frame Pulse                        |

| GND-RPE                  | : Ground for Receive PECL Buffer       | R/W_B       | : Read/write Control                         |

| GND-CR                   | : Ground for Clock Recovery Circuit    | TADD0-TADD4 | 4 : Transmit PHY Device Address              |

| GND-CS                   | : Ground for Clock Synthesis           | TCL         | : Internal Transmit System Clock             |

| GND-SP                   | : Ground for Serial/Parallel Circuit   | TCLAV       | : Transmit Cell Available                    |

| GND-TPE                  | : Ground for Transmit PECL Buffer      | TCLK        | : Transmit Data Transferring Clock           |

| JCK                      | : JTAG Clock                           | TCOC        | : Transmit Clock Output Complement           |

| JDI                      | : JTAG Data Input                      | тсот        | : Transmit Clock Output True                 |

| JDO                      | : JTAG Data Output                     | TDI0-TDI7   | : Transmit Data Input from the ATM Layer     |

| JMS                      | : JTAG Mode Select                     | TDOC        | : Transmit Data Output Complement            |

| JRST_B                   | : JTAG Reset                           | TDOT        | : Transmit Data Output True                  |

| MADD0-MADD               | 6: Management Interface Address Bus    | TENBL_B     | : Transmit Data Enable                       |

| MD0-MD7                  | : Management Interface Data Bus        | TEST0-TEST2 | : Test Mode Pin                              |

| MSEL                     | : Management Interface Mode Select     | TFC         | : Transmit Reference Clock                   |

| PHINT_B                  | : Physical Interrupt                   | TFKC        | : Transmit Reference Clock Complement        |

| PHYALM0-                 | : PHY Alarm Detection                  | TFKT        | : Transmit Reference Clock True              |

| PHYALM2                  |                                        | TFSS        | : Transmit Frame Set Signal                  |

| PMDALM                   | : PMD Device Alarm                     | TPC         | : Transmit Parallel Data Clock               |

| PSEL0, PSEL <sup>2</sup> | 1 : PMD Mode Select                    | TPD0-TPD7   | : Transmit Parallel Data                     |

| RADD0-RADD4              | 1 : Receive PHY Device Address         | TSOC        | : Transmit Start Address of ATM Cell         |

| RCIC                     | : Receive Clock Input Complement       | TxFP        | : Transmit Frame Pulse                       |

| RCIT                     | : Receive Clock Input True             | UMPSEL      | : Utopia Multi-PHY Mode Select               |

| RCL                      | : Internal Receive System Clock        | VDD         | : Supply Voltage for Logic Circuit           |

| RCLAV                    | : Receive Cell Available               | VDD-RPE     | : Voltage Supply for Receive PECL Buffer     |

| RCLK                     | : Receive Data Transferring Clock      | VDD-CR      | : Voltage Supply for Clock Recovery Circuit  |

| RD_B                     | : Read Select                          | VDD-CS      | : Voltage Supply for Clock Synthesis         |

| RDIC                     | : Receive Data Input Complement        | VDD-SP      | : Voltage Supply for Serial/Parallel Circuit |

| RDIT                     | : Receive Data Input True              | VDD-TPE     | : Voltage Supply for Transmit PECL Buffer    |

| RDO0-RDO7                | : Receive Data Output                  | WR_B        | : Write Select                               |

| RDY_B                    | :Ready Signal                          |             |                                              |

|                          |                                        |             |                                              |

(1/2)

#### 1. PIN FUNCTIONS

#### 1.1 PMD Interface

| Pin name      | Pin No. | I/O level              | I/O | Function                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDIT          | 54      | P-ECL<br>True(+)       | Ι   | Serial receive data input. When PSEL [1:0] is set to 00, the data is sampled on a clock recovered by the internal clock recovery PLL.                                                                                                                                                                                                  |

| RDIC          | 55      | P-ECL<br>Complement(-) | Ι   | When PSEL [1:0] is set to 01, the data is sampled on the clock input to RCIT/RCIC.                                                                                                                                                                                                                                                     |

| RCIT          | 51      | P-ECL<br>True(+)       | Ι   | Serial receive clock input (155.52 MHz).<br>When PSEL [1:0] is set to 01, the input is used as a receive clock.                                                                                                                                                                                                                        |

| RCIC          | 52      | P-ECL<br>Complement(-) | Ι   |                                                                                                                                                                                                                                                                                                                                        |

| TDOT          | 47      | P-ECL<br>True(+)       | 0   | Serial transmit data output. The data is output in sync with the rising edge of the serial clock TCOT.                                                                                                                                                                                                                                 |

| TDOC          | 48      | P-ECL<br>Complement(-) | 0   |                                                                                                                                                                                                                                                                                                                                        |

| тсот          | 43      | P-ECL<br>True(+)       | 0   | Serial transmit clock output (155.52 MHz).<br>When PSEL [1:0] is set to 00, the clock generated by the internal<br>synthesizer PLL is output as the transmit clock. When PSEL [1:0] is<br>set to 01, the clock supplied to TFKT/TFKC is output.                                                                                        |

| тсос          | 44      | P-ECL<br>Complement(-) | 0   | Depending on the mode selected, the transmit data may be latched<br>by the receive clock for output. Even in such a case, this pin outputs<br>the clock of the internal synthesizer or the clock input to the<br>TFKT/TFKC pin in accordance with the setting of the PSEL[1:0] pins.<br>It does not output the receive recovery clock. |

| TFKT          | 40      | P-ECL<br>True(+)       | I   | Serial transmit clock input (155.52 MHz).<br>When PSEL [1:0] is set to 01, the input is used as the transmit clock.                                                                                                                                                                                                                    |

| TFKC          | 41      | P-ECL<br>Complement(-) | Ι   |                                                                                                                                                                                                                                                                                                                                        |

| RPD0-<br>RPD7 | 61-68   | TTL*                   | Ι   | Parallel receive data input. When PSEL [1:0] is set to 1X, these pins input receive data. The data is sampled in sync with the rising edge of parallel receive clock RPC.                                                                                                                                                              |

| RPC           | 59      | TTL*                   | Ι   | Parallel receive clock input (19.44 MHz).<br>When PSEL [1:0] is set to 1X to select parallel mode, this pin inputs a<br>19.44 MHz receive clock.                                                                                                                                                                                       |

| TPD0-<br>TPD7 | 17-24   | TTL*                   | 0   | Parallel transmit data output. When PSEL [1:0] is set to 1X to select parallel mode, these pins output transmit data in sync with the rising edge of PC.                                                                                                                                                                               |

| TPC           | 25      | TTL*                   | 0   | Parallel transmit clock output. When PSEL [1:0] is set to 1X, this pin outputs the clock (19.44 MHz) supplied to TFC.                                                                                                                                                                                                                  |

★

(2/3)

|   | Pin name            | Pin No. | I/O level | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|---------------------|---------|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * | TFC                 | 26      | TTL*      | I   | Parallel transmit clock input. When PSEL [1:0] is set to 1X to select parallel mode, this pin inputs a parallel transmit clock of 19.44 MHz. If the TxCL bits [1:0] of the MDR1 register are set to 10 in the serial mode with PSEL[1:0] = "00", input the 19.44 MHz source clock of the internal clock synthesizer PLL.                                                                                                                                                                                                               |

| * | REFCLK              | 28      | TTL*      | I   | Reference clock input. This pin supplies a system clock of 19.44 MHz to the internal clock recovery/synthesizer. Always input this clock.                                                                                                                                                                                                                                                                                                                                                                                              |

|   | PSEL0,<br>PSEL1     | 69, 70  | TTL*      | Ι   | <ul> <li>PMD interface mode select input. These pins select the interface mode of the PMD layer to be used.</li> <li>PSEL [1:0] = 00 :Serial mode. The clock generated by the internal clock recovery/synthesizer PLL is used for transmission and reception.</li> <li>PSEL [1:0] = 01 :Serial mode. The clock input of the external RCIT/RCIC and TFKT/TFKC is used for transmission and reception.</li> <li>PSEL [1:0] = 1x:Parallel mode. The clock input of RPC and TFC is used.</li> </ul>                                        |

| * | AIN1                | 31      | Analog    | 0   | This pin connects the loop filter of the internal synthesizer PLL. Leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | PMDALM              | 76      | TTL*      | I   | PMD layer alarm signal input. The signal level of this pin is reflected<br>in the state bit of an internal register. The transition of the bit can be<br>used as an interrupt source. The state signal from a peripheral<br>device is input.                                                                                                                                                                                                                                                                                           |

|   | PHYALM0-<br>PHYALM2 | 10-12   | TTL*      | 0   | PHY layer alarm detection signal output. These pins output a signal indicating that an internally monitored error state (PMDALM, CMDARM, LOS, OOF, LOF, LOP, OCD, LCD, Line AIS, Path AIS, Line RDI, or Path RDI) has been detected. The pins can output an error either singly or in combination. The type of the error to be indicated is selected by setting the internal AMPR, AMR1, and AMR2 registers. For details on use, refer to <b>3.5</b> Alarm Report Pins (PHYALM[2:0], PMDALM) in $\mu$ PD98404 User's Manual (S11821E). |

|   | RxFP                | 74      | TTL*      | 0   | Frame pulse output for the receive side (8 kHz). This pin outputs a pulse signal at one-clock intervals in sync with the RCL clock in the frame synchronization state.                                                                                                                                                                                                                                                                                                                                                                 |

$\star$

$\star$

(3/3)

| Pin name | Pin No. | I/O level | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|---------|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxFP     | 14      | TTL*      | 0   | Frame pulse signal output for the transmit side (8 kHz). This pin outputs a pulse signal at one-clock intervals in sync with the TCL clock.                                                                                                                                                                                                                                                                                |

| TFSS     | 13      | TTL*      | I   | Transmit frame output disable signal input. When the signal is high, the transmit frame output stops. When the signal is low, transmission starts from the beginning of a frame. The $\mu$ PD98404 samples this signal at the rising edge of the TCL clock. The transmit frame output is resumed at the ninth rising edge of the TCL clock after the rising edge at which the high level of this signal was last detected. |

| RCL      | 75      | TTL*      | 0   | Internal system clock output for the receive side (19.44 MHz). This pin outputs the receive clock divided by 8. The source receive clock depends on the selected mode, which is either the clock generated by the internal clock recovery PLL or the clock supplied from the RCIT/RCIC and RFC pins. Clock output from this pin is stopped while the device is being reset.                                                |

| TCL      | 15      | TTL*      | 0   | Internal system clock output of the transmit side (19.44 MHz).<br>This pin outputs the transmit clock divided by 8. The source transmit<br>clock depends on the selected mode, which is either the clock<br>generated by the internal synthesizer or the clock supplied from the<br>TCIT/TCIC and TFC pins. Clock output from this pin is stopped while<br>the device is being reset.                                      |

#### 1.2 ATM layer interface

(1/2)

| Pin name      | Pin No. | I/O level | I/O                     | Function                                                                                                                                                                                                                                                                   |

|---------------|---------|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDO0-<br>RDO7 | 130-137 | TTL*      | O<br>(2 or 3-<br>state) | Receive data output.<br>These pins form an 8-bit data bus that outputs receive data to an ATM<br>layer device. The data is output in sync with the rising edge of the<br>RCLK clock. These pins operate in two or three states, depending on<br>the UTOPIA interface mode. |

| RCLK          | 128     | TTL*      | I                       | Receive clock input. This pin supplies a clock of up to 40 MHz for receive data transfer.                                                                                                                                                                                  |

| RSOC          | 126     | TTL*      | O<br>(2 or 3-<br>state) | Receive cell start position signal output.<br>This pin outputs a signal indicating the position of the first byte of a<br>receive cell. This pin operates in two or three states, depending on<br>the UTOPIA interface mode.                                               |

| RENBL_B       | 127     | TTL*      | I                       | Receive enable signal input.<br>This pin inputs a signal indicating that the ATM layer is ready to<br>receive data.                                                                                                                                                        |

| Pin name          | Pin No. | I/O level | I/O                     | (2/2)<br>Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|---------|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |         |           |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EMPTY_B/<br>RCLAV | 125     | TTL*      | O<br>(2 or 3-<br>state) | Receive FIFO data transfer disable signal output or<br>receive FIFO cell data transfer enable signal output.<br>This pin functions as either EMPTY_B (2-state operation) or RCLAV<br>(3-state operation), depending on the selected mode of the UTOPIA<br>interface.<br>EMPTY_B indicates that the receive FIFO has no receive data bytes<br>to be transferred to the ATM layer.<br>RCLAV indicates that the receive FIFO has data of at least once cell<br>to be transferred to the ATM layer. This pin operates in two or three<br>states, depending on the UTOPIA interface mode. |

| RADD0-<br>RADD4   | 138-142 | TTL*      | I                       | PHY address input for the receive side. In multi-PHY mode, these pins input the address of the PHY layer device to be selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TDI0-<br>TDI7     | 111-118 | TTL*      | I                       | Transmit data input. These pins form an 8-bit data bus that inputs transmit data. The data is input in sync with the rising edge of the TCLK clock.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TCLK              | 120     | TTL*      | I                       | Transmit clock input. This pin inputs a clock of 20 to 40 MHz for transmit data transfer.<br><b>Caution The</b> $\mu$ PD98404 also uses this clock as the system clock of the management interface block. Therefore, always input a clock of 20 MHz or higher.                                                                                                                                                                                                                                                                                                                       |

| TSOC              | 122     | TTL*      | I                       | Transmit cell start position input.<br>This pin inputs a signal indicating the position of the first byte of the transmit cell input to the $\mu$ PD98404.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TENBL_B           | 121     | TTL*      | I                       | Transmit enable input.<br>This pin inputs a signal indicating that an ATM layer device is<br>outputting valid transmit data to TDI0 - TDI7.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FULL_B/<br>TCLAV  | 123     | TTL*      | O<br>(2 or 3-<br>state) | Transmit FIFO data transfer disable signal output or transmit FIFO<br>cell data transfer enable signal output.<br>This pin functions as either FULL_B (2-state operation) or TCLAV (3-<br>state operation), depending on the selected UTOPIA interface mode.<br>FULL_B indicates that the transmit FIFO has no free area to receive<br>transmit data. TCLAV indicates that the transmit FIFO has a free<br>area of at least one cell for storing transmit data. This pin operates in<br>two or three states, depending on the UTOPIA interface mode.                                 |

| TADD0-<br>TADD4   | 103-107 | TTL*      | I                       | PHY address input for the transmit side. When used in multi-PHY mode, these pins input an address for selecting a PHY layer device.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UMPSEL            | 85      | TTL*      | Ι                       | <ul><li>Multi-PHY mode select signal input.</li><li>When the signal is high, multi-PHY mode is selected.</li><li>When the signal is low, single PHY mode is selected.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                      |

$\star$

#### 1.3 Management interface

| 1.3 Mana        | gement in | terface   |                      | (1/2)                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-----------|-----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name        | Pin No.   | I/O level | I/O                  | Function                                                                                                                                                                                                                                                                                                                                           |

| MSEL            | 77        | TTL*      | I                    | <ul> <li>Mode select signal input. The level of input to this pin determines the management interface mode.</li> <li>MSEL = 1: Pin functions RD_B, WR_B, and RDY_B are selected.</li> <li>MSEL = 0: Pin functions DS_B, R/W_B, and ACK_B are selected.</li> </ul>                                                                                  |

| MADD0-<br>MADD6 | 78-84     | TTL*      | I                    | Address input.<br>These pins form an address bus to input the address of an internal register of the $\mu$ PD98404.                                                                                                                                                                                                                                |

| MD0-MD7         | 87-94     | TTL*      | I/O<br>(3-<br>state) | 8-bit data bus. These pins form a data bus to read or write data of an internal register of the $\mu$ PD98404.                                                                                                                                                                                                                                     |

| CS_B            | 96        | TTL*      | I                    | Chip select signal input. When the signal is low, access to an internal register is enabled.                                                                                                                                                                                                                                                       |

| DS_B/<br>RD_B   | 97        | TTL*      | 1                    | <ul> <li>Data strobe signal input or read signal input. This pin functions as either DS_B or RD_B, depending on the mode selected by the MSEL pin.</li> <li>MSEL = 0: This pin functions as DS_B to input the data strobe signal.</li> <li>MSEL = 1: This pin functions as RD_B to select read access.</li> </ul>                                  |

| R/W_B/<br>WR_B  | 98        | TTL*      | I                    | Read/write signal input or write signal input. This pin functions as<br>either R/W_B or WR_B, depending on the mode selected by the<br>MSEL pin.<br>MSEL = 0: This pin functions as R/W_B that inputs the<br>read/write control signal.<br>High: Read cycle<br>Low: Write cycle<br>MSEL = 1: This pin functions as WR_B that selects write access. |

| ACK_B/<br>RDY_B | 99        | TTL*      | O<br>(3-<br>state)   | <ul> <li>Data acknowledge signal output or ready signal output. This pin functions as either ACK_B or RDY_B, depending on the mode selected by the MSEL pin.</li> <li>MSEL = 0 : The pin functions as ACK_B that outputs the data strobe signal.</li> <li>MSEL = 1 : The pin functions as RDY_B that selects read access.</li> </ul>               |

| PHINT_B         | 100       | TTL*      | 0                    | Interrupt signal output.<br>This pin notifies the host that an internal interrupt source has been<br>detected. The pin is active low.                                                                                                                                                                                                              |

(2/2)

| Pin name | Pin No. | I/O level | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_B  | 101     | TTL*      | Ι   | System reset signal input. The signal initializes the $\mu$ PD98404. The input signal should be kept low for 1 $\mu$ s or more. Especially, in case of the power on, above-mentioned pulse width must be kept after the supply voltage reaches equal to or more than 90% at least. When the RESET_B signal is input, the following clock must be input according to the PMD interface mode. Serial mode : TCLK/RCLK clock Parallel mode: TCLK/RCLK and TFC/RPC clocks |

#### 1.4 JTAG boundary scan

| Pin name | Pin No. | I/O level | I/O                | Function                                                                                     |

|----------|---------|-----------|--------------------|----------------------------------------------------------------------------------------------|

| JDI      | 4       | TTL*      | Ι                  | Boundary scan data input.<br>When not being used, this pin should be grounded.               |

| JDO      | 3       | TTL*      | O<br>(3-<br>state) | Boundary scan data output.<br>When not being used, this pin should be left open.             |

| JCK      | 2       | TTL*      | I                  | Boundary scan clock input.<br>When not being used, this pin should be grounded.              |

| JMS      | 5       | TTL*      | I                  | Boundary scan mode select signal input.<br>When not being used, this pin should be grounded. |

| JRST_B   | 6       | TTL*      | I                  | Boundary scan reset signal input.<br>When not being used, this pin should be grounded.       |

**Remark** Processing of JTAG boundary scan pins not used (during normal operation) The reason that the JRST\_B pin is grounded when it is not used (during normal operation) is to better prevent malfunctioning of the JTAG logic. The JTAG pin may be also processed in either of the following ways:

> Reset the JTAG logic without using the JRST\_B pin Reset the JTAG logic by using the JMS and JCK pins and keep it in the reset status (the JRST\_B pin is pulled up).

Fix the JMS pin to 1 (pull up) and input 5 clock cycles or more to the JCK pin.

Reset the JTAG logic by using the JRST\_B pin

Input a low pulse of the same width as RESET\_B of the μPD98404 to the JRST\_B pin. If both the JMS and JRST\_B pins are pulled up and kept high, the JTAG logic is not released from the reset status. Therefore, the normal operation is not affected. Fix the input level of the JDI and JCK pins by pulling them down or up.

\*

#### 1.5 Internal test pins

| Pin name        | Pin No. | I/O level | I/O | Function                                                                                                                                                                               |

|-----------------|---------|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST0-<br>TEST2 | 7-9     | TTL*      | I   | These pins are used to test the $\mu$ PD98404. In normal operation, all these pins should be grounded.<br>TEST [2:0] =000 : Normal operation<br>TEST [2:0] =Other than 000 : Test mode |

#### 1.6 Power and ground

| Pin name | Pin No.                                             | I/O | Function                                                                                                                                           |  |

|----------|-----------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD      | 1, 27, 36, 60, 73, 95,<br>108, 119, 129             | -   | Power supply (+3.3 V $\pm 5\%)$ and ground for the general logic block.                                                                            |  |

| GND      | 16, 37, 71, 72, 86, 102,<br>109, 110, 124, 143, 144 | -   |                                                                                                                                                    |  |

| VDD-TPE  | 39, 45, 49                                          | -   | Power supply (+3.3 V $\pm 5\%$ ) and ground for output PECL I/O. Any noise in this power supply will affect the jitter characteristics. A          |  |

| GND-TPE  | 42, 46                                              | -   | means of eliminating this noise, such as a filter, is needed.                                                                                      |  |

| VDD-RPE  | 53                                                  | -   | Power supply (+3.3 V $\pm$ 5%) and ground for input PECL I/O. Any noise in this power supply will affect the jitter characteristics. A             |  |

| GND-RPE  | 50, 56                                              | -   | means of eliminating this noise, such as a filter, is needed.                                                                                      |  |

| VDD-SP   | 35                                                  | -   | Power supply (+3.3 V $\pm$ 5%) and ground for the serial /parallel block. Any noise in this power supply will affect the jitter characteristics. A |  |

| GND-SP   | 38                                                  | -   | means of eliminating this noise, such as a filter, is needed.                                                                                      |  |

| VDD-CS   | 32, 33                                              | -   | Power supply (+3.3 V $\pm$ 5%) and ground for the clock synthesizer PLL block. Any noise in this power supply will affect the jitter               |  |

| GND-CS   | 29, 30, 34                                          | -   | characteristics. A means of eliminating this noise, such as a filte needed.                                                                        |  |

| VDD-CR   | 58                                                  | -   | Power supply (+3.3 V $\pm$ 5%) and ground for the clock recovery PLL block. Any noise in this power supply will affect the jitter                  |  |

| GND-CR   | 57                                                  | -   | characteristics. A means of eliminating this noise, such as a filter, is needed.                                                                   |  |

#### **★**1.7 Recommended connection of unused pins

| Pin                       | Recommended Connection of Unused Pins                        |  |  |  |

|---------------------------|--------------------------------------------------------------|--|--|--|

| Each input pin at level   | Connect to ground (parallel input pin in serial mode)        |  |  |  |

| other than P-ECL          | RPD0 through RPD7, RPC, TFC                                  |  |  |  |

|                           | (Multi-PHY pins in single PHY mode)                          |  |  |  |

|                           | TADD0 to TADD4, RADD0 through RADD4                          |  |  |  |

|                           | (others)                                                     |  |  |  |

|                           | TFSS (essential)                                             |  |  |  |

| Each input pin at P-ECL   | Pull up True(+) pins (TFKT, RCIT, RDIT) to 3.3 V. Connect    |  |  |  |

| level                     | Complement(-) pins (TFKC, RCIC, RDIC) to ground.             |  |  |  |

| Output pin                | Leave open.                                                  |  |  |  |

|                           | (Parallel input pins in serial mode)                         |  |  |  |

|                           | TPD0 to TPD7                                                 |  |  |  |

|                           | TPC                                                          |  |  |  |

|                           | (others)                                                     |  |  |  |

|                           | TxFP, RxFP, TCL, RCL                                         |  |  |  |

| Output pin at P-ECL level | Leave open.                                                  |  |  |  |

|                           | TDOT, TDOC, TCOT, TCOC                                       |  |  |  |

| AIN1                      | Leave Open.                                                  |  |  |  |

|                           | Because noise on this pin affects the characteristics of the |  |  |  |

|                           | internal PLL, do not wire a clock line in the vicinity.      |  |  |  |

#### 2. ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings**

#### "\*" mark indicates portion which have been revised from old edition.

| Item                  | Symbol  | Condition                          | Ratings                  | Unit |

|-----------------------|---------|------------------------------------|--------------------------|------|

| Power supply voltage  | Vdd     |                                    | -0.5 to +4.6             | V    |

| Input/output voltage  | V11/V01 | Pin other than P-ECL, analog level | –0.5 to +6.6 or VDD +3.0 | V    |

|                       | V12/V02 | P-ECL, analog level                | –0.5 to +4.6 or VDD +0.5 | V    |

| Operating temperature | TA      |                                    | -45 to +85               | °C   |

| Storage temperature   | Tstg    |                                    | -65 to +150              | °C   |

Caution If even one of the parameters exceeds its absolute maximum rating even momentarily, the quality of the product may be degraded. The absolute maximum rating therefore specifies the upper or lower limit of the values at which the product can be used without physical damage. Be sure not to exceed or fall below these values when using the product.

#### Capacitance

| Parameter                | Symbol | Condition          | MIN. | TYP. | MAX. | Unit |

|--------------------------|--------|--------------------|------|------|------|------|

| Input capacitance        | Cı     | Frequency: = 1 MHz |      | 6    | 10   | pF   |

| Output capacitance       | Co     | Frequency: = 1 MHz |      | 6    | 10   | pF   |

| Input/output capacitance | Сю     | Frequency: = 1 MHz |      | 6    | 10   | pF   |

#### **Recommended Operating Conditions**

| Parameter                   | Symbol  | Condition                      | MIN.                        | TYP. | MAX.                        | Unit |

|-----------------------------|---------|--------------------------------|-----------------------------|------|-----------------------------|------|

| Power supply voltage        | Vdd     |                                | $V_{\text{DD}} \times 0.95$ | 3.3  | $V_{\text{DD}} \times 1.05$ | V    |

| Operating temperature range | TA      |                                | -40                         |      | +85                         | °C   |

| Low-level input voltage     | VIL1    | Pin other than P-ECL level pin | 0                           |      | 0.8                         | V    |

|                             | VIL2    | P-ECL level pin                | V <sub>DD</sub> - 2.82      |      | Vdd - 1.50                  | V    |

| High-level input voltage    | VIH1    | Pin other than P-ECL level pin | 2.2                         |      | 5.25                        | V    |

|                             | VIH2    | P-ECL level pin                | Vdd - 1.49                  |      | $V_{\text{DD}}-0.40$        | V    |

| Differential input voltage  | VIDIFF2 |                                | 300                         |      | 1900                        | mV   |

**Remark** P-ECL level pins: RDIT, RDIC, RCIT, RDIC, TDOT, TDOC, TCOT, TCOC, TFKT, TFKC Analog pins : AIN1

#### DC Characteristics (V<sub>DD</sub> = $3.3 \pm 0.15$ V, T<sub>A</sub> = -40 to $+85^{\circ}$ C)

| Parameter                 | Symbol | Condition                                                                 | MIN.        | TYP.        | MAX.        | Unit |

|---------------------------|--------|---------------------------------------------------------------------------|-------------|-------------|-------------|------|

| Off-state output current  | loz    | VI = VDD or GND                                                           |             |             | ±10         | μA   |

| Input leakage current     | IL11   | VI = VDD or GND                                                           |             |             | ±10         | μA   |

|                           |        | Pin other than P-ECL level pin                                            |             |             |             |      |

|                           | ILI2   | P-ECL level pin         ±10           IoL = +8mA, Vdd = 3.3 V         0.4 |             |             |             | μA   |

| Low-level output voltage  | Vol1   | Iol = +8mA, Vdd = 3.3 V                                                   |             |             | 0.4         | V    |

|                           |        | Pin other than P-ECL level pin                                            |             |             |             |      |

|                           | Vol2   | $R_L = 50 \ \Omega, \ V_T = V_{DD} - 2 \ V$                               | Vdd – 2.175 | Vdd – 1.975 | Vdd – 1.755 | V    |

|                           |        | P-ECL level pin                                                           |             |             |             |      |

| High-level output voltage | Vон1   | Іон = -8 mA, Vdd = 3.3 V                                                  | 2.4         |             |             | V    |

|                           |        | Pin other than P-ECL level pin                                            |             |             |             |      |

|                           | Vон2   | $R_L = 50 \Omega$ , $V_T = V_{DD} - 2 V$                                  | Vdd - 1.14  | Vdd - 0.92  | VDD - 0.69  | V    |

|                           |        | P-ECL level pin                                                           |             |             |             |      |

| Power supply current      | IDD    | During normal operation                                                   |             | 200         | 450         | mA   |

#### AC Characteristics (V<sub>DD</sub> = $3.3 \pm 0.15$ V, T<sub>A</sub> = -40 to $+85^{\circ}$ C)

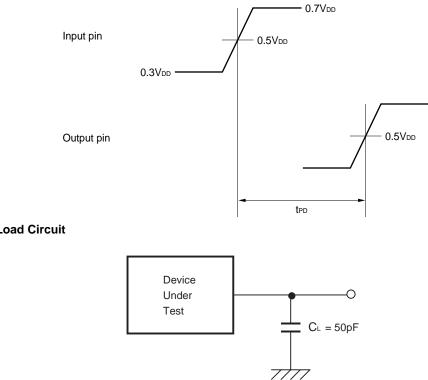

#### **AC Test Condition**

$\star$

The propagation delay time is defined as shown below.

AC Testing Load Circuit

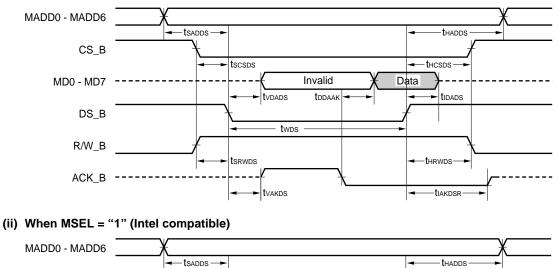

#### **Management Interface**

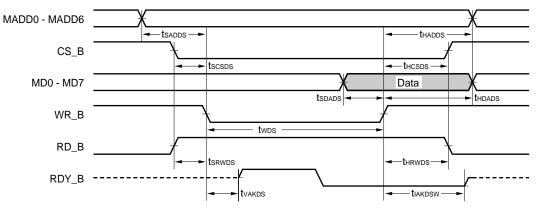

#### a) Internal register read

| Parameter                                                                                                                      | Symbol          | Condition             | MIN.      | TYP. | MAX.          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------|------|---------------|------|

| Address setup time (to DS_B $\downarrow$ [RD_B $\downarrow$ ])                                                                 | tsadds          |                       | 10        |      |               | ns   |

| CS_B setup time (to DS_B $\downarrow$ [RD_B $\downarrow$ ])                                                                    | tscsds          |                       | 5         |      | 9 	imes tсүтк | ns   |

| R/W_B[WR_B] setup time<br>(to DS_B↓ [RD_B↓])                                                                                   | tsrwds          |                       | 5         |      |               | ns   |

| Address hold time (to DS_B $\uparrow$ [RD_B $\uparrow$ ])                                                                      | <b>t</b> HADDS  |                       | 4         |      |               | ns   |

| CS_B hold time (to DS_B $\uparrow$ [RD_B $\uparrow$ ])                                                                         | tHCSDS          |                       | 0         |      |               | ns   |

| R/W_B [WR_B] hold time<br>(to DS_B↑ [RD_B↑])                                                                                   | <b>t</b> HRWDS  |                       | 4         |      |               | ns   |

| $\begin{array}{l} DS\_B \downarrow [RD\_B \downarrow] \to ACK\_B \ [RDY\_B] \\ \text{output delay time} \end{array}$           | <b>t</b> vakds  | Load capacity = 50 pF |           |      | 15            | ns   |

| $DS\_B\downarrow [RD\_B\downarrow] \rightarrow data \ output \ delay time$                                                     | tvdads          | Load capacity = 50 pF |           |      | 20            | ns   |

| $\begin{array}{l} DS\_B^{\uparrow} \; [RD\_B^{\uparrow}] \rightarrow ACK\_B \; [RDY\_B] \; float \\ delay \; time \end{array}$ | <b>t</b> IAKDSR | Load capacity = 50 pF | 5         |      | 30            | ns   |

| $DS\_B^{\uparrow}  [RD\_B^{\uparrow}] \to data \ float \ delay \ time$                                                         |                 | Load capacity = 50 pF | 15        |      | 45            | ns   |

| $ACK{\downarrow} \rightarrow data$ output delay time                                                                           | <b>t</b> ddaak  | Load capacity = 50 pF |           |      | 10            | ns   |

| DS_B[RD_B] pulse width <sup>Note</sup>                                                                                         | twos            |                       | 50        |      |               | ns   |

| $DS_B^{RD_B^{}} \rightarrow DS_B^{RD_B^{}} \downarrow$<br>recovery time                                                        | <b>t</b> dsint  |                       | 4 × tсутк |      |               | ns   |

×

\*

Note twos defines the time during which the μPD98404 can recognize DS\_B [RD\_B] as a low level, and does not define the pulse width of DS\_B [RD\_B] with which data can be accurately read.

The time required for the μPD98404 to make ACK\_B [RDY\_B] low after DS\_B [RD\_B] has gone low differs depending on the register to be accessed. Make DS\_B [RD\_B] high after confirming that ACK\_B [RDY\_B]. The time required for the μPD98404 to make ACK\_B [RDY\_B] low after DS\_B [RD\_B] has gone low is "4 x TCLK clock cycle (tcvTK)" at best. So that any register can be read without using ACK\_B [RDY\_B], widen the pulse width of DS\_B [RD\_B] to at least to "4 x TCLK clock cycle".

**Remark** tCYTK is the cycle of the TCLK clock.

Invalid

**t**DDAAK

-thcsps

tIDADS

-thrwds

-tiakdsr

Data

-

- tscsps

-

tsrwds

tvdads

tvakds

— twos –

(i) When MSEL = "0" (Motorola compatible)

CS\_B

RD\_B

WR\_B

RDY\_B -

MD0 - MD7 -

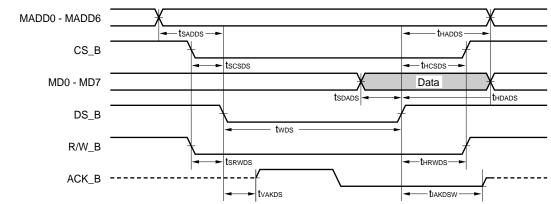

#### b) Internal register write

| Parameter                                                                                                                                                                      | Symbol          | Condition             | MIN.      | TYP. | MAX.          | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------|------|---------------|------|

| Address setup time (to DS_B $\downarrow$ [WR_B $\downarrow$ ])                                                                                                                 | <b>t</b> SADDS  |                       | 10        |      |               | ns   |

| CS_B setup time (to DS_B $\downarrow$ [WR_B $\downarrow$ ])                                                                                                                    | tscsds          |                       | 5         |      | 9 	imes tсүтк | ns   |

| R/W_B[RD_B] setup time<br>(to DS_B↓ [WR_B↓])                                                                                                                                   | tsrwds          |                       | 5         |      |               | ns   |

| Data setup time (to DS_B $\uparrow$ [WR_B $\uparrow$ ])                                                                                                                        | tsdads          |                       | 15        |      |               | ns   |

| Address hold time (to DS_B $\uparrow$ [WR_B $\uparrow$ ])                                                                                                                      | <b>t</b> HADDS  |                       | 4         |      |               | ns   |

| CS_B hold time (to DS_B $\uparrow$ [WR_B $\uparrow$ ])                                                                                                                         | thcsps          |                       | 0         |      |               | ns   |

| R/W_B [WR_B] hold time<br>(to DS_B↑ [WR_B↑])                                                                                                                                   | thrwds          |                       | 4         |      |               | ns   |

| Data hold time (to DS_B↑ [WR_B↑])                                                                                                                                              | thdads          |                       | 4         |      |               | ns   |

| $\begin{array}{l} DS\_B\downarrow [WR\_B\downarrow] \rightarrow ACK\_B [RDY\_B] \\ output delay time \end{array}$                                                              | tvakds          | Load capacity = 50 pF |           |      | 15            | ns   |

| $\label{eq:def-basic} \begin{array}{l} \text{DS}\_B^{\uparrow} \ [\text{WR}\_B^{\uparrow}] \rightarrow \text{ACK}\_B \ [\text{RDY}\_B] \\ \text{float delay time} \end{array}$ | <b>t</b> iakdsw | Load capacity = 50 pF |           |      | 10            | ns   |

| DS_B [WR_B] pulse width <sup>Note</sup>                                                                                                                                        | twos            |                       | 50        |      |               | ns   |

| $DS_B^{T}WR_B^{J}\rightarrow DS_B^{W}WR_B^{J}$ recovery time                                                                                                                   | <b>t</b> dsint  |                       | 4 × tсутк |      |               | ns   |

+

**Note** twos defines the time during which the  $\mu$ PD98404 can recognize DS\_B [WR\_B] as a low level, and does not define the pulse width of DS\_B [WR\_B] with which data can be accurately read.

The time required for the  $\mu$ PD98404 to make ACK\_B [RDY\_B] low after DS\_B [WR\_B] has gone low differs depending on the register to be accessed. Make DS\_B [WR\_B] high after confirming that ACK\_B [RDY\_B] has gone low.

The time required for the  $\mu$ PD98404 to make ACK\_B [RDY\_B] low after DS\_B [WR\_B] has gone low is "4 x TCLK clock cycle (tcvTk)" at best. So that any register can be write without using ACK\_B [RDY\_B], widen the pulse width of DS\_B [WR\_B] to at least to "4 x TCLK clock cycle".

**Remark** tCYTK is the cycle of the TCLK clock.

(i) When MSEL = "0" (Motorola compatible)

#### (ii) When MSEL = "1" (Intel compatible)

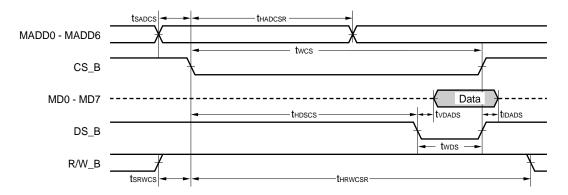

c) Internal register read/write (NEASCOT-S15 connection mode, MSEL = "0")

#### (i) Read timing

| Parameter                                               | Symbol          | Condition             | MIN.           | TYP. | MAX.               | Unit |

|---------------------------------------------------------|-----------------|-----------------------|----------------|------|--------------------|------|

| Address setup time (to CS_B $\downarrow$ )              | tsadcs          |                       | 10             |      |                    | ns   |

| R/W_B setup time (to CS_B↓)                             | tsrwcs          |                       | 10             |      |                    | ns   |

| Address hold time (to CS_B $\downarrow$ )               | <b>t</b> HADCSR |                       | 5×tсүтк+10     |      |                    | ns   |

| R/W_B hold time (to CS_B↓)                              | thrwcsr         |                       | 15×tсүтк+10    |      |                    | ns   |

| DS_B hold time (to CS_B↓)                               | tHDSCS          |                       | 15×tсүтк+10    |      |                    | ns   |

| $DS\_B {\downarrow} \to data \text{ output delay time}$ | tvdads          | Load capacity = 50 pF |                |      | <b>30 + t</b> сутк | ns   |

| $DS\_B^{\uparrow}\todata\ float\ delay\ time$           | tidads          | Load capacity = 50 pF | 15             |      | 45                 | ns   |

| CS_B pulse width                                        | twcs            |                       | 15 	imes tсүтк |      |                    | ns   |

| DS_B pulse width                                        | twos            |                       | 4 	imes tсүтк  |      |                    | ns   |

**Remark** tCYTK is the cycle of the TCLK clock.

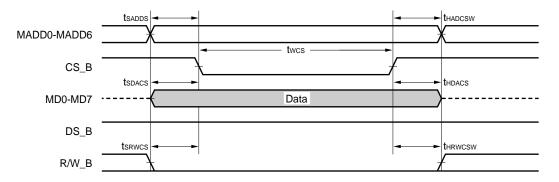

#### (ii) Write timing

| Parameter                                 | Symbol          | Condition | MIN.          | TYP. | MAX. | Unit |

|-------------------------------------------|-----------------|-----------|---------------|------|------|------|

| Address setup time (to $CS_B\downarrow$ ) | <b>t</b> SADCS  |           | 10            |      |      | ns   |

| R/W_B setup time (to CS_B↓)               | tsrwcs          |           | 10            |      |      | ns   |

| Data setup time (to $CS_B\downarrow$ )    | tsdacs          |           | 10            |      |      | ns   |

| Address hold time (to CS_B <sup>1</sup> ) | <b>t</b> HADCSW |           | 10            |      |      | ns   |

| R/W_B hold time (to CS_B↑)                | <b>t</b> HRWCSW |           | 10            |      |      | ns   |

| Data hold time (to CS_B↑)                 | <b>t</b> HDACS  |           | 10            |      |      | ns   |

| CS_B pulse width                          | twcs            |           | 4 	imes tсүтк |      |      | ns   |

**Remark** tcytk is the cycle of the TCLK clock.

\* Caution If the device is reset via software by setting the CMR2 register, do not read or write all the registers for the duration of at least "20 x TCLK clock cycle (tcytκ)" from that write cycle. Otherwise, the registers may not be read or written correctly.

## NEC

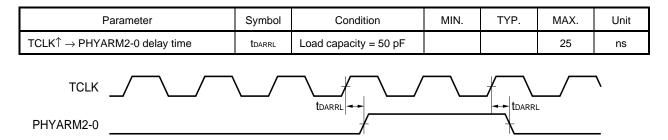

#### OAM interface

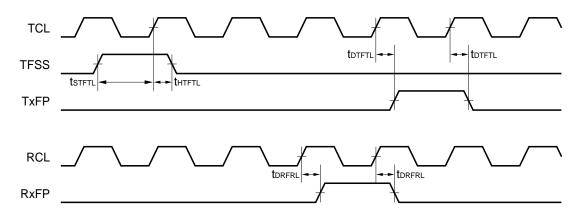

#### **Control signal interface**

| Parameter                                    | Symbol         | Condition             | MIN. | TYP. | MAX. | Unit |

|----------------------------------------------|----------------|-----------------------|------|------|------|------|

| TFSS setup time (to TCL↑)                    | <b>t</b> STFTL |                       | 20   |      |      | ns   |

| TFSS hold time (to TCL <sup>↑</sup> )        | <b>t</b> htftl |                       | 5    |      |      | ns   |

| $TCL^{\uparrow} \to TxFP \text{ delay time}$ | <b>t</b> dtftl | Load capacity = 50 pF |      |      | 25   | ns   |

| $RCL^\uparrow \to RxFP$ delay time           | <b>t</b> DRFRL | Load capacity = 50 pF |      |      | 25   | ns   |

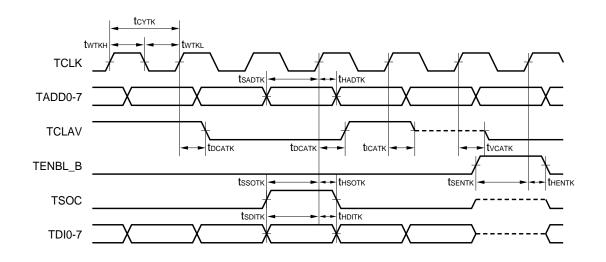

#### UTOPIA interface (transmit side)

|   | Parameter                                                           | Symbol         | Condition             | MIN.                        | TYP. | MAX.            | Unit |

|---|---------------------------------------------------------------------|----------------|-----------------------|-----------------------------|------|-----------------|------|

| * | TCLK cycle time                                                     | tсүтк          |                       | 25                          |      | 50              | ns   |

|   | TCLK high level width                                               | twткн          |                       | $0.4 	imes t_{\text{СУТК}}$ |      | 0.6 	imes tсутк | ns   |

|   | TCLK low level width                                                | twtĸ∟          |                       | $0.4 	imes t_{CYTK}$        |      | 0.6 	imes tсутк | ns   |

| * | $TCLK^{\uparrow} \to TCLAV^{\uparrow\downarrow} \text{ delay time}$ | <b>t</b> DCATK | Load capacity = 50 pF | 1                           |      | 19              | ns   |

|   | $TCLK^\uparrow \to TCLAV$ output delay time                         | tvcatk         | Load capacity = 50 pF | 1                           |      | 19              | ns   |

|   | $TCLK \uparrow \to TCLAV$ data float delay time                     | ticatk         | Load capacity = 50 pF | 1                           |      | 25              | ns   |

|   | TDI0-7 setup time (to TCLK↑)                                        | tsditk         |                       | 4                           |      |                 | ns   |

|   | TDI0-7 hold time (to TCLK↑)                                         | tноітк         |                       | 1                           |      |                 | ns   |

|   | TSOC setup time (to TCLK $\uparrow$ )                               | <b>t</b> ssotk |                       | 4                           |      |                 | ns   |

|   | TSOC hold time (to TCLK $\uparrow$ )                                | tнsотк         |                       | 1                           |      |                 | ns   |

|   | TADD0-7 setup time (to TCLK $\uparrow$ )                            | <b>t</b> sadtk |                       | 4                           |      |                 | ns   |

|   | TADD0-7 hold time (to TCLK↑)                                        | <b>t</b> hadtk |                       | 1                           |      |                 | ns   |

|   | TENBL_B setup time (to TCLK $\uparrow$ )                            | <b>t</b> sentk |                       | 4                           |      |                 | ns   |

|   | TENBL_B hold time (to TCLK $\uparrow$ )                             | <b>t</b> hentk |                       | 1                           |      |                 | ns   |

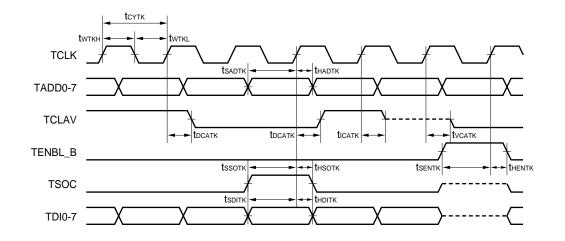

#### **UTOPIA** interface (receive side)

|   | Parameter                                                           | Symbol         | Condition             | MIN.            | TYP. | MAX.            | Unit |

|---|---------------------------------------------------------------------|----------------|-----------------------|-----------------|------|-----------------|------|

|   | RCLK cycle time                                                     | tсурк          |                       | 25              |      |                 | ns   |

|   | RCLK high level width                                               | <b>t</b> wrkh  |                       | 0.4 	imes tсурк |      | 0.6 	imes tсурк | ns   |

|   | RCLK low level width                                                | twrkl          |                       | 0.4 	imes tсурк |      | 0.6 	imes tсурк | ns   |

| * | $RCLK^{\uparrow}  ightarrow RCLAV^{\uparrow\downarrow}$ delay time  | <b>t</b> dcark | Load capacity = 50 pF | 1               |      | 19              | ns   |

|   | $RCLK^{\uparrow} \to RCLAV$ output delay time                       | <b>t</b> vcark | Load capacity = 50 pF | 1               |      | 19              | ns   |

|   | $RCLK^{\uparrow} \to RCLAV$ data float delay time                   | <b>t</b> icark | Load capacity = 50 pF | 1               |      | 25              | ns   |

| * | $RCLK^{\uparrow} \to RDO0\text{-}7^{\uparrow\downarrow}$ delay time | <b>t</b> ddork | Load capacity = 50 pF | 1               |      | 19              | ns   |

|   | $RCLK^\uparrow  ightarrow RDO0-7$ output delay time                 | <b>t</b> vdork | Load capacity = 50 pF | 1               |      | 19              | ns   |

|   | $RCLK^\uparrow \to RDO0\text{-7}$ data float delay time             | <b>t</b> idork | Load capacity = 50 pF | 1               |      | 25              | ns   |

| * | $RCLK^{\uparrow} \to RSOC^{\uparrow\downarrow} \text{ delay time}$  | <b>t</b> dsork | Load capacity = 50 pF | 1               |      | 19              | ns   |

|   | $RCLK^\uparrow \to RSOC$ output delay time                          | <b>t</b> vsork | Load capacity = 50 pF | 1               |      | 19              | ns   |

|   | $RCLK^{\uparrow} \to RSOC$ data float delay time                    | <b>t</b> ISORK | Load capacity = 50 pF | 1               |      | 25              | ns   |

|   | RADD0-7 setup time (to RCLK <sup>↑</sup> )                          | <b>t</b> SADRK |                       | 4               |      |                 | ns   |

|   | RADD0-7 hold time (to RCLK↑)                                        | <b>t</b> HADRK |                       | 1               |      |                 | ns   |

|   | RENBL_B setup time (to RCLK <sup>↑</sup> )                          | <b>t</b> senrk |                       | 4               |      |                 | ns   |

|   | RENBL_B hold time (to RCLK <sup>↑</sup> )                           | <b>t</b> HENRK |                       | 1               |      |                 | ns   |

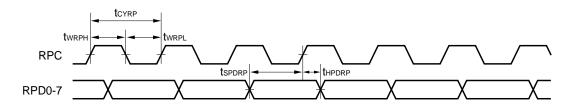

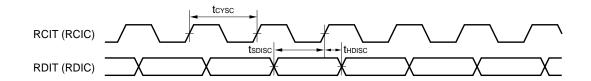

#### PMD parallel interface (receive side)

| Parameter                        | Symbol         | Condition | MIN.                 | TYP. | MAX.                 | Unit |

|----------------------------------|----------------|-----------|----------------------|------|----------------------|------|

| RPC cycle time                   | tcyrp          |           | 50                   |      |                      | ns   |

| RPC high level width             | twrph          |           | $0.4 	imes t_{CYRP}$ |      | $0.6 	imes t_{CYRP}$ | ns   |

| RPC low level width              | twrpl          |           | $0.4 	imes t_{CYRP}$ |      | $0.6 	imes t_{CYRP}$ | ns   |

| RPD0 - RPD7 setup time (to RPC↑) | <b>t</b> SPDRP |           | 10                   |      |                      | ns   |

| RPD0 - RPD7 hold time (to RPC↑)  | <b>t</b> HPDRP |           | 5                    |      |                      | ns   |

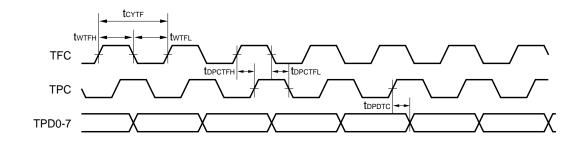

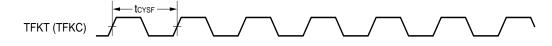

#### PMD parallel interface (transmit side)

| Parameter                                                       | Symbol          | Condition             | MIN.                         | TYP. | MAX.                         | Unit |

|-----------------------------------------------------------------|-----------------|-----------------------|------------------------------|------|------------------------------|------|

| TFC cycle time                                                  | <b>t</b> CYTF   |                       | 50                           |      |                              | ns   |

| TFC high level width                                            | <b>t</b> wtfh   |                       | $0.4 \times t_{\text{CYTF}}$ |      | $0.6 \times t_{\text{CYTF}}$ | ns   |

| TFC low level width                                             | <b>t</b> wtfl   |                       | $0.4 \times t_{\text{CYTF}}$ |      | $0.6 \times t_{\text{CYTF}}$ | ns   |