# YAMAHA'L 5 1

# **YSS220**

## (SP3) Surround Processor 3

#### ■ OUTLINE

YSS220(SP3) is an LSI which has surround capability by digital audio technology. The LSI has built-in A/D, D/A converters which enable digital sound processing for analog signals. With a 256k pseudo SRAM or SRAM connected, the LSI can process digital delay up to 512ms.

#### ■ FEATURES

- Built-in 15-bit floating ADC (L, R 2 channels) and DAC (FL, FR, RL, RR4 channels) enable digital processing for analog signals with 32kHz internal sampling frequency.

- 4 channels except center output can output digital signals as well. With a DAC connected externally, it will be possible with up to 5 channels (FL, C, FR, RL, RR).

- Hi-performance surround by mixing many echoes with using up to 512ms digital delay.

- Preset mode for easy control by terminal setting.

- Register control mode where it is possible to set various coefficients using microprocessor serial interface for original sound processing.

- Internal DSP is a 24-bit × 13-bit high speed multiplier with 128 steps.

- One 256k (32k x 8) pseudo SRAM or SRAM to be connected.

- 12.288MHz (384fs) master clock.

- 5V single power supply, Si-gate CMOS process.

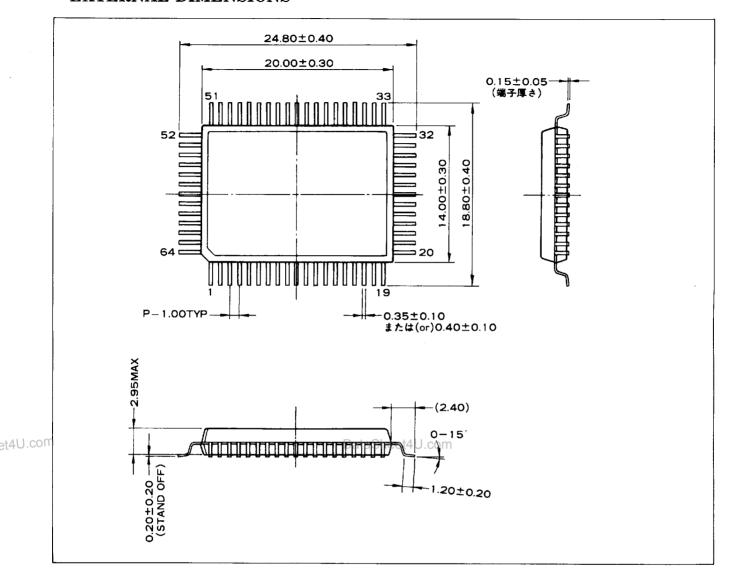

- 64-pin plastic QFP(YSS220-F)

Note: Due to the nature of the product, the preset data cannot be disclosed although partially.

DataShe

YAMAHA CORPORATION:

YSS220 CATALOG CATALOG No.: LSI-4SS2202

1993.11

www.DataSheet4U.com

DataSheet/II.com

DataShe

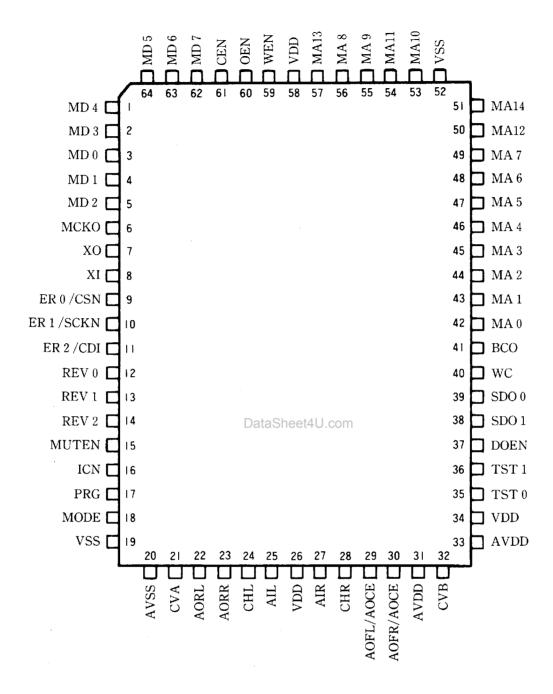

#### ■ PIN DESCRIPTION

<64pin QFP Top View>

2

et4U.com

## **YSS220**

| No. | Name      | I/O           | Description                                       |                            |  |  |  |

|-----|-----------|---------------|---------------------------------------------------|----------------------------|--|--|--|

| 1   | MD4       | I/O           | External RAM interface data terminal              |                            |  |  |  |

| 2   | MD3       | I/O           | External RAM interface data terminal              |                            |  |  |  |

| 3   | MD0       | I/O           | External RAM interface data terminal              |                            |  |  |  |

| 4   | MD1       | I/O           | External RAM interface data terminal              |                            |  |  |  |

| 5   | MD2       | I/O           | External RAM interface data terminal              |                            |  |  |  |

| 6   | мско      | 0             | DOEN='L': Master clock output (12.                | 288MHz)                    |  |  |  |

|     |           |               | DOEN='H': Fixed to 'L'                            |                            |  |  |  |

| 7   | xo        | O             | X'tal oscillator terminal                         |                            |  |  |  |

| 8   | XI        | I             | X'tal oscillator terminal or external clo         | ock input(12.288MHz)       |  |  |  |

|     |           |               | MODE = 'H' $MODE = 'L'$                           |                            |  |  |  |

| 9   | ER0/CSN   | I + s         | ER0 : E/R preset select 0                         | CSN: CPU I/F chip select   |  |  |  |

| 10  | ER1/SCKN  | I + s         | ER1 : E/R preset select 1                         | SCKN: CPU I/F serial clock |  |  |  |

| 11  | ER2/CDI   | I + s         | ER2: E/R preset select 2                          | CDI: CPU I/F serial data   |  |  |  |

| 12  | REV0      | I +           | Reverbration preset select 0                      |                            |  |  |  |

| 13  | REV1      | I +           | Reverbration preset select 1                      |                            |  |  |  |

| 14  | REV2      | I +           | Reverbration preset select 2                      |                            |  |  |  |

| 15  | MUTEN     | I +           | Output muting control (low-active)                |                            |  |  |  |

| 16  | ICN       | Is            | Initial clear input                               |                            |  |  |  |

| 17  | PRG       | I +           | DSP program select (available only when MODE='H') |                            |  |  |  |

|     |           |               | 'L': Mode 0, 'H': Mode 1                          | • •                        |  |  |  |

| 18  | MODE      | I +           | Operation mode select                             |                            |  |  |  |

|     |           |               | 'L': Register control mode, 'H': Pres             | set mode                   |  |  |  |

| 19  | VSS       | _             | Ground (digital block)Sheet4U.com                 |                            |  |  |  |

| 20  | AVSS      | $-\mathbf{A}$ | Ground (analog block)                             |                            |  |  |  |

| 21  | CVA       | - A           | L-ch ADC center voltage terminal                  |                            |  |  |  |

| 22  | AORL      | OA            | Rear L-ch DAC output                              |                            |  |  |  |

| 23  | AORR      | OA            | Rear R-ch DAC output                              |                            |  |  |  |

| 24  | CHL       | - A           | AIL input sample/hold capacitor terms             | inal                       |  |  |  |

| 25  | AIL       | IA            | L-ch ADC input                                    |                            |  |  |  |

| 26  | VDD       | _             | +5V power supply (digital block)                  |                            |  |  |  |

| 27  | AIR       | IA            | R-ch ADC input                                    |                            |  |  |  |

| 28  | CHR       | - A           | AIR input sample/hold capacitor term              | inal                       |  |  |  |

| 29  | AOFL/AOCE | OA            | DOEN='H': Front L-ch DAC output                   |                            |  |  |  |

|     |           |               | DOEN='L': C-ch DAC output                         |                            |  |  |  |

| 30  | AOFR/AOCE | OA            | DOEN = 'H': Front R-ch DAC output                 |                            |  |  |  |

|     |           |               | DOEN='L': C-ch DAC output                         |                            |  |  |  |

| 31  | AVDD      | - A           | +5V power supply (analog block)                   |                            |  |  |  |

| 32  | CVB       | - <b>A</b>    | R-ch, C-ch ADC center voltage termin              | al                         |  |  |  |

et4U.com

## **YSS220**

|          | No.  | Name | I/O | Description + 5V nower supply (analog block)    |              |  |  |

|----------|------|------|-----|-------------------------------------------------|--------------|--|--|

|          | 33   | AVDD | - A | +5V power supply (analog block)                 |              |  |  |

|          | 34   | VDD  | -   | +5V power supply (digital lock)                 |              |  |  |

|          | 35   | TST0 | I+  | LSI test terminal (Connect to VDD)              |              |  |  |

|          | 36   | TST1 | I+  | LSI test terminal (Connect to VDD)              |              |  |  |

|          | 37   | DOEN | I + | Digital signal output/Analog C-ch output enable |              |  |  |

|          |      |      |     | DOEN='L'                                        | DOEN='H'     |  |  |

|          | 38   | SDO1 | О   | Digital signal output rear channel (RL, RR)     | Fixed to 'L' |  |  |

|          | 39   | SDO0 | О   | Digital signal output front channel (FL, FR)    | Fixed to 'L' |  |  |

|          | 40   | wc   | О   | Digital signal output word clock fs             | Fixed to 'L' |  |  |

|          | 41   | BCO  | 0   | Digital signal output bit clock 64fs            | Fixed to 'H' |  |  |

|          | 42   | MA0  | 0   | ternal RAM interface address terminal           |              |  |  |

|          | 43   | MA1  | 0   | External RAM interface address terminal         |              |  |  |

|          | 44   | MA2  | О   | External RAM interface address terminal         |              |  |  |

|          | 45   | MA3  | О   | External RAM interface address terminal         |              |  |  |

|          | 46   | MA4  | О   | External RAM interface address terminal         |              |  |  |

|          | 47   | MA5  | О   | External RAM interface address terminal         |              |  |  |

|          | 48   | MA6  | О   | External RAM interface address terminal         |              |  |  |

|          | 49   | MA7  | О   | External RAM interface address terminal         |              |  |  |

|          | 50   | MA12 | О   | External RAM interface address terminal         |              |  |  |

|          | 51   | MA14 | О   | External RAM interface address terminal         |              |  |  |

|          | 52   | vss  | _   | Ground (digital block)                          |              |  |  |

|          | 53   | MA10 | О   | External RAM interface address terminal         |              |  |  |

| et4U.con | ր 54 | MA11 | 0   | External RAM interface address terminal         |              |  |  |

|          | 55   | MA9  | 0   | External RAM interface address terminal         |              |  |  |

|          | 56   | MA8  | О   | External RAM interface address terminal         |              |  |  |

|          | 57   | MA13 | О   | External RAM interface address terminal         |              |  |  |

|          | 58   | VDD  | _   | +5V power supply (digital block)                |              |  |  |

|          | 59   | WEN  | 0   | External RAM interface write enable terminal    |              |  |  |

|          | 60   | OEN  | О   | External RAM interface output enable terminal   |              |  |  |

|          | 61   | CEN  | О   | External RAM interface chip enable terminal     |              |  |  |

|          | 62   | MD7  | I/O | External RAM interface data terminal            |              |  |  |

|          | 63   | MD6  | I/O | External RAM interface data terminal            |              |  |  |

|          | 64   | MD5  | I/O | External RAM interface data terminal            |              |  |  |

NOTE) I+: Input terminal with a pull-up resister

IS: Schmitt input

A: analog terminal

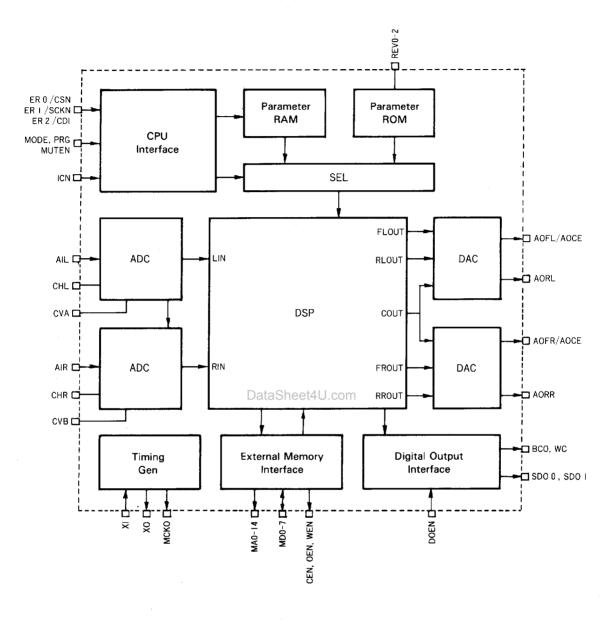

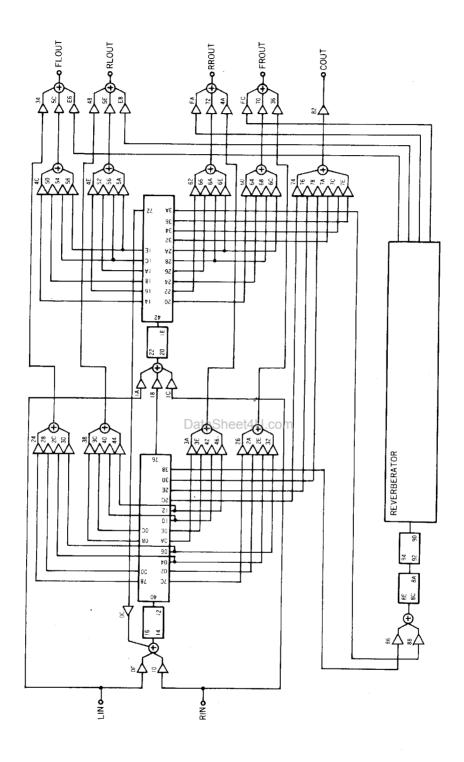

#### ■ BLOCK DIAGRAM

et4U.com

#### ■ FUNCTION DESCRIPTION

#### 1. Clocks XI, XO, MCKO

X'tal oscillation circuit is formed by using XI, XO terminals. The oscillation frequency is 12.288MHz (fs=32KHz).

When DOEN='L', master clock is output through MCKO terminal.

#### 2. ADCs and DACs AIL, AIR, CHL, CHR,

#### AOFL/AOCE, AORL, AOFR/AOCE, AORR, CVA, CVB

L, R audio signals are input to AIL, AIR terminals. External capacitors are required to CHL, CHR terminals for sample/hold. CVA, CVB are center voltage terminals of L and R channels ADCs. Connect capacitors for stability, and bias AIL, AIR terminals with these voltages, respectively. The AIL and AIR signal are DC-cut by internal HPF after A/D conversion. DAC sigals are output thorough AOFL/AOCE, AORL, AOFR/AOCE, AORR terminals. Connect

According to setting of DOEN terminal, outputs from the DACs are as follows:

capacitors for sample/hold, and buffer with a hi-impedance input for output.

| DOEN | MODE          | AOFL/ | AOFR/ | AORL  | AORR  | DIGITAL OUT      |

|------|---------------|-------|-------|-------|-------|------------------|

|      |               | AOCE  | AOCE  |       |       |                  |

| 'H'  | 4CHANNEL MODE | FLOUT | FROUT | RLOUT | RROUT | OFF              |

| L'   | 5CHANNEL MODE | COUT  | COUT  | RLOUT | RROUT | FL, FR, (RL, RR) |

4U.com

DataShe

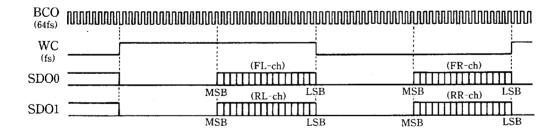

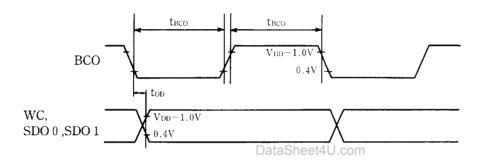

#### 3. Digital output DOEN, BCO, WC, SDO0, SDO1

Except center channel, each channel can also output digital data.

If digital output is required, set DOEN terminal to 'L'.

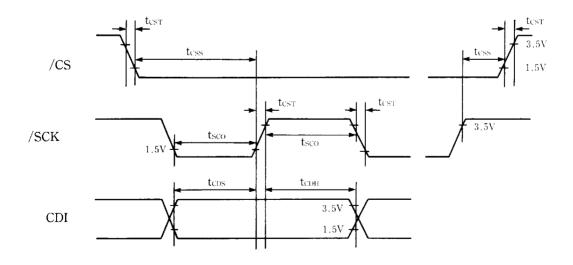

#### 4. Microprocessor interface

MODE, PRG, MUTEN

ERO/CSN, ER1/SCKN, ER2/CDI, REV0, REV1, REV2

LSI control method varies according to setting for MODE terminal.

(Each of ER0/CSN, ER1/SCKN, ER2/CDI terminals has different functions depending on its MODE setting and terminal names indicate both functions. In this section, however, only the name for the set mode is indicated.)

#### (1) Preset mode (MODE='H')

All control is done by terminal settings.

Use PRG terminal for program setting, ER0, ER1, ER2, REV0, REV1, REV2 terminals for preset selection.

In this mode, when MUTEN terminal is set to 'L', both DAC outputs and digital outputs are muted instantly.

(2) Register control mode (MODE='L')

All control is done by writing data to registers using microprocessor serial interface (using CSN, SCKN, CEDI terminals).

In this mode, REV0, REV1, REV2, MUTEN terminals are invaild.

#### 5. External RAM interface MAO~MA14, MD0~7, CEN, WEN, OEN

This LSI requires a 256K(32k\*8word) pseudo SRAM or SRAM.

#### 6. Initial clear

ICN, TST0, TST1

DataSheet4U.com

This LSI requires initial clear when the power is turned on. Set ICN terminal to 'L' for one sampling period or more. TST0, TST1 are LSI test terminals. Connect them to VDD.

et4U.com

www.DataSheet4U.com

YAMAHA

## **YSS220**

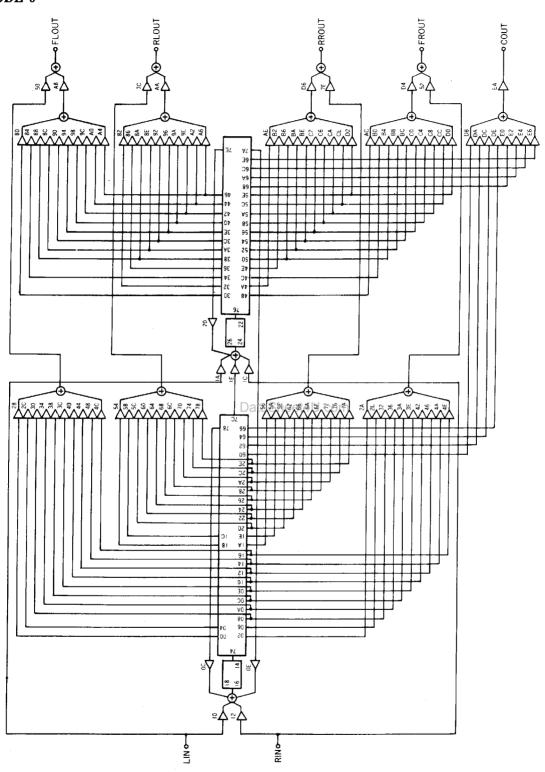

#### ■ DSP SIGNAL FLOW

#### 1. MODE 0

et4U.com

DataShe

8

#### 2. MODE 1

DataShe

9

et4U.com

MAMAYA

**YSS220**

#### 3. DSP signal flow description

#### • The number in the flow

In this flow, each number marked on the multiplier corresponds to the lower byte of the coefficient register address.

The number marked on delay tap (for discrimination, they are in different direction from those on the multiplier) corresponds to the lower byte of the memory pointer register addresses.

The box with 3 coefficent register addresses indicates the 1st order IIR filter.

#### • Processing blocks

The signal flow is devided into 3 processing blocks.

#### (1) VOL (VOLUME) block

This block consists of following attenuators immediately before output for each mode.

MODE 0: 0250H, 02A8H, 027CH, 02AAH, 02D6H, 027EH, 02D4H, 0252H and 02EAH

$\mathbf{MODE}\ 1:\ 0234H,\ 025CH,\ 02E6H,\ 0248H,\ 025EH,\ 02E8H,\ 02FAH,\ 0272H,\ 024AH,\ 02FCH,$

0270H, 0236H and 0282H

DataSheet4U.com

et4U.com

#### (2) REV (REVERBERATOR) block

This block is indicated as 'REVERBERATOR' in the Mode 1 signal flow diagram. Eight types of reverberator can be selected for this block by setting the terminal or OPR1.

This block uses momory addresses 1B80H-3FFFH for Preset #0-5 and 2590H-3FFFH for Preset #6 and 7.

#### (3) E/R (EARLY REFLECTION) block

This block consists of other parts of the signal flow than the above. For this block, it is possible to select 4 types of preset patterns in MODE 0 and 7 types in MODE 1 (by setting the terminal or OPR1) or all parameters can be set. In MODE 1, care should be used as the REV block uses a part of the memory as described above.

#### Registers not assigned in the flow

Do not write any data to the memory pointer registers and the coefficent registers which are not assigned in the flow.

10

#### ■ CONTROL DESCRIPTION

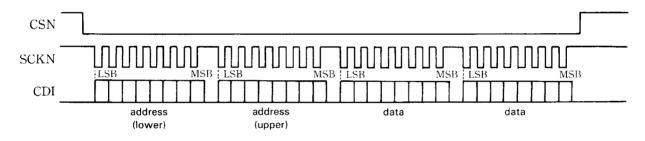

#### 1. Microprocessor interface

When in the register control mode (MODE='L'), function control and setting of DSP parameter are performed by writing data to the registers.

After setting the CSN terminal to 'L', send 2 bytes of the register addresses and then send the data, using SCKN and CDI terminals. As the register address where the data is written undergoes automatic increment at each sending of 1-byte data, the data is written in continuous addresses one after another only by sending them.

#### a) When address is 0000H or 0001H.

#### b) When address is 0100H or more.

et4U.com

#### .....

YAMAHA

#### 2. Register map

| Address<br>(HEX)  | Name            | Description                         |

|-------------------|-----------------|-------------------------------------|

| 0000              | OPR0            | Internal operation setting register |

| 0001              | OPR1            | Preset data selection register      |

| 0100<br>↓<br>017F | M00<br>↓<br>M7F | Memory pointer register             |

| 0200<br>↓<br>02FF | C00<br>↓<br>CFF | Coefficent register                 |

#### (Note)

- \* Do not write data in the other addresses.

- \* Data is not fixed when initial clear (except OPR0).

#### 3. Data setting

#### (1)OPR0

b0 (LSB)

: Output muting ('1'=Muted)

**b**1

: Program select ('0'=Mode 0, '1'=Mode 1)

b2

: "VOL block" preset mode selection ('1'=preset)

b3

: "E/R block" preset mode selection ('1'=preset)

b4-b7 (MSB)

: Set to '0' at all times.

#### (2)OPR1

b0 (LSB), b1, b2

: "E/R block" preset pattern selection

(Preset # = b2\*4 + b1\*2 + b0) ...com

**b**3

et4U.com

: Don't care.

b4, b5, b6

: "REV block" preset pattern selection (Mode 1 only)

(Preset # = b6\*4 + b5\*2 + b4)

b7 (MSB)

: don't care.

#### < Preset patterns>

|        | E/R Preset# | Guide name | REV Preset # | Rev. time  |

|--------|-------------|------------|--------------|------------|

| Mode 0 | 0           | Hall 1     |              |            |

|        | 1           | Hall 2     | Fix to 0     |            |

|        | 2           | Stadium    |              |            |

|        | 3           | Disco 1    |              |            |

| Mode 1 | 0           | Hall 3     | 0            | Hall 1.0S  |

|        | 1           | Hall 4     | 1            | Hall 1.5S  |

|        | 2           | Church 1   | 2            | Hall 2.0s  |

|        | 3           | Church 2   | 3            | Hall 2.5s  |

|        | 4           | Plate      | 4            | Hall 3.0s  |

|        | 5           | Disco 2    | 5            | Hall 3.5s  |

|        | 6           | ≪Mute≫     | 6            | Plate 1.5s |

|        | 7           | (INHIBIT)  | 7            | Plate 2.5s |

12

**YSS220**

YAMAHA

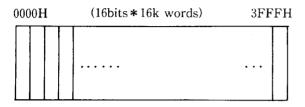

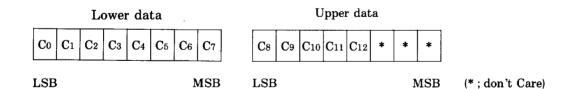

$(3)M00 \sim M7F$

These registers control the delay time by setting read and write addresses of the external RAM. The upper byte of the memory pointer register address is defined by 01H and the data written in that address and the next one becomes the access pointer of the memory map as shown below. The lower byte of the memory pointer register address corresponds to the number marked on the delay tap in the DSP signal flow diagram.

The access pointers are defined by 2-byte and available between 0000H and 3FFFH.

The audio data is written in the memory address indicated by the write pointer and read from the address indicated by the read poiner. The data in the memory shifts to the next address for every sample time.

Therefore, the difference between the wirte pointer and the read pointer is defined as delay time and obtained by using the following equation where the sampling frequency is 32KHz.

Delay time=[Read pointer-Write pointer] × (1/32000) [S]

DataSheet4LLcom

DataShe

$(4)C00 \sim CFF$

et4U.com

These registers determine coefficents of the internal multiplier.

The lower byte coefficent register address is defined by 02H and the data written in that address and the next one becomes the coefficent value according to the data assignments as shown below. The lower byte of the coefficent register address corresponds to the number marked on the multiplier in the DSP signal flow diagram.

The coefficient value of the attenuator is 13-bit, 2's complement:

(Coefficient value) =

$$(-1) \times C_{12} + \sum_{N=0}^{11} C_n \times 2^{n-12}$$

13

www.DataSheet4U.com

**YSS220**

#### 4. Terminal control

When in the preset mode (MODE = 'H'), function control and setting of DSP parameter are performed by setting terminals.

| Terminal             | Function                                                                            | Description                                                                                |

|----------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| PRG                  | DSP mode selection                                                                  | 'L': Mode 0<br>'H': Mode 1                                                                 |

| ER0<br>ER1<br>ER2    | E/R Preset selection                                                                | Preset # = ER2*4 + ER1*2 + ER0<br>(0='L', 1='H')<br>Refer to < Preset Patterns > table.    |

| REV0<br>REV1<br>REV2 | REV preset selection (Available only when in Mode 1. Fix all to 'L' when in Mode 0) | Preset # = REV2*4 + REV1*2 + REV0<br>(0='L', 1='H')<br>Refer to < Preset Patterns > table. |

| MUTEN                | Output Muting                                                                       | 'L': Muting                                                                                |

et4U.com

DataSheet4U.com

#### ■ ELECTRICAL CHARACTERISTICS

#### 1. Absolute maximum ratings

| Parameter             | Symbol | Rating                   | Unit |

|-----------------------|--------|--------------------------|------|

| Power supply voltage  | VDD    | -0.3 ~ 7.0               | V    |

| Input voltage         | Vı     | $-0.3 \sim V_{DD} + 0.5$ | V    |

| Operating temperature | Тор    | <b>-40∼85</b>            | °C   |

| Storage temperature   | Tstg   | -50~125                  | °C   |

#### 2. Recommended Operating Conditions

| Parameter             | Symbol                     | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------|------|------|------|------|

| Power supply voltage  | $\mathbf{V}_{\mathrm{DD}}$ | 4.5  | 5.0  | 5.5  | V    |

| Operating temperature | Тор                        | 0    | 25   | 70   | °C   |

#### 3. DC Characteristics

| Parameter                  | Symbol | Condition        | Min.    | Тур. | Max. | Unit    |

|----------------------------|--------|------------------|---------|------|------|---------|

| Power supply current       | W      | VDD=5.0V         |         |      | 225  | mW      |

| Input voltage H level (1)  | VIH1   | *1               | 2.2     |      |      | V       |

| Input voltage L level (1)  | VIL1   | *1               |         |      | 0.8  | v       |

| Input voltage H level (2)  | VIH2   | *2               | 3.5     |      |      | V       |

| Input voltage L level (2)  | VIL2   | *2               |         |      | 1.5  | V       |

| Input voltage H level (3)  | VIH3   | *3 DataSheet4U.  | 3.5     |      |      | V       |

| Input voltage L level (3)  | VIL3   | *3               | 00111   |      | 0.8  | V       |

| Input leakage current      | VLI    |                  |         |      | 10   | $\mu A$ |

| Input capacitance          | CI     |                  |         |      | 10   | рF      |

| Input capacitance          | Co     |                  |         |      | 10   | рF      |

| Output voltage H level (1) | Vol    | IoL=0.4mA, *4    | VDD-1.0 |      |      | V       |

| Output voltage L level (1) | Vон    | IOH = -1.6mA, *4 |         |      | 0.4  | V       |

| Output voltage H level (2) | Vol    | IOL=0.4mA, *5    | VDD-1.0 |      |      | V       |

| Output voltage L level (2) | Voн    | IOH = -1.6mA, *5 |         |      | 1.0  | V       |

<sup>\*1)</sup> Applicable to MD0  $\sim$  MD7 terminals.

DataShe

et4U.com

<sup>\*2)</sup> Applicable to input terminals other than XI terminal.

<sup>\*3)</sup> Applicable to XI terminal.

<sup>\*4)</sup> Applicable to output terminals other than XO terminal.

<sup>\*5)</sup> Applicable to XO terminal.

## **YSS220**

#### 4. AC Characteristics

| Parameter      |                 | Symbol | Min.    | Тур.   | Max.    | Unit |

|----------------|-----------------|--------|---------|--------|---------|------|

| XI             | frequency       | fxı    | 11.0    | 12.288 | 13.0    | MHz  |

| XI             | duty            | Dxı    |         | 50     |         | %    |

| BCO            | frequency       | fвс    |         | 64fx1  |         | Hz   |

| BCO            | ON/OFF time     | tBCO   | 180     |        |         | ns   |

| WC, SDO0, SDO1 | output delay    | ton    | - 40    |        | 40      | ns   |

| CSN            | setup time      | tcss   | 1/50fs  |        |         | s    |

| SCKN           | ON/OFF time     | tsco   | 1/50fs  |        |         | s    |

| CDI            | setup time      | tcds   | 1/100fs |        |         | s    |

| CDI            | hold time       | tсон   | 1/100fs |        |         | s    |

| CSN, SCKN      | Transition time | test   |         |        | 1/150fs | s    |

(Note) Load capacitance 30pF

et4U.com

## **YSS220**

#### 5. Analog Characteristics

| Parameter                     | Symbol    | Condition   | Min. | Typ. | Max. | Unit |

|-------------------------------|-----------|-------------|------|------|------|------|

| Analog input voltage          | VIA       | Amplitude   |      | 4.70 |      | V    |

| Analog output voltage         | VOA       | Amplitude   |      | 4.70 |      | V    |

| DC offset voltage             | Vc        |             |      | 2.5  |      | V    |

| Total harmonic distortion * 1 | THD+N (1) | 1kHz, 0dB   |      | 0.4  | 0.8  | %    |

|                               | THD+N (2) | 1kHz, -30dB |      | 0.6  | 1.2  | %    |

| Signal to noise ratio         | S/N       | S=0dB       | 80   | 85   |      | dΒ   |

<sup>\*1)</sup> LPF with fc=10kHz, 36dB/oct is used when OdB=4.70PP, A/D→D/A through.

et4U.com

DataSheet4U.com

<sup>\*2)</sup> IHF-A is used when OdB=4.70VPP, A/D $\rightarrow$ D/A through.

#### **EXTERNAL DIMENSIONS**

Note) The specifications of this product are subject to improvement changes without prior notice.

18

#### IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANYTHIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

et4U.com

DataShe

# AGENCY

#### YAMAHA CORPORATION

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Toyooka-mura, Iwata-gun, Shizuoka-ken, 438-0192

Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8568

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office Namba Tsujimoto Nissei Bldg. 4F

1-13-17, Namba Naka, Naniwa-ku, Osaka City, Osaka, 556-0011

Tel. +81-6-6633-3690 Fax. +81-6-6633-3691

■ U.S.A. Office YAMAHA Systems Technology

100 Century Center Court, San Jose, CA 95112

Tel. +1-408-467-2300 Fax. +1-408-437-8791

COPYING PROHIBITED © 1988 YAMAHA CORPORATION 0.71K 8705 Printed in Japan

www.DataSheet4U.com

# YAMAHA'L S I

### **APPLICATION NEWS**

No. : AN 079

Date of Issue: 1995. 8. 1

Device Name: YSS220 (SP3)

#### YAMAHA CORPORATION

Semi-conductor Sales Department Sales Engineering Section

#### YSS220 (SP3) MICROPROCESSOR INTERFACE

#### **ADDITIONAL SPECIFICATION**

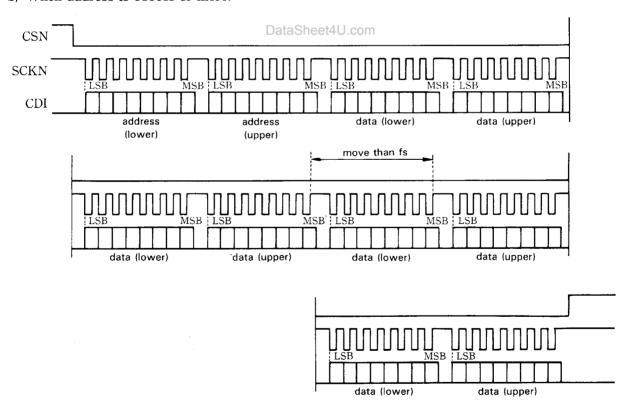

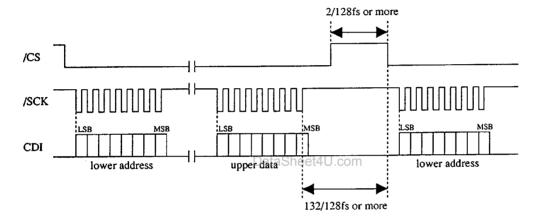

Data transmission to discontinuous address

When sending the data to the discontinuous address, it is necessary to set the timing as shown above.

et4U.com

DataSheet4U.com www.DataSheet4U.com