# **SPMC75F2413A**

## 16-bit MCU with Two Channels Motor Controller

Feb. 16, 2006

Version 1.1

Sunplus Innovation Technology reserves the right to change this documentation without prior notice. Information provided by Sunplus Innovation Technology is believed to be accurate and reliable. However, Sunplus Innovation Technology makes no warranty for any errors which may appear in this document. Contact Sunplus Innovation Technology to obtain the latest version of device specifications before placing your order. No responsibility is assumed by Sunplus Innovation Technology for any infringement of patent or other rights of third parties which may result from its use. In addition, SunplusIT products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the support devices/ systems written approval of SunplusIT.

### **Table of Contents**

#### PAGE

| 1. | GEN  | IERAL DESCRIPTION                                         | 7    |

|----|------|-----------------------------------------------------------|------|

| 2. | FEA  | TURES                                                     | 7    |

| 3. | BLC  | DCK DIAGRAM                                               | 8    |

| 4. | SIG  | NAL DESCRIPTIONS                                          | 9    |

|    | 4.1. | PIN DESCRIPTIONS                                          | 9    |

|    |      | 4.1.1. 80-Pin QFP/ 64-Pin QFP package signals description | 9    |

|    | 4.2. | PIN ASSIGNMENT                                            | 11   |

|    |      | 4.2.1. 80-Pin QFP Package                                 | 11   |

|    |      | 4.2.2. 64-Pin QFP Package                                 | . 12 |

| 5. | FUN  | ICTIONAL DESCRIPTIONS                                     | . 13 |

|    | 5.1. | CPU Core                                                  | . 13 |

|    | 5.2. | MEMORY ORGANIZATION                                       | . 13 |

|    |      | 5.2.1. Memory Map                                         | . 13 |

|    |      | 5.2.2. Flash Organization and Control                     | . 14 |

|    |      | 5.2.3. SRAM                                               | . 18 |

|    |      | 5.2.4. Reset and Interrupt Vectors                        | . 18 |

|    | 5.3. | CLOCK GENERATION MODULE (CGM)                             | . 32 |

|    |      | 5.3.1. Crystal Oscillator                                 | . 32 |

|    |      | 5.3.2. Phase-lock Loop (PLL)                              | . 32 |

|    |      | 5.3.3. External clock                                     | . 32 |

|    |      | 5.3.4. Clock Monitoring                                   | . 32 |

|    |      | 5.3.5. RC Oscillator                                      | . 34 |

|    | 5.4. | Power Saving Modes                                        | . 34 |

|    |      | 5.4.1. Wake-up Sources                                    | . 35 |

|    | 5.5. | INTERRUPT                                                 | . 37 |

|    |      | 5.5.1. Interrupt Source                                   | . 37 |

|    |      | 5.5.2. Interrupt procedure                                | . 39 |

|    | 5.6. | RESET MANAGEMENT                                          | .42  |

|    |      | 5.6.1. Power on reset (POR)                               |      |

|    |      | 5.6.2. External reset                                     | 42   |

|    |      | 5.6.3. Low voltage reset (LVR)                            | 43   |

|    |      | 5.6.4. Watchdog timer reset (WDTR)                        |      |

|    |      | 5.6.5. Illegal address reset (IAR)                        |      |

|    |      | 5.6.6. Illegal instruction reset (IIR)                    |      |

|    |      | GENERAL PURPOSE I/O PORTS (GPIO)                          |      |

|    |      | TIMER/PWM MODULE (TPM)                                    |      |

|    | 5.9. | PDC TIMER 0 AND 1                                         |      |

|    |      | 5.9.1. Module Introduction                                |      |

|    |      | 5.9.2. PDC Timer Counting Operation                       |      |

|    |      | 5.9.3. Phase Counting Mode Operation                      |      |

|    |      | 5.9.4. Position Detection Change (PDC) Mode Operation     | .77  |

|    | 5.10.TPM TIMER 2 MODULE                                                                    | 80  |

|----|--------------------------------------------------------------------------------------------|-----|

|    | 5.10.1. Introduction                                                                       | 80  |

|    | 5.10.2. TPM Timer 2 Counting Operation                                                     | 81  |

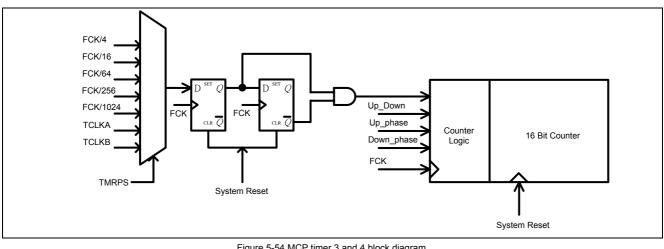

|    | 5.11. MCP TIMER 3 AND 4 MODULE                                                             | 95  |

|    | 5.11.1.Introduction                                                                        |     |

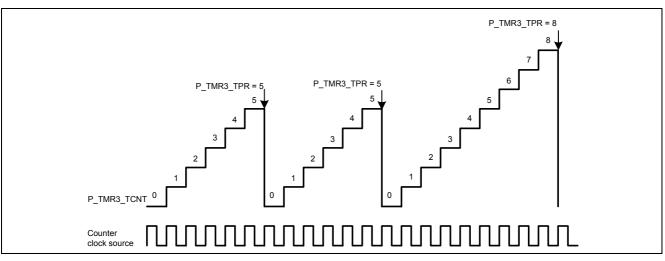

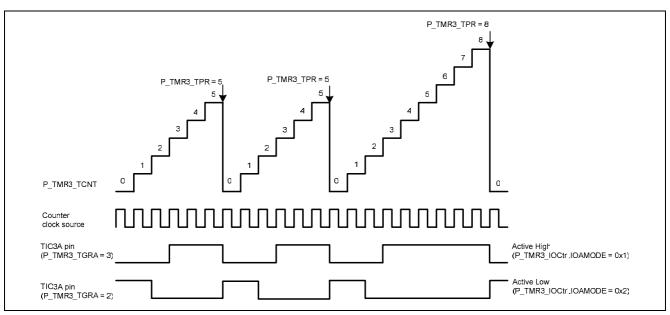

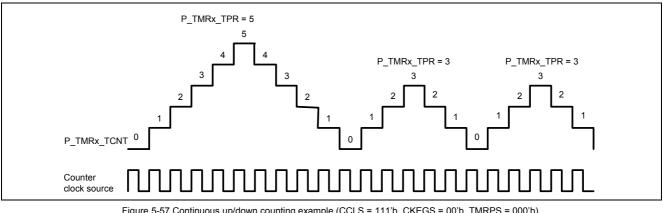

|    | 5.11.2.MCP Timer 3 and 4 Counting Operation                                                | 97  |

|    | 5.12.Compare Match Timer                                                                   | 119 |

|    | 5.13. TIME BASE MODULE                                                                     | 121 |

|    | 5.14.Serial Communication Interface                                                        | 122 |

|    | 5.14.1. SPI (Standard Peripheral Interface)                                                | 122 |

|    | 5.14.2. SPI Operation                                                                      | 123 |

|    | 5.14.3. UART (Universal Asynchronous Receiver/Transceiver)                                 | 127 |

|    | 5.14.4. UART Operation                                                                     | 127 |

|    | 5.15.ANALOG-TO-DIGITAL CONVERTER (ADC)                                                     | 132 |

|    | 5.16.WATCHDOG TIMER (WDT)                                                                  | 137 |

| 6. | 6. ELECTRICAL SPECIFICATIONS                                                               | 140 |

|    | 6.1. ABSOLUTE MAXIMUM RATINGS                                                              | 140 |

|    | 6.2. DC CHARACTERISTICS (VDD = 4.5~5.5V, T <sub>A</sub> = -40~85°C)                        | 140 |

|    | 6.3. AC CHARACTERISTICS (VDD = 4.5~5.5V, T <sub>A</sub> = -40~85°C)                        | 140 |

|    | 6.4. ANALOG INTERFACE ELECTRICAL CHARACTERISTICS (VDD = 5.0V, T <sub>A</sub> = -40°C~85°C) | 141 |

| 7. | 7. SPMC75F2413A EVM BOARD V1.1 SCHEMATIC                                                   |     |

| 8. | 3. PACKAGE/PAD LOCATIONS                                                                   | 145 |

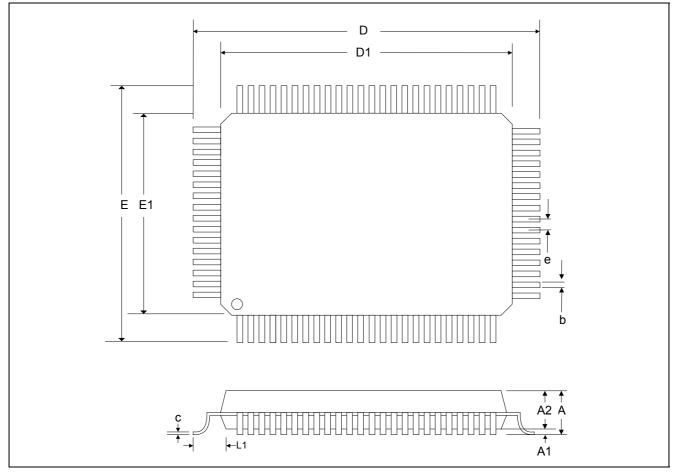

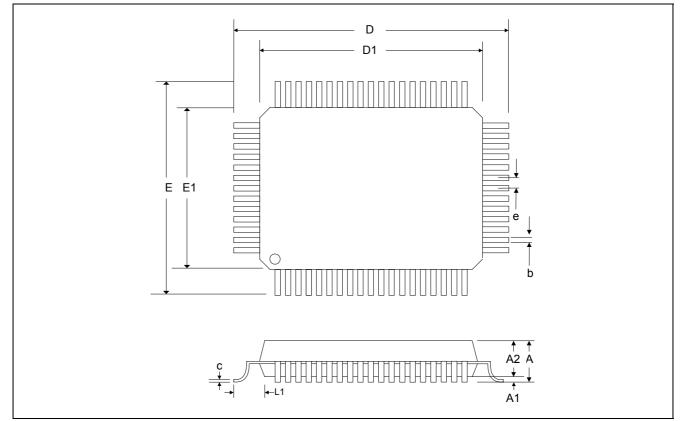

|    | 8.1. PACKAGE INFORMATION                                                                   | 145 |

|    | 8.1.1. 80 PIN QFP                                                                          | 145 |

|    | 8.1.2. 64 PIN QFP                                                                          | 146 |

|    | 8.2. Ordering Information                                                                  | 146 |

|    | 8.3. STORAGE CONDITION AND PERIOD FOR PACKAGE                                              | 147 |

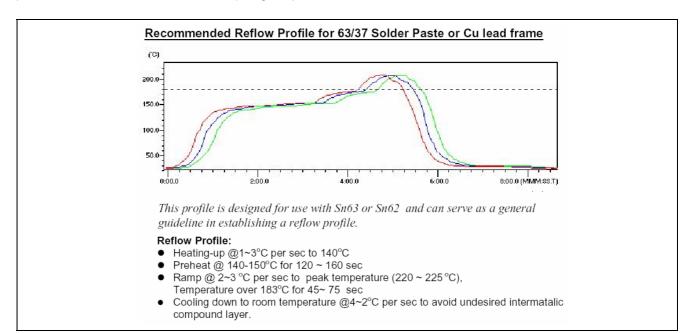

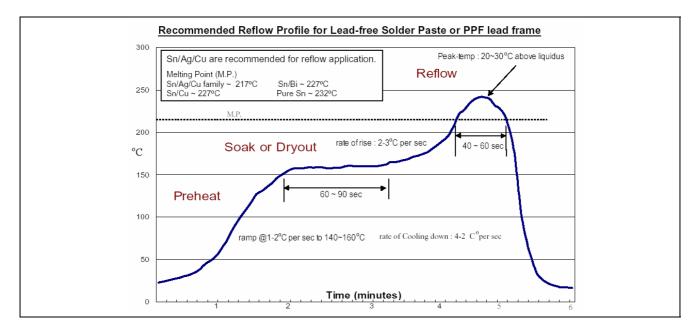

|    | 8.4. RECOMMENDED SMT TEMPERATURE PROFILE                                                   |     |

| 9. | ). DISCLAIMER                                                                              |     |

| 10 | 0. REVISION HISTORY                                                                        |     |

|    |                                                                                            |     |

### Figures

#### PAGE

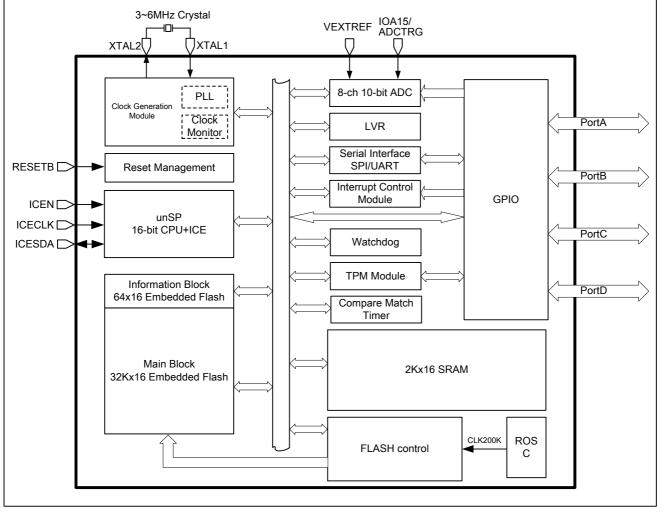

| Figure 3-1 SPMC75F2413A function block diagram                                                      | Q  |

|-----------------------------------------------------------------------------------------------------|----|

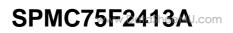

| Figure 4-1 SPMC75F2413A QFP80 package                                                               |    |

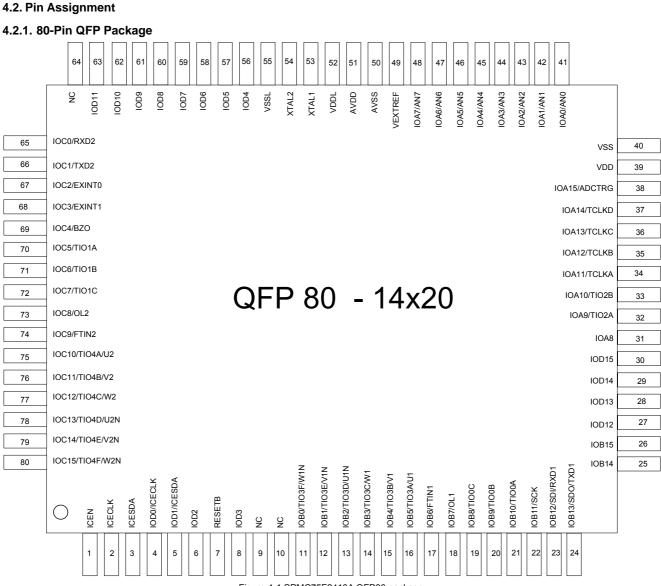

| Figure 4-2 SPMC75F2413A QFP64 package                                                               |    |

| Figure 5-1 Memory allocation                                                                        |    |

| Figure 5-2 Structure of Information block                                                           |    |

| Figure 5-2 Structure of finite information block                                                    |    |

| Figure 5-5 Pageo and name of hash                                                                   |    |

|                                                                                                     |    |

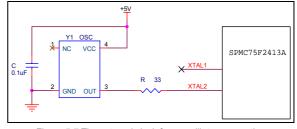

| Figure 5-5 The crystal circuit connection<br>Figure 5-6 PLL and external clock block diagram        |    |

|                                                                                                     |    |

| Figure 5-7 The external clock from oscillator connection                                            |    |

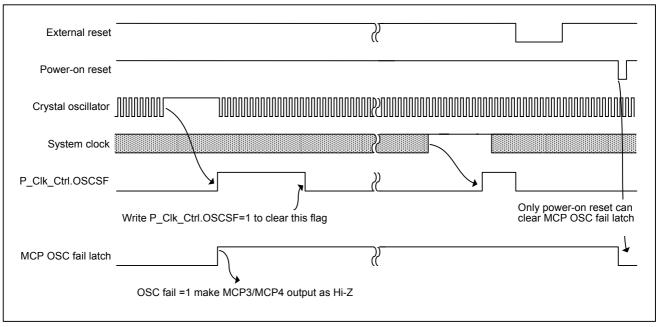

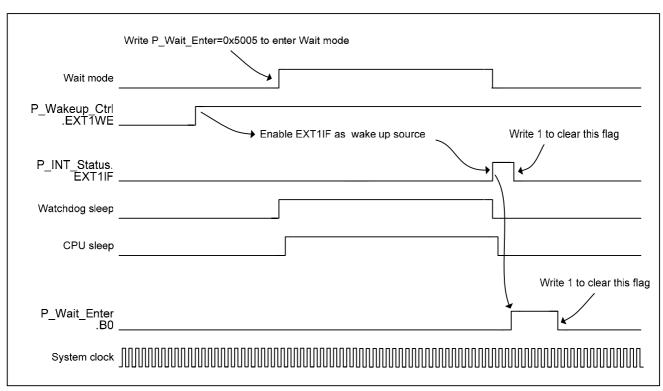

| Figure 5-8 Clock Fail timing<br>Figure 5-9 Wait mode timing                                         |    |

|                                                                                                     |    |

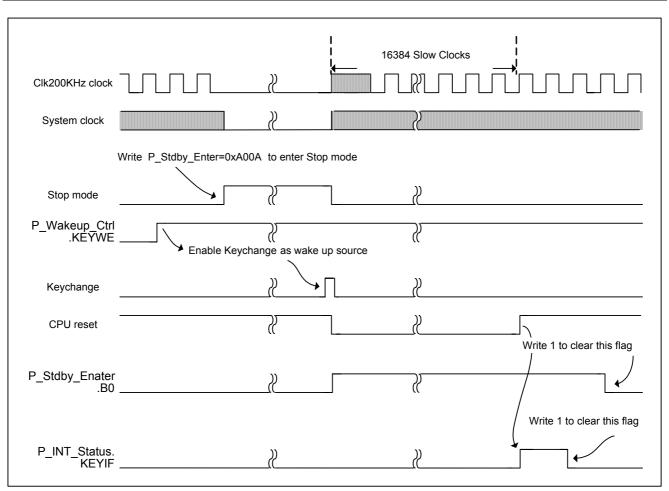

| Figure 5-10 Standby mode timing                                                                     |    |

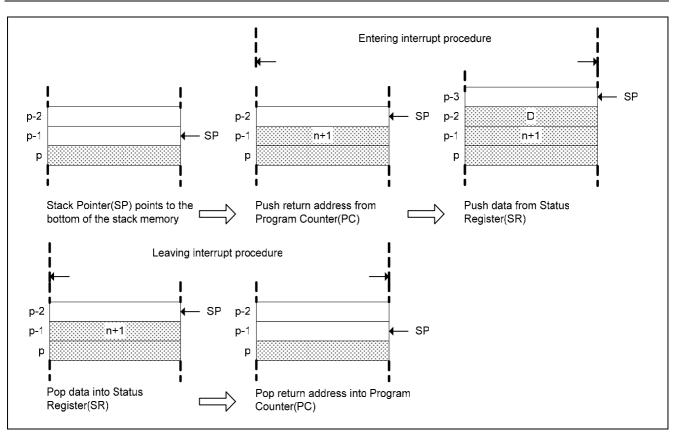

| Figure 5-11 Interrupt procedure timing                                                              |    |

| Figure 5-12 Stack memory operation with interrupt procedure                                         |    |

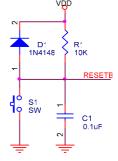

| Figure 5-13 External reset circuit                                                                  |    |

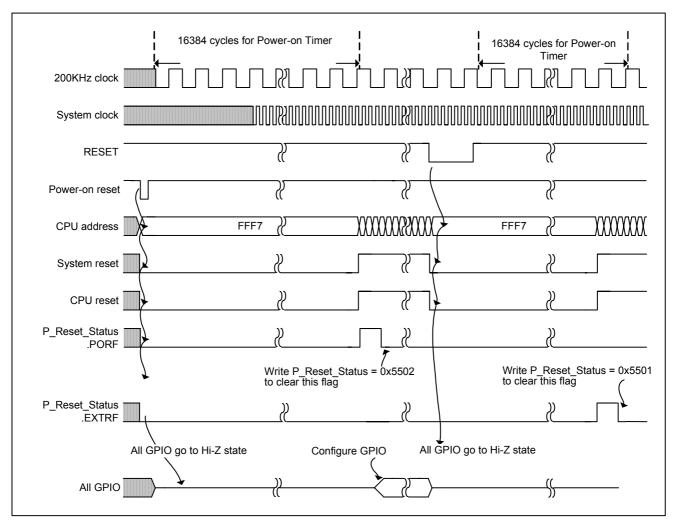

| Figure 5-14 Power-on reset, external reset and power-up timer timing                                |    |

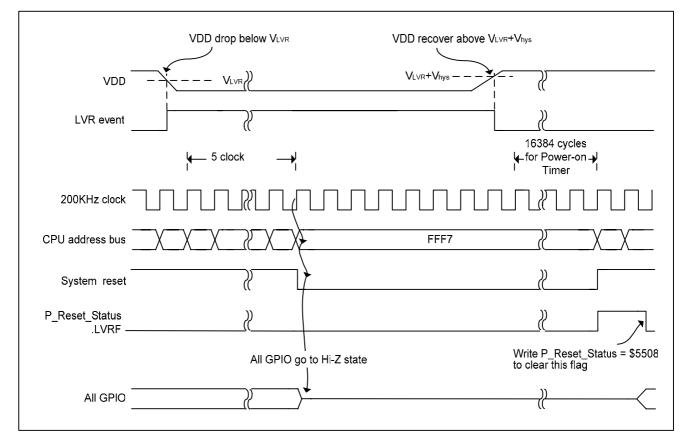

| Figure 5-15 Low voltage reset timing                                                                |    |

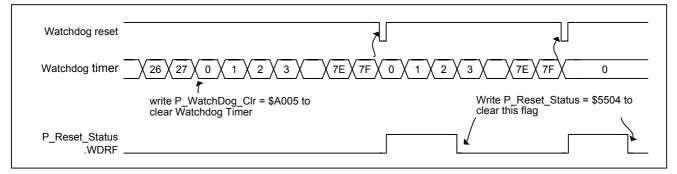

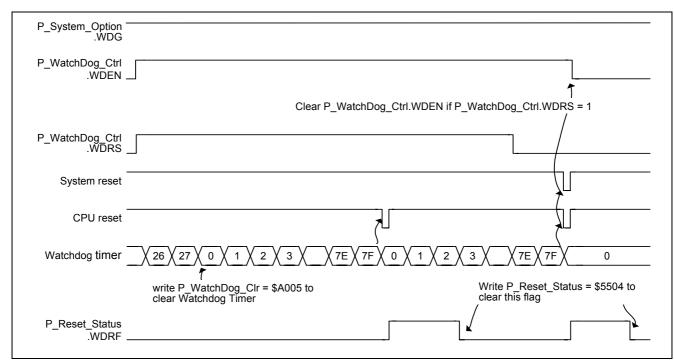

| Figure 5-16 Watchdog timer reset timing                                                             |    |

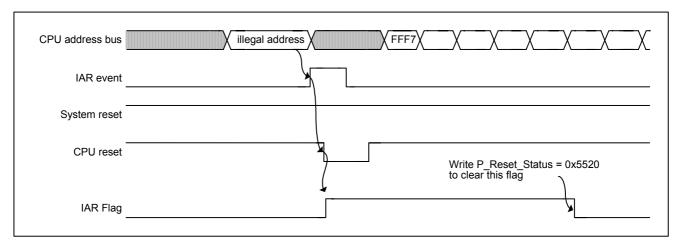

| Figure 5-17 Illegal address reset timing                                                            |    |

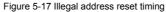

| Figure 5-18 Illegal instruction reset timing                                                        |    |

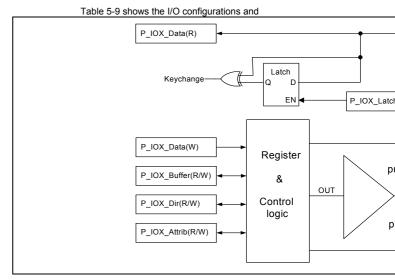

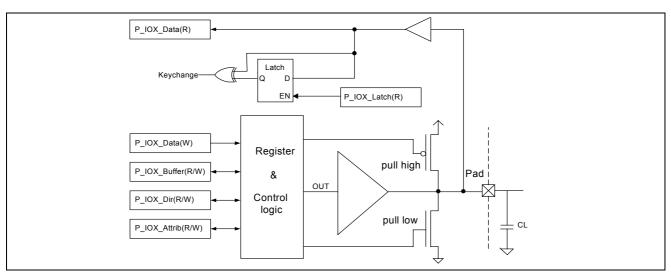

| Figure 5-19 IO structure diagram                                                                    |    |

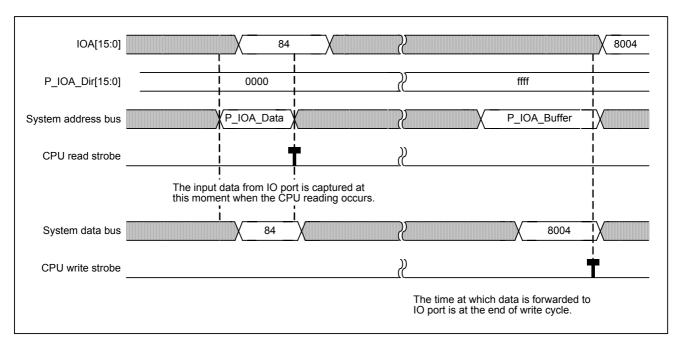

| Figure 5-20 GPIO input/output timing                                                                |    |

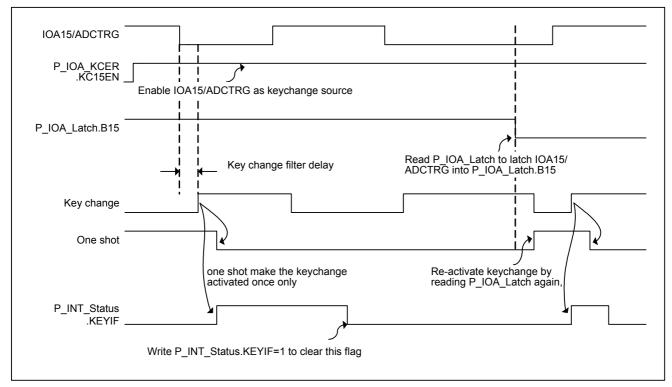

| Figure 5-21 Keychange timing                                                                        |    |

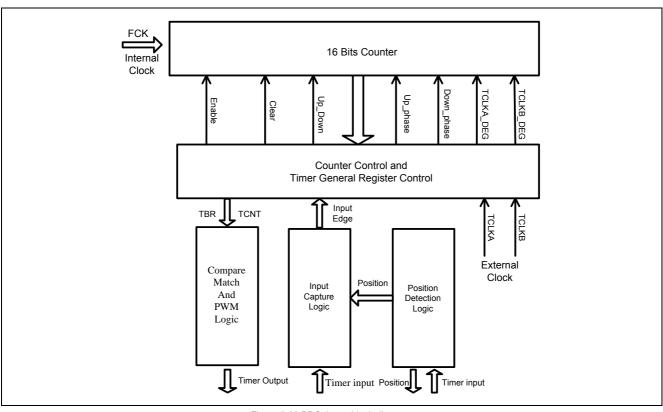

| Figure 5-22 PDC timers block diagram                                                                |    |

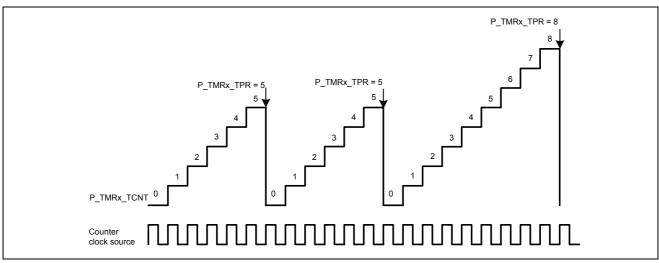

| Figure 5-23 Continuous up counting example (CCLS = 111'b, CKEGS = 00'b, TMRPS = 000'b)              |    |

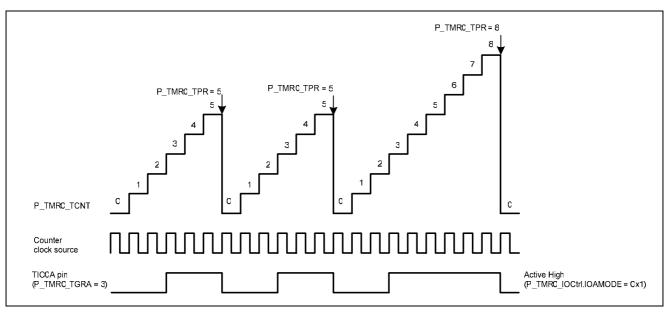

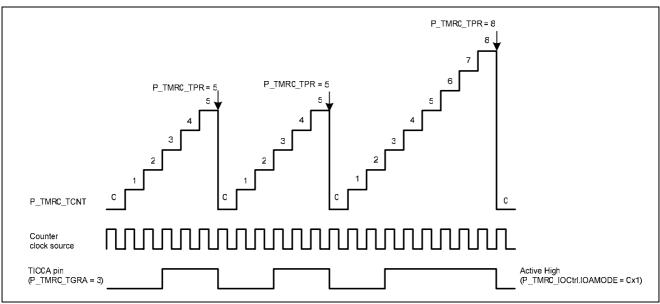

| Figure 5-24 shows the normal continuous up counting mode for edge-aligned PWM generation of timer 0 |    |

| Figure 5-25 Edge-Aligned mode PWM                                                                   |    |

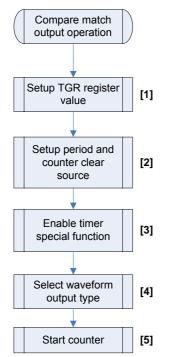

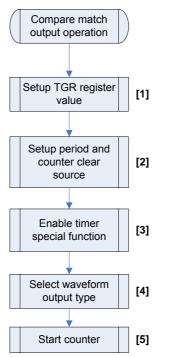

| Figure 5-26 Example programming flowchart of PWM compare match output operation                     |    |

| Figure 5-27 TMR0 edge aligned PWM                                                                   |    |

| Figure 5-28 Timer mode output timing                                                                |    |

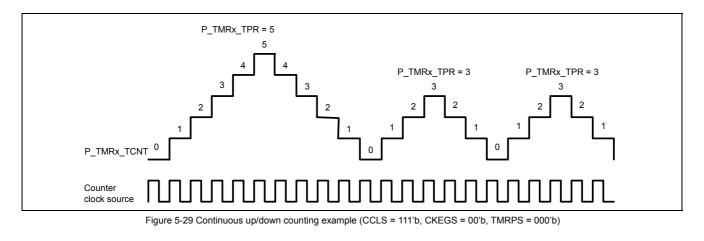

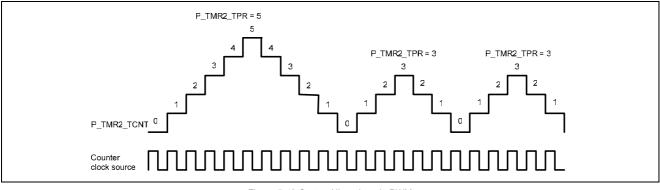

| Figure 5-29 Continuous up/down counting example (CCLS = 111'b, CKEGS = 00'b, TMRPS = 000'b)         | 63 |

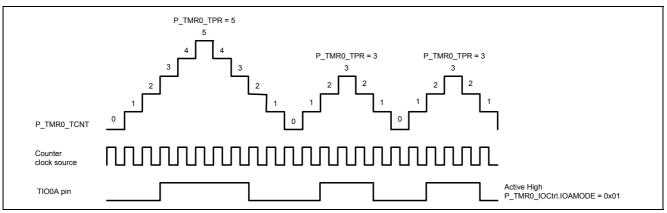

| Figure 5-30 Center-aligned mode PWM                                                                 |    |

| Figure 5-31 TMR0 center aligned PWM                                                                 |    |

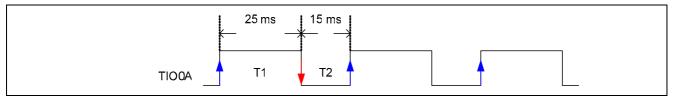

| Figure 5-32 input capture signal connected to TIO0A                                                 |    |

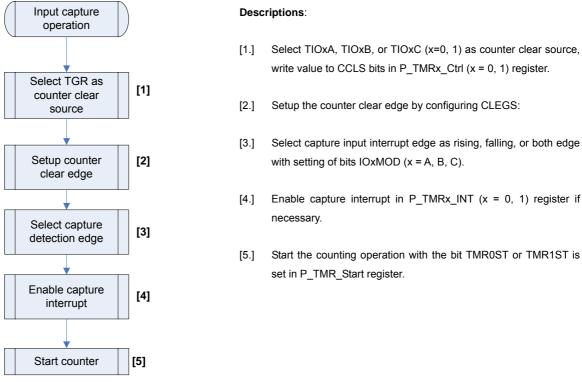

| Figure 5-33 Example programming flowchart of input capture operation                                |    |

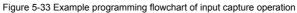

| Figure 5-34 Capture input signal width and cycle                                                    |    |

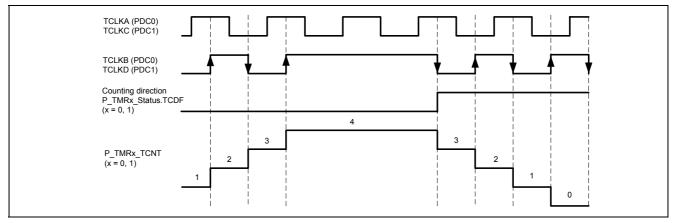

| Figure 5-35 phase counting mode 1                                                                   |    |

| Figure 5-36 phase counting mode 2                                                                   |    |

| Figure 5-37 phase counting mode 3                                                                   |    |

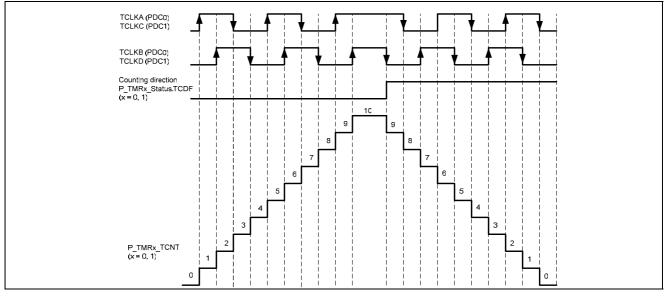

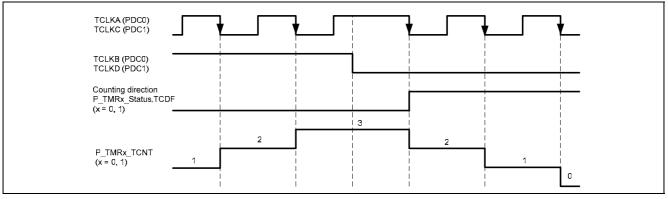

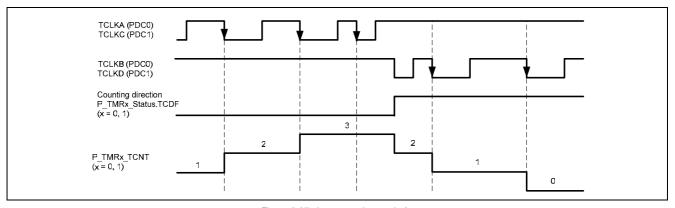

| Figure 5-38 phase counting mode 4                                                                   |    |

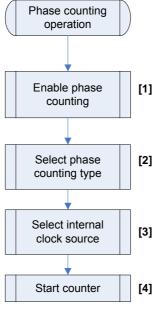

| Figure 5-39 Example programming flowchart of phase counting operation                               |    |

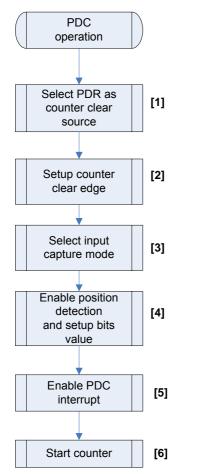

| Figure 5-40 Example programming flowchart of PDC operation                                          |    |

| Figure 5-41 Position detection with noise filter                                                    |    |

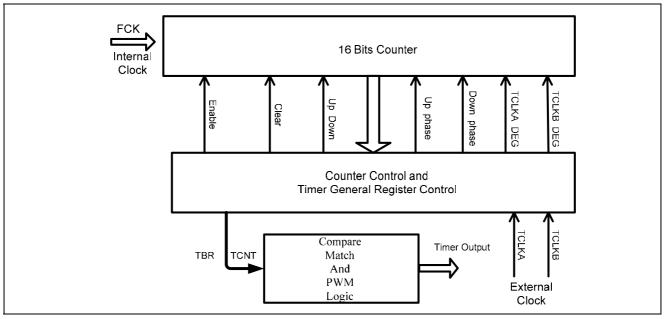

| Figure 5-42 TPM timer 2 block diagram                                                               |    |

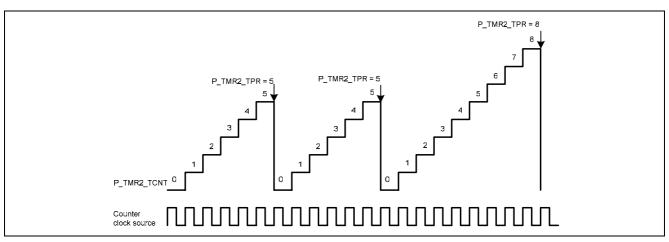

| Figure 5-43 Continuous up counting example (CCLS = 111'b, CKEGS = 00'b, TMRPS = 000'b)              | 82 |

| Figure 5-44 Edge-Aligned mode PWM                                                           | 82  |

|---------------------------------------------------------------------------------------------|-----|

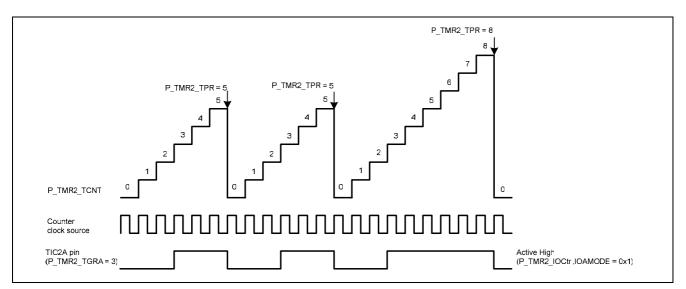

| Figure 5-45 Example programming flowchart of PWM compare match output operation             | 83  |

| Figure 5-46 TMR2 edge aligned PWM                                                           | 84  |

| Figure 5-47 Timer mode output timing                                                        | 85  |

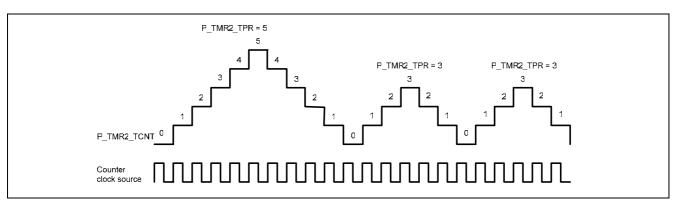

| Figure 5-48 Continuous up/down counting example (CCLS = 111'b, CKEGS = 00'b, TMRPS = 000'b) | 86  |

| Figure 5-49 Center-Aligned mode PWM                                                         | 86  |

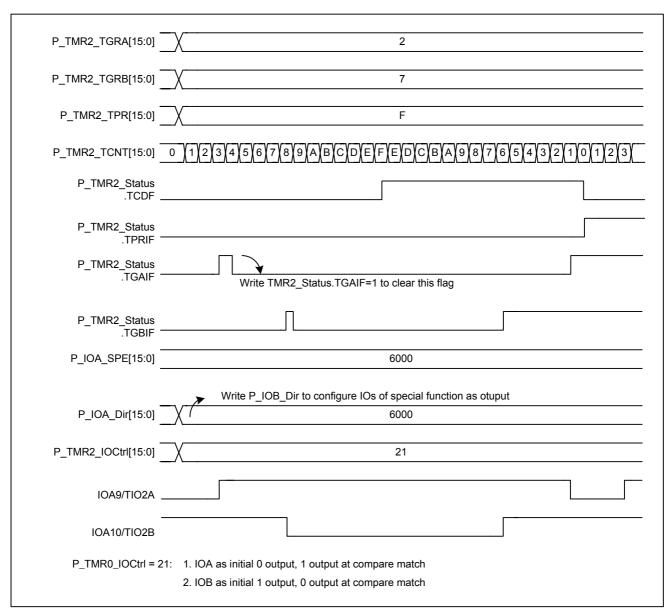

| Figure 5-50 TMR2 center aligned PWM                                                         | 87  |

| Figure 5-51 input capture signal connected to TIO2A                                         | 88  |

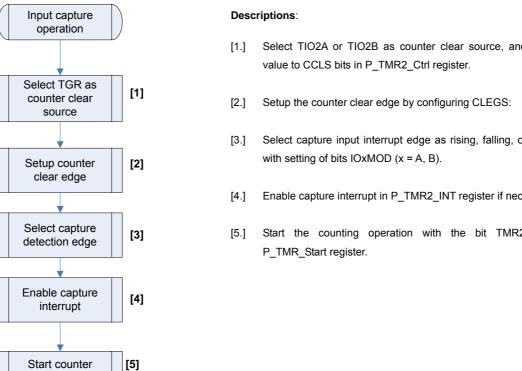

| Figure 5-52 Example programming flowchart of input capture operation                        | 89  |

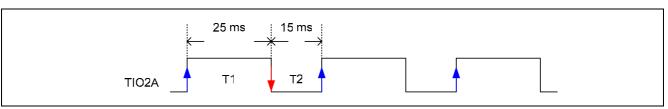

| Figure 5-53 Capture input signal width and cycle                                            | 90  |

| Figure 5-54 MCP timer 3 and 4 block diagram                                                 | 95  |

| Figure 5-55 Continuous up counting example (CCLS = 111'b, CKEGS = 00'b, TMRPS = 000'b)      | 97  |

| Figure 5-56 Edge-Aligned mode PWM                                                           | 98  |

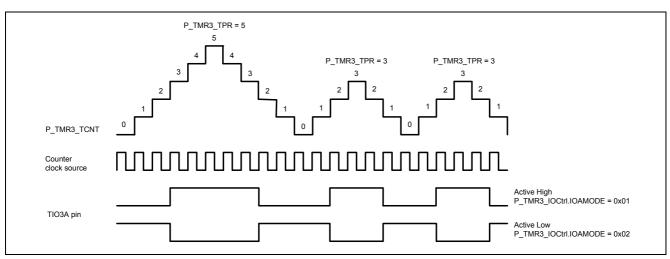

| Figure 5-57 Continuous up/down counting example (CCLS = 111'b, CKEGS = 00'b, TMRPS = 000'b) | 98  |

| Figure 5-58 Center-Aligned mode PWM                                                         | 99  |

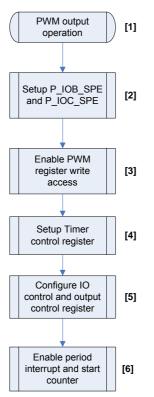

| Figure 5-59 Example programming flowchart of PWM operation                                  | 106 |

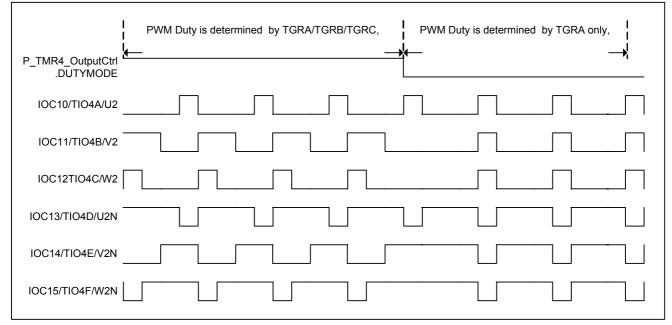

| Figure 5-60 PWM output timing with different duty mode selection                            | 107 |

| Figure 5-61 Output polarity timing                                                          | 108 |

| Figure 5-62 PWM Sync mode                                                                   | 109 |

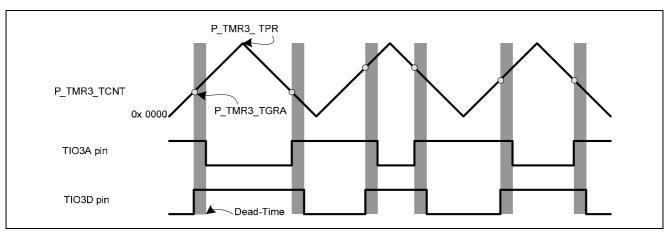

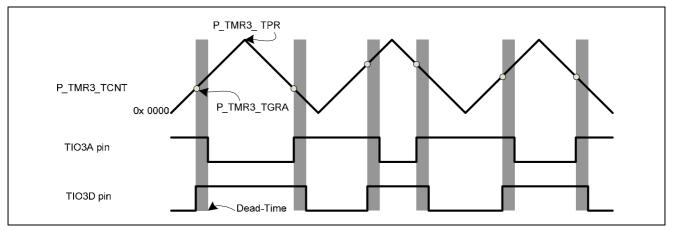

| Figure 5-63 shows the center-aligned complementary PWM with dead time inserted of timer 3   | 111 |

| Figure 5-64 Active-low PWM mode of dead-time generation                                     | 111 |

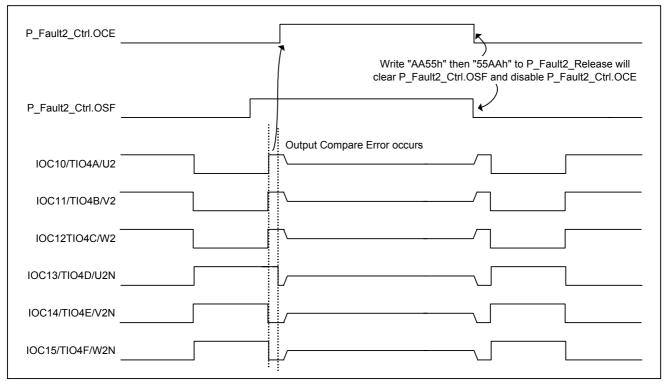

| Figure 5-65 Fault error timing                                                              | 113 |

| Figure 5-66 Output compare error                                                            | 113 |

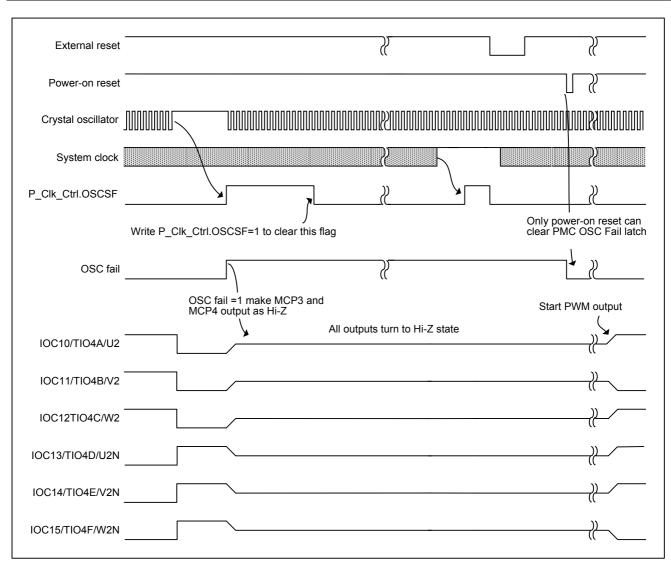

| Figure 5-67 Oscillator stopped timing                                                       | 114 |

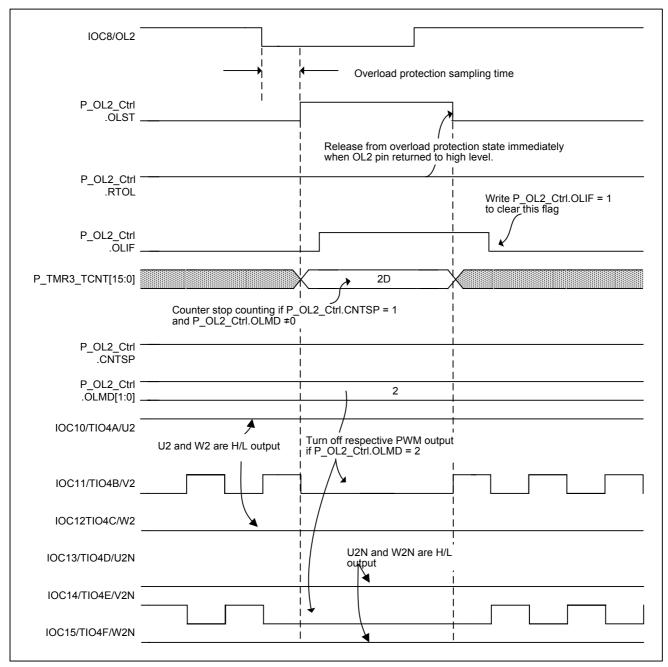

| Figure 5-68 Stop PWM output only when overload occurs                                       | 116 |

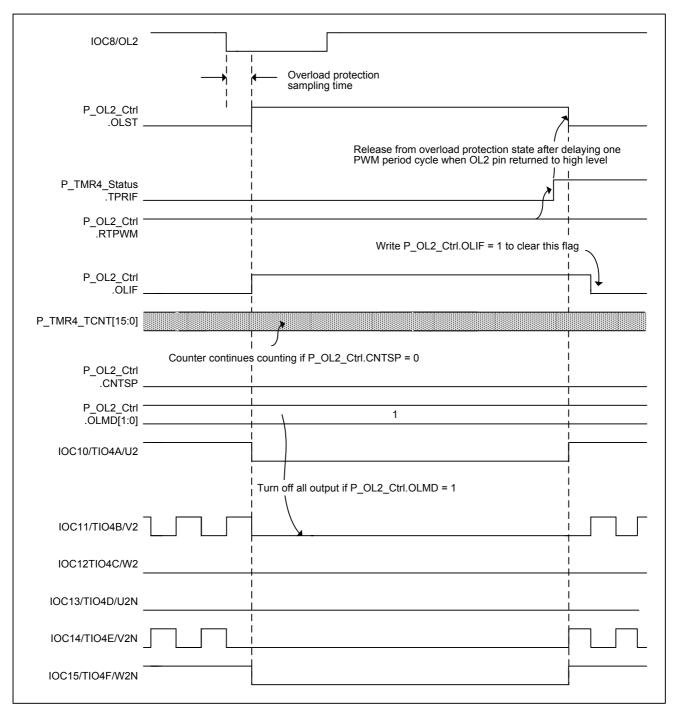

| Figure 5-69 Stop all output when overload occurs                                            | 117 |

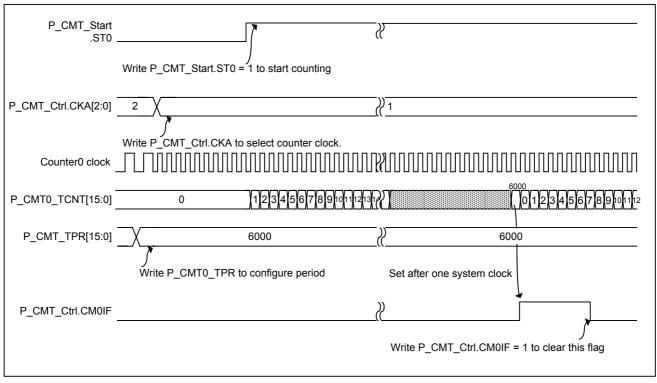

| Figure 5-70 CMT timing                                                                      | 119 |

| Figure 5-71 Timebase and buzzer output timing                                               | 121 |

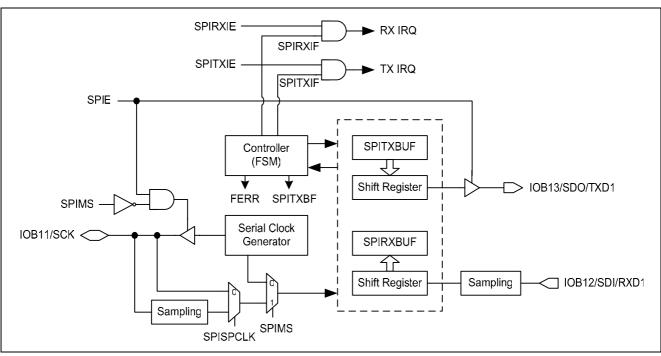

| Figure 5-72 Function block diagram of SPI interface                                         | 123 |

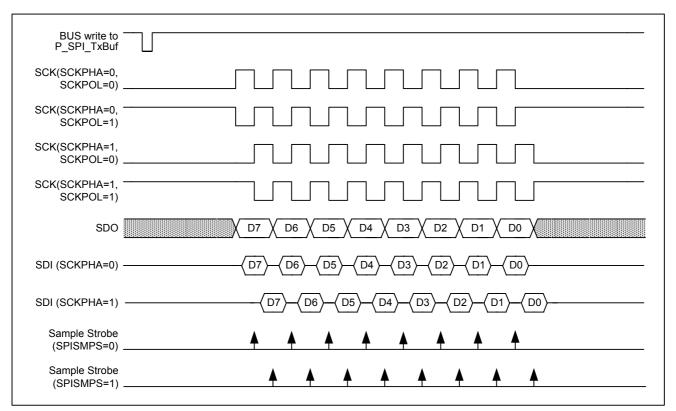

| Figure 5-73 SPI mode timing, Master Mode                                                    | 124 |

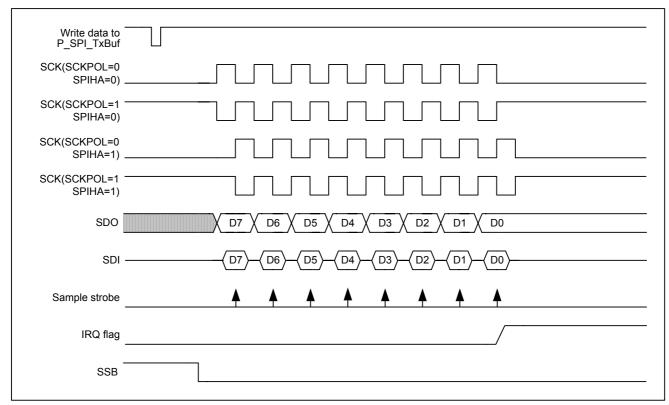

| Figure 5-74 SPI mode timing, Slave Mode, SPIPHA = 0                                         | 125 |

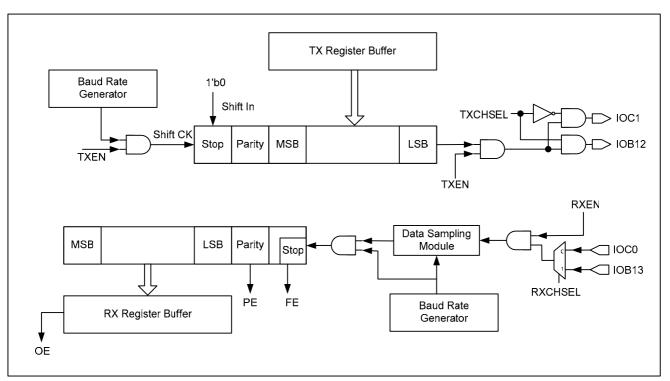

| Figure 5-75 UART block diagram                                                              | 128 |

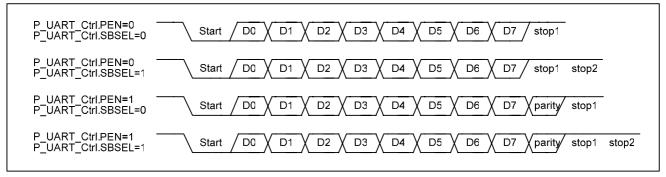

| Figure 5-76 UART Data Format                                                                | 128 |

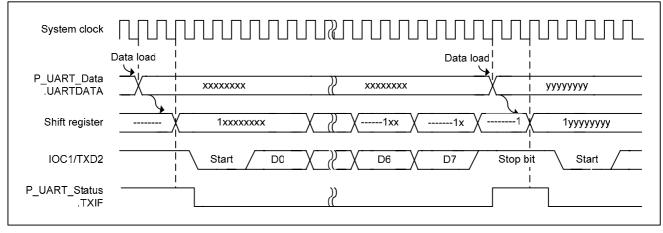

| Figure 5-77 Data Transmission Timing                                                        | 128 |

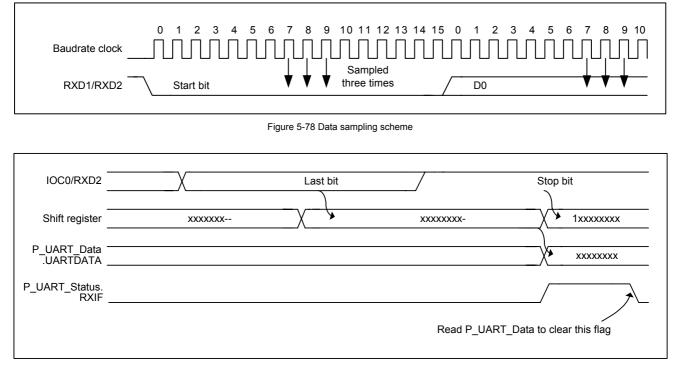

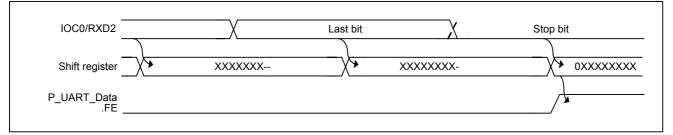

| Figure 5-78 Data sampling scheme                                                            | 129 |

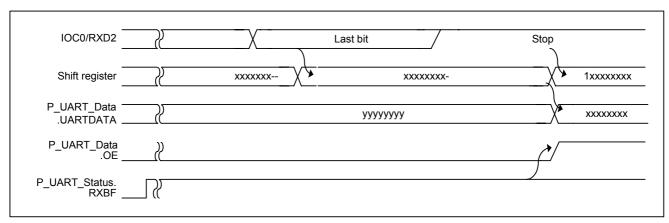

| Figure 5-79 RX buffer full                                                                  | 129 |

| Figure 5-80 Overrun error timing                                                            | 130 |

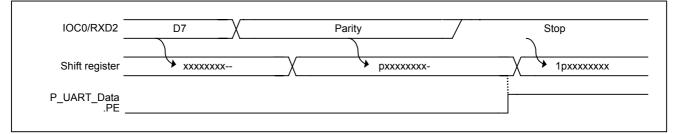

| Figure 5-81 Parity Error timing                                                             | 130 |

| Figure 5-82 Frame Error timing                                                              | 130 |

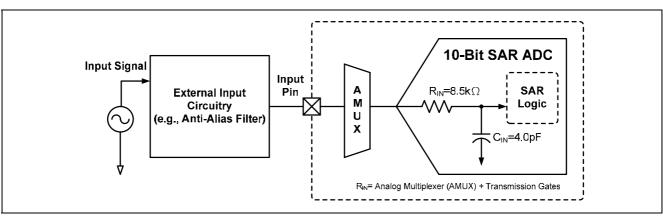

| Figure 5-83 ADC equivalent circuit for SPMC75F2413A                                         | 133 |

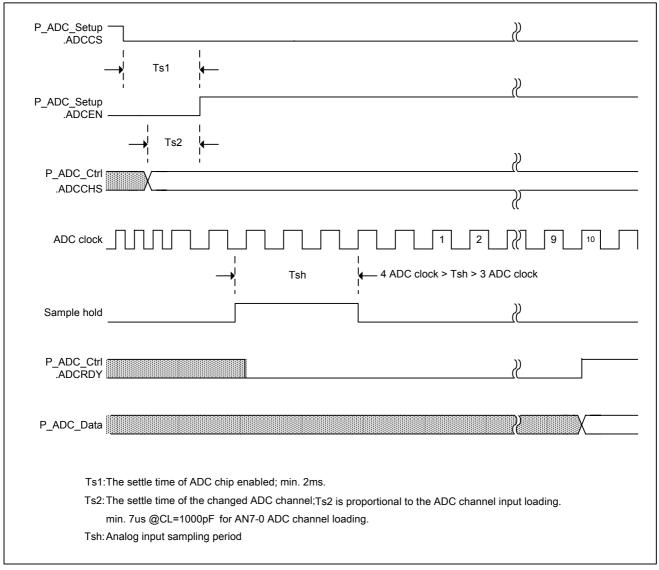

| Figure 5-84 ADC timing diagram                                                              | 133 |

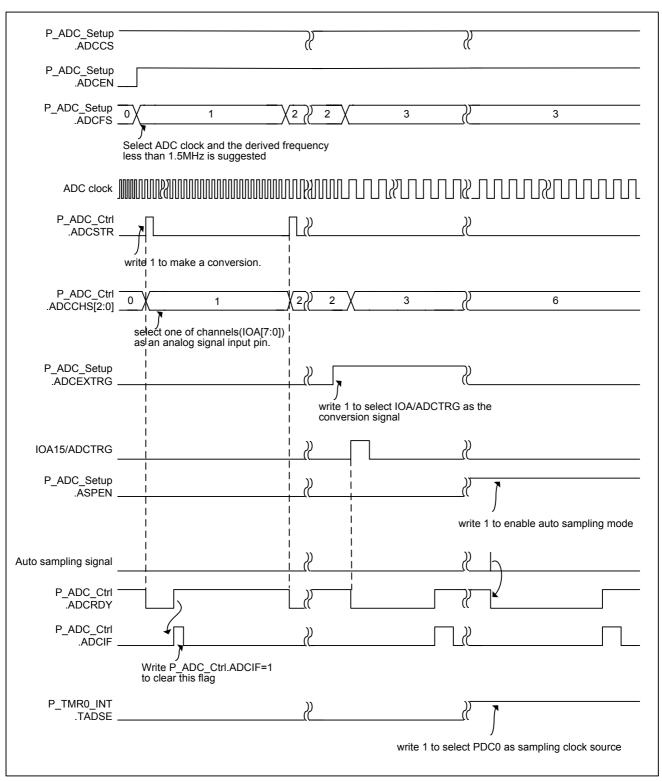

| Figure 5-85 AD conversion timing                                                            | 135 |

| Figure 5-86 Watchdog Timing Diagram                                                         | 138 |

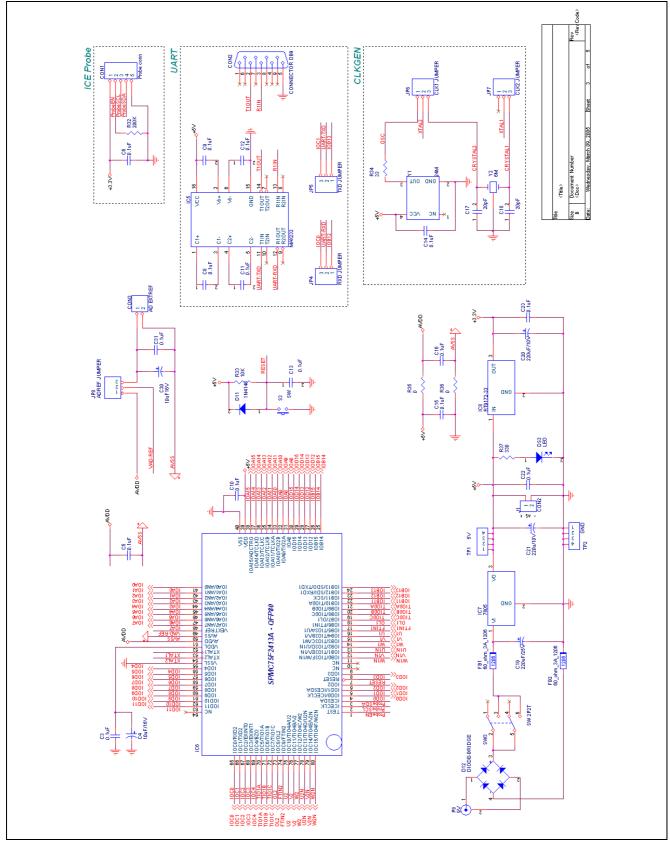

| Figure 7-1 SPMC75F2413A EVM board circuit part I                                            | 142 |

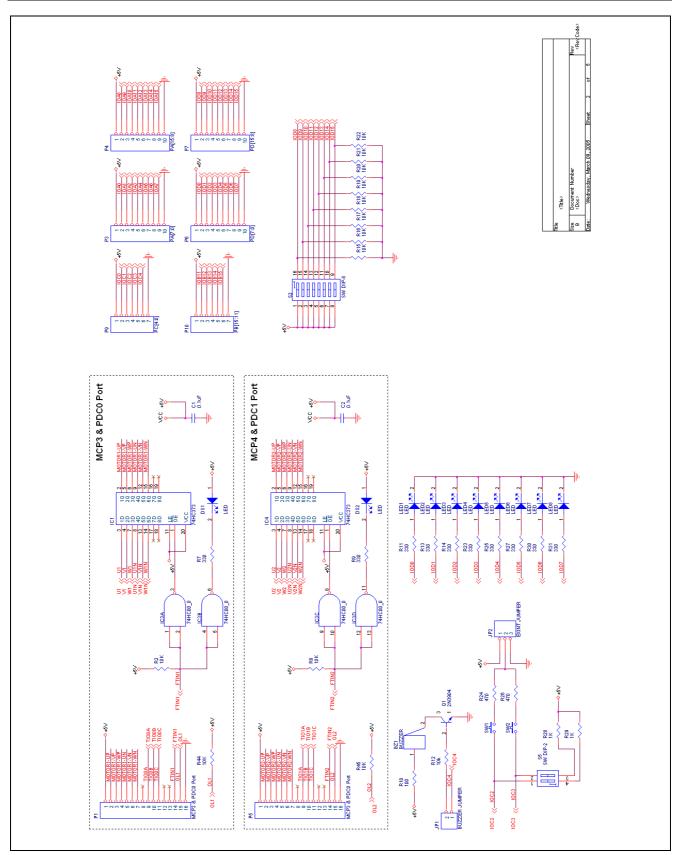

| Figure 7-2 SPMC75F2413A EVM board circuit part II                                           | 143 |

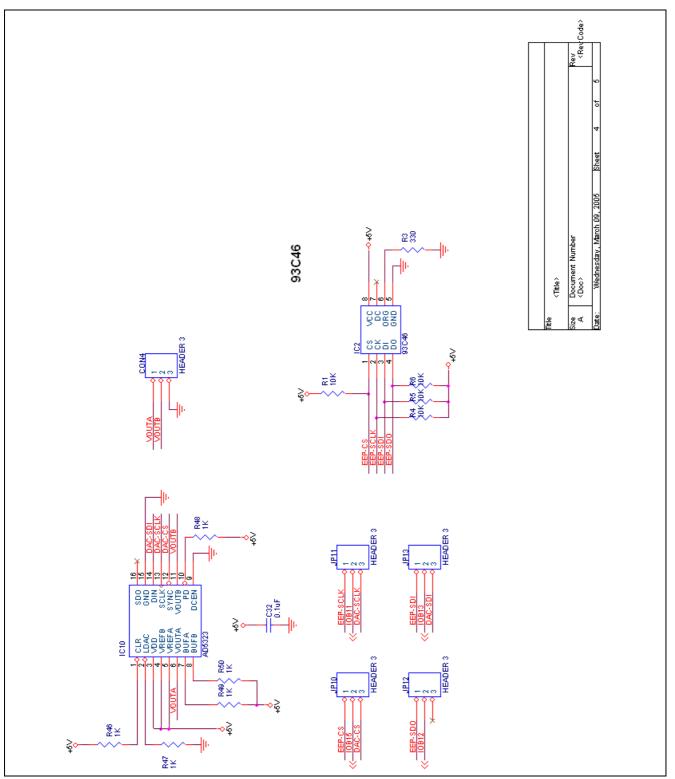

| Figure 7-3 SPMC75F2413A EVM board circuit part III                                          | 144 |

|                                                                                             |     |

### Tables

#### PAGE

| Table 5-1 Detailed Address Mapping                          |  |

|-------------------------------------------------------------|--|

| Table 5-2 Command function and access flow                  |  |

| Table 5-3 Flash/SRAM access table in normal and ICE mode    |  |

| Table 5-4 Interrupts vectors list                           |  |

| Table 5-5 the relationship between mode and operation       |  |

| Table 5-6 Interrupt sources of each IRQ level               |  |

| Table 5-7 Reset source and effected modules                 |  |

| Table 5-8 Open-drain Configuration                          |  |

| Table 5-9 I/O Configuration                                 |  |

| Table 5-10 PDC timers specification                         |  |

| Table 5-11 Input capture configuration settings and results |  |

| Table 5-12 phase counting mode 1 relationship               |  |

| Table 5-13 phase counting mode 2 relationship               |  |

| Table 5-14 phase counting mode 3 relationship               |  |

| Table 5-15 phase counting mode 4 relationship               |  |

| Table 5-16 TPM Timer 2 Specification                        |  |

| Table 5-17 input capture configuration settings and results |  |

| Table 5-18 MCP timer 3 and 4 specification                  |  |

| Table 5-19 Fault input and PWM output pins combinations     |  |

| Table 5-20 Overload protection interrupt when POLP = 1      |  |

| Table 5-21 Overload protection interrupt when POLP = 0      |  |

| Table 5-22 P_UART_BaudRate setup value at FCK = 24.0 MHz    |  |

| Table 5-23 WDT Time-out selections                          |  |

|                                                             |  |

### **16-BIT MCU WITH TWO CHANNELS MOTOR CONTROLLER**

#### **1. GENERAL DESCRIPTION**

The SPMC75F2413A, a 16-bit architecture product, carries the newest 16-bit microprocessor,  $\mu' nSP^{TM}$  (pronounced as *micro-n*-SP), developed by Sunplus Innovation Technology. The high processing speed assures the  $\mu' nSP^{TM}$  is capable of handling complex digital signal processes easily and rapidly. The memory capacity includes 32K-word flash memory plus a 2K-word working SRAM. Also, a 2-channel motor driver is incorporated which can drive two BLDC (Brushless DC) or AC induction motors simultaneously. Other features include PLL, 64 programmable multi-functional I/Os, UART, SPI, five 16-bit general-purpose timers, two compare match timers, low voltage reset, 8-ch 10-bit ADC input and many others. The device is suitable for home appliances with motors, such as air conditioners, washing machines, or refrigerators.

#### 2. FEATURES

- SunplusIT 16-bit µ'nSP processor (ISA 1.2)

- Operating voltage:

4.5V ~ 5.5V

- Operating speed: 12~24MHz

- Operating temperature: -40°C~85°C

- On-chip Memory

- 32KW (32K\*16) Flash

- 2KW (2K\*16) SRAM

- Clock for system operation

- Crystal oscillator, On-chip PLL and external clock for clock generation

- Monitoring for clock failed

- Power management

- 2 power-down modes: Wait/Standby

- Each peripheral can be powered down independently

- Up to 38 interrupt sources

- Up to 6 reset status flag

- Up to 64 GPIO pins

- Twelve 16-bit motor drive PWM outputs (MCP)

- 2-channel motor drive PWM outputs (3-phase 6-pin complementary PWM outputs)

- Center- or Edge-aligned PWM outputs

- PWM overload protection with external OL1/OL2 input pins

- Emergency PWM outputs shutdown with external fault protection pins

- Programmable dead-time control

- PWM service and fault interrupt generation

- Capable of driving AC induction and BLDC motors

- Five 16-bit general-purpose timers (TPM)

- Timer 0/1 each supports 3-channel Capture/Compare/PWM function

- Timer 2 supports 2-channel Capture/Compare/PWM function

- Timer 3/4 supports motor drive PWM function

- Two Compare Match Timers

- One Timebase timer

- 10-bit analog-to-digital converter

- 8 multiplexed input channels

- 10µs (100kHz) conversion time

- Support top reference voltage input

- Serial communication interface

- UART

- SPI

- Watchdog timer

- Embedded In-Circuit-Emulation Circuit

#### 3. BLOCK DIAGRAM

Figure 3-1 SPMC75F2413A function block diagram

#### 4. SIGNAL DESCRIPTIONS

#### 4.1. Pin Descriptions

#### 4.1.1. 80-Pin QFP/ 64-Pin QFP package signals description

|                | PIN   | No    | Туре   | Description                                                          |  |

|----------------|-------|-------|--------|----------------------------------------------------------------------|--|

| Mnemonic       | QFP80 | QFP64 |        |                                                                      |  |

| ICEN           | 1     | 1     | I (PL) | ICE/Program or Normal mode control                                   |  |

| ICECLK         | 2     | -     | I/O    | ICE serial clock input (3V IO)                                       |  |

| ICESDA         | 3     | -     | I/O    | ICE serial address/data input/output (3V IO)                         |  |

| IOD0/ICECLK    | 4     | 2     | I/O    | IOD0 or ICE serial clock input (for QFP64 package)                   |  |

| IOD1/ICESDA    | 5     | 3     | I/O    | IOD1 or ICE serial address/data input/output (for QFP64 package)     |  |

| IOD2           | 6     | 4     | I/O    | IOD2                                                                 |  |

| RESETB         | 7     | 5     | I (PH) | External reset                                                       |  |

| IOD3           | 8     | 6     | I/O    | IOD3                                                                 |  |

| NC             | 9     | -     | -      | No Connection                                                        |  |

| NC             | 10    | -     | -      | No Connection                                                        |  |

| IOB0/TIO3F/W1N | 11    | 7     | I/O    | IOB0 or TPM channel 3 input/output F or motor drive W1N phase output |  |

| IOB1/TIO3E/V1N | 12    | 8     | I/O    | IOB1 or TPM channel 3 input/output E or motor drive V1N phase output |  |

| IOB2/TIO3D/U1N | 13    | 9     | I/O    | IOB2 or TPM channel 3 input/output D or motor drive U1N phase output |  |

| IOB3/TIO3C/W1  | 14    | 10    | I/O    | IOB3 or TPM channel 3 input/output C or motor drive W1 phase output  |  |

| IOB4/TIO3B/V1  | 15    | 11    | I/O    | IOB4 or TPM channel 3 input/output B or motor drive V1 phase output  |  |

| IOB5/TIO3A/U1  | 16    | 12    | I/O    | IOB5 or TPM channel 3 input/output A or motor drive U1 phase output  |  |

| IOB6/FTIN1     | 17    | 13    | I/O    | IOB6 or external fault protection input 1                            |  |

| IOB7/OL1 18    |       | 14    | I/O    | IOB7 or overload protection input 1                                  |  |

| IOB8/TIO0C     | 19    | 15    | I/O    | IOB8 or TPM channel 0 input/output C                                 |  |

| IOB9/TIO0B     | 20    | 16    | I/O    | IOB9 or TPM channel 0 input/output B                                 |  |

| IOB10/TIO0A    | 21    | 17    | I/O    | IOB10 or TPM channel 0 input/output A                                |  |

| IOB11/SCK      | 22    | 18    | I/O    | IOB11 or SPI clock input/output                                      |  |

| IOB12/SDI/RXD1 | 23    | 19    | I/O    | IOB12 or SPI data input or UART receive data input 1                 |  |

| IOB13/SDO/TXD1 | 24    | 20    | I/O    | IOB13 or SPI data output or UART transmit data output 1              |  |

| IOB14          | 25    | 21    | I/O    | IOB14                                                                |  |

| IOB15          | 26    | 22    | I/O    | IOB15                                                                |  |

| IOD12          | 27    | -     | I/O    | IOD12                                                                |  |

| IOD13          | 28    | -     | I/O    | IOD13                                                                |  |

| IOD14          | 29    | -     | I/O    | IOD14                                                                |  |

| IOD15          | 30    | -     | I/O    | IOD15                                                                |  |

| IOA8           | 31    | 23    | I/O    | IOA8                                                                 |  |

| IOA9/TIO2A     | 32    | 24    | I/O    | IOA9 or TPM channel 2 input/output A                                 |  |

| IOA10/TIO2B    | 33    | 25    | I/O    | IOA10 or TPM channel 2 input/output B                                |  |

| IOA11/TCLKA    | 34    | 26    | I/O    | IOA11 or external clock A input                                      |  |

| IOA12/TCLKB    | 35    | 27    | I/O    | IOA12 or external clock B input                                      |  |

| IOA13/TCLKC    | 36    | 28    | I/O    | IOA13 or external clock C input                                      |  |

| IOA14/TCLKD    | 37    | 29    | I/O    | IOA14 or external clock D input                                      |  |

| IOA15/ADCTRG   | 38    | 30    | I/O    | IOA15 or A/D converter external trigger to start a conversion        |  |

| VDD            | 39    | 31    | P      | 5V power input for IO and built-in regulator                         |  |

| VSS            | 40    | 32    | P      | Ground for IO                                                        |  |

| Maaraasia                                                                                       | PIN No 1                                           |          | Туре                                                                  | Description                                                             |  |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------|----------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| Mnemonic                                                                                        | QFP80                                              | QFP64    |                                                                       |                                                                         |  |

| IOA0/AN0                                                                                        | 41                                                 | 33       | I/O                                                                   | IOA0 or analog input channel 0 of ADC                                   |  |

| IOA1/AN1                                                                                        | 42                                                 | 34       | I/O                                                                   | IOA1 or analog input channel 1 of ADC                                   |  |

| IOA2/AN2                                                                                        | 43                                                 | 35       | I/O                                                                   | IOA2 or analog input channel 2 of ADC                                   |  |

| IOA3/AN3                                                                                        | 44                                                 | 36       | I/O                                                                   | IOA3 or analog input channel 3 of ADC                                   |  |

| IOA4/AN4                                                                                        | 45                                                 | 37       | I/O                                                                   | IOA4 or analog input channel 4 of ADC                                   |  |

| IOA5/AN5                                                                                        | 46                                                 | 38       | I/O                                                                   | IOA5 or analog input channel 5 of ADC                                   |  |

| IOA6/AN6                                                                                        | 47                                                 | 39       | I/O                                                                   | IOA6 or analog input channel 6 of ADC                                   |  |

| IOA7/AN7                                                                                        | 48                                                 | 40       | I/O                                                                   | IOA7 or analog input channel 7 of ADC                                   |  |

| VEXTREF                                                                                         | 49                                                 | 41       | I                                                                     | ADC top voltage reference                                               |  |

| AVSS                                                                                            | 50                                                 | 42       | Р                                                                     | Analog ground for ADC                                                   |  |

| AVDD                                                                                            | 51                                                 | 43       | Р                                                                     | Analog power for ADC                                                    |  |

| VDDL                                                                                            | 52                                                 | 44       | Р                                                                     | External capacitance pin for internal step-down regulator/Digital power |  |

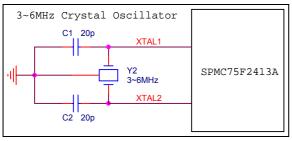

| XTAL1                                                                                           | 53                                                 | 45       | I                                                                     | External 3-6MHz crystal input for crystal oscillator                    |  |

| XTAL2                                                                                           | 54                                                 | 46       | 0                                                                     | External 3-6MHz crystal output / External clock input                   |  |

| VSSL                                                                                            | 55                                                 | 47       | Р                                                                     | Digital ground                                                          |  |

| IOD4                                                                                            | 56                                                 | 48       | I/O                                                                   | IOD4                                                                    |  |

| IOD5                                                                                            | 57                                                 | -        | I/O                                                                   | IOD5                                                                    |  |

| IOD6                                                                                            | 58                                                 | 58 - I/O |                                                                       | IOD6                                                                    |  |

| IOD7                                                                                            | 59                                                 | -        | I/O                                                                   | IOD7                                                                    |  |

| IOD8                                                                                            | 60                                                 | -        | I/O                                                                   | IOD8                                                                    |  |

| IOD9                                                                                            | 61                                                 | -        | I/O                                                                   | IOD9                                                                    |  |

| IOD10                                                                                           | 62                                                 | -        | I/O                                                                   | IOD10                                                                   |  |

| IOD11                                                                                           | 63                                                 | -        | I/O                                                                   | IOD11                                                                   |  |

| NC                                                                                              | 64                                                 | -        | -                                                                     | No connection                                                           |  |

| IOC0/RXD2                                                                                       | D/RXD2 65 49 I/O IOC0 or UART receive data input 2 |          | IOC0 or UART receive data input 2                                     |                                                                         |  |

| IOC1/TXD2                                                                                       | 66                                                 | 50       | I/O                                                                   | IOC1 or UART transmit data output 2                                     |  |

| IOC2/EXINT0                                                                                     | 67                                                 | 51       | I/O                                                                   | IOC2 or external interrupt input 0                                      |  |

| IOC3/EXINT1                                                                                     | 68                                                 | 52       | I/O                                                                   | IOC3 or external interrupt input 1                                      |  |

| IOC4/BZO                                                                                        | 69                                                 | 53       | I/O                                                                   | IOC4 or buzzer output                                                   |  |

| IOC5/TIO1A                                                                                      | 70                                                 | 54       | I/O                                                                   | IOC5 or TPM channel 1 input/output A                                    |  |

| IOC6/TIO1B                                                                                      | 71                                                 | 55       | I/O                                                                   | IOC6 or TPM channel 1 input/output B                                    |  |

| IOC7/TIO1C                                                                                      | 72                                                 | 56       | I/O                                                                   | IOC7 or TPM channel 1 input/output C                                    |  |

| IOC8/OL2                                                                                        | 73                                                 | 57       | I/O                                                                   | IOC8 or overload protection input 2                                     |  |

| IOC9/FTIN2                                                                                      | 74                                                 | 58       | I/O                                                                   | IOC9 or external fault input 2                                          |  |

| IOC10/TIO4A/U2                                                                                  | 75                                                 | 59       | I/O                                                                   | IOC10 or TPM channel 4 input/output A or motor drive U2 phase output    |  |

| IOC11/TIO4B/V2                                                                                  | 76                                                 | 60       | I/O                                                                   | IOC11 or TPM channel 4 input/output B or motor drive V2 phase output    |  |

| IOC12/TIO4C/W2                                                                                  | 77                                                 | 61       | I/O                                                                   | IOC12 or TPM channel 4 input/output C or motor drive W2 phase output    |  |

| IOC13/TIO4D/U2N                                                                                 | 78                                                 | 62       | I/O                                                                   | IOC13 or TPM channel 4 input/output E or motor drive U2N phase output   |  |

| IOC14/TIO4E/V2N                                                                                 | 79                                                 | 63       | I/O                                                                   | IOC14 or TPM channel 4 input/output E or motor drive V2N phase output   |  |

| IOC15/TIO4F/W2N 80 64 I/O IOC15 or TPM channel 4 input/output F or motor drive W2N phase output |                                                    |          | IOC15 or TPM channel 4 input/output F or motor drive W2N phase output |                                                                         |  |

Legend: I = Input, O = Output, P = Power, PL = Pull-low, PH = Pull-high

#### Figure 4-1 SPMC75F2413A QFP80 package

#### © Sunplus Innovation Technology Inc. Proprietary & Confidential

#### 5. FUNCTIONAL DESCRIPTIONS

#### 5.1. CPU Core

The SPMC75F2413A consists the newest 16-bit microprocessor,  $\mu$ '*n*SP<sup>TM</sup> (pronounced as *micro-n*-SP), developed by Sunplus Innovation Technology. The CPU features include:

- 16-bit data bus / 22-bit address bus

- 4M words (8M bytes) memory space

- 64 banks / 64k words per bank

- Thirteen 16-bit registers

- 5 general registers (R1-R5)

- 4 secondary registers (SR1-SR4)

- 3 system registers (SP, SR, PC)

- Inner registers (FR)

- Ten interrupts

- 1 fast interrupt (FIQ)

- 8 normal interrupts (IRQ0-IRQ7)

- 1 software interrupt (BRK)

- Support IRQ nested mode

- Six addressing modes

- Immediate (I6/I16)

- Direct (A6/A16)

- Indirect+ auto indexing address (DS indirect)

- Relative (BP+IM6)

- Multiple indirect (PUSH/POP)

- Register

- 16x16 multiplication & up to 16-level inner product operation

- Three multiplication mode: signed x signed, signed x unsigned, unsigned x unsigned

- 4 bits guard bit of inner product operation to avoid overflow

- Integer/Fraction mode

- 1-bit division

- DIVS: divide the sign bit; DIVQ: divide the quotient

- Divide 32-bit numerator and a 16-bit denominator

- Effective-exponent detect operation (EXP)

- Bit operation

- Bit test / set / clr / inv operation to full memory space or registers

- Multi-cycles 16-bit shift operation

- Support 32-bit shift with combining 2 shift instructions

- Far Indirect JMP by MR register

- Far Indirect Call by MR register

- NOP operation

- DS segment access instructions

- CPU inner flags access instructions

#### 5.2. Memory Organization

#### 5.2.1. Memory Map

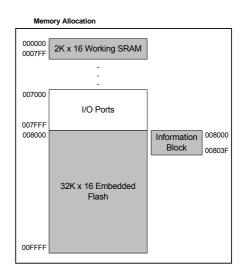

The device contains 32KW flash and 2KW SRAM. The memory space can be separated into three blocks: SRAM, I/O port registers, and flash. The SRAM is used for stack, variable or data storage. The I/O port register is used to control the peripheral modules. The embedded flash is designed for programming code. The block diagram of memory is shown as Figure 5-1. Table 5-1 shows the detailed memory allocation.

Figure 5-1 Memory allocation

**Note:** The address of 000800 – 006FFF and 010000 – 3FFFFF is reserved and cannot be accessed. An IAR (Illegal Address Reset) will be generated if CPU reads or writes these addresses.

#### Table 5-1 Detailed Address Mapping

| I/O Address (Hex) | Mapping                                      |  |  |

|-------------------|----------------------------------------------|--|--|

| 0000~07FF         | 2KW SRAM                                     |  |  |

| 0800~6FFF         | Illegal                                      |  |  |

| 7000~701F         | System Control                               |  |  |

| 7020~704F         | Memory Control                               |  |  |

| 7050~705F         | Reserved                                     |  |  |

| 7060~709F         | I/O Port Control                             |  |  |

| 70A0~70AF         | Interrupt Control                            |  |  |

| 70B0~70BF         | Time Base Control                            |  |  |

| 70C0~70DF         | Timer Control                                |  |  |

| 70E0~70FF         | Reserved                                     |  |  |

| 7100~711F         | UART Control                                 |  |  |

| 7120~713F         | Reserved                                     |  |  |

| 7140~715F         | SPI Control                                  |  |  |

| 7160~73FF         | Reserved                                     |  |  |

| 7400~747F         | Timer/PWM Module Control (for motor control) |  |  |

| 7500~751F         | Compare Match Timer Control                  |  |  |

| 7600~7FFF         | Illegal                                      |  |  |

| 8000~FFFF         | 32KW Program ROM                             |  |  |

| 10000~ 3FFFFF     | lllegal                                      |  |  |

#### 5.2.2. Flash Organization and Control

#### 5.2.2.1. Introduction

The SPMC75F2413A has two flash blocks: information block and normal block. Only one of the two blocks can be addressed at the same time. The information block contains 64 words. The address of information block is mapped from 0x8000 ~ 0x803F. The 0x8000 is a system option register P\_System\_Option. The other addresses are used for storing important information such version control, date, vender name, project name etc. The information block's structure is in Figure 5-2 and they only can be written in ICE mode or by writer. The 32K words of normal block are partitioned into 16 banks, 2K words each. Except the bank between 0xF000 and 0xF7FF can be programmed to be read-only or read-write in free run mode independently, the others are read-only bank. Moreover, each 2K-word bank can also be separated by eight frames so that the 32K embedded flash can be divided to 128 frames. The user can erase each frame separately. The relation of page and frame of flash is shown in Figure 5-3.

|        | 64 Words        |  |  |  |

|--------|-----------------|--|--|--|

| 0x8000 | P_System_Option |  |  |  |

| 0x8001 |                 |  |  |  |

|        | :               |  |  |  |

|        | :               |  |  |  |

|        | :               |  |  |  |

|        | :               |  |  |  |

| 0x803F |                 |  |  |  |

Figure 5-2 Structure of Information block

#### **[Example 6-1]** : Set bank14 as read-only mode

|        | 16 Banks |     | 8 Frames |

|--------|----------|-----|----------|

| 0x8000 | 2K x 16  | ] / | 256 x16  |

|        | :        | /[  | 256 x16  |

|        | :        | / [ |          |

|        | :        |     | :        |

|        | :        |     | :        |

|        | :        |     | :        |

|        | 2K x 16  | γι  |          |

|        | 2K x 16  | 1   |          |

| 0xFFFF | 2K x 16  | ]   |          |

Figure 5-3 Page0 and frame of flash

#### 5.2.2.2. Flash Operation

There are two registers for flash control: P\_Flash\_RW (0x704D) and P\_Flash\_Cmd (0x7555). The flash access control, P\_Flash\_RW (0x704D), can be configured by two consecutive write cycles, keeping away from inadvertent writing. First, write 0x5a5a to P\_Flash\_RW, and then write the configuration data to P\_Flash\_RW within 16 clock cycles.

The flash command register, P\_Flash\_Cmd, is a write only register that is for accepting/performing flash command. Before performing any commands, users should write 0xAAAA to P\_Flash\_Cmd for entering flash command mode at first. Table 5-2 shows the command and access flow.

Remarkably, the characteristic of flash is that the data bit can only be programmed from 1 to 0, but it is not allowed to be from 0 to 1. Therefore, if users intend to program flash, the frame erase instruction must be executed first, which erase data bit from 0 to 1.

| Exam                                                   | <b>Example 6-1</b> Set bank14 as read-only mode                      |                |                                |  |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------|----------------|--------------------------------|--|--|--|--|--|

| #define                                                | #define CW_FlashRW_CMD 0x5A5A                                        |                | //Flash RW Command             |  |  |  |  |  |

| #define                                                | CB_BK14WDIS                                                          | (0x4000 >> 14) |                                |  |  |  |  |  |

| P_Flash                                                | _RW->W = CW_FlashRW_CMD;                                             |                | /* Flash Read Write Command */ |  |  |  |  |  |

| P_Flash                                                | P_Flash_RW->B.BK14WENB = CB_BK14WDIS; /* Set Bank 14 as Read Only */ |                |                                |  |  |  |  |  |

| Listing 6-1 read-only mode for bank 14 of flash memory |                                                                      |                |                                |  |  |  |  |  |

#### Table 5-2 Command function and access flow

|                                    | Frame Erase            | Program Mode             | Sequential Program Mode                    |

|------------------------------------|------------------------|--------------------------|--------------------------------------------|

| 1 cycle                            | P_Flash_Cmd = 0xAAAA   |                          |                                            |

| 2 cycle                            | [P_Flash_Cmd] = 0x5511 | [ P_Flash_Cmd ] = 0x5533 | [ P_Flash_Cmd ] = <b>0x5544</b>            |

| 3 cycle                            | Set Frame Address      | Write Data               | Write Data                                 |

| 4 cycle Write any data and wait 20 |                        | Wait 40us End – Auto     | Wait 40us – Auto                           |

|                                    | End – Auto             |                          | Go to 2 cycle                              |

|                                    |                        |                          | [ P_Flash_Cmd ]= <b>0xFFFF</b> → Go to End |

#### **[Example 6-2]** : Example for frame erasing:

| #define CW_FlashCMD                 | 0xAAAA            | //Flash Command FLash Block                              |

|-------------------------------------|-------------------|----------------------------------------------------------|

| #define CW_PageErase                | 0x5511            | //Flash Page Erase Command                               |

| unsigned int *P_WordAdr;            |                   |                                                          |

| P_Flash_Cmd->W = CW_FlashCMD;       |                   |                                                          |

| P_Flash_Cmd->W = CW_PageErase;      |                   |                                                          |

| P_WordAdr = (unsigned int *)0xF000; |                   | /* P_WordAdr = start address of bank 14 */               |

| *P_WordAdr = 0;                     |                   | /* Write any data to erase the first frame of bank 14 */ |

|                                     | Listing 6-2 frame | erasing of flash memory                                  |

Listing 6-2 frame erasing of flash memory

#### [Example 6-3] : Example for program mode: Write 0x1234 to the address of 0xF000

| #define CW_FlashCMD                             | 0xAAAA | //Flash Command FLash Block                |  |  |  |

|-------------------------------------------------|--------|--------------------------------------------|--|--|--|

| #define CW_Program                              | 0x5533 | //Flash Program Command                    |  |  |  |

| unsigned int *P_WordAdr;                        |        |                                            |  |  |  |

| P_Flash_Cmd->W = CW_FlashCMD;                   |        |                                            |  |  |  |

| P_Flash_Cmd->W = CW_Program;                    |        |                                            |  |  |  |

| P_WordAdr = (unsigned int *)0xF000;             |        | /* P_WordAdr = start address of bank 14 */ |  |  |  |

| *(unsigned int *)P_WordAdr = 0x1234;            |        | /* program one word = 0x1234 */            |  |  |  |

| <b>Listing 6-3</b> program mode of flash memory |        |                                            |  |  |  |

Listing 6-3 program mode of flash memory

[Example 6-4] Example for sequential program mode: Write data to flash with sequential program mode, address is from 0xF000 to 0xF020.

| #define CW_FlashCMD                  | 0xAAAA | //Flash Command FLash Block            |

|--------------------------------------|--------|----------------------------------------|

| #define CW_Sequential                | 0x5544 | //Flash Sequential Program Command     |

| #define CW_SequentialEnd             | 0xFFFF | //Flash Sequential Program End Command |

| unsigned int *P_WordAdr;             |        |                                        |

| unsigned int i,uiData=1;             |        |                                        |

| P_Flash_Cmd->W = CW_FlashCMD;        |        |                                        |

|                                      |        |                                        |

| for(i=0xF000;i<=0xF020;i++)          |        |                                        |

| {                                    |        |                                        |

| P_Flash_Cmd->W = CW_Sequential;      |        |                                        |

| P_WordAdr = (unsigned int *)i;       |        | // program address is the content of i |

| *(unsigned int *)P_WordAdr = uiData; |        | // program uiData to P_WordAdr         |

| uiData ++;                           |        |                                        |

| }/* End For Loop */                  |        |                                        |

|                                      |        |                                        |

| P_Flash_Cmd->W = CW_SequentialEnd;   |        |                                        |

Listing 6-4 sequential program mode of flash memory

1

Reserved

#### • P\_Flash\_RW (0x704D): Embedded Flash Access Control Register

1

Reserved

The flash access control, P\_Flash\_RW, exclusively sets up banks14 with read only or full access in free run mode. This port

from inadvertent writing. First, write 0x5A5A to P\_Flash\_RW, and then write configuration data to P\_Flash\_RW in duration of less than 16 clock cycles.

1

Reserved

Reserved

| can be configure | ed by two consec | cutive write cycle | to keep away | than 16 clock | cycles.  |           |          |

|------------------|------------------|--------------------|--------------|---------------|----------|-----------|----------|

| B15              | B14              | B13                | B12          | B11           | B10      | В9        | B8       |

| R                | R/W              | R                  | R            | R             | R        | R         | R        |

| 0                | 0                | 0                  | 0            | 0             | 0        | 0         | 0        |

| Reserved         | BK14WENB         | Reserved           | Reserved     | Reserved      | Reserved | Reserved  | Reserved |

| Reserved         | DK 14WEIND       | Reserved           | Reserved     | Reserved      | Reserved | INESEIVEU | Reserveu |

| Reserved         | DK 14VVEIND      | Reserved           | Reserved     | Reserved      | Reserved | Reserved  | Reserved |

| B7               | BK 14WEINB<br>B6 | B5                 | B4           | B3            | B2       | B1        | B0       |

|                  |                  |                    |              |               |          |           |          |

1

Reserved

1

Reserved

| B15   | Reserved |                            |               |              |

|-------|----------|----------------------------|---------------|--------------|

| B14   | BK14WENB | F000h-F7FFh access control | 0= Read/write | 1= Read-only |

| B13-0 | Reserved |                            |               |              |

#### • P\_Flash\_Cmd (0x7555): Embedded flash command register

1

Reserved

This port is used to issue flash command. Before performing any commands, users should write 0xAAAA to P Flash Cmd for

entering flash command mode at first. Please see the Table 5-2.

1

Reserved

| B15 | B14      | B13 | B12   | B11  | B10 | B9 | B8 |

|-----|----------|-----|-------|------|-----|----|----|

| W   | W        | W   | W     | W    | W   | W  | W  |

| 0   | 0        | 0   | 0     | 0    | 0   | 0  | 0  |

|     |          |     | Flash | iCmd |     |    |    |

|     |          |     |       |      |     |    |    |

| B7  | B6       | B5  | B4    | B3   | B2  | B1 | B0 |

| W   | W        | W   | W     | W    | W   | W  | W  |

| 0   | 0        | 0   | 0     | 0    | 0   | 0  | 0  |

|     | FlashCmd |     |       |      |     |    |    |

#### • P\_System\_Option (0x8000): System Option Register

| B15 | B14                  | B13 | B12  | B11 | B11 B10 |     | B9   | B8 |

|-----|----------------------|-----|------|-----|---------|-----|------|----|

| R/W | R/W R/W R/W R/W      |     | / R/ | W F | R/W     | R/W |      |    |

| 0   | 1 0 1 0 1            |     | 1    | 0   | 1       |     |      |    |

|     | Verification Pattern |     |      |     |         |     |      |    |

|     |                      |     |      |     |         |     |      |    |

| B7  | B6                   | B5  | B4   | B3  | B2      | B1  |      | B0 |

|     |                      |     |      |     |         |     | D/M/ |    |

| Бі                   | ВО  | 55  | D4       | 60  | BZ  | ы    | BU  |

|----------------------|-----|-----|----------|-----|-----|------|-----|

| R/W                  | R/W | R/W | R/W      | R/W | R/W | R/W  | R/W |

| 0                    | 1   | 0   | 1        | 0   | 1   | 1    | 1   |

| Verification Pattern |     | SCB | Reserved | LVR | WDG | CLKS |     |

| B15-5 | Verification Pattern | ICE or Writer will write 01010101010 to this area                                                                                      |            |           |  |

|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|--|

| В4    | SCB                  | Security enable, active low 0: Security enabled, the 1: Security dia<br>normal block in the flash readable or wr<br>cannot be accessed |            |           |  |

| В3    | Reserved             |                                                                                                                                        |            |           |  |

| B2    | LVR                  | Enable low voltage reset function                                                                                                      | 0: Disable | 1: Enable |  |

| B1    | WDG                  | Enable watchdog function                                                                                                               | 0: Disable | 1: Enable |  |

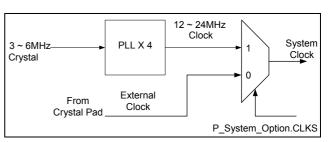

| В0 | CLKS | Clock Source Selection | 0:  | external   | clock    | input,   | 1: crystal | oscillator, | connect a |

|----|------|------------------------|-----|------------|----------|----------|------------|-------------|-----------|

|    |      |                        | con | nect an os | cillator | or clock | crystal    | device      | between   |

|    |      |                        | sou | rce to XTA | L2.      |          | XTAL1 ar   | nd XTAL2.   |           |

The "mass erase" command execute on main block is to erase main block only, but erase main block and information block if the command execute on information block. In case of security option in information block is enabled, SPMC75F2413A are protected from reading data through ICE or Writer function. If the security is enabled on under ICE enable mode, the flash main block does not allow to be read/write but information block can be read by ICE and the only command that user can perform is "mass erase". In addition, SRAM cannot be accessed (read/write) in ICE enable mode. Please refer to Table 5-3 for detail.

In normal operation (ICEN = 0), CPU can access the flash data and the working SRAM. The ICE cannot program the flash memory when the ICE mode is activated and security is enabled. This hardware protection prevents hackers from downloading a program to flash or SRAM then write source code out to GPIOs. Table 5-3 shows Flash and SRAM access table.

#### Table 5-3 Flash/SRAM access table in normal and ICE mode

| Normal mode(ICEN=0) |      |                  |        |       |  |  |

|---------------------|------|------------------|--------|-------|--|--|

|                     |      | SCB =0           | SCB =1 |       |  |  |

|                     | Read | Write            | Read   | Write |  |  |

| SRAM                | Yes  | Yes              | Yes    | Yes   |  |  |

| FLASH main block    | Yes  | Yes              | Yes    | Yes   |  |  |

| FLASH information   |      |                  | Yes    |       |  |  |

| block               | Yes  | No               |        | No    |  |  |

| ICE mode(ICEN=1)    |      |                  |        |       |  |  |

| SRAM                | No   | No               | Yes    | Yes   |  |  |

|                     | Nia  | No               | Vee    | Vee   |  |  |

| FLASH main block    | No   | (but mass erase) | Yes    | Yes   |  |  |

| FLASH information   | Nia  | No               | Vee    | Vee   |  |  |

| block               | No   | (but mass erase) | Yes    | Yes   |  |  |

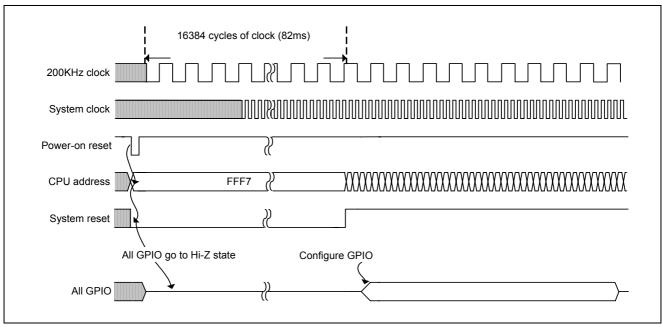

#### 5.2.2.3. Power-up procedure

When power is turned on, option bits are read by the system. The option bits are stored in the first word of embedded flash information block (address = 0x8000). When power is turned on, the system reset is activated until the power-on-timer counts 16384 cycles of 200KHz clock then, reset signal is released. Remarkably, all GPIO is on the high impedance state initially and can be configured after power-on procedure.

Figure 5-4 Power-up procedure

© Sunplus Innovation Technology Inc. Proprietary & Confidential

#### 5.2.3. SRAM

The SRAM can be used for stack, variable and data storage. Stack is used for storing the return address of function call and pushing instruction data. The direction of stack goes from bottom to up. This stack is a FILO (first in last out) structure, and the stack address is indicated by stack pointer (SP).

The variable and data storage is configured by the user. Users can use direct access, indirect access or base pointer (BP) to load or save SRAM data. Note that the stack and variable or storage data must not overlap each other; otherwise, CPU will run into an unknown state. The SPMC75F2413A addresses maximum 2K-word SRAM. The address range is from 0x0000 to 0x07FF. In addition, the stack pointer (SP) is allocated at the end of maximum address initially, i.e. 0x07FF.

#### 5.2.4. Reset and Interrupt Vectors

Addresses 0xFFF5 to 0xFFFF are reserved for reset and interrupt vectors. A reset forces the program counter (PC) points to address 0xFFF7. When a device reset occurs, the program execution will branch to 0xFFF7, named "Reset Vector Address". The SPMC75F2413A has 10 interrupts. The address and function name list are given in the following table.

#### Table 5-4 Interrupts vectors list

| Reset or IRQ vector | Address |

|---------------------|---------|

| BRK                 | 0xFFF5  |

| FIQ                 | 0xFFF6  |

| Reset               | 0xFFF7  |

| IRQ0                | 0xFFF8  |

| IRQ1                | 0xFFF9  |

| IRQ2                | 0xFFFA  |

| IRQ3                | 0xFFFB  |

| IRQ4                | 0xFFFC  |

| IRQ5                | 0xFFFD  |

| IRQ6                | 0xFFFE  |

| IRQ7                | 0xFFFF  |

#### **CPU and Peripherals Control Registers List**

#### CPU control/status registers

|           | Desister           | Deset          |          |                     |                |                | Bit F        | Field          | -                |               |               |

|-----------|--------------------|----------------|----------|---------------------|----------------|----------------|--------------|----------------|------------------|---------------|---------------|

| Address   | Register<br>Name   | Reset<br>value | R/W      | B15                 | B14            | B13            | B12          | B11            | B10              | B9            | B8            |

|           | Name               | Value          |          | B7                  | B6             | B5             | B4           | B3             | B2               | B1            | B0            |

| 0x7006-75 | 55: CPU control/st | atus regis     | ters     | 1                   |                |                |              |                |                  |               |               |

| 0x7006    | P_Reset_Status     | 0x0000         | R        |                     | ,              |                |              | -              | 1                |               |               |

|           |                    |                |          |                     | IIRF           | IARF           | _            | LVRF           | WDRF             | PORF          | EXTRF         |

|           |                    |                |          | The flag of         | f reset status | s for firmwa   | ire checking |                |                  |               |               |

|           |                    |                | W        |                     | , i i          |                | i            | i              | i                | i             |               |

|           |                    |                |          | _                   | IIRF           | IARF           | _            | LVRF           | WDRF             | PORF          | EXTRF         |

|           |                    |                |          | To properly to 1.   | y clear rese   | t flags, FCH   | HK must be   | written to 0   | 0x55 with sp     | pecified reso | et flag is se |

| 0x7007    | P_Clk_Ctrl         | 0x0000         | R        | OSCSF               | OSCIE          |                |              | -              |                  |               |               |

|           |                    |                |          | This as sist        |                |                |              |                |                  |               |               |

|           |                    |                | 10/      |                     | ter is used fo | or monitorin   | g CPU cloc   | k status       |                  |               |               |

|           |                    |                | W        | OSCSF               | OSCIE          |                |              | -              |                  |               |               |

|           |                    |                |          | Write '1' to        | OSCSF wil      | l clear this f | flaq.        |                |                  |               |               |

| 0x700A    | P_WatchDog_Ctrl    | 0x0000         | R        | WDEN                | WDRS           |                | <u> </u>     |                | _                |               |               |

|           | _ 0_               |                |          |                     |                | WDCHK          |              |                |                  | WDPS          |               |

|           |                    |                |          | This regist         | ter provides   | the watchd     | og clear tim | er and on/o    | off function for | or firmware   | setting       |

|           |                    |                | W        | WDEN                | WDRS           |                |              |                | _                |               |               |

|           |                    |                |          |                     |                | WDCHK          |              |                |                  | WDPS          |               |

|           |                    |                |          | To change           | the settings   | of this regi   | ister, WDCH  | IK must be     | written with     | "10101".      |               |

| 0x700B    | P_WatchDog_Clr     | 0x0000         | R        |                     |                | V              | Watchdog C   | lear Registe   | er               |               |               |

|           |                    |                |          |                     |                | ١              | Watchdog C   | lear Regist    | er               |               |               |

|           |                    |                |          | This regist         | ter is used to | clear watc     | hdog timer,  | Write 0xA0     | 05 to clear      | watchdog ti   | mer           |

| 0x700C    | P_Wait_Enter       | 0x0000         | R        |                     |                | Wa             | ait-Mode En  | trance Reg     | ister            |               |               |

|           |                    |                |          |                     |                | Wa             | ait-Mode En  | trance Reg     | ister            |               |               |

|           |                    |                |          | Read 0x00           | 001 indicates  | s that it is w | /ake-up fron | n wait mode    | 9.               |               |               |

|           |                    |                | W        |                     |                | Wa             | ait-Mode En  | trance Reg     | ister            |               |               |

|           |                    |                |          |                     |                | Wa             | ait-Mode En  | trance Reg     | ister            |               |               |

|           |                    |                | <u> </u> | Write 0x50          | 005 to enter   | wait mode      | (CPU off, Pl | LL on) and     | write 0x000      | 1 will clear  | wait flag.    |

| 0x700E    | P_Stdby_Enter      | 0x0000         | R        |                     |                | Stan           | dby-Enter E  | intrance Re    | gister           |               |               |

|           |                    |                |          |                     |                |                | idby-Enter E |                |                  |               |               |

|           |                    |                |          | Read 0x00           | 001 indicates  | s that it is w | /ake-up fron | n Standby n    | node.            |               |               |

|           |                    |                | W        |                     |                | Stan           | idby-Enter E | Entrance Re    | egister          |               |               |

|           |                    |                |          |                     |                |                | idby-Enter E |                | Ŭ                |               |               |

|           |                    |                |          | Write 0xA0<br>flag. | 00A to enter   | standby me     | ode (CPU o   | ff, PLL off) a | and write 0>     | (0001 will c  | lear standby  |

| 0x700F    | P_Wakeup_Ctrl      | 0x0000         | R/W      | KEYWE               | UARTWE         | SPIWE          | EXT1WE       | EXT0WE         |                  | _             |               |

|           |                    |                |          | TPM2WE              |                | PDC0WE         |              |                | -                |               |               |

|           |                    |                |          | This regist         | ter determine  | es the wake    | eup source   | when the ch    | nip is in pow    | er-saving n   | node.         |

| 0x704D    | P_Flash_RW         | 0x0000         | R/W      |                     | BK14WNB        |                |              |                |                  |               |               |

|           |                    |                |          |                     |                |                | -            | _              |                  |               |               |

|         | Register    | Reset  |     |                                                                                                                              | -   | -      | Bit         | Field       |             |    |    |  |  |  |

|---------|-------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------------|-------------|-------------|----|----|--|--|--|

| Address | Register    | value  | R/W | B15                                                                                                                          | B14 | B13    | B12         | B11         | B10         | B9 | B8 |  |  |  |

|         | Name        | value  |     | B7                                                                                                                           | B6  | B5     | B4          | B3          | B2          | B1 | B0 |  |  |  |

|         |             |        |     | First, write 0x5A5A to P_Flash_RW, and then write configuration data to P_Flash_RW ir duration of less than 16 clock cycles. |     |        |             |             |             |    |    |  |  |  |

| 0x7555  | P_Flash_Cmd | 0x0000 | R/W |                                                                                                                              |     | Embedd | ed Flash Ac | cess Contro | ol Register |    |    |  |  |  |

|         |             |        |     | Embedded Flash Access Control Register                                                                                       |     |        |             |             |             |    |    |  |  |  |

|         |             |        |     | This port is used to issue flash command.                                                                                    |     |        |             |             |             |    |    |  |  |  |

#### IO Port registers

|           | _                |              |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |               | Bit          | Field          |                |             |              |  |  |  |