## **IT8510E/TE/G**

**Embedded Controller**

**Preliminary Specification 0.7.2**

ITE TECH. INC.

Copyright © 2005 ITE Tech. Inc.

This is Preliminary document release. All specifications are subject to change without notice.

The material contained in this document supersedes all previous documentation issued for the related products included herein. Please contact ITE Tech. Inc. for the latest document(s). All sales are subject to ITE's Standard Terms and Conditions, a copy of which is included in the back of this document.

ITE, IT8510E/TE/G is a trademark of ITE Tech. Inc. All other trademarks are claimed by their respective owners. All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

ITE Tech. Inc.

Marketing Department

8F, No. 233-1, Bao Chiao RD., Hsin Tien,

Phone: (02) 2912-6889

Fax: (02) 2910-2551, 2910-2552

Taipei County 231, Taiwan, R.O.C.

If you have any marketing or sales questions, please contact:

**P.Y. Chang**, at ITE Taiwan: E-mail: <u>p.y.chang@ite.com.tw</u>, Tel: 886-2-29126889 X6052,

Fax: 886-2-29102551

To find out more about ITE, visit our World Wide Web at:

http://www.ite.com.tw

Or e-mail <a href="mailto:itesupport@ite.com.tw">itesupport@ite.com.tw</a> for more product information/services

## **Revision History**

| Section | Revision                                                                                                                | Page No. |

|---------|-------------------------------------------------------------------------------------------------------------------------|----------|

| 6       | • In section 6.2.2.4, the value of Chip Version (CHIPVER) was changed.                                                  | 48       |

| 6       | <ul> <li>In section 6.3.4.1 FBIU Configuration Register (FBCFG), OVRSHBM<br/>and OVRBADDR fields were added.</li> </ul> | 76       |

| 6       | <ul> <li>In section 6.3.4.2 Flash Programming Configuration Register (FPCFG),<br/>HSPD field was added.</li> </ul>      | 77       |

| 7       | <ul> <li>In section 7.4.3.5 Keyboard Scan In Control Register (KSICTRLR),<br/>OVRPPEN field was added.</li> </ul>       | 174      |

| 7       | <ul> <li>In section 7.5.3.1 General Control Register (GCR), GFLE field was<br/>added.</li> </ul>                        | 176      |

| 7       | <ul> <li>In section 7.11.4.5 Prescaler Clock Frequency Select Register<br/>(PCFSR), its table was revised.</li> </ul>   | 222      |

| 7       | In section 7.14.4.10, Chip Version (ECHIPVER) was added                                                                 | 247      |

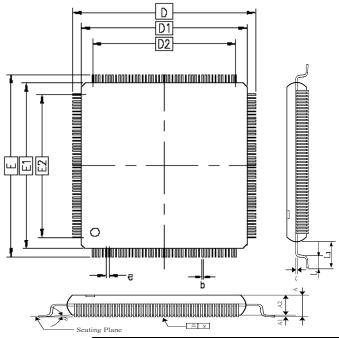

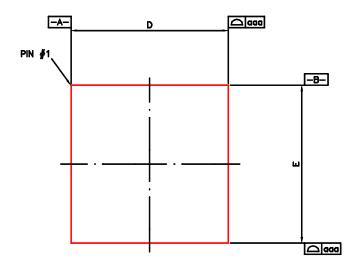

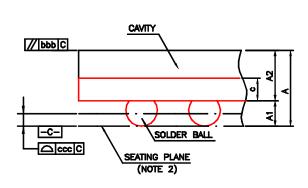

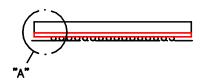

| 4, 11   | TFBGA package information was added.                                                                                    | 263      |

| 12      | In section 12 Ordering Information, lead-free information was added.                                                    | 267      |

## **CONTENTS**

| 1. | Featu      | res                  |                                                                   | 1  |

|----|------------|----------------------|-------------------------------------------------------------------|----|

| 2. | Gener      | al Description.      |                                                                   | 3  |

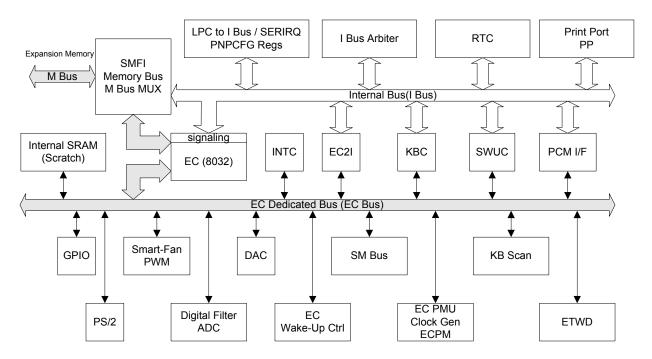

| 3. | Syste      | m Block Diagra       | m                                                                 | 5  |

|    | 3.1        | Block Diagram        |                                                                   | 5  |

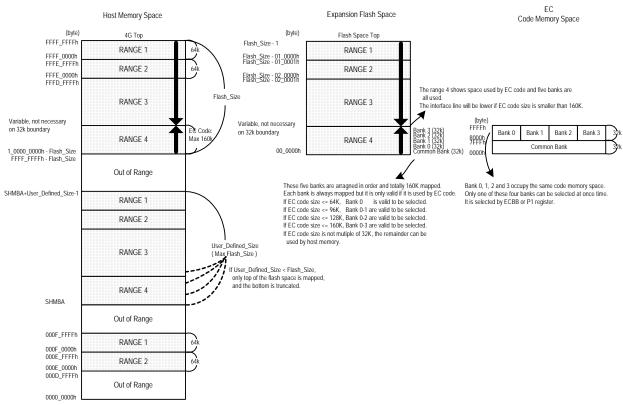

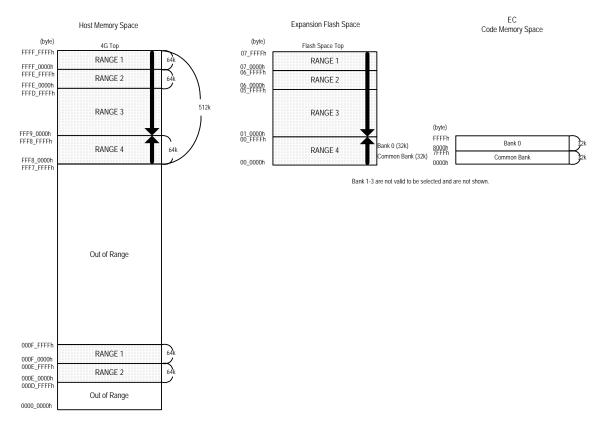

|    | 3.2        |                      | ed Memory Space                                                   |    |

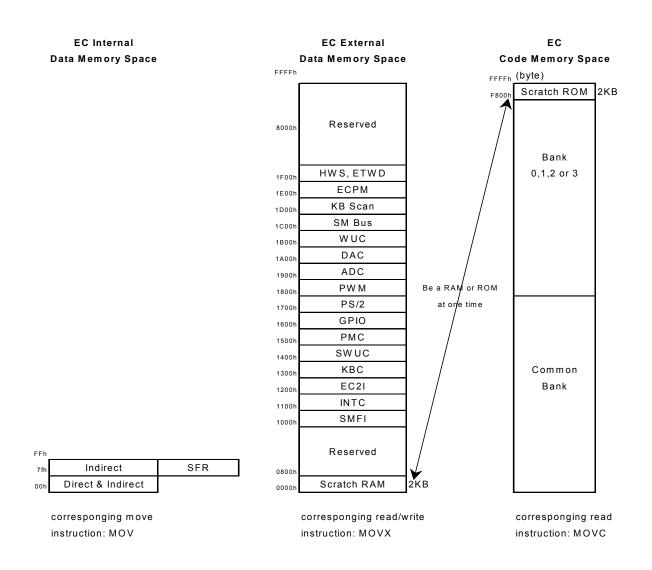

|    | 3.3        |                      | emory Space                                                       |    |

|    | 3.4        | •                    | eviation                                                          |    |

|    |            | •                    |                                                                   |    |

| 5. | Pin De     | escriptions          |                                                                   | 17 |

|    | 5.1        |                      | ns                                                                |    |

|    | 5.2        |                      | anes and Power States                                             |    |

|    | 5.3        |                      | nes and States                                                    |    |

|    | 5.4<br>5.5 |                      | errupt to INTCs and Types                                         |    |

|    | 5.5        |                      | re Interrupts to INTC                                             |    |

|    | 5.6        |                      | ode and Clock Domain                                              |    |

|    | 5.7        |                      | Schmitt-Trigger or Open-Drain Function                            |    |

|    | 5.8        | Power Consur         | nption Consideration                                              | 36 |

| 6. | Host [     | Domain Functio       | ns                                                                | 39 |

|    | 6.1        |                      | Interface                                                         |    |

|    |            |                      | ew                                                                |    |

|    |            |                      | es                                                                |    |

|    |            |                      | ted LPC Cycle Type                                                |    |

|    |            |                      | Port Functionzed IRQ (SERIRQ)                                     |    |

|    |            |                      | re Interrupts to INTC/WUC                                         |    |

|    |            | 6.1.7 LPCPI          | D# and CLKRUN#                                                    | 42 |

|    |            |                      | Items                                                             |    |

|    | 6.2        |                      | Configuration (PNPCFG)                                            |    |

|    |            |                      | I Device Assignment                                               |    |

|    |            | •                    | I/O Configuration Registers                                       |    |

|    |            | 6.2.2.1<br>6.2.2.2   | Logical Device Number (LDN)                                       |    |

|    |            | 6.2.2.3              | Chip ID Byte 2 (CHIPID2)                                          |    |

|    |            | 6.2.2.4              | Chip Version (CHIPVER)                                            |    |

|    |            | 6.2.2.5              | Super I/O Control Register (SIOCTRL)                              |    |

|    |            | 6.2.2.6              | Super I/O IRQ Configuration Register (SIOIRQ)                     | 49 |

|    |            | 6.2.2.7              | Super I/O General Purpose Register (SIOGP)                        |    |

|    |            | 6.2.2.8              | Super I/O Power Mode Register (SIOPWR)                            |    |

|    |            |                      | ard Logical Device Configuration Registers                        |    |

|    |            | 6.2.3.1<br>6.2.3.2   | Logical Device Activate Register (LDA)                            |    |

|    |            | 6.2.3.3              | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])   |    |

|    |            | 6.2.3.4              | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8]) |    |

|    |            | 6.2.3.5              | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])   |    |

|    |            | 6.2.3.6              | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)      |    |

|    |            | 6.2.3.7              | Interrupt Request Type Select (IRQTP)                             |    |

|    |            | 6.2.3.8              | DMA Channel Select 0 (DMAS0)                                      |    |

|    |            | 6.2.3.9              | DMA Channel Select 0 (DMAS1)                                      |    |

|    |            | 6.2.4 Syster 6.2.4.1 | n Wake-Up Control (SWUC) Configuration Registers                  |    |

|    |            | 6.2.4.2              | I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8]) |    |

|    |            | J.L.T.L              | C. Cado / tad coo bite [10.0] for becomptor a (10.b/tba[10.0])    |    |

|       | 6.2.4.3  | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])    |    |

|-------|----------|--------------------------------------------------------------------|----|

|       | 6.2.4.4  | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8])  |    |

|       | 6.2.4.5  | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])    |    |

|       | 6.2.4.6  | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)       |    |

|       | 6.2.4.7  | Interrupt Request Type Select (IRQTP)                              | 54 |

| 6.2.5 | KBC / N  | Nouse Interface Configuration Registers                            | 54 |

|       | 6.2.5.1  | Logical Device Activate Register (LDA)                             |    |

|       | 6.2.5.2  | I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8])  | 55 |

|       | 6.2.5.3  | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])    | 55 |

|       | 6.2.5.4  | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8])  |    |

|       | 6.2.5.5  | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])    |    |

|       | 6.2.5.6  | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)       |    |

|       | 6.2.5.7  | Interrupt Request Type Select (IRQTP)                              |    |

| 6.2.6 |          | Keyboard Interface Configuration Registers                         |    |

|       | 6.2.6.1  | Logical Device Activate Register (LDA)                             |    |

|       | 6.2.6.2  | I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8])  |    |

|       | 6.2.6.3  | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])    |    |

|       | 6.2.6.4  | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8])  | 57 |

|       | 6.2.6.5  | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])    |    |

|       | 6.2.6.6  | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)       |    |

|       | 6.2.6.7  | Interrupt Request Type Select (IRQTP)                              |    |

| 6.2.7 |          | Memory/Flash Interface (SMFI) Configuration Registers              |    |

| 0     | 6.2.7.1  | Logical Device Activate Register (LDA)                             |    |

|       | 6.2.7.2  | I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8])  |    |

|       | 6.2.7.3  | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])    |    |

|       | 6.2.7.4  | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8])  |    |

|       | 6.2.7.5  | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])    |    |

|       | 6.2.7.6  | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)       |    |

|       | 6.2.7.7  | Interrupt Request Type Select (IRQTP)                              |    |

|       | 6.2.7.8  | Shared Memory Configuration Register (SHMC)                        | 59 |

|       | 6.2.7.9  | Shared Memory Base Address High Byte Register (SHMBAH)             |    |

|       |          | Shared Memory Base Address Low Byte Register (SHMBAL)              |    |

|       |          | Shared Memory Size Configuration Register (SHMSZ)                  |    |

|       |          | LPC Memory Control (LPCMCTRL)                                      |    |

| 6.2.8 |          | me Clock (RTC) Configuration Registers                             |    |

| 0.2.0 | 6.2.8.1  | Logical Device Activate Register (LDA)                             |    |

|       |          | I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8])  |    |

|       |          | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])    |    |

|       |          | I/O Port Base Address Bits [1:0] for Descriptor 1 (IOBAD1[1:0])    |    |

|       |          | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD1[13:0])   |    |

|       | 6.2.8.6  | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)       |    |

|       | 6.2.8.7  | Interrupt Request Type Select (IRQTP)                              |    |

|       |          |                                                                    |    |

|       | 6.2.8.8  | RAM Lock Register (RLR)                                            | 02 |

|       | 6.2.8.9  |                                                                    |    |

| 000   |          | Month Alarm Register Offset (MONAO)                                |    |

| 6.2.9 | 6.2.9.1  | Management I/F Channel 1 Configuration Registers                   |    |

|       |          | Logical Device Activate Register (LDA)                             |    |

|       | 6.2.9.2  | I/O Port Base Address Bits [15:8] for Descriptor 0 (IOBAD0[15:8])  |    |

|       | 6.2.9.3  | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])    |    |

|       | 6.2.9.4  | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8])  |    |

|       | 6.2.9.5  | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])    |    |

|       | 6.2.9.6  | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)       |    |

| 004   | 6.2.9.7  | Interrupt Request Type Select (IRQTP)                              |    |

| 6.2.1 |          | Management I/F Channel 2 Configuration Registers                   |    |

|       | 6.2.10.1 | Logical Device Activate Register (LDA)                             | 65 |

|       | n ノ 10 ソ | I/O POIT Base Address Bits 115:81 for Descriptor () (IOBAD0115:81) | 65 |

|     |                | I/O Port Base Address Bits [7:0] for Descriptor 0 (IOBAD0[7:0])     |    |

|-----|----------------|---------------------------------------------------------------------|----|

|     | 6.2.10.4       | I/O Port Base Address Bits [15:8] for Descriptor 1 (IOBAD1[15:8])   | 65 |

|     | 6.2.10.5       | I/O Port Base Address Bits [7:0] for Descriptor 1 (IOBAD0[7:0])     | 65 |

|     |                | Interrupt Request Number and Wake-Up on IRQ Enable (IRQNUMX)        |    |

|     |                | Interrupt Request Type Select (IRQTP)                               |    |

|     | 6.2.11 Prograr | mming Guide                                                         | 67 |

| 6.3 |                | y Flash Interface Bridge (SMFI)                                     |    |

|     |                | ?W                                                                  | 69 |

|     |                | <del>2</del> \$                                                     |    |

|     | 6.3.3 Function | n Description                                                       |    |

|     | 6.3.3.1        | Flash Requirement                                                   |    |

|     | 6.3.3.2        | Host to M Bus Translation                                           |    |

|     | 6.3.3.3        | Memory Mapping                                                      | 69 |

|     | 6.3.3.4        | Indirect Memory Read/Write Transaction                              |    |

|     | 6.3.3.5        | Locking Between Host and EC Domains                                 | 70 |

|     | 6.3.3.6        | Host Access Protection                                              |    |

|     | 6.3.3.7        | Response to a Forbidden Access                                      |    |

|     | 6.3.3.8        | Scratch SRAM                                                        | 71 |

|     | 6.3.3.9        | No-wait Mode                                                        |    |

|     |                | Flash Interface                                                     |    |

|     | 6.3.4 EC Inte  | erface Registers                                                    |    |

|     | 6.3.4.1        | FBIU Configuration Register (FBCFG)                                 |    |

|     | 6.3.4.2        | Flash Programming Configuration Register (FPCFG)                    |    |

|     | 6.3.4.3        | Memory Zone Configuration Register (MZCFG)                          |    |

|     | 6.3.4.4        | Static Memory Zone Configuration Register (SMZCFG)                  |    |

|     | 6.3.4.5        | Flash EC Code Banking Select Register (FECBSR)                      |    |

|     | 6.3.4.6        | Flash Memory Size Select Register (FMSSR)                           |    |

|     | 6.3.4.7        | Flash Memory Prescaler Register (FMPSR)                             | 80 |

|     | 6.3.4.8        | Shared Memory EC Control and Status Register (SMECCS)               | 80 |

|     | 6.3.4.9        | Shared Memory Host Semaphore Register (SMHSR)                       | 81 |

|     | 6.3.4.10       | Shared Memory EC Override Read Protect Registers 0-9 (SMECORPR 0-9) | 81 |

|     |                | Shared Memory EC Override Write Protect Registers 0-9 (SMECOWPR0-9) |    |

|     | 6.3.5 Host In  | terface Registers                                                   |    |

|     | 6.3.5.1        | Shared Memory Indirect Memory Address Register 0 (SMIMAR0)          |    |

|     | 6.3.5.2        | Shared Memory Indirect Memory Address Register 1 (SMIMAR1)          |    |

|     | 6.3.5.3        | Shared Memory Indirect Memory Address Register 2 (SMIMAR2)          |    |

|     | 6.3.5.4        | Shared Memory Indirect Memory Address Register 3 (SMIMAR3)          |    |

|     | 6.3.5.5        | Shared Memory Indirect Memory Data Register (SMIMDR)                |    |

|     | 6.3.5.6        | Shared Memory Host Access Protect Register 1-4 (SMHAPR1-4)          |    |

|     |                | Shared Memory Host Semaphore Register (SMHSR)                       |    |

| 6.4 |                | Up Control (SWUC)                                                   |    |

|     |                | €W                                                                  |    |

|     |                | es                                                                  |    |

|     |                | nal Description                                                     |    |

|     | 6.4.3.1        | Wake-Up Status                                                      |    |

|     | 6.4.3.2        | Wake-Up Events                                                      |    |

|     | 6.4.3.3        | Wake-Up Output Events                                               |    |

|     | 6.4.3.4        | Other SWUC Controlled Options                                       |    |

|     |                | terface Registers                                                   |    |

|     | 6.4.4.1        | Wake-Up Event Status Register (WKSTR)                               |    |

|     | 6.4.4.2        | Wake-Up Event Enable Register (WKER)                                |    |

|     | 6.4.4.3        | Wake-Up Signals Monitor Register (WKSMR)                            |    |

|     | 6.4.4.4        | Wake-Up ACPI Status Register (WKACPIR)                              |    |

|     | 6.4.4.5        | Wake-Up SMI Enable Register (WKSMIER)                               |    |

|     | 6.4.4.6        | Wake-Up IRQ Enable Register (WKIRQER)                               |    |

|     | 6.4.5 EC Inte  | erface Registers                                                    | 93 |

|     | 6.4.5.1        | SWUC Control Status 1 Register (SWCTL1)                           |     |

|-----|----------------|-------------------------------------------------------------------|-----|

|     | 6.4.5.2        | SWUC Control Status 2 Register (SWCTL2)                           |     |

|     | 6.4.5.3        | SWUC Control Status 3 Register (SWCTL3)                           |     |

|     | 6.4.5.4        | SWUC Host Configuration Base Address Low Byte Register (SWCBALR)  |     |

|     | 6.4.5.5        | SWUC Host Configuration Base Address High Byte Register (SWCBAHR) |     |

|     | 6.4.5.6        | SWUC Interrupt Enable Register (SWCIER)                           |     |

|     | 6.4.5.7        | SWUC Host Event Status Register (SWCHSTR)                         |     |

|     | 6.4.5.8        | SWUC Host Event Interrupt Enable Register (SWCHIER)               |     |

| 6.5 |                | troller (KBC)                                                     |     |

|     |                | ew                                                                |     |

|     |                | es                                                                |     |

|     |                | onal Description                                                  |     |

|     | 6.5.4 Host Ir  | nterface Registers                                                | 99  |

|     | 6.5.4.1        | KBC Data Input Register (KBDIR)                                   |     |

|     | 6.5.4.2        | KBC Data Output Register (KBDOR)                                  |     |

|     | 6.5.4.3        | KBC Command Register (KBCMDR)                                     |     |

|     | 6.5.4.4        | KBC Status Register (KBSTR)                                       |     |

|     | 6.5.5 EC Into  | erface Registers                                                  | 101 |

|     | 6.5.5.1        | KBC Host Interface Control Register (KBHICR)                      |     |

|     | 6.5.5.2        | KBC Interrupt Control Register (KBIRQR)                           |     |

|     | 6.5.5.3        | KBC Host Interface Keyboard/Mouse Status Register (KBHISR)        |     |

|     | 6.5.5.4        | KBC Host Interface Keyboard Data Output Register (KBHIKDOR)       |     |

|     | 6.5.5.5        | KBC Host Interface Mouse Data Output Register (KBHIMDOR)          | 103 |

|     | 6.5.5.6        | KBC Host Interface Keyboard/Mouse Data Input Register (KBHIDIR)   | 104 |

| 6.6 |                | ement Channel (PMC)                                               |     |

|     | 6.6.1 Overvi   | ew                                                                | 105 |

|     | 6.6.2 Featur   | es                                                                | 105 |

|     | 6.6.3 Function | onal Description                                                  |     |

|     | 6.6.3.1        | General Description                                               | 105 |

|     | 6.6.3.2        | Compatible Mode                                                   | 106 |

|     | 6.6.3.3        | Enhanced PM mode                                                  |     |

|     | 6.6.4 Host Ir  | nterface Registers                                                | 108 |

|     | 6.6.4.1        | PMC Data Input Register (PMDIR)                                   | 109 |

|     | 6.6.4.2        | PMC Data Output Register (PMDOR)                                  | 109 |

|     | 6.6.4.3        | PMC Command Register (PMCMDR)                                     |     |

|     | 6.6.4.4        | Status Register (PMSTR)                                           | 109 |

|     | 6.6.5 EC Into  | erface Registers                                                  | 110 |

|     | 6.6.5.1        | PM Status Register (PMSTS)                                        |     |

|     | 6.6.5.2        | PM Data Out Port (PMDO)                                           | 111 |

|     | 6.6.5.3        | PM Data Out Port with SCI (PMDOSCI)                               | 111 |

|     | 6.6.5.4        | PM Data Out Port with SMI (PMDOSMI)                               | 111 |

|     | 6.6.5.5        | PM Data In Port (PMDI)                                            | 111 |

|     | 6.6.5.6        | PM Data In Port with SCI (PMDISCI)                                | 112 |

|     | 6.6.5.7        | PM Control (PMCTL)                                                | 112 |

|     | 6.6.5.8        | PM Interrupt Control (PMIC)                                       | 113 |

|     | 6.6.5.9        | PM Interrupt Enable (PMIE)                                        |     |

| 6.7 | Real-Time Clo  | ck (RTC)                                                          |     |

|     |                | ew                                                                |     |

|     |                | e                                                                 |     |

|     |                | onal Description                                                  |     |

|     |                | nterface Registers                                                |     |

|     | 6.7.4.1        | RTC Bank 0 Register                                               |     |

|     | ·              | 6.7.4.1.1 Seconds Register (SECREG)                               | 118 |

|     |                | 6.7.4.1.2 Seconds Alarm 1 Register (SECA1REG)                     |     |

|     |                | 6.7.4.1.3 Minutes Register (MINREG)                               |     |

|     |                | 6.7.4.1.4 Minutes Alarm 1 Register (MINA1REG)                     |     |

|    |                | 07445               | Harris Davistas (HDDEO)                   | 440  |

|----|----------------|---------------------|-------------------------------------------|------|

|    |                | 6.7.4.1.5           | Hours Register (HRREG)                    |      |

|    |                | 6.7.4.1.6           | Hours Alarm 1 Register (HRA1REG)          |      |

|    |                | 6.7.4.1.7           | Day Of Week Register (DOWREG)             |      |

|    |                | 6.7.4.1.8           | Date Of Month Register (DOMREG)           |      |

|    |                | 6.7.4.1.9           | Month Register (MONREG)                   |      |

|    |                | 6.7.4.1.10          | Year Register (YRREG)                     |      |

|    |                | 6.7.4.1.11          | RTC Control Register A (CTLREGA)          |      |

|    |                | 6.7.4.1.12          | RTC Control Register B (CTLREGB)          |      |

|    |                | 6.7.4.1.13          | RTC Control Register C (CTLREGC)          |      |

|    |                | 6.7.4.1.14          | RTC Control Register D (CTLREGD)          | 123  |

|    |                | 6.7.4.1.15          | Date of Month Alarm 1 Register (DOMA1REG) | 123  |

|    |                | 6.7.4.1.16          | Month Alarm 1 Register (MONA1REG)         | 123  |

|    | 6.7.4          | .2 RTC Bank 1       | Register                                  |      |

|    |                | 6.7.4.2.1           | Seconds Alarm 2 Register (SECA2REG)       |      |

|    |                | 6.7.4.2.2           | Minutes Alarm 2 Register (MINA2REG)       |      |

|    |                | 6.7.4.2.3           | Hours Alarm 2 Register (HRA2REG)          |      |

|    |                | 6.7.4.2.4           | Date of Month Alarm 2 Register (DOMA2REG) |      |

|    |                | 6.7.4.2.5           | Month Alarm 2 Register (MONA2REG)         |      |

|    | 6.7.4          |                     | ister                                     |      |

|    | 0.1.1          | 6.7.4.3.1           | RTC Index Register of Bank 0 (RIRB0)      |      |

|    |                | 6.7.4.3.2           | RTC Data Register of Bank 0 (RDRB0)       |      |

|    |                | 6.7.4.3.3           | RTC Index Register of Bank 1 (RIRB1)      |      |

|    |                | 6.7.4.3.4           | RTC Data Register of Bank 1 (RDRB1)       | 125  |

| _  | CC Damain Fund |                     |                                           |      |

| ١. |                |                     |                                           |      |

|    |                |                     | EC)                                       |      |

|    |                |                     |                                           |      |

|    |                |                     |                                           |      |

|    |                |                     |                                           |      |

|    |                |                     | on                                        |      |

|    |                |                     | n                                         |      |

|    |                |                     |                                           |      |

|    |                |                     |                                           |      |

|    | 7.1.8 Idle     | e and Doze/Sleep    | Mode                                      | 142  |

|    | 7.1.9 EC       |                     | Description                               |      |

|    | 7.1.9          | 0.1 Port 0 Regist   | ter (P0R)                                 | 143  |

|    | 7.1.9          | 0.2 Stack Pointe    | r Register (SPR)                          | 143  |

|    | 7.1.9          | 0.3 Data Pointer    | Low Register (DPLR)                       | 143  |

|    | 7.1.9          | 0.4 Data Pointer    | High Register (DPHR)                      | 144  |

|    | 7.1.9          | 0.5 Data Pointer    | 1 Low Register (DP1LR)                    | 144  |

|    | 7.1.9          | 0.6 Data Pointer    | 1 High Register (DP1HR)                   | 144  |

|    | 7.1.9          |                     | Select Register (DPSR)                    |      |

|    | 7.1.9          |                     | ol Register (PCON)                        |      |

|    | 7.1.9          |                     | ol Register (TCON)                        |      |

|    |                |                     | Register (TMOD)                           |      |

|    |                |                     | Byte Register (TL0R)                      |      |

|    |                |                     | Byte Register (TL1R)                      |      |

|    |                |                     | Byte Register (TH0R)                      |      |

|    |                |                     | Byte Register (TH1R)                      |      |

|    |                |                     | Register (CKCON)                          |      |

|    |                |                     | ter (P1R)                                 |      |

|    | 7.1.8          | 17 Sorial Dort      | ontrol Register (SCON)                    | 1/10 |

|    |                |                     |                                           |      |

|    |                |                     | uffer Register (SBUFR)                    |      |

|    |                |                     | ter (P2R)                                 |      |

|    |                |                     | ble Register (IE)                         |      |

|    |                |                     | ter (P3R)                                 |      |

|    | 7.1.8          | ı.∠∠ ınterrupt Pric | ority Register (IP)                       | 150  |

|     | 7.1.9.23       | Status Register (STATUS)                                | . 150 |

|-----|----------------|---------------------------------------------------------|-------|

|     | 7.1.9.24       | Timer 2 Control Register (T2CON)                        | . 150 |

|     |                | Timer Mode Register (T2MOD)                             |       |

|     |                | Timer 2 Capture Low Byte Register (RCAP2LR)             |       |

|     |                | Timer 2 Capture High Byte Register (RCAP2HR)            |       |

|     |                | Timer 2 Low Byte Register (TL2R)                        |       |

|     | 7.1.9.20       | Timer 2 High Byte Register (TH2R)                       | 151   |

|     | 7.1.9.29       | Program Status Word Register (PSW)                      | 152   |

|     | 7.1.9.30       | Watch Day Times Control Deviator (WDTCON)               | 152   |

|     | 7.1.9.31       | Watch Dog Timer Control Register (WDTCON)               | . 152 |

|     |                | Accumulator Register (ACC)                              |       |

|     |                | Power Down Control Register (PDCON)                     |       |

|     |                | B Register (BR)                                         |       |

|     |                | mming Guide                                             |       |

| 7.2 |                | oller (INTC)                                            |       |

|     | 7.2.1 Overvie  | ew                                                      | . 155 |

|     | 7.2.2 Feature  | 98                                                      | . 155 |

|     | 7.2.3 Function | nal Description                                         | . 155 |

|     | 7.2.3.1        | Power Fail Interrupt                                    |       |

|     | 7.2.3.2        | Programmable Interrupts                                 |       |

|     |                | erface Registers                                        |       |

|     | 7.2.4.1        | Interrupt Status Register 0 (ISR0)                      |       |

|     | 7.2.4.2        | Interrupt Status Register 1 (ISR1)                      |       |

|     | 7.2.4.3        | Interrupt Status Register 7 (ISR2)                      |       |

|     |                |                                                         |       |

|     | 7.2.4.4        | Interrupt Status Register 3 (ISR3)                      |       |

|     | 7.2.4.5        | Interrupt Enable Register 0 (IER0)                      |       |

|     | 7.2.4.6        | Interrupt Enable Register 1 (IER1)                      |       |

|     | 7.2.4.7        | Interrupt Enable Register 2 (IER2)                      |       |

|     | 7.2.4.8        | Interrupt Enable Register 3 (IER3)                      |       |

|     | 7.2.4.9        | Interrupt Edge/Level-Triggered Mode Register 0 (IELMR0) |       |

|     |                | Interrupt Edge/Level-Triggered Mode Register 1 (IELMR1) |       |

|     |                | Interrupt Edge/Level-Triggered Mode Register 2 (IELMR2) |       |

|     | 7.2.4.12       | Interrupt Edge/Level-Triggered Mode Register 3 (IELMR3) | . 160 |

|     | 7.2.4.13       | Interrupt Polarity Register 0 (IPOLR0)                  | . 160 |

|     |                | Interrupt Polarity Register 1 (IPOLR1)                  |       |

|     |                | Interrupt Polarity Register 2 (IPOLR2)                  |       |

|     |                | Interrupt Polarity Register 3 (IPOLR3)                  |       |

|     |                | Interrupt Vector Register (IVCT)                        |       |

|     |                | 8032 INT0# Status (INT0ST)                              |       |

|     |                | Power Fail Register (PFAILR)                            |       |

|     |                | nterrupt Assignments                                    |       |

|     |                | ·                                                       |       |

| 7 2 |                | mming Guide                                             |       |

| 7.3 | •              | rol (WUC)                                               |       |

|     |                | ew                                                      |       |

|     |                | es                                                      |       |

|     |                | onal Description                                        |       |

|     |                | erface Registers                                        |       |

|     | 7.3.4.1        | Wake-Up Edge Mode Register (WUEMR1)                     | . 167 |

|     | 7.3.4.2        | Wake-Up Edge Mode Register (WUEMR2)                     |       |

|     | 7.3.4.3        | Wake-Up Edge Mode Register (WUEMR3)                     |       |

|     | 7.3.4.4        | Wake-Up Edge Mode Register (WUEMR4)                     | . 168 |

|     | 7.3.4.5        | Wake-Up Edge Sense Register (WUESR1)                    |       |

|     | 7.3.4.6        | Wake-Up Edge Sense Register (WUESR2)                    |       |

|     | 7.3.4.7        | Wake-Up Edge Sense Register (WUESR3)                    |       |

|     | 7.3.4.8        | Wake-Up Edge Sense Register (WUESR4)                    |       |

|     | 7.3.4.9        | Wake-Up Enable Register (WUENR1)                        |       |

|     |                |                                                         | 170   |

|     |                |                                                         |       |

|     | 7.3.4.11 Wake        | -Up Enable Register (WUENR3)                  | 170                |

|-----|----------------------|-----------------------------------------------|--------------------|

|     |                      | -Up Enable Register (WUENR4)                  |                    |

|     |                      | ssignments                                    |                    |

|     |                      | Guide                                         |                    |

| 7.4 |                      | n Controller                                  |                    |

|     | 7.4.1 Overview       |                                               | 173                |

|     | 7.4.2 Features       |                                               | 173                |

|     | 7.4.3 EC Interface F | Registers                                     | 173                |

|     | 7.4.3.1 Keybo        | pard Scan Out Low Byte Data Register (KSOLR)  | 173                |

|     | 7.4.3.2 Keybo        | pard Scan Out High Byte Data Register (KSOHR) | 173                |

|     | 7.4.3.3 Keybo        | pard Scan Out Control Register (KSOCTRLR)     | 173                |

|     |                      | pard Scan In Data Register (KSIR)             |                    |

|     | 7.4.3.5 Keybo        | pard Scan In Control Register (KSICTRLR)      | 174                |

| 7.5 | General Purpose I/O  | Port (GPIO)                                   | 175                |

|     | 7.5.1 Overview       |                                               | 175                |

|     |                      |                                               | 175                |

|     |                      | Registers                                     |                    |

|     | 7.5.3.1 Gene         | ral Control Register (GCR)                    | 176                |

|     |                      | Oata Registers A-I (GPDRA-GPDRI)              |                    |

|     |                      | Control n Registers (GPCRn, n = A0-I7)        |                    |

|     |                      | t Type Registers A-I (GPOTA-GPOTI)            |                    |

|     |                      | ction Selection                               |                    |

|     |                      | Guide                                         |                    |

| 7.6 |                      | Management Controller (ECPM)                  |                    |

|     |                      |                                               |                    |

|     |                      |                                               |                    |

|     |                      | Registers                                     |                    |

|     |                      | Frequency Select Register (CFSELR)            |                    |

|     |                      | Gating Control 1 Register (CGCTRL1R)          |                    |

|     |                      | Gating Control 2 Register (CGCTRL2R)          |                    |

|     |                      | Control (PLLCTRL)                             |                    |

| 7.7 |                      | IB)                                           |                    |

|     |                      |                                               |                    |

|     |                      |                                               |                    |

|     |                      | scription                                     |                    |

|     |                      | JS Master Interface                           |                    |

|     |                      | JS Slave Interface                            |                    |

|     |                      | JS Porting Guide                              |                    |

|     |                      | Registers<br>Status Register (HOSTA)          |                    |

|     |                      | Control Register (HOCTL)                      |                    |

|     |                      | Command Register (HOCMD)                      |                    |

|     |                      | mit Slave Address Register (TRASLA)           |                    |

|     |                      | D Register (D0REG)                            |                    |

|     |                      | 1 Register (D1REG)                            |                    |

|     |                      | Block Data Byte Register (HOBDB)              |                    |

|     |                      | et Error Check Register (PECERC)              |                    |

|     |                      | ve Slave Address Register (RESLADR)           |                    |

|     |                      | Data Register (SLDA)                          |                    |

|     | 7.7.4.10 Slave       | JS Pin Control Register (SMBPCTL)             | 193<br>10 <i>4</i> |

|     |                      | Status Register (SLSTA)                       |                    |

|     | 7.7.4.12 Slave       | Interrupt Control Register (SICR)             | 105                |

|     |                      | Device Address Register (NDADR)               |                    |

|     |                      | Data Low Byte Register (NDLB)                 |                    |

|     | 7.7.4 16 Notify      | Data High Byte Register (NDHB)                | 195                |

|     |                      | Control Register 2 (HOCTL2)                   |                    |

|      | 7.7.4.18 4.7 μs Register (4P7USREG)                                         | 196 |

|------|-----------------------------------------------------------------------------|-----|

|      | 7.7.4.19 4.0 μs Register (4P0USREG)                                         | 196 |

|      | 7.7.4.20 300 ns Register (300NSREG)                                         |     |

|      | 7.7.4.21 250 ns Register (250NSREG)                                         |     |

|      | 7.7.4.22 25 ms Register (25MSREG)                                           |     |

|      | 7.7.4.23 45.3 μs Low Register (45P3USLREG)                                  | 197 |

|      | 7.7.4.24 45.3 μs High Register (45P3USHREG)                                 |     |

| 7.8  | PS/2 Interface                                                              |     |

| 1.0  |                                                                             |     |

|      |                                                                             |     |

|      | 7.8.2 Features                                                              |     |

|      | 7.8.3 Functional Description                                                |     |

|      | 7.8.3.1 Hardware Mode Selected                                              |     |

|      | 7.8.3.2 Software Mode Selected                                              |     |

|      | 7.8.4 EC Interface Registers                                                | 199 |

|      | 7.8.4.1 PS/2 Control Register 1-4 (PSCTL1-4)                                | 200 |

|      | 7.8.4.2 PS/2 Interrupt Control Register 1-4 (PSINT1-4)                      |     |

|      | 7.8.4.3 PS/2 Status Register 1-4 (PSSTS1-4)                                 |     |

|      | 7.8.4.4 PS/2 Data Register 1-4 (PSDAT1-4)                                   |     |

| 7.9  | Digital To Analog Converter (DAC)                                           |     |

| 1.5  | 7.9.1 Overview                                                              |     |

|      |                                                                             |     |

|      | 7.9.2 Feature                                                               |     |

|      | 7.9.3 Functional Description                                                |     |

|      | 7.9.4 EC Interface Registers                                                |     |

|      | 7.9.4.1 DAC Control Register (DACCTRL)                                      |     |

|      | 7.9.4.2 DAC Data Channel 0~3 Register (DACDAT0~3)                           | 203 |

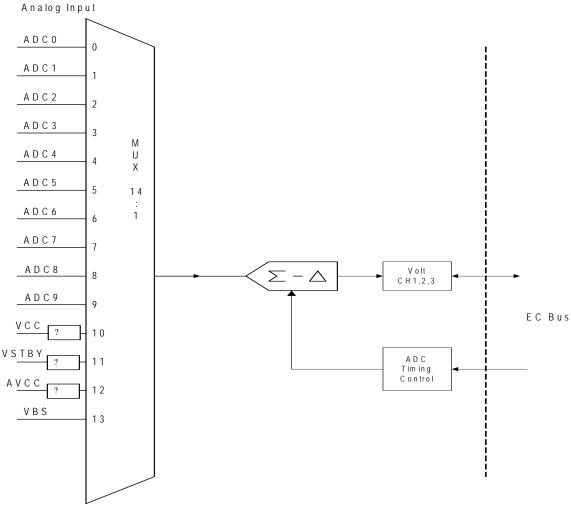

| 7.10 | Analog to Digital Converter (ADC)                                           | 204 |

|      | 7.10.1 Overview                                                             | 204 |

|      | 7.10.2 Features                                                             |     |

|      | 7.10.3 Functional Description                                               |     |

|      | 7.10.3.1 ADC General Description                                            |     |

|      | 7.10.3.2 Voltage Measurement                                                |     |

|      |                                                                             |     |

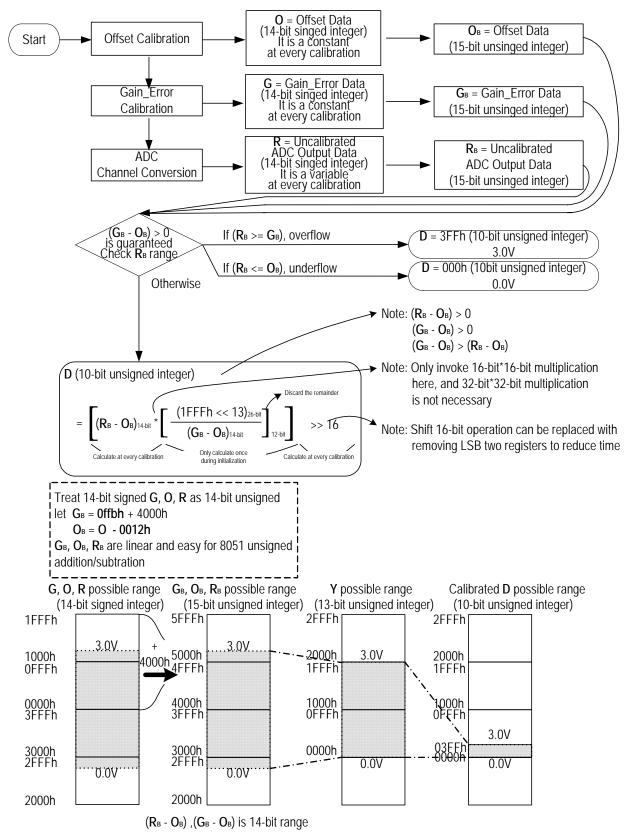

|      | 7.10.3.3 ADC Operation                                                      |     |

|      | 7.10.4 EC Interface Registers                                               |     |

|      | 7.10.4.1 ADC Status Register (ADCSTS)                                       |     |

|      | 7.10.4.2 ADC Configuration Register (ADCCFG)                                |     |

|      | 7.10.4.3 ADC Clock Control Register (ADCCTL)                                | 208 |

|      | 7.10.4.4 ADC Delay Control Register (ADCDCTL)                               | 209 |

|      | 7.10.4.5 Calibration Data Control Register (KDCTL)                          | 209 |

|      | 7.10.4.6 Voltage Channel 1 Control Register (VCH1CTL)                       |     |

|      | 7.10.4.7 Volt Channel 1 Data Buffer LSB (VCH1DATL)                          |     |

|      | 7.10.4.8 Volt Channel 1 Data Buffer MSB (VCH1DATM)                          |     |

|      | 7.10.4.9 Voltage Channel 2 Control Register (VCH2CTL)                       |     |

|      |                                                                             |     |

|      | 7.10.4.10 Volt Channel 2 Data Buffer LSB (VCH2DATL)                         |     |

|      | 7.10.4.11 Volt Channel 2 Data Buffer MSB (VCH2DATM)                         |     |

|      | 7.10.4.12 Voltage Channel 3 Control Register (VCHN3CTL)                     |     |

|      | 7.10.4.13 Volt Channel 3 Data Buffer LSB (VCH3DATL)                         |     |

|      | 7.10.4.14 Volt Channel 3 Data Buffer MSB (VCH3DATM)                         |     |

|      | 7.10.4.15 Volt High Scale Calibration Data Buffer LSB (VHSCDBL)             | 213 |

|      | 7.10.4.16 Volt High Scale Calibration Data Buffer MSB (VHSCDBM)             |     |

|      | 7.10.4.17 Volt High Scale Gain-Error Calibration Data Buffer LSB (VHSGCDBL) |     |

|      | 7.10.4.18 Volt High Scale Gain-Error Calibration Data Buffer MSB (VHSGCDBM) |     |

|      | 7.10.5 ADC Programming Guide                                                |     |

| 7 11 | PWM and SmartAuto Fan Control (PWM)                                         |     |

| 1.11 |                                                                             |     |

|      | 7.11.1 Overview                                                             |     |

|      | 7.11.2 Features                                                             |     |

|      | 7.11.3 Functional Description                                               | 218 |

|      | 7.11.3.1 General Description                                     |     |

|------|------------------------------------------------------------------|-----|

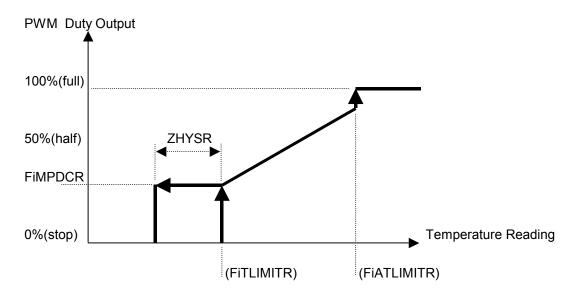

|      | 7.11.3.2 SmartAuto Fan Control Mode                              |     |

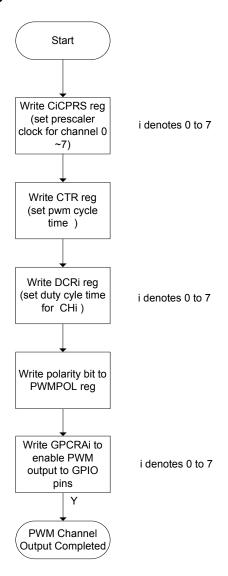

|      | 7.11.3.3 Manual Fan Control Mode                                 | 219 |

|      | 7.11.4 EC Interface Registers                                    | 221 |

|      | 7.11.4.1 Channel 0 Clock Prescaler Register (C0CPRS)             | 221 |

|      | 7.11.4.2 Cycle Time Register (CTR)                               |     |

|      | 7.11.4.3 PWM Duty Cycle Register 0 to 7(DCRi)                    | 222 |

|      | 7.11.4.4 PWM Polarity Register (PWMPOL)                          |     |

|      | 7.11.4.5 Prescaler Clock Frequency Select Register (PCFSR)       |     |

|      | 7.11.4.6 Prescaler Clock Source Select Group Low(PCSSGL)         |     |

|      | 7.11.4.7 Prescaler Clock Source Select Group High(PCSSGh)        | 224 |

|      | 7.11.4.8 Fan 1 Configuration Register (FAN1CNF)                  |     |

|      | 7.11.4.9 Fan 2 Configuration Register (FAN2CNF)                  |     |

|      | 7.11.4.10 SmartAuto Fan 1 Speed Range Register (AF1SRR)          |     |

|      | 7.11.4.11 SmartAuto Fan 2 Speed Range Register (AF2SRR)          |     |

|      | 7.11.4.12 Min/Off PWM Limit Register (MOPL)                      |     |

|      | 7.11.4.13 Fan 1 Minimum PWM Duty Cycle Register (F1MPDCR)        | 228 |

|      | 7.11.4.14 Fan 2 Minimum PWM Duty Cycle Register (F2MPDCR)        |     |

|      | 7.11.4.15 Fan 1 Temperature LIMIT Register (F1TLIMITR)           |     |

|      | 7.11.4.16 Fan 2 Temperature LIMIT Register (F2TLIMITR)           |     |

|      | 7.11.4.17 Fan 1 Absolute Temperature LIMIT Register (F1ATLIMITR) |     |

|      | 7.11.4.18 Fan 2 Absolute Temperature LIMIT Register (F2ATLIMITR) |     |

|      | 7.11.4.19 Zone Hysteresis Register (ZHYSR)                       | 220 |

|      | 7.11.4.20 Fan 1 Temperature Record Register (F1TRR)              |     |

|      | 7.11.4.21 Fan 2 Temperature Record Register (F2TRR)              |     |

|      | 7.11.4.22 Fan 1 Tachometer LSB Reading Register (F1TLRR)         | 230 |

|      | 7.11.4.23 Fan 1 Tachometer MSB Reading Register (F1TMRR)         | 230 |

|      | 7.11.4.24 Fan 2 Tachometer LSB Reading Register (F2TLRR)         |     |

|      | 7.11.4.25 Fan 2 Tachometer MSB Reading Register (F2TMRR)         |     |

|      | 7.11.4.26 Zone Interrupt Status Control Register (ZINTSCR)       |     |

|      | 7.11.4.27 Zone Temperature Interrupt Enable Register (ZTIER)     |     |

|      | 7.11.4.28 Channel 4 Clock Prescaler Register (C4CPRS)            |     |

|      | 7.11.4.29 Channel 4 Clock Prescaler MSB Register (C4MCPRS)       | 232 |

|      | 7.11.4.30 Channel 6 Clock Prescaler MSB Register (C6MCPRS)       |     |

|      | 7.11.4.31 Channel 6 Clock Prescaler Register (C6CPRS)            |     |

|      | 7.11.4.32 Channel 7 Clock Prescaler MSB Register (C7MCPRS)       |     |

|      | 7.11.4.33 Channel 7 Clock Prescaler Register (C7CPRS)            |     |

|      | 7.11.5 PWM Programming Guide                                     |     |

| 7 12 | EC Access to Host Controlled Modules (EC2I Bridge)               |     |

| 1.12 | 7.12.1 Overview                                                  |     |

|      | 7.12.2 Features                                                  |     |

|      | 7.12.3 Functional Description                                    |     |

|      | 7.12.4 EC Interface Registers                                    |     |

|      | 7.12.4.1 Indirect Host I/O Address Register (IHIOA)              |     |

|      | 7.12.4.2 Indirect Host Data Register (IHD)                       |     |

|      | 7.12.4.3 Lock Super I/O Host Access Register (LSIOHA)            |     |

|      | 7.12.4.4 Super I/O Access Lock Violation Register (SIOLV)        |     |

|      | 7.12.4.5 EC to I-Bus Modules Access Enable Register (IBMAE)      |     |

|      | 7.12.4.6 I-Bus Control Register (IBCTL)                          |     |

|      | 7.12.4.0 I-Bus Control Register (IBCTL)                          |     |

| 7 12 | Hardware Strap (HWS)                                             |     |

| 1.13 |                                                                  |     |

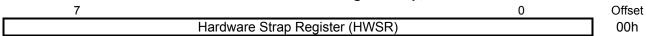

|      | 7.13.1 Overview                                                  |     |

|      | 7.13.2 EC Interface Registers                                    |     |

| 711  |                                                                  |     |

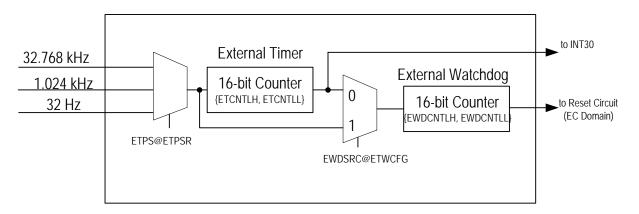

| 1.14 | External Timer and External Watchdog (ETWD)                      |     |

|      | 7.14.1 Overview                                                  | 243 |

| 7.14.2 Features                                                                                   |     |

|---------------------------------------------------------------------------------------------------|-----|

| 7.14.3 Functional Description                                                                     |     |

| 7.14.3.1 External Timer Operation                                                                 |     |

| 7.14.3.2 External WDT Operation                                                                   |     |

| 7.14.4.1 External Timer/WDT Configuration Register (ETWCFG)                                       |     |

| 7.14.4.2 External Timer Prescaler Register (ETPSR)                                                |     |

| 7.14.4.3 External Timer Counter High Byte (ETCNTLHR)                                              |     |

| 7.14.4.4 External Timer Counter Low Byte (ETCNTLLR)                                               |     |

| 7.14.4.5 External Timer/WDT Control Register (ETWCTRL)                                            |     |

| 7.14.4.6 External WDT Counter High Byte (EWDCNTLHR)                                               |     |

| 7.14.4.7 External WDT Counter (EWDCNTLLR)                                                         |     |

| 7.14.4.9 Reset Scratch Register (RSTSCR)                                                          |     |

| 7.14.4.10 Chip Version (ECHIPVER)                                                                 |     |

| 7.15 Print Port (PP)                                                                              |     |

| 7.15.1 Overview                                                                                   |     |

| 7.15.2 Features                                                                                   |     |

| 7.15.3 Functional Description                                                                     |     |

| 7.15.3.2 In-System Programming Operation                                                          |     |

| 8. DC Characteristics                                                                             |     |

| Applied Voltage of VSTBY, VCC, AVCC, VBAT 0.3V to +3.6V                                           |     |

| 9. AC Characteristics                                                                             | 253 |

| 10. Analog Device Characteristics                                                                 | 261 |

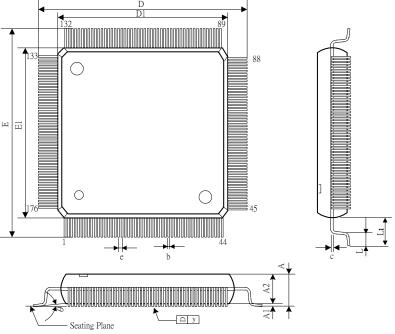

| 11. Package Information                                                                           | 263 |

| 12. Ordering Information                                                                          | 267 |

|                                                                                                   |     |

| FIGURES                                                                                           |     |

| Figure 3-1. Host/Flash and EC/Flash Mapping (General)                                             |     |

| Figure 3-2. Host/Flash and EC/Flash Mapping (Flash Size = 512k, EC Code = 64k, No User-Deexample) |     |

| Figure 3-3. EC 8032 Data/Code Memory Map                                                          | 9   |

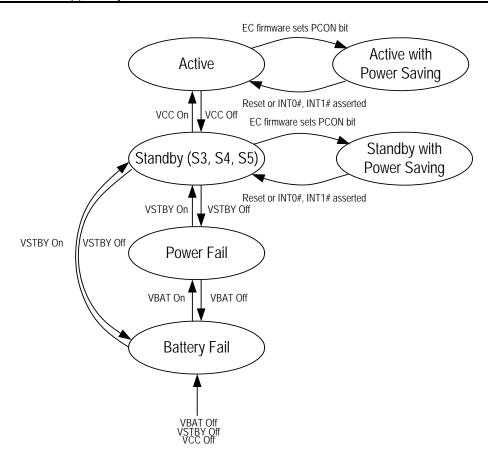

| Figure 5-1. Power State Transitions                                                               | 23  |

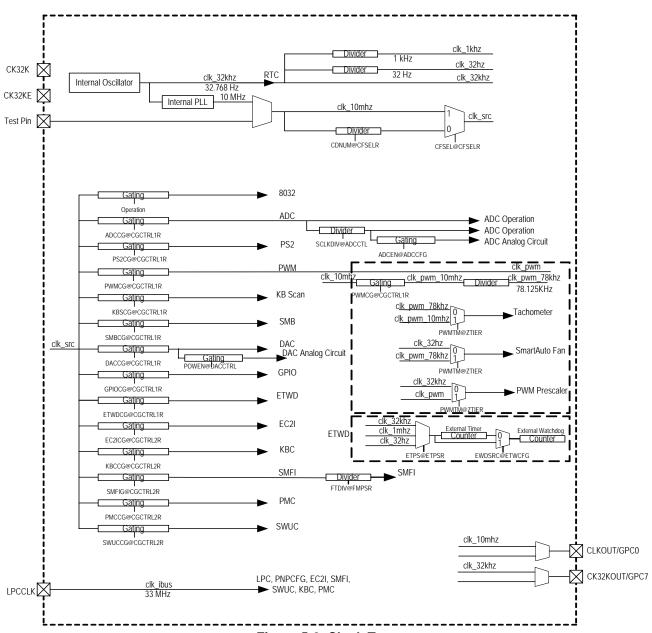

| Figure 5-2. Clock Tree                                                                            | 31  |

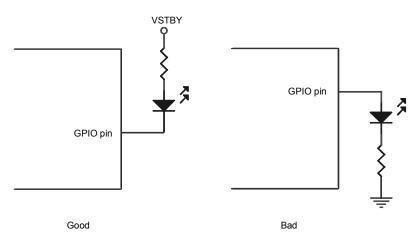

| Figure 5-3. LED connection                                                                        | 37  |

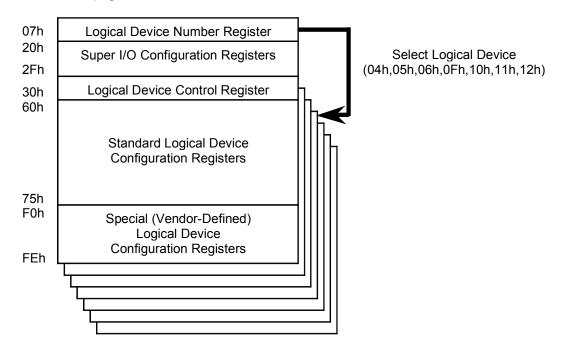

| Figure 6-1. Host View Register Map via Index-Data Pair                                            | 47  |

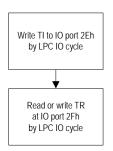

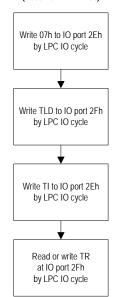

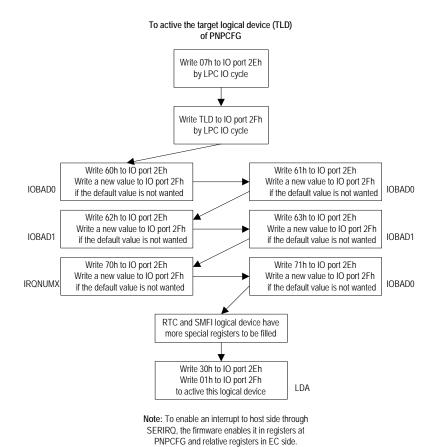

| Figure 6-2. Program Flow Chart for PNPCFG                                                         | 68  |

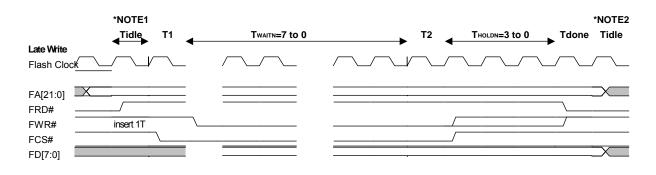

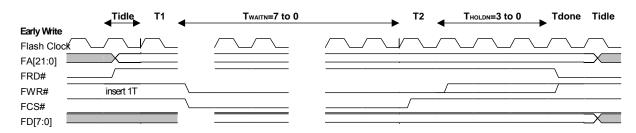

| Figure 6-3. Late Write and Early Write                                                            | 73  |

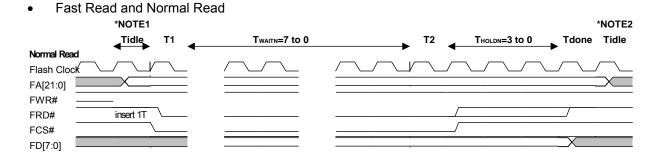

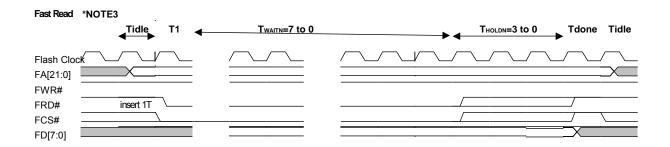

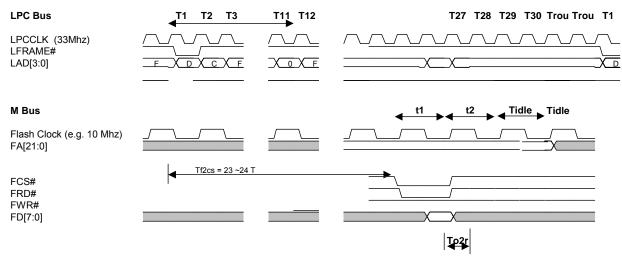

| Figure 6-4. Fast Read and Normal Read                                                             | 73  |

| Figure 6-5. Minimum Latency Timing of Flash Memory Read Cycle                                     | 74  |

| Figure 6-6. Minimum Latency Timing of Flash Memory Read Cycle in LPC Burst                        | 75  |

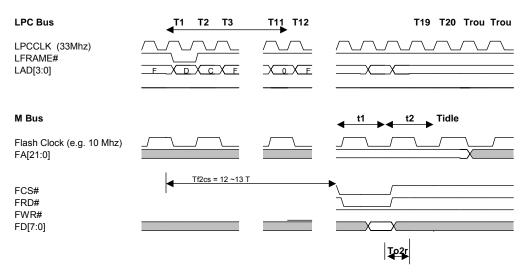

| Figure 6-7. Minimum Latency Timing of Flash Memory Write Cycle                                    | 75  |

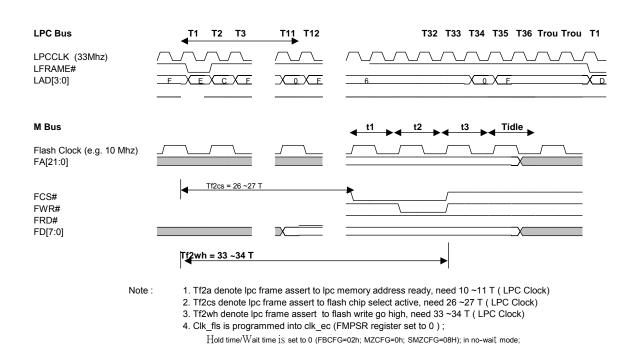

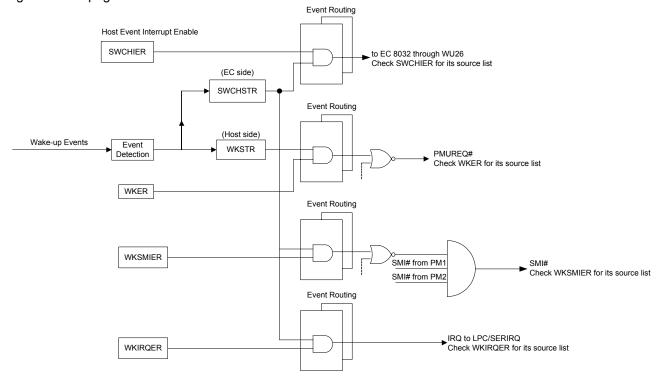

| Figure 6-8. Wakeup Event and Gathering Scheme                                                     | 86  |

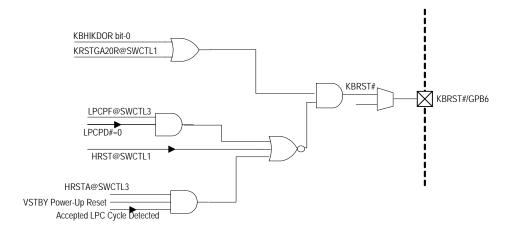

| Figure 6-9. KBRST# Output Scheme                                                                  | 89  |

| Figure 6-10. GA20 Output Scheme                                                                   | 89  |

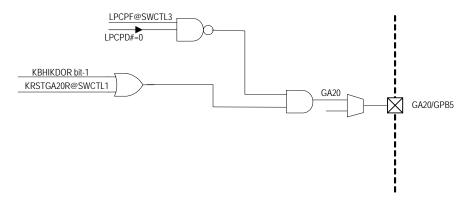

| Figure 6-11. KBC Host Interface Block Diagram                                                     | 98  |

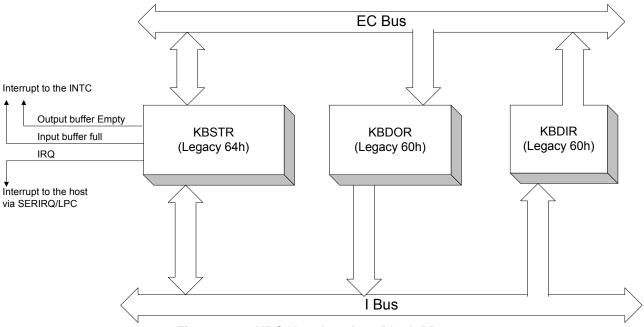

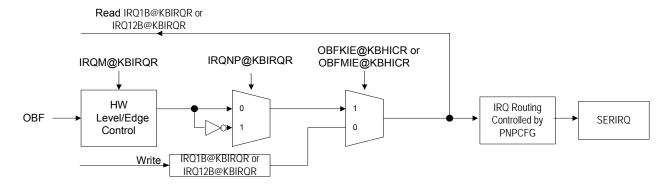

| Figure 6-12. IRQ Control in KBC Module                                         | 99  |

|--------------------------------------------------------------------------------|-----|

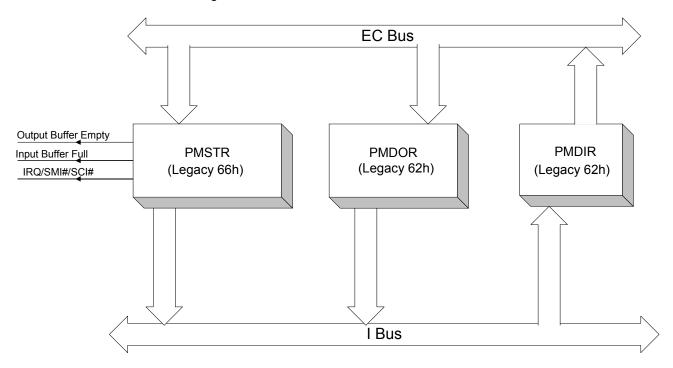

| Figure 6-13. PMC Host Interface Block Diagram                                  | 105 |

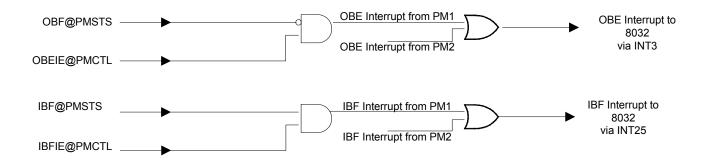

| Figure 6-14. EC Interrupt Request for PMC                                      | 106 |

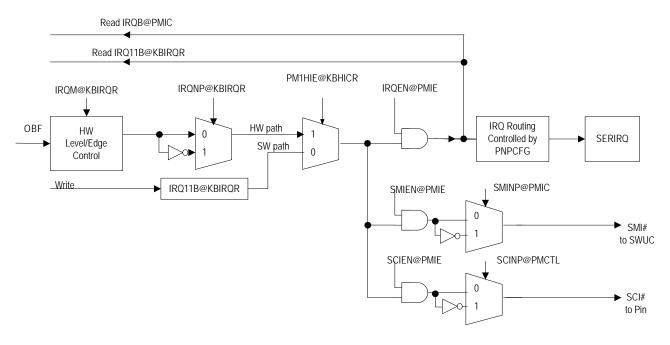

| Figure 6-15. IRQ/SCI#/SMI# Control in PMC Compatible Mode                      | 107 |

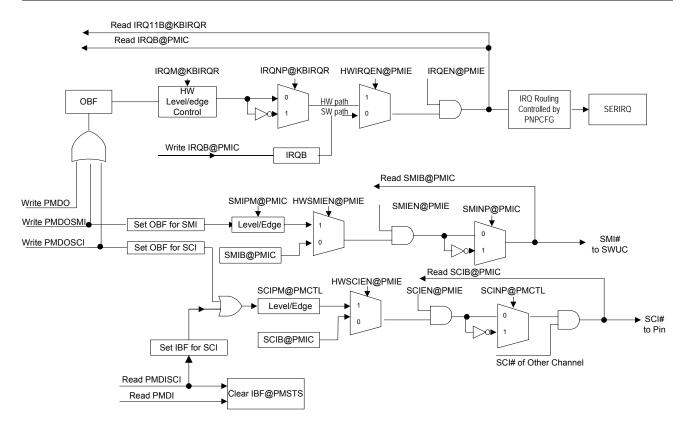

| Figure 6-16. IRQ/SCI#/SMI# Control in PMC Enhanced Mode                        | 108 |

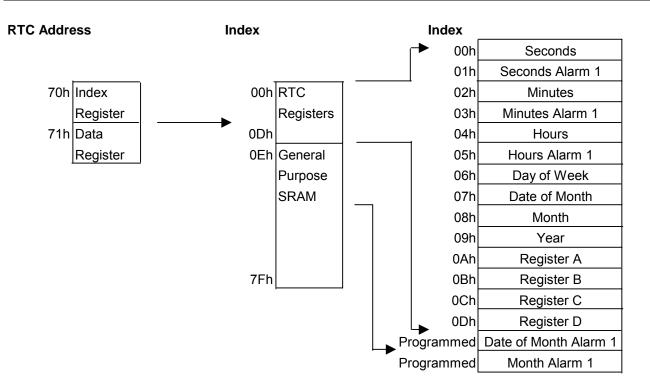

| Figure 6-17. Register Map of RTC                                               | 117 |

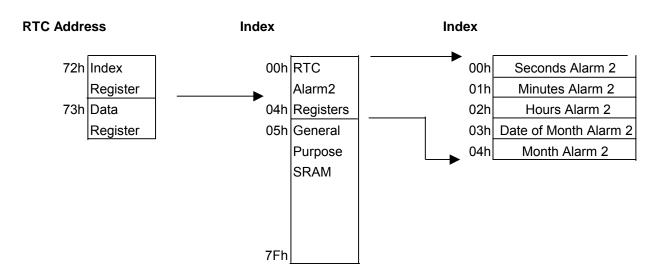

| Figure 7-1. Interrupt Control System Configuration                             | 129 |

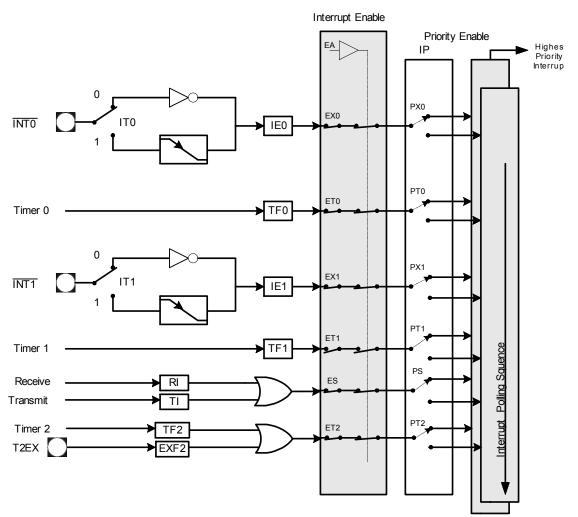

| Figure 7-2. Interrupt Response Time                                            | 131 |

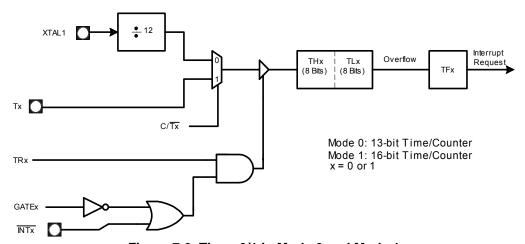

| Figure 7-3. Timer 0/1 in Mode 0 and Mode 1                                     | 131 |

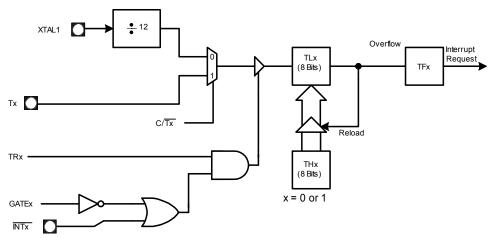

| Figure 7-4. Timer 0/1 in Mode 2, Auto-Reload                                   | 132 |

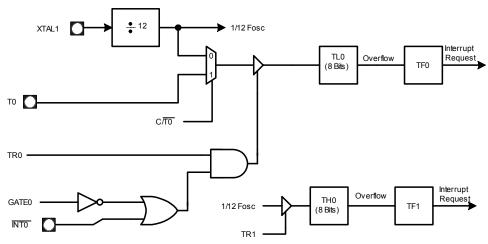

| Figure 7-5. Timer 0 in Mode 3 Two 8-bit Timers                                 | 132 |

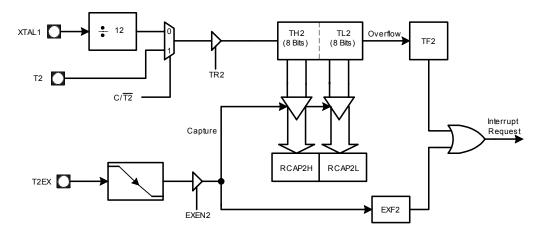

| Figure 7-6. Timer 2: Capture Mode                                              | 134 |

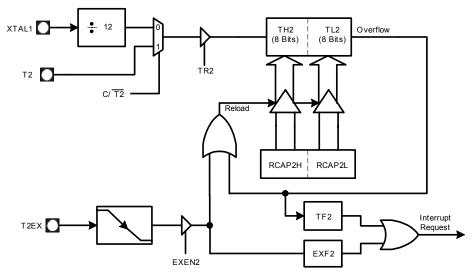

| Figure 7-7. Timer 2: Auto Reload (DECN = 0)                                    | 135 |

| Figure 7-8. Timer 2: Auto Reload Mode (DECN = 1)                               | 135 |

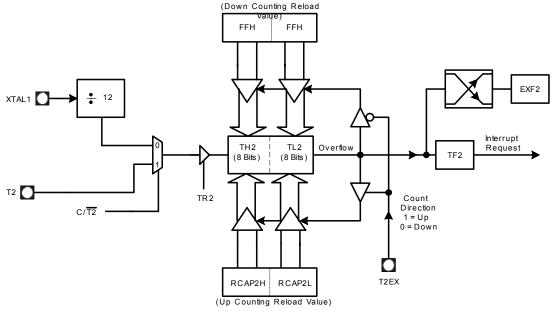

| Figure 7-9. Timer 2: Clock Out Mode                                            | 136 |

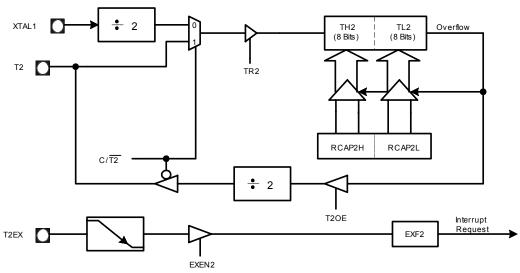

| Figure 7-10. Watchdog Timer                                                    | 137 |

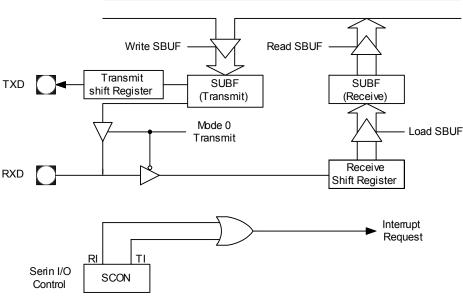

| Figure 7-11. Serial Port Block Diagram                                         | 138 |

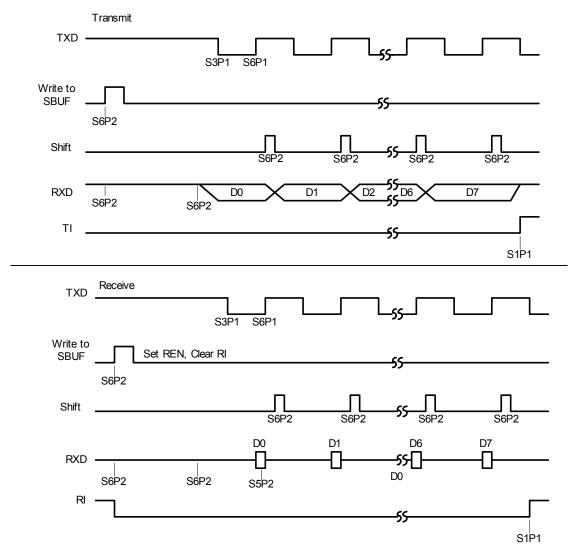

| Figure 7-12. Mode 0 Timing                                                     | 139 |

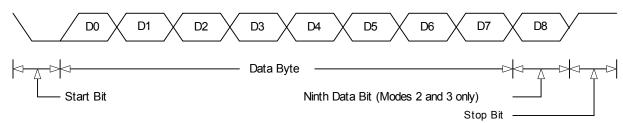

| Figure 7-13. Data Frame (Mode 1, 2 and 3)                                      | 140 |

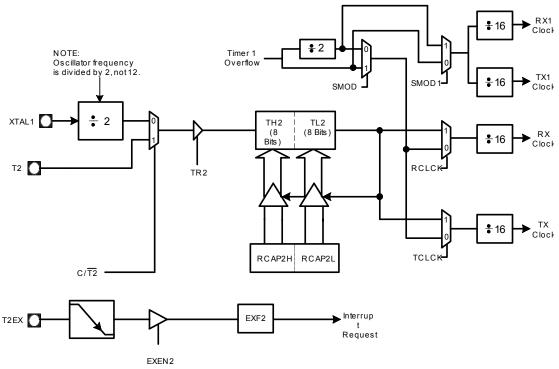

| Figure 7-14. Timer 2 in Baud Rate Generator Mode                               | 142 |

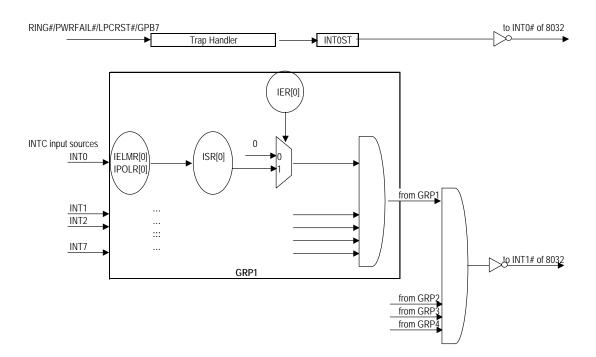

| Figure 7-15. INTC Simplified Digram                                            | 165 |

| Figure 7-16. Program Flow Chart for INTC                                       | 166 |

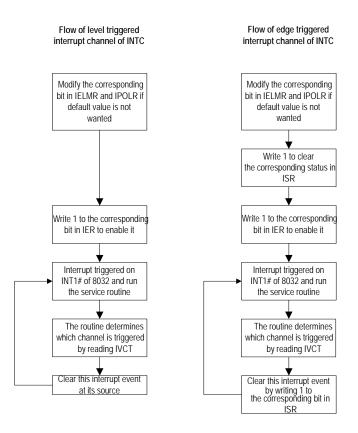

| Figure 7-17. WUC Simplified Digram                                             | 172 |

| Figure 7-18. Program Flow Chart for WUC                                        | 172 |

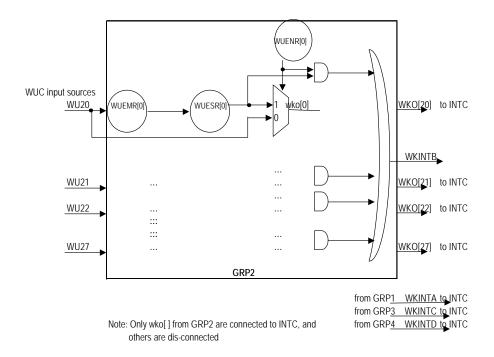

| Figure 7-19. GPIO Simplified Diagram                                           | 181 |

| Figure 7-20. ADC Channels Control Diagram                                      | 204 |

| Figure 7-21. ADC Software Calibration Flow                                     | 216 |

| Figure 7-22. ADC Software Calibration Flow in a Special Case                   | 217 |

| Figure 7-23. SmartAuto Fan PWM output vs Temperature Reading                   | 219 |

| Figure 7-24. Program Flow Chart for PWM Channel Output                         | 234 |

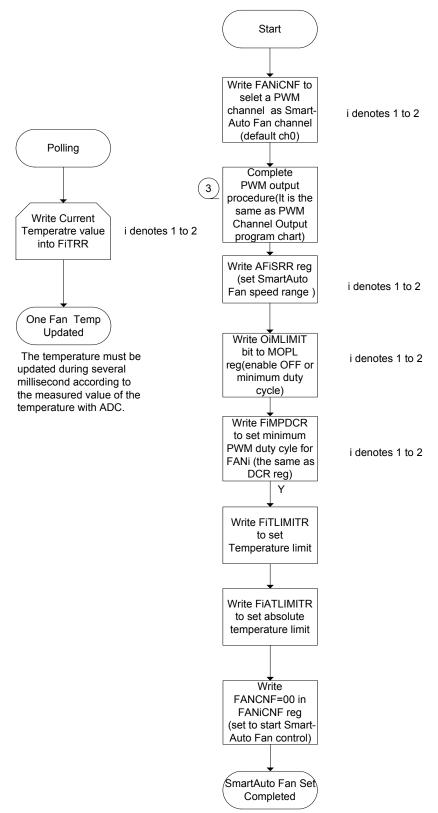

| Figure 7-25. Program Flow Chart for SmartAuto Fan Channel Output               | 235 |

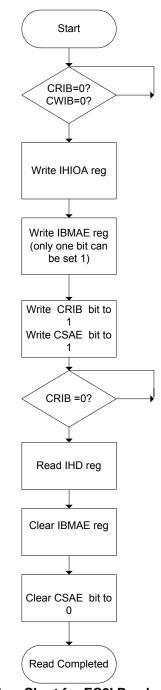

| Figure 7-26. Program Flow Chart for EC2I Read                                  | 240 |

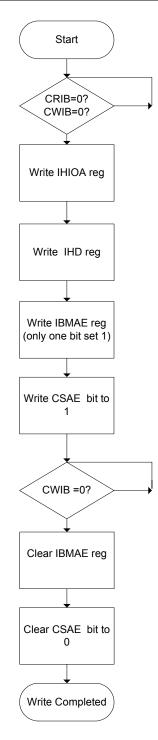

| Figure 7-27. Program Flow Chart for EC2I Write                                 | 241 |

| Figure 7-28. Simplified Diagram                                                | 243 |

| Figure 7-29. Parallel Port Female 25-Pin Connector                             | 248 |

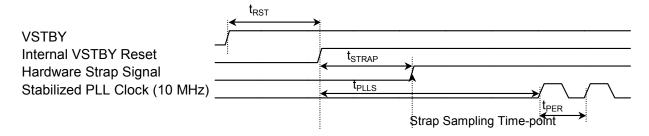

| Figure 9-1. Reset Timing                                                       | 253 |

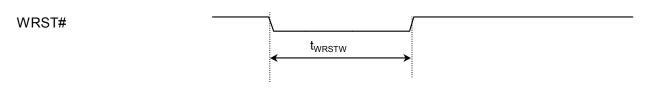

| Figure 9-2. Warm Reset Timing                                                  | 253 |

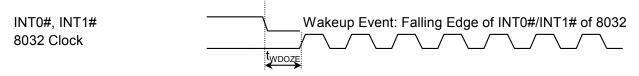

| Figure 9-3. Wakeup from Doze Mode Timing                                       | 253 |

| Figure 9-4. Wake Up from Sleep Mode Timing                                     | 254 |

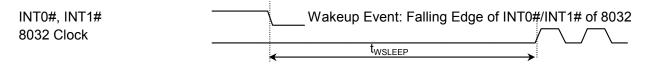

| Figure 9-5. Asynchronous External Wakeup/Interrupt Source Edge Detected Timing | 254 |

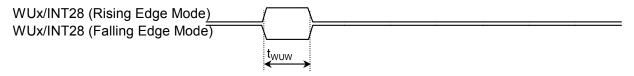

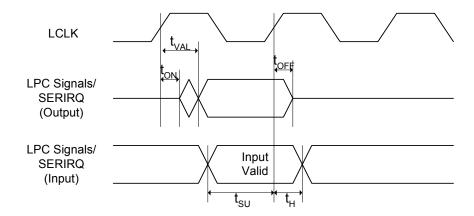

| Figure 9-6. LPC and SERIRQ Timing                                              | 254 |

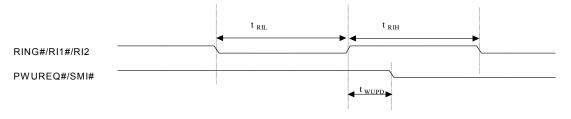

| Figure 9-7. SWUC Wake Up Timing                                                | 255 |

|                                                                                |     |

## IT8510E

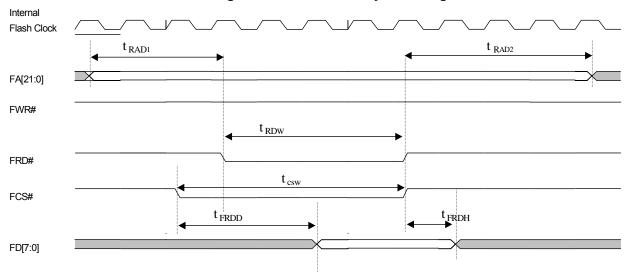

| Figure 9-8. Flash Read Cycle Timing                               | 255 |

|-------------------------------------------------------------------|-----|

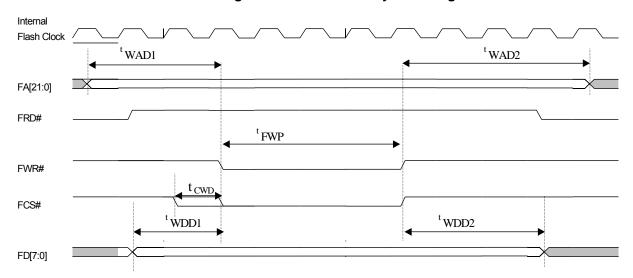

| Figure 9-9. Flash Write Cycle Timing                              | 256 |

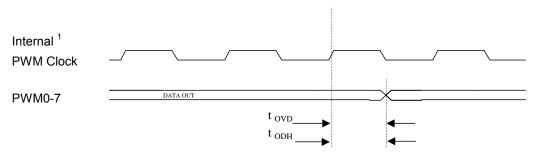

| Figure 9-10. PWM Output Timing                                    | 257 |

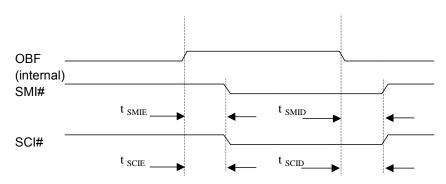

| Figure 9-11. PMC SMI#/SCI# Timing                                 | 257 |

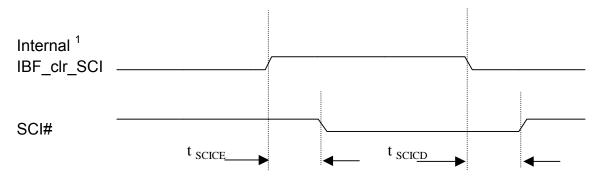

| Figure 9-12. PMC IBF/SCI# Timing                                  | 258 |

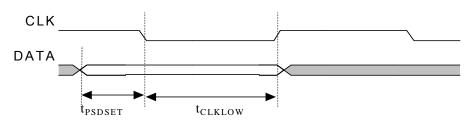

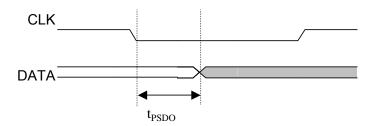

| Figure 9-13. PS/2 Receive/Transmit Timing                         | 258 |

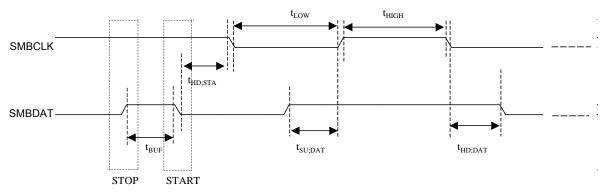

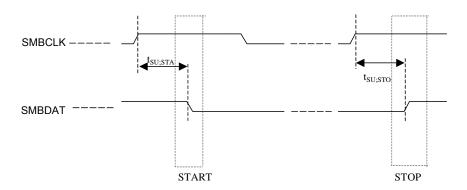

| Figure 9-14. SMBUS Timing                                         | 259 |

|                                                                   |     |

| TABLES                                                            |     |

| Table 3-1. Host/Flash Mapping                                     |     |

| Table 3-2. EC/Flash Mapping                                       |     |

| Table 3-3. Flash Read/Write Protection Controlled by EC Side      |     |

| Table 3-4. Flash Read/Write Protection Controlled by Host Side    |     |

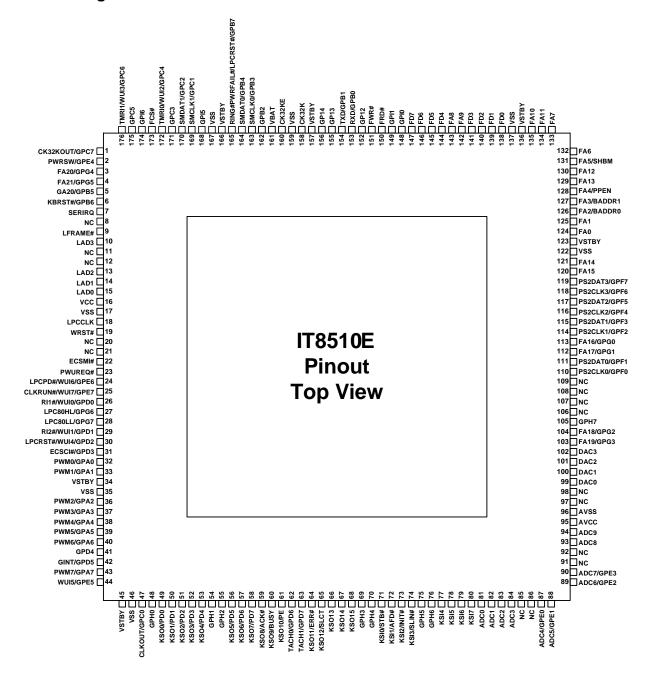

| Table 4-1. Pins Listed in Numeric Order (176-pin LQFP)            |     |

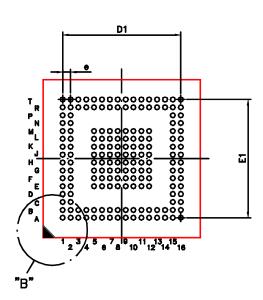

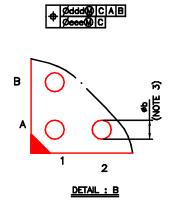

| Table 4-2. Pins Listed in Numeric Order (176-pin TFBGA)           |     |

| Table 4-3. Pins Listed in Alphabetical Order (176-pin LQFP/TFBGA) |     |

| Table 5-1. Pin Descriptions of LPC Bus Interface                  |     |

| Table 5-2. Pin Descriptions of External Flash Interface           |     |

| Table 5-3. Pin Descriptions of Keyboard Matrix Scan Interface     |     |

| Table 5-4. Pin Descriptions of SM Bus Interface                   |     |

| Table 5-5. Pin Descriptions of PS/2 Interface                     |     |

| Table 5-6. Pin Descriptions of PWM Interface                      |     |

| Table 5-7. Pin Descriptions of Wake Up Control Interface          |     |

| Table 5-8. Pin Descriptions of UART Interface                     |     |

| Table 5-9. Pin Descriptions of Parallel Port Interface            |     |

| Table 5-10. Pin Descriptions of GPIO Interface                    |     |

| Table 5-11. Pin Descriptions of Hardware Strap                    |     |

| Table 5-12. Pin Descriptions of NC                                |     |

| Table 5-13. Pin Descriptions of ADC Input Interface               |     |

| Table 5-14. Pin Descriptions of DAC Output Interface              |     |

| Table 5-15. Pin Descriptions of Clock                             |     |

| Table 5-16. Pin Descriptions of Power/Ground Signals              |     |

| Table 5-17. Power States                                          | 23  |

| Table 5-18. Quick Table of Power Plane for Pins                   |     |

| Table 5-19. Pin States of LPC Bus Interface                       | 24  |

| Table 5-20. Pin States of External Flash Interface                | 25  |

| Table 5-21. Pin States of Keyboard Matrix Scan Interface          |     |

| Table 5-22. Pin States of SM Bus Interface                        |     |

| Table 5-23. Pin States of PS/2 Interface                          |     |

| Table 5-24. Pin States of PWM Interface                           |     |

| Table 5-25. Pin States of Wake Up Control Interface               | 26  |

| www.ite.com.tw xiii IT                                                                    | 8510E/TE/G V0.7.2 |

|-------------------------------------------------------------------------------------------|-------------------|

| Table 7-3. Timer 2 Modes of Operation                                                     | 136               |

| Table 7-2. System Interrupt Table                                                         | 129               |

| Table 7-1. 8032 Port Usage                                                                | 127               |

| Table 6-26. Host View Register Map via Index-Data I/O Pair, RTC Bank 1                    |                   |

| Table 6-25. Host View Register Map via Index-Data I/O Pair, RTC Bank 0                    |                   |

| Table 6-24. Host View Register Map, RTC                                                   |                   |

| Table 6-23. EC View Register Map, PMC                                                     |                   |

| Table 6-22. Host View Register Map, PMC                                                   |                   |

| Table 6-21. EC View Register Map, KBC                                                     |                   |

| Table 6-20. Host View Register Map, KBC                                                   |                   |

| Table 6-19. EC View Register Map, SWUC                                                    |                   |

| Table 6-18. Host View Register Map, SWUC                                                  |                   |

| Table 6-17. Host View Register Map, SMFI                                                  |                   |

| Table 6-16. EC View Register Map, SMFI                                                    |                   |

| Table 6-15. M-bus Grant Behavior                                                          |                   |

| Table 6-14. Mapped Host Memory Address                                                    |                   |

| Table 6-13. Host View Register Map via Index-Data I/O, PM2 Logical Device                 |                   |

| Table 6-12. Host View Register Map via Index-Data I/O, PM1 Logical Device                 |                   |

| Table 6-11. Host View Register Map via Index-Data I/O Pair, RTC Logical Device            |                   |

| Table 6-10. Host View Register Map via Index-Data I/O Pair, SMFI Interface Logical Device |                   |

| Table 6-9. Host View Register Map via Index-Data I/O Pair, KBC / Keyboard Interface Log   |                   |

| Table 6-8. Host View Register Map via Index-Data I/O Pair, KBC / Mouse Interface Logical  |                   |

| Table 6-7. Host View Register Map via Index-Data I/O Pair, SWUC Logical Device            |                   |

| Table 6-6. Logical Device Number (LDN) Assignments                                        |                   |

| Table 6-5. Interrupt Request (IRQ) Number Assignment, Logical Device IRQ via SERIRQ       | •                 |

| Table 6-4. Host View Register Map via Index-Data I/O Pair, Standard Plug and Play Confi   |                   |

| Table 6-3. Host View Register Map, Logical Devices                                        |                   |

| Table 6-2. Host View Register Map, PNPCFG                                                 |                   |

| Table 6-1. LPC/FWH Response                                                               |                   |

| Table 5-38. Signals with Open-Drain Function                                              | 35                |

| Table 5-37. Pins with Schmitt-Trigger Function                                            | 35                |

| Table 5-36. Pins with Pull Function                                                       |                   |

| Table 5-35. Module Status in Each Power State/Clock Operation                             |                   |

| Table 5-34. Power Saving by EC Clock Operation Mode                                       |                   |

| Table 5-33. Clock Types                                                                   | 30                |

| Table 5-32. Reset Types and Applied Module                                                | 29                |

| Table 5-31. Reset Sources                                                                 | 29                |

| Table 5-30. Pin States of Clock                                                           |                   |

| Table 5-29. Pin States of DAC Output Interface                                            |                   |

| Table 5-28. Pin States of ADC Input Interface                                             |                   |

| Table 5-27. Pin States of GPIO Interface                                                  |                   |

| Table 5-26. Pin States of UART Interface                                                  | 26                |

## IT8510E

| Table 7-4. Serial Port Signals                                                  | 138 |

|---------------------------------------------------------------------------------|-----|

| Table 7-5. Selecting the Baud Rate Generator(s)                                 | 141 |

| Table 7-6. Internal RAM Map                                                     | 143 |

| Table 7-7. EC View Register Map, INTC                                           | 156 |

| Table 7-8. INTC Interrupt Assignments                                           | 164 |

| Table 7-9. EC View Register Map, WUC                                            | 167 |

| Table 7-10. WUC Input Assignments                                               | 171 |

| Table 7-11. EC View Register Map, KB Scan                                       | 173 |

| Table 7-12. EC View Register Map, GPIO                                          | 175 |

| Table 7-13. GPIO Alternate Function                                             | 179 |

| Table 7-14. EC View Register Map, ECPM                                          | 182 |

| Table 7-15. EC View Register Map, SMBUS                                         | 190 |

| Table 7-16. EC View Register Map, PS/2                                          | 199 |

| Table 7-17. EC View Register Map, DAC                                           | 202 |

| Table 7-18. EC View Register Map, ADC                                           | 207 |

| Table 7-19. Detail Step of ADC Channel Conversion                               | 215 |

| Table 7-20. EC View Register Map, PWM                                           | 221 |

| Table 7-21. EC View Register Map, EC2I                                          | 237 |

| Table 7-22. EC View Register Map, HWS                                           | 242 |

| Table 7-23. EC View Register Map, ETWD                                          | 244 |

| Table 8-1. Power Consumption                                                    | 252 |

| Table 9-1. Reset AC Table                                                       | 253 |

| Table 9-2. Warm Reset AC Table                                                  | 253 |

| Table 9-3. Wakeup from Doze Mode AC Table                                       | 254 |

| Table 9-4. Wake Up from Sleep Mode AC Table                                     | 254 |

| Table 9-5. Asynchronous External Wakeup/Interrupt Source Edge Detected AC Table | 254 |

| Table 9-6. LPC and SERIRQ AC Table                                              | 255 |

| Table 9-7. SWUC Wake Up AC Table                                                | 255 |

| Table 9-8. Flash Read Cycle AC Table                                            | 256 |

| Table 9-9. Flash Write Cycle AC Table                                           | 256 |

| Table 9-10. PWM Output AC Table                                                 | 257 |

| Table 9-11. PMC SMI#/SCI# AC Table                                              | 257 |

| Table 9-12. PMC IBF/SCI# AC Table                                               | 258 |

| Table 9-13. PS/2 Receive/Transmit AC Table                                      | 258 |

| Table 9-14. SMBUS AC Table                                                      | 259 |

| Table 10-1. ADC Characteristics                                                 | 261 |

| Table 10-2 DAC Characteristics                                                  | 261 |

#### 1. Features

#### ■ 8032 Embedded Controller

- Twin Turbo version

- 1 instruction at 1 machine cycle

- Maximum 10 MHz for EC domain and 8032

- Instruction set compatible with standard 8051

#### ■ LPC Bus Interface

- Compatible with the LPC specification v1.1

- Supports I/O read/write

- Supports Memory read/write

- Supports FWH read/write

- Serial IRQ

#### **■** External Flash Interface

- Up to 4M bytes Flash space shared by the host and EC side

- 8-bit data bus

#### ■ SM Bus Controller

- SM Bus spec. 2.0

- SM Bus host and slave

#### ■ System Wake Up Control

- Modem RI# wake up

- Telephone RING# wake up

- IRQ/SMI routing

#### **■** EC Wake Up Control

- 32 external/internal wake up events

#### ■ Interrupt Controller

- 32 interrupt events to EC

- Fixed priority

#### ■ Timer / Watch Dog Timer

- 3 16-bit multi-function timers inside 8032, which is based on EC clock

- 1 watch dog timer inside 8032, which is based on EC clock

- 1 external timer in ETWD module, which is based on RTC clock

- 1 external WDT in ETWD module, which is based on RTC clock

#### ■ UART

- Full duplex UART

#### ■ ACPI Power Management Channel

- 2 Power Management channels

- Compatible and enhanced mode

#### ■ RTC

- Supports 2 lockable memory areas

- Supports power-switch circuit

#### ■ GPIO

- Supports 71-bit GPIO

- Supports two alarms

- Programmable pull up/pull down

- Schmitt trigger for input

#### **■ KBC Interface**

- 8042 style KBC interface

- Legacy IRQ1 and IRQ12

- Fast A20G and KB reset

#### ■ ADC

- 14 ADC channels (10 external)

- 10-bit ADC resolution (accuracy ±4LSB)

- Digital filter for noise reduction

- Conversion time for 14 channels within 100 ms

#### DAC

- 4 DAC channels

- 8-bit DAC

#### ■ PWM with SmartAuto Fan Control

- 8 PWM channels

- SmartAuto Fan control

- Base clock frequency is 32.768KHz

- 2 Tachometers for measuring fan speed