## 12-bit/12MSPS CCD/CIS Analogue Front End/Digitiser

Production Data, April 1999, Rev 4.0

### DESCRIPTION

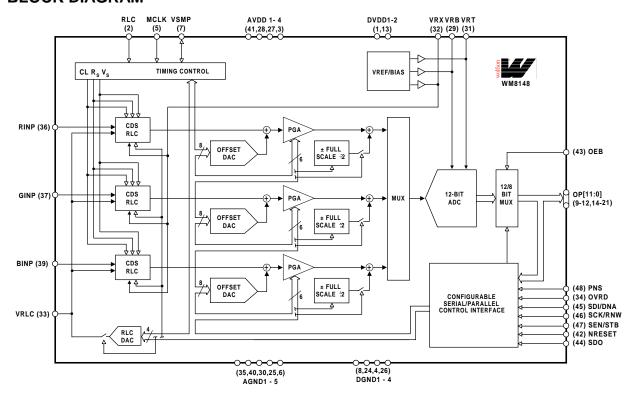

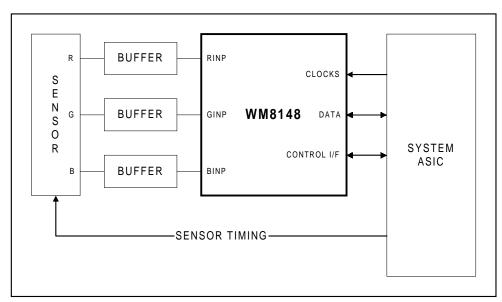

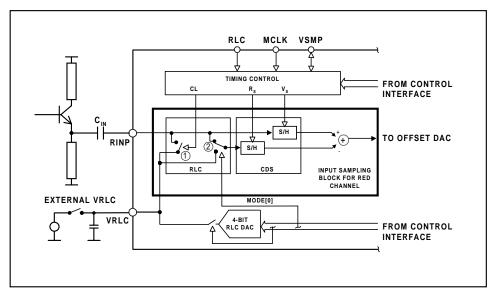

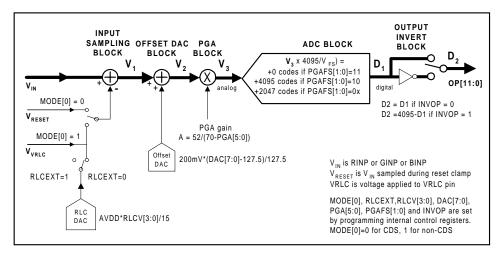

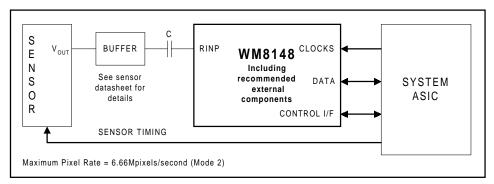

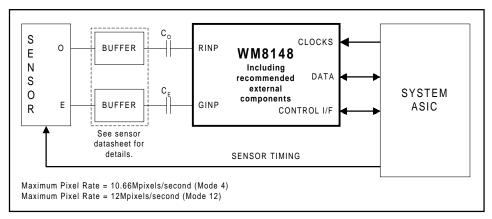

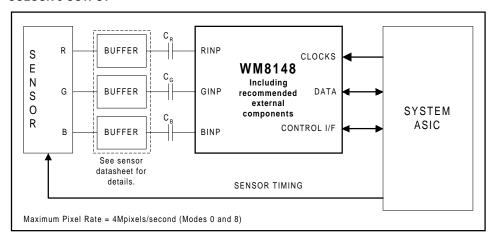

The WM8148 is a 12-bit, 12MSPS analogue front end/digitiser IC, which interfaces to colour or monochrome linear array CCDs or contact image sensors (CIS). The device includes all the signal conditioning circuitry required to process the analogue signals from the CCD or CIS prior to the internal ADC.

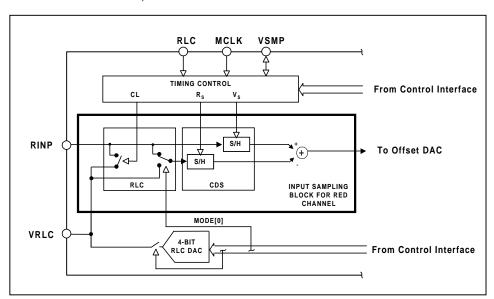

Three signal-processing channels are included in the device. Each channel features reset level clamping, correlated double sampling (CDS), offset correction and programmable gain amplification (PGA). The output signal from each channel is then multiplexed into a high performance 12-bit analogue to digital converter (ADC).

The reset level clamp and/or CDS functions can be selected or bypassed depending on the application.

The WM8148 can be operated in several modes. The operational mode of the device, including the sampling scheme and power management is programmed via the serial/parallel control interface.

Output data is presented in either 12-bit parallel or byte-wide (8+4-bit) format.

#### **FEATURES**

- · Correlated double sampling

- · Programmable gain amplifier

- Programmable input clamp voltage

- Offset correction

- 12-bit, 12MSPS ADC

- Internal voltage reference

- 12-bit or 8+4 bit data output mode

- Single 5V supply or 5V analogue/3.3V digital supply

- · Programmable sample timing

- Control interface compatible with previous Wolfson AFEs

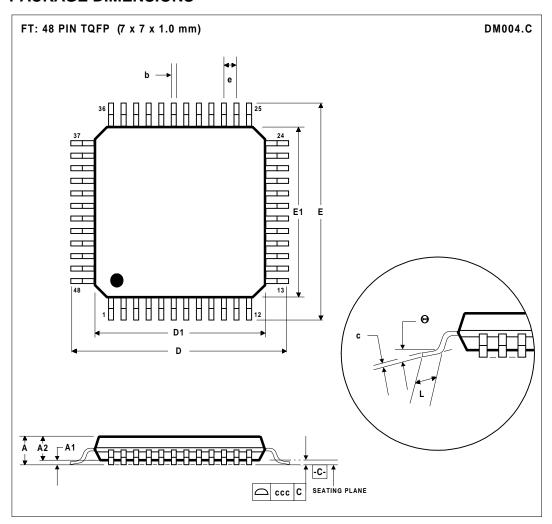

- 48-pin TQFP package

#### **APPLICATIONS**

- Flatbed scanners

- Document scanners

- Multi-function peripherals (MFPs)

- Colour copiers

- Character recognition systems

- Linear array CCDs

- Contact image sensors (CIS)

### **BLOCK DIAGRAM**

## **WOLFSON MICROELECTRONICS LTD**

Lutton Court, Bernard Terrace, Edinburgh, EH8 9NX, UK

Tel: +44 (0) 131 667 9386 Fax: +44 (0) 131 667 5176 Email: sales@wolfson.co.uk http://www.wolfson.co.uk Production Data contain final specifications current on publication date. Supply of products conforms to Wolfson Microelectronics' Terms and Conditions.

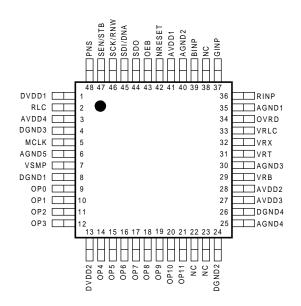

## **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| DEVICE       | TEMP. RANGE | PACKAGE                       |

|--------------|-------------|-------------------------------|

| XWM8148CFT/V | 0 to 70°C   | 48-pin 1mm<br>thick body TQFP |

## **PIN DESCRIPTION**

| PIN | NAME  | TYPE           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |  |  |  |  |  |

|-----|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1   | DVDD1 | Supply         | Digital supply (3.3V to 5V) for digital inputs and SDO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                              |  |  |  |  |  |

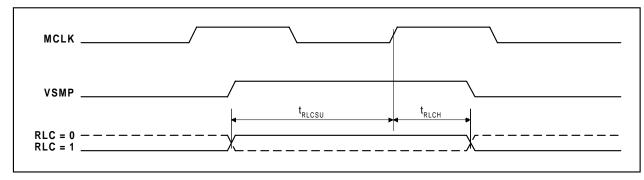

| 2   | RLC   | Digital input  | Selects whether reset level clamp is appli pixel then this pin can be tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ed, active high. If RLC is required on every                                                                                                                 |  |  |  |  |  |

| 3   | AVDD4 | Supply         | Analogue supply (5V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |  |  |  |  |  |

| 4   | DGND3 | Ground         | Digital ground (0V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |  |  |  |  |  |

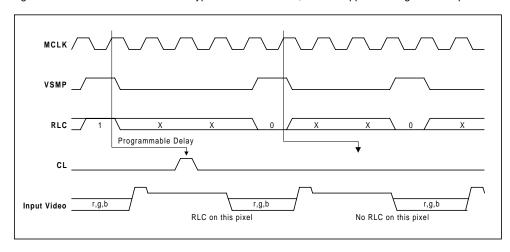

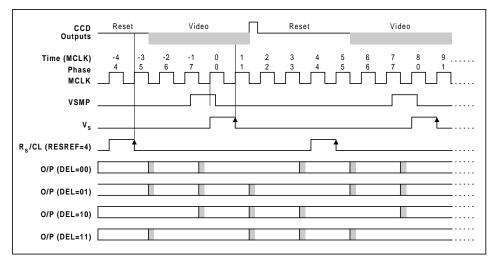

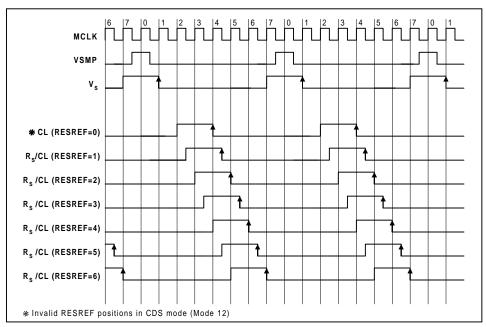

| 5   | MCLK  | Digital input  | Master clock. This clock is applied at N times the input pixel rate (N = 12, 8, 6, or 4 dependent on input sampling mode). MCLK is divided internally by N to generate internal clocks and to provide the clock source for digital logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                              |  |  |  |  |  |

| 6   | AGND5 | Ground         | Analogue ground (0V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |  |  |  |  |  |

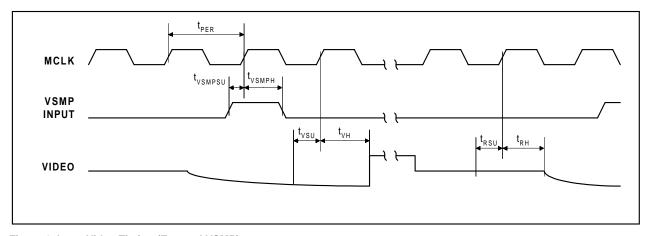

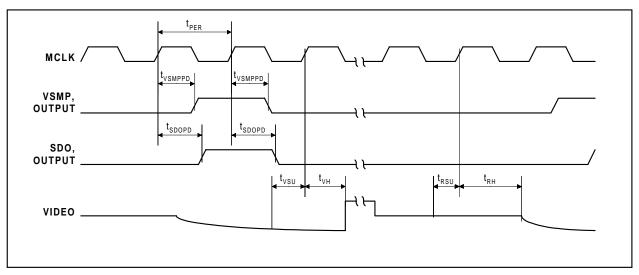

| 7   | VSMP  | Digital IO     | Video sample synchronisation pulse. This                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | pin may be either an input (default) or output.                                                                                                              |  |  |  |  |  |

|     |       |                | Input: This signal is pulsed externally to synchronise the WM8148's video input sample instant and the N-phase internal clock to CCD clocks and interface bus timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output: This signal is pulsed internally to flag the video input sample instant, to allow the CCD clocks and interface bus to be synchronised to the WM8148. |  |  |  |  |  |

| 8   | DGND1 | Ground         | Digital ground (0V) for output drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                              |  |  |  |  |  |

| 9   | OP0   | Digital output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | out MSB on OP[11] and LSB on pin OP[0].                                                                                                                      |  |  |  |  |  |

| 10  | OP1   | Digital output | See description of pins 14-21 for mode de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | efinitions.                                                                                                                                                  |  |  |  |  |  |

| 11  | OP2   | Digital output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |  |  |  |  |  |

| 12  | OP3   | Digital output |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                              |  |  |  |  |  |

| 13  | DVDD2 | Supply         | Digital supply (3.3V-5V) for Digital IO pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              |  |  |  |  |  |

| 14  | OP4   | Digital IO     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [4] to OP[11], signal data is output if OEB = 0                                                                                                              |  |  |  |  |  |

| 15  | OP5   | Digital IO     | and register write data is input if OEB = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                                                                                                                                            |  |  |  |  |  |

| 16  | OP6   | Digital IO     | There are five main modes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |  |  |  |  |  |

| 17  | OP7   | Digital IO     | Hi-Z: when OEB = 1     Output 13 hit truel to hit signal data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | tout from hus                                                                                                                                                |  |  |  |  |  |

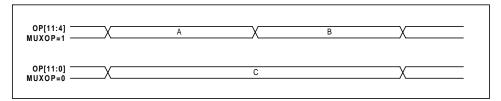

| 18  | OP8   | Digital IO     | <ul> <li>Output 12-bit: twelve bit signal data ou</li> <li>Output 8-bit muxed: signal data output</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | on OP[11:4] at 2 * ADC conversion rate                                                                                                                       |  |  |  |  |  |

| 19  | OP9   | Digital IO     | <ul> <li>Input 8-bit: register write data input on</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                              |  |  |  |  |  |

| 20  | OP10  | Digital IO     | Output 8-bit: register write data input on     Output 8-bit: register readback data output 8-bit: register readback data output 8-bit: register write data input on the control of th |                                                                                                                                                              |  |  |  |  |  |

| 21  | OP11  | Digital IO     | - Catput o bit. register readback data od                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nput on or [11.4]                                                                                                                                            |  |  |  |  |  |

| PIN | NAME    | TYPE            | DESCRIPTION                                                                                                                                                                                                                                                       |                                                                                                                    |  |  |  |

|-----|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 22  | NC      |                 | No internal connection.                                                                                                                                                                                                                                           |                                                                                                                    |  |  |  |

| 23  | NC      |                 | No internal connection.                                                                                                                                                                                                                                           |                                                                                                                    |  |  |  |

| 24  | DGND2   | Ground          | Digital ground (0V) for output drivers.                                                                                                                                                                                                                           | Digital ground (0V) for output drivers.                                                                            |  |  |  |

| 25  | AGND4   | Ground          | Analogue ground (0V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

| 26  | DGND4   | Ground          | Digital ground (0V).                                                                                                                                                                                                                                              |                                                                                                                    |  |  |  |

| 27  | AVDD3   | Supply          | Analogue supply (5V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

| 28  | AVDD2   | Supply          | Analogue supply (5V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

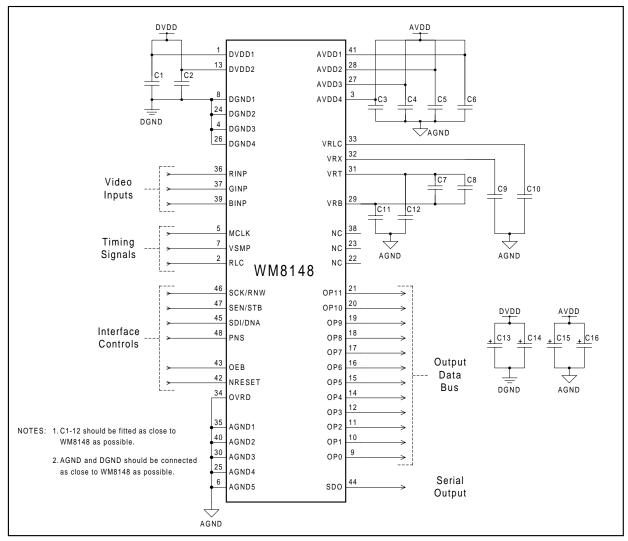

| 29  | VRB     | Analogue output | Lower reference voltage. This pin must capacitors. See Recommended Externa                                                                                                                                                                                        | be connected to AGND and VRT via decoupling al Components section for details.                                     |  |  |  |

| 30  | AGND3   | Ground          | Analogue ground (0V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

| 31  | VRT     | Analogue output | Upper reference voltage. This pin must capacitors. See Recommended Externa                                                                                                                                                                                        | be connected to AGND and VRB via decoupling al Components section for details.                                     |  |  |  |

| 32  | VRX     | Analogue output | Input return bias voltage. This pin must capacitors. See Recommended Externa                                                                                                                                                                                      | , 0                                                                                                                |  |  |  |

| 33  | VRLC    | Analogue IO     | Selectable analogue output voltage for RLC or single-ended bias reference.  This pin would typically be connected to AGND via a decoupling capacitor.  See Recommended External Components section for details. VRLC can be externally driven if programmed Hi-Z. |                                                                                                                    |  |  |  |

| 34  | OVRD    | Analogue input  | Override pin. Typically tied low externally.  The sense of this pin defines the device function on reset. Refer to the description of pin 42 for details.                                                                                                         |                                                                                                                    |  |  |  |

| 35  | AGND1   | Ground          | Analogue ground (0V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

| 36  | RINP    | Analogue input  | Red channel input video.                                                                                                                                                                                                                                          |                                                                                                                    |  |  |  |

| 37  | GINP    | Analogue input  | Green channel input video.                                                                                                                                                                                                                                        |                                                                                                                    |  |  |  |

| 38  | NC      |                 | No internal connection.                                                                                                                                                                                                                                           |                                                                                                                    |  |  |  |

| 39  | BINP    | Analogue input  | Blue channel input video.                                                                                                                                                                                                                                         |                                                                                                                    |  |  |  |

| 40  | AGND2   | Ground          | Analogue ground (0V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

| 41  | AVDD1   | Supply          | Analogue supply (5V).                                                                                                                                                                                                                                             |                                                                                                                    |  |  |  |

| 42  | NRESET  | Digital input   |                                                                                                                                                                                                                                                                   |                                                                                                                    |  |  |  |

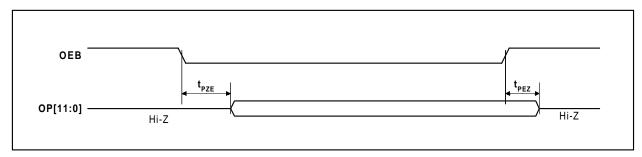

| 43  | OEB     | Digital input   | Output enable control, all outputs disab This pin must be externally connected.                                                                                                                                                                                   | led when OEB = 1.                                                                                                  |  |  |  |

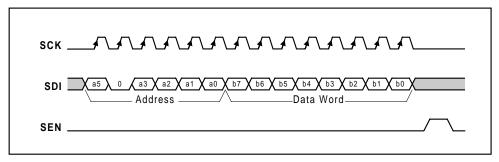

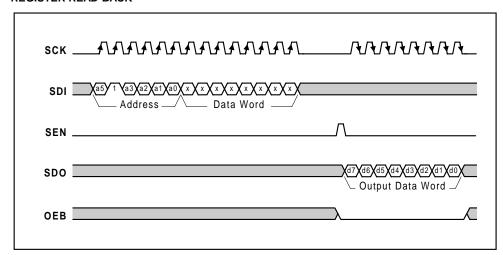

| 44  | SDO     | Digital output  | Serial Interface: register read-back,<br>VSMP output, setup error flag or<br>over-range flag (depending on control<br>bits SDO [1:0]).                                                                                                                            | Parallel Interface: Hi-Z, VSMP output, set-up error flag or over-range flag (depending on control bits SDO [1:0]). |  |  |  |

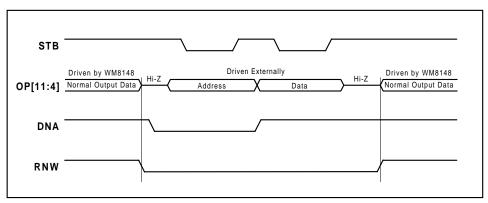

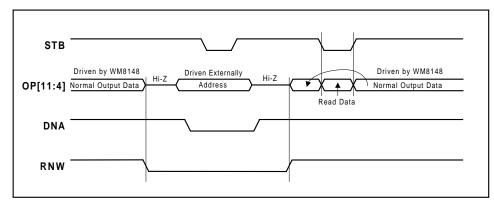

| 45  | SDI/DNA | Digital input   | Serial interface: serial input data signal.                                                                                                                                                                                                                       | Parallel interface: High = data, Low = address.                                                                    |  |  |  |

| 46  | SCK/RNW | Digital input   | Serial interface: serial clock signal.                                                                                                                                                                                                                            | Parallel interface: High = OP[11:4] is output bus, Low = OP[11:4] is input bus (Hi-Z).                             |  |  |  |

| 47  | SEN/STB | Digital input   | Serial interface: enable pulse, active high.                                                                                                                                                                                                                      | Parallel interface: strobe, active low.                                                                            |  |  |  |

| 48  | PNS     | Digital input   | Low = serial interface, High = parallel in                                                                                                                                                                                                                        | terface. This pin must be externally connected.                                                                    |  |  |  |

### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

As per JEDEC specifications A112-A and A113-B, this product requires specific storage conditions prior to surface mount assembly and will be supplied in vacuum-sealed moisture barrier bags. It has been classified as having a Moisture Sensitivity Level of 2.

| CONDITION                                   | MIN        | MAX          |

|---------------------------------------------|------------|--------------|

| Analogue supply voltages: AVDD1 – 4         | GND - 0.3V | GND + 7V     |

| Digital supply voltages: DVDD1 - 2          | GND - 0.3V | GND + 7V     |

| Digital grounds: DGND1 – 4                  | GND - 0.3V | GND + 0.3V   |

| Analogue grounds: AGND1 – 5                 | GND - 0.3V | GND + 0.3V   |

| Digital inputs and SDO                      | GND - 0.3V | DVDD1 + 0.3V |

| Digital outputs (not SDO)                   | GND - 0.3V | DVDD2 + 0.3V |

| Digital IO pins                             | GND - 0.3V | DVDD2 + 0.3V |

| RINP, GINP, BINP                            | GND - 0.3V | AVDD + 0.3V  |

| Other pins                                  | GND - 0.3V | AVDD + 0.3V  |

|                                             |            |              |

| Operating temperature range: T <sub>A</sub> | 0°C        | +70°C        |

| Storage temperature                         | -50°C      | +150°C       |

| Lead temperature (soldering, 10 seconds)    |            | +260°C       |

| Lead temperature (soldering, 2 minutes)     |            | +183°C       |

#### Notes:

- GND denotes the voltage of any ground pin. AVDD denotes the voltage applied to any AVDD pin.

- AGND and DGND pins are intended to be operated at the same potential. Differential voltages between these pins will degrade performance.

## RECOMMENDED OPERATING CONDITIONS

| CONDITION                                | SYMBOL         | MIN  | TYP | MAX  | UNITS |

|------------------------------------------|----------------|------|-----|------|-------|

| Operating temperature range              | T <sub>A</sub> | 0    |     | 70   | °C    |

| Digital input and output supply voltages | DVDD1 – 2      | 2.97 | 5   | 5.25 | V     |

| Analogue supply voltages                 | AVDD1 – 4      | 4.75 | 5   | 5.25 | V     |

## **ELECTRICAL CHARACTERISTICS**

#### **TEST CONDITIONS**

$AVDD = 4.75 \text{ to } 5.25\text{V}, \text{ DVDD1 and DVDD2} = 2.97 \text{ to } 5.25\text{V}, \text{ AGND} = \text{DGND} = 0\text{V}, \text{ } T_{\text{A}} = 0 \text{ to } 70^{\circ}\text{C}, \text{ MCLK} = 48\text{MHz unless otherwise stated (AVDD denotes the voltage applied to all AVDD pins)}.$

| PARAMETER                                                      | SYMBOL           | TEST<br>CONDITIONS               | MIN       | TYP         | MAX  | UNIT     |

|----------------------------------------------------------------|------------------|----------------------------------|-----------|-------------|------|----------|

| Overall System Performance Includi NO MISSING CODES GUARANTEED |                  | , PGA, Offset and CDS            | Functions |             |      |          |

| Full-scale input voltage range                                 |                  | Max Gain                         |           | 0.413       |      | V        |

|                                                                |                  | Gain = 1.0                       |           | 3.0         |      | V        |

|                                                                |                  | Min Gain                         |           | 4.13        |      | V        |

| Zero-scale transition error                                    |                  | Gain = 1.0                       |           | 20          |      | mV       |

| Full-scale transition error                                    |                  | Gain = 1.0                       |           | 20          |      | mV       |

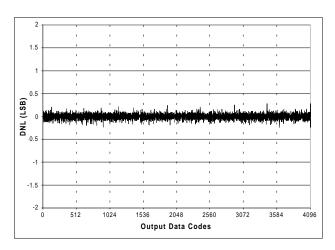

| Differential non-linearity                                     | DNL              | Gain = 1.0                       |           | 0.25        | 1.00 | LSB      |

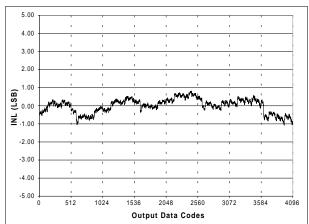

| Integral non-linearity                                         | INL              | Gain = 1.0                       |           | 1.0         |      | LSB      |

| ANALOGUE SPECIFICATION                                         |                  |                                  |           |             |      |          |

| Input Multiplexer                                              |                  |                                  |           |             |      |          |

| Channel to channel gain matching                               |                  |                                  |           | 1           |      | %        |

| Input voltage range                                            | V <sub>IN</sub>  |                                  | 0         |             | AVDD | V        |

| References                                                     | •                |                                  |           | •           | •    | •        |

| Upper reference voltage                                        | VRT              |                                  | 3.00      | 3.30        | 3.60 | V        |

| Lower reference voltage                                        | VRB              |                                  | 1.50      | 1.80        | 2.10 | V        |

| Input return bias voltage                                      | VRX              |                                  | 1.50      | 1.75        | 2.00 | V        |

| Diff. reference voltage (VRT-VRB)                              | $V_{RTB}$        |                                  | 1.30      | 1.50        | 1.70 | V        |

| Output resistance VRT, VRB, VRX                                |                  | VRT, VRB, VRX<br>buffers enabled |           | 2           |      | Ω        |

| Resistance VRT to VRB                                          |                  | VRT, VRB buffers disabled        | 500       | 800         | 1100 | Ω        |

| VRX Hi-Z leakage current                                       |                  | VRX buffer disabled              |           |             | 1    | μА       |

| VRLC/Reset-Level Clamp (RLC)                                   |                  |                                  |           |             |      | •        |

| RLC switching impedance                                        |                  |                                  |           | 75          |      | Ω        |

| VRLC Hi-Z leakage current                                      |                  | VRLC = 0 to AVDD                 |           |             | 1    | μΑ       |

| VRLC DAC resolution                                            |                  |                                  | 4         |             |      | bits     |

| VRLC DAC step                                                  |                  | AVDD = 5V                        | 290       | 333         | 370  | mV/ste   |

| VRLC short-circuit current                                     |                  |                                  |           | 5           |      | mA       |

| VRLC output resistance                                         |                  | VRLC = AVDD                      |           | 80          |      | Ω        |

| •                                                              |                  | VRLC = 0V                        |           | 80          |      | Ω        |

|                                                                |                  | VRLC = other                     |           | 5           |      | Ω        |

| Offset DAC                                                     |                  |                                  |           |             |      | _        |

| Resolution                                                     |                  |                                  | 8         |             |      | bits     |

| Differential non-linearity                                     | DNL              |                                  | -0.25     | 0.05        | 0.25 | LSB      |

| Integral non-linearity                                         | INL              |                                  | -0.50     | 0.10        | 0.50 | LSB      |

| Output voltage                                                 |                  | Code 00(hex)<br>Code FF(hex)     |           | -200<br>200 |      | mV<br>mV |

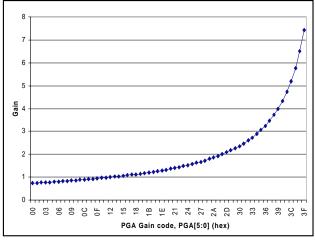

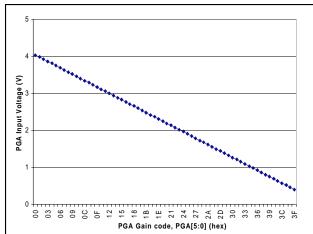

| Programmable Gain Amplifier. Mond                              | tonicity Guara   |                                  |           | •           | •    | •        |

| Resolution                                                     |                  |                                  | 6         |             |      | bits     |

| Max gain, each channel                                         | G <sub>MAX</sub> |                                  |           | 7.4         |      | V/V      |

| Min gain, each channel                                         | G <sub>MIN</sub> |                                  |           | 0.74        |      | V/V      |

| Gain error, each channel                                       |                  |                                  |           | 2           | 5    | %        |

## **TEST CONDITIONS**

$AVDD = 4.75 \text{ to } 5.25\text{V}, \ DVDD1 \ \text{and} \ DVDD2 = 2.97 \ \text{to } 5.25\text{V}, \ AGND = DGND = 0\text{V}, \ T_A = 0 \ \text{to } 70^{\circ}\text{C}, \ MCLK = 48\text{MHz} \ \text{unless}$  otherwise stated (AVDD denotes the voltage applied to all AVDD pins).

| PARAMETER                              | SYMBOL            | TEST<br>CONDITIONS                              | MIN         | TYP | MAX         | UNIT |

|----------------------------------------|-------------------|-------------------------------------------------|-------------|-----|-------------|------|

| DIGITAL SPECIFICATIONS                 |                   |                                                 |             |     |             |      |

| Digital Inputs                         |                   |                                                 |             |     |             |      |

| High level input voltage               | $V_{IH}$          |                                                 | 0.8 * DVDD1 |     |             | V    |

| Low level input voltage                | $V_{IL}$          |                                                 |             |     | 0.2 * DVDD1 | V    |

| High level input current               | I <sub>IH</sub>   |                                                 |             |     | 1           | μΑ   |

| Low level input current                | I <sub>IL</sub>   |                                                 |             |     | 1           | μΑ   |

| Input capacitance                      | Cı                |                                                 |             | 5   |             | pF   |

| Digital Outputs                        |                   |                                                 |             |     |             |      |

| High level output voltage              | V <sub>OH</sub>   | I <sub>OH</sub> = 1mA, DVDD =<br>DVDD1 or DVDD2 | DVDD - 0.5  |     |             | V    |

| Low level output voltage               | $V_{OL}$          | I <sub>OL</sub> = 1mA                           |             |     | 0.5         | V    |

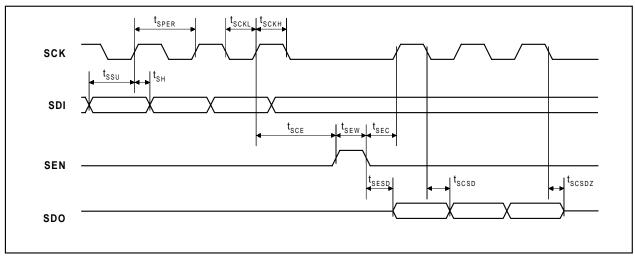

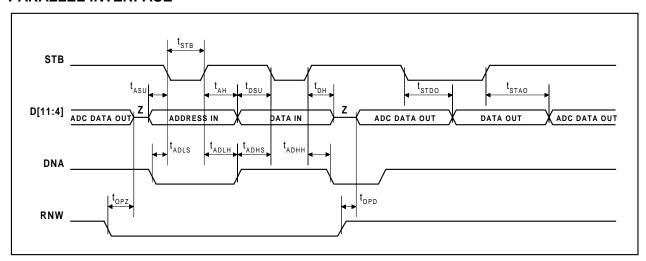

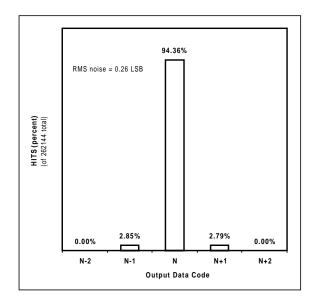

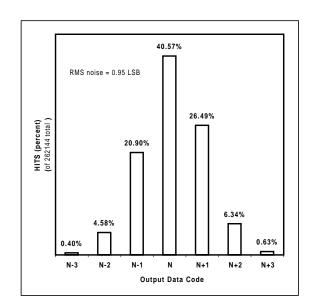

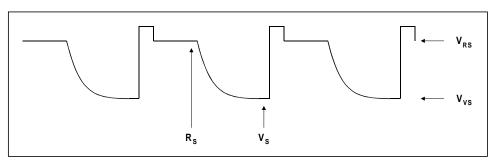

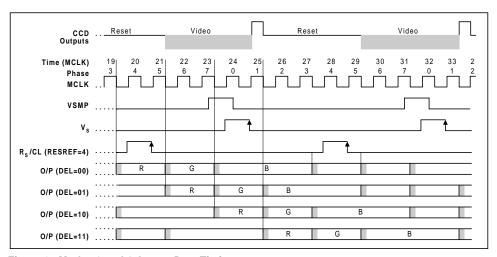

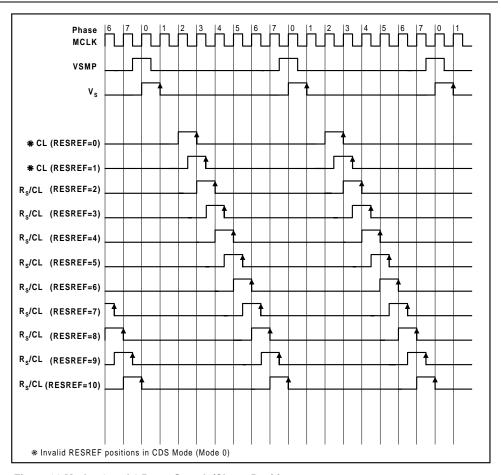

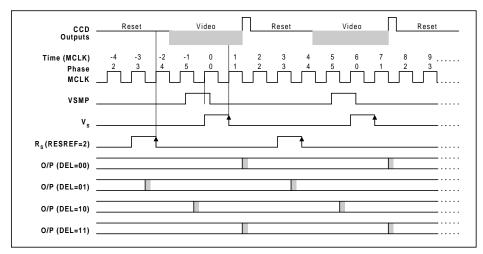

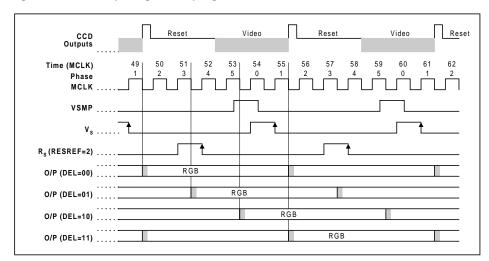

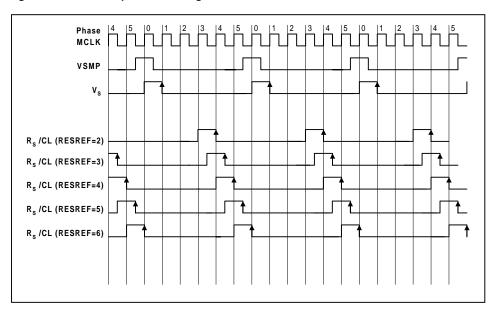

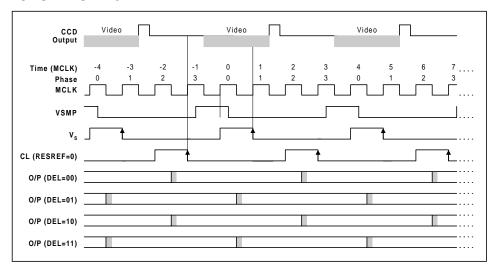

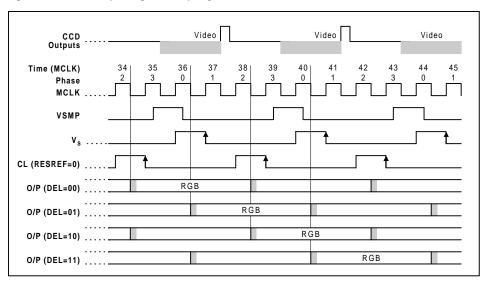

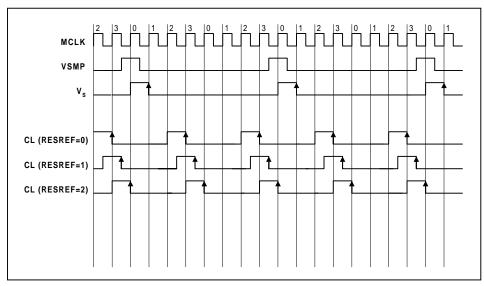

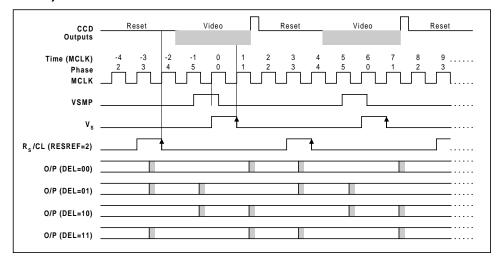

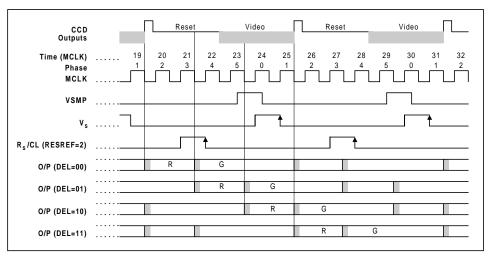

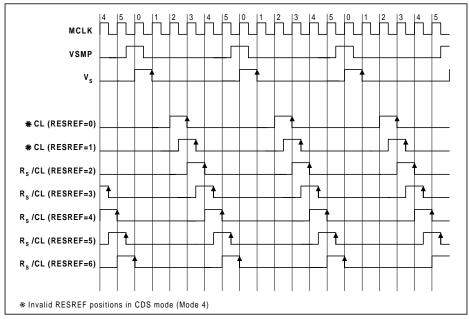

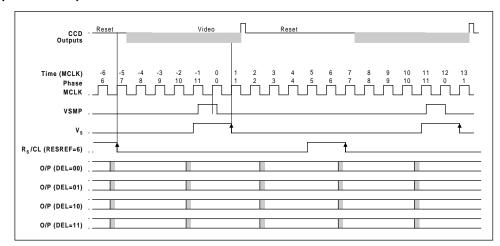

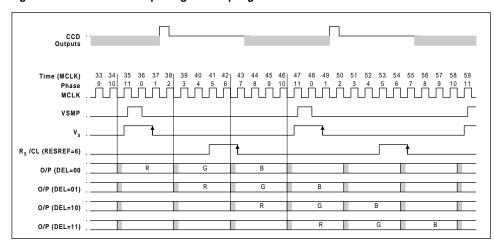

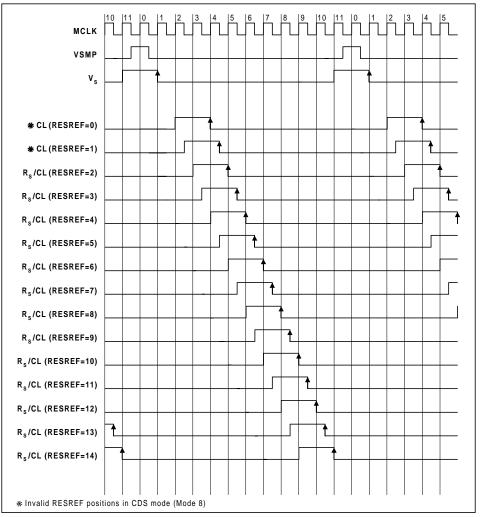

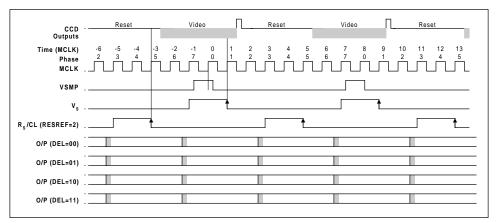

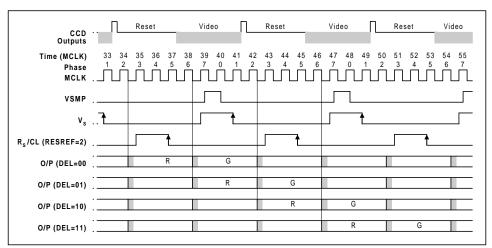

| High impedance output current          | l <sub>OZ</sub>   |                                                 |             |     | 1           | μΑ   |