# MOS INTEGRATED CIRCUIT $\mu$ PD46128512-X

# 128M-BIT CMOS MOBILE SPECIFIED RAM 8M-WORD BY 16-BIT EXTENDED TEMPERATURE OPERATION

# Description

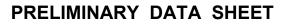

The  $\mu$ PD46128512-X is a high speed, low power, 134,217,728 bits (8,388,608 words by 16 bits) CMOS Mobile Specified RAM featuring asynchronous page read and random write, synchronous burst read/write function.

The  $\mu$ PD46128512-X is fabricated with advanced CMOS technology using one-transistor memory cell.

# Features

- 8,388,608 words by 16 bits organization

- Asynchronous page read mode

- Synchronous read and write mode

- Burst length: 8 words / 16 words / continuous

- Clock latency: 5, 6, 7, 8, 9, 10

- Burst sequence: Linear burst

- Max clock frequency: 108/83 MHz

- Byte data control: /LB (DQ0 to DQ7), /UB (DQ8 to DQ15)

- Low voltage operation: 1.7 to 2.0 V

- Operating ambient temperature: T<sub>A</sub> = -30 to +85 °C

- Chip Enable input: /CE1 pin

- Standby Mode input: CE2 pin

- Standby Mode 1: Normal standby (Memory cell data hold valid)

- Standby Mode 2: Density of memory cell data hold is variable

| μPD46128512           | Clock     | Asynchronous   | Operating  | Operating   | Supply current |      |        |         |         |         |                |        |         |         |      |

|-----------------------|-----------|----------------|------------|-------------|----------------|------|--------|---------|---------|---------|----------------|--------|---------|---------|------|

|                       | frequency | initial access | supply     | ambient     | At operating   |      |        |         | A       | At stan | dby <i>µ</i> A | 4      |         |         |      |

|                       | MHz       | time           | voltage    | temperature | mA             |      |        | (MAX.)  | )       |         |                |        | (TYP.)  |         |      |

|                       | (MAX.)    | ns             | V          | °C          | (MAX.)         |      | Densit | y of da | ta hold |         |                | Densit | y of da | ta hold |      |

|                       |           | (MAX.)         |            |             |                | 128M | 32M    | 16M     | 8M      | 0M      | 128M           | 32M    | 16M     | 8M      | 0M   |

|                       |           |                |            |             |                | bits | bits   | bits    | bits    | bits    | bits           | bits   | bits    | bits    | bits |

| -E9X <sup>Note</sup>  | 108       | 70             | 1.7 to 2.0 | -30 to +85  | 60             | 250  | T.B.D. | T.B.D.  | T.B.D.  | 65      | 80             | T.B.D. | T.B.D.  | T.B.D.  | 15   |

| -E10X <sup>Note</sup> |           | 85             |            |             | 50             |      |        |         |         |         |                |        |         |         |      |

| -E11X                 | 83        | 70             |            |             | 60             |      |        |         |         |         |                |        |         |         |      |

| -E12X                 |           | 85             |            |             | 50             |      |        |         |         |         |                |        |         |         |      |

Note Under consideration

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

The mark  $\star$  shows major revised points.

# **Ordering Information**

$\mu$ PD46128512-X is mainly shipping by wafer.

Please consult with our sales offices for package samples and ordering information.

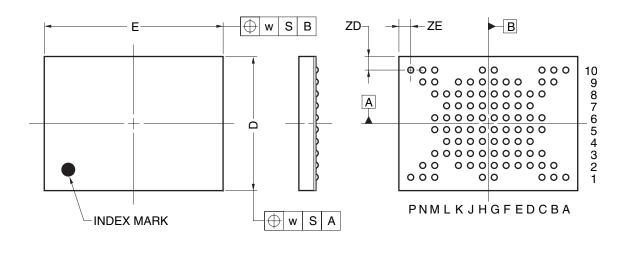

# **Pin Configuration**

The following is pin configuration of package sample.

/xxx indicates active low signal.

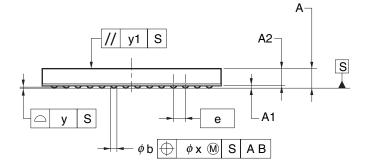

# 93-PIN TAPE FBGA (12x9)

| Top View       |    | Bottom View    |

|----------------|----|----------------|

| 000 00 000     | 10 | 000 00 000     |

| 00 00000 00    | 9  | 00 000000 00   |

| 0000000000     | 8  | 0000000000     |

| 0000000        | 7  | 00000000       |

| 0000000000     | 6  | 0000000000     |

| 0000000000     | 5  | 0000000000     |

| 0000000        | 4  | 00000000       |

| 0000000000     | 3  | 0000000000     |

| 00000000000000 | 2  | 00 00000000    |

| 000 00 000     | 1  | 000 00 000     |

| ABCDEFGHJKLMNP |    | PNMLKJHGFEDCBA |

|    |    |    |    |     |      |       | Тор | View |      |      |      |    |    |    |

|----|----|----|----|-----|------|-------|-----|------|------|------|------|----|----|----|

|    | А  | В  | С  | D   | Е    | F     | G   | Н    | J    | К    | L    | М  | Ν  | Р  |

| 10 | NC | NC | NC |     |      |       | NC  | NC   |      |      |      | NC | NC | NC |

| 9  |    | NC | NC |     | A15  | A21   | A22 | A16  | NC   | Vss  |      | NC | NC |    |

| 8  |    |    | NC | A11 | A12  | A13   | A14 | NC   | DQ15 | DQ7  | DQ14 | NC |    |    |

| 7  |    |    |    | A8  | A19  | A9    | A10 | DQ6  | DQ13 | DQ12 | DQ5  |    |    |    |

| 6  |    |    | NC | /WE | CE2  | A20   | NC  | NC   | DQ4  | Vcc  | NC   | NC |    |    |

| 5  |    |    | NC | CLK | /ADV | /WAIT | NC  | NC   | DQ3  | Vcc  | DQ11 | NC |    |    |

| 4  |    |    |    | /LB | /UB  | A18   | A17 | DQ1  | DQ9  | DQ10 | DQ2  |    |    |    |

| 3  |    |    | NC | A7  | A6   | A5    | A4  | GND  | /OE  | DQ0  | DQ8  | NC |    |    |

| 2  |    | NC | NC | NC  | A3   | A2    | A1  | A0   | NC   | /CE1 |      | NC | NC |    |

| 1  | NC | NC | NC |     |      |       | NC  | NC   |      |      |      | NC | NC | NC |

| A0 to A22   | : Address inputs         | CLK     | : Clock input         |

|-------------|--------------------------|---------|-----------------------|

| DQ0 to DQ15 | : Data inputs / outputs  | /ADV    | : Address Valid Input |

| /CE1        | : Chip select input      | /WAIT   | : Wait output         |

| CE2         | : Standby mode input     | Vcc     | : Power supply        |

| /WE         | : Write enable input     | GND     | : Ground              |

| /OE         | : Output enable input    | NC Note | : No Connection       |

| /LB, /UB    | : Byte data select input |         |                       |

Note Some signals can be applied because this pin is not internally connected.

**Remark** Refer to **Package Drawing** for the index mark.

# NEC

# **Block Diagram**

Preliminary Data Sheet M17507EJ2V0DS

# Truth Table

# **Asynchronous Operation**

| Mode                                | /CE1 | CE2 | /ADV  | /OE | /WE | /LB | /UB | DQ         |             | /WAIT  |

|-------------------------------------|------|-----|-------|-----|-----|-----|-----|------------|-------------|--------|

|                                     |      |     |       |     |     |     |     | DQ0 to DQ7 | DQ8 to DQ15 |        |

| Not selected (Standby Mode 1)       | Н    | н   | ×     | ×   | ×   | ×   | ×   | High-Z     | High-Z      | High-Z |

| Not selected (Standby Mode 2) Note1 | ×    | L   | ×     | ×   | ×   | ×   | ×   | High-Z     | High-Z      | High-Z |

| Word read                           | L    | н   | Note3 | L   | Н   | L   | L   | Dout       | Dout        | High-Z |

| Lower byte read                     |      |     |       |     |     | L   | Н   | Dout       | High-Z      | High-Z |

| Upper byte read                     |      |     |       |     |     | Н   | L   | High-Z     | Dout        | High-Z |

| Output disable                      |      |     |       |     |     | Н   | Н   | High-Z     | High-Z      | High-Z |

| Output disable                      |      |     |       | Н   |     | ×   | ×   | High-Z     | High-Z      | High-Z |

| Word write                          |      |     |       |     | L   | L   | L   | Din        | Din         | High-Z |

| Lower byte write                    |      |     |       |     |     | L   | Н   | Din        | High-Z      | High-Z |

| Upper byte write                    |      |     |       |     |     | Н   | L   | High-Z     | Din         | High-Z |

| Abort write Note2                   |      |     |       |     |     | Н   | Н   | High-Z     | High-Z      | High-Z |

Notes 1. CE2 pin must be fixed HIGH except Standby Mode 2 (refer to 2.3 Standby Mode Status Transition).

2. If /WE = LOW and /LB = /UB = HIGH, memory does not accept write data, so write operation is not available.

**3.** Fixed LOW or toggle HIGH  $\rightarrow$  LOW  $\rightarrow$  HIGH

$\label{eq:remark} \begin{array}{ll} \mbox{Remark} & \mbox{H}, \mbox{HIGH}: \mbox{V}_{IH}, \ \mbox{L}, \ \mbox{LOW}: \mbox{V}_{IL}, \ \ \mbox{X}: \mbox{V}_{IH} \ \ \mbox{or} \ \ \mbox{V}_{IL} \\ & \mbox{Clock pin must be fixed either LOW or HIGH}. \end{array}$

#### **Burst Operation**

NEC

| Mode                                 | /CE1 | CE2 | CLK       | /ADV | /OE                  | /WE                  | /LB                | /UB                | DQ                      |                         | /WAIT  |

|--------------------------------------|------|-----|-----------|------|----------------------|----------------------|--------------------|--------------------|-------------------------|-------------------------|--------|

|                                      |      |     |           |      |                      |                      |                    |                    | DQ0 to DQ7              | DQ8 to DQ15             | Note8  |

| Not selected (Standby Mode 1)        | н    | Н   | ×         | ×    | ×                    | ×                    | ×                  | ×                  | High-Z                  | High-Z                  | High-Z |

| Not selected (Standby Mode 2) Note1  | ×    | L   | ×         | ×    | ×                    | ×                    | ×                  | ×                  | High-Z                  | High-Z                  | High-Z |

| Start address latch                  | L    | н   | <br>Note4 | L    | $\times^{\rm Note7}$ | $\times^{\rm Note7}$ | × <sup>Note9</sup> | × <sup>Note9</sup> | High-Z <sup>Note5</sup> | High-Z <sup>Note5</sup> | ×      |

| Advanced burst read to next address  |      |     | <br>Note4 | н    | L                    | н                    |                    |                    | Dout                    | Dout                    | Output |

|                                      |      |     |           |      |                      |                      |                    |                    |                         |                         | Valid  |

| Burst read suspend Note2             |      |     |           |      | н                    |                      |                    |                    | High-Z                  | High-Z                  | HIGH   |

| Burst read resume Note2              |      |     |           |      | L                    |                      |                    |                    | Dout                    | Dout                    | HIGH   |

| Burst read termination Note3         | Ţ    |     | ×         |      | ×                    |                      |                    |                    | High-Z                  | High-Z                  | High-Z |

| Advanced burst write to next address | L    |     | <br>Note4 |      | н                    | L                    |                    |                    | DIN                     | DIN                     | Output |

|                                      |      |     |           |      |                      |                      |                    |                    |                         |                         | Valid  |

| Burst write suspend Note2            |      |     |           |      |                      | н                    |                    |                    | High-Z                  | High-Z                  | HIGH   |

| Burst write resume Note2             |      |     |           |      |                      | L                    |                    |                    | Din                     | Din                     | HIGH   |

| Burst write termination Note3        | Ŀ    |     | ×         |      |                      | ×                    |                    |                    | High-Z                  | High-Z                  | High-Z |

| Abort write Note6                    | L    |     | ×         |      | ×                    | Note10               | HIGH               | HIGH               | High-Z                  | High-Z                  | HIGH   |

Notes 1.

. CE2 pin must be fixed HIGH except Standby Mode 2 (refer to 2.3 Standby Mode Status Transition).

Be sure to suspend or resume a burst read after outputting the first read access data. Be sure to suspend or resume a burst write after latching the first write data. Burst write suspend or resume is available when setting WC = 1 (/WE level control) through Mode Register Set.

3. /CE1 must be fixed HIGH during tTRB specification until next read or write operation.

4. Valid clock edge shall be set either positive or negative edge through Mode Register Set.

5. If /OE = LOW and /LB = /UB = LOW, output is valid. If /OE = LOW and /LB = /UB = HIGH, output is high impedance.

If /WE = LOW, output is high impedance. If /OE = /WE = HIGH, output is high impedance.

- 6. If /WE = LOW and /LB = /UB = HIGH, memory does not accept write data, so write operation is not available.

- Both of two pins (/OE and /WE) or either of two should be connected to HIGH. It is prohibited to bring the both /OE and /WE to LOW.

- 8. Refer to the 4.10 /WAIT.

- **9.** For the Burst Read, the /UB, /LB setup time to CLK (t<sub>BC</sub>) must be satisfied. For the Burst Write, the /UB, /LB setup time to CLK (t<sub>BC</sub>) must be satisfied. Once /LB and /UB inputs are determined, they must not be changed until the end of burst operation.

- **10.** In case of WC = 0, /WE is HIGH.

- In case of WC = 1, /WE is LOW.

The explanation of WC refers to Table 5-2. Mode Register Definition (5th Bus Cycle) and 5.9 /WE control.

Remark H, HIGH : VIH, L, LOW : VIL, X: VIH or VIL, J : valid edge

\*

# CONTENTS

| 1. Initialization                                                                                                                   | 9  |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. Partial Refresh                                                                                                                  | 11 |

| 2.1 Standby Mode                                                                                                                    |    |

| 2.1 Standby Mode                                                                                                                    |    |

| 2.3 Standby Mode Status Transition                                                                                                  |    |

| 2.4 Addresses for Which Partial Refresh Is Supported                                                                                |    |

|                                                                                                                                     | 13 |

| 3. Page Read Operation                                                                                                              |    |

| 3.1 Features of Page Read Operation                                                                                                 | 14 |

| 3.2 Page Length                                                                                                                     | 14 |

| 3.3 Page-Corresponding Addresses                                                                                                    | 14 |

| 3.4 Page Start Address                                                                                                              | 14 |

| 3.5 Page Direction                                                                                                                  | 14 |

| 3.6 Interrupt during Page Read Operation                                                                                            | 14 |

| 3.7 When Page Read is not Used                                                                                                      | 14 |

| 4. Burst Operation                                                                                                                  | 15 |

| 4.1 Features of Burst Operation                                                                                                     |    |

| 4.2 Burst Length                                                                                                                    |    |

| 4.3 Latency                                                                                                                         |    |

| 4.4 Single Write                                                                                                                    |    |

| 4.4 Single Write                                                                                                                    |    |

| 4.6 Burst Read Suspend/Resume                                                                                                       |    |

| 4.7 Burst Write Suspend/Resume                                                                                                      |    |

| 4.7 Burst White Suspend/Resume                                                                                                      |    |

| 4.9 Burst Write Termination                                                                                                         |    |

| 4.9 Buist while remnination                                                                                                         |    |

| 4.10/WAIT                                                                                                                           |    |

| ·                                                                                                                                   |    |

| 4.10.2 Dummy Wait Cycles at Continuous Burst Operation<br>4.11 Reset Function from Synchronous Burst Mode to Asynchronous Page Mode |    |

|                                                                                                                                     |    |

| 5. Mode Register Settings                                                                                                           |    |

| 5.1 Mode Register Setting Method                                                                                                    |    |

| 5.2 Cautions for Setting Mode Register                                                                                              |    |

| 5.3 Partial Refresh Density                                                                                                         |    |

| 5.4 Burst Length                                                                                                                    |    |

| 5.5 Function Mode                                                                                                                   |    |

| 5.6 Valid Clock Edge                                                                                                                |    |

| 5.7 Read Latency (Write Latency)                                                                                                    |    |

| 5.8 Single Write                                                                                                                    |    |

| 5.9 /WE Control                                                                                                                     |    |

| 5.10 Reset to Page Mode                                                                                                             | 31 |

| 5.11 Reserved Bits                                                                                                                  |    |

| 5.12 Cautions for Timing Chart of Setting Mode Register                                                                             |    |

| 6. Electrical Specifications                                                                                                        | 33 |

| 7. Asynchronous AC Specification, Timing Chart | 36 |

|------------------------------------------------|----|

| 8. Synchronous AC Specification, Timing Chart  | 57 |

| 9. Mode Register Setting Timing                | 74 |

| 10. Standby Mode Timing Chart                  | 77 |

| 11. Package Drawing                            | 78 |

| 12. Recommended Soldering Conditions           | 79 |

# NEC

# 1. Initialization

Initialize the  $\mu$ PD46128512-X at power application using the following sequence to stabilize internal circuits. There are 2 method of initialization.

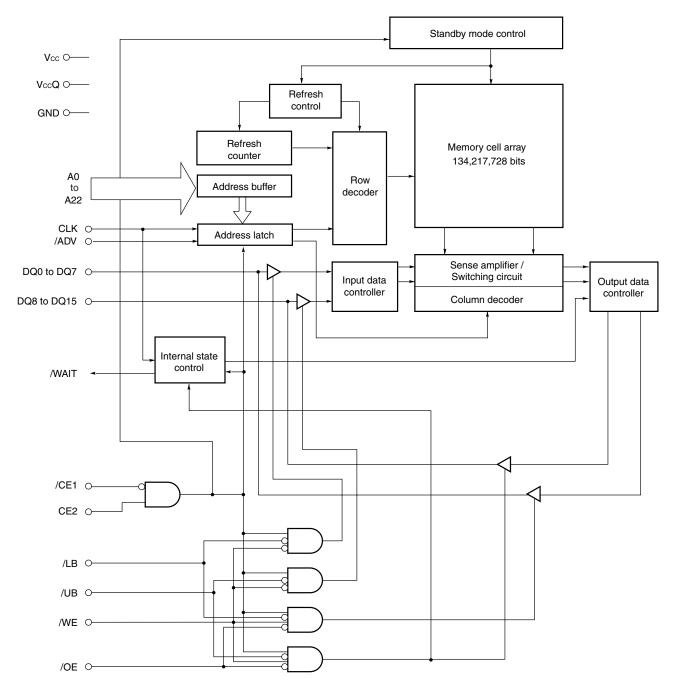

# **Initialization Timing 1**

- (1) Following power application, make CE2 HIGH after fixing CE2 to LOW for the period of tvHMH. Make /CE1 HIGH before making CE2 HIGH.

- (2) /CE1 and CE2 are fixed HIGH for the period of t\_MHCL.

Normal operation is possible after the completion of initialization.

# Figure 1-1. Initialization Timing Chart 1

Cautions 1. Make CE2 LOW when starting the power supply.

2. tvhmh is specified from when the power supply voltage reaches the prescribed minimum value (Vcc (MIN.), VccQ (MIN.)).

#### Initialization Timing 1

| Parameter                                             | Symbol | MIN. | MAX. | Unit |

|-------------------------------------------------------|--------|------|------|------|

| Power application to CE2 LOW hold                     | t∨нмн  | 50   |      | μs   |

| /CE1 HIGH to CE2 HIGH                                 | tснмн  | 0    |      | ns   |

| Following power application CE2 HIGH hold to /CE1 LOW | tмнcL  | 300  |      | μs   |

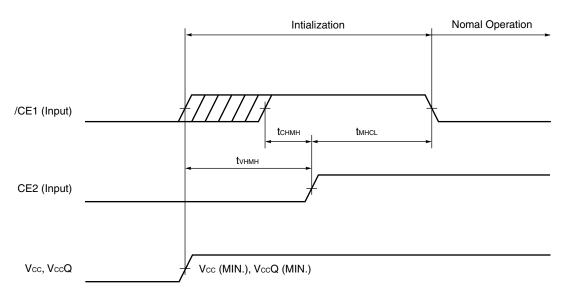

# **Initialization Timing 2**

(1) Following power application, make CE2 and /CE1 HIGH for the period of tMHCL.

Normal operation is possible after the completion of initialization.

#### Figure 1-2. Initialization Timing Chart 2

- Cautions 1. tmhcL is specified from when the power supply voltage reaches the prescribed minimum value (Vcc (MIN.), VccQ (MIN.)).

- 2. If the period from power supplying to value Vcc (MIN.), VccQ (MIN.) is beyond 10 ms or power supply is not stable rise, should be used Initialization Timing Chart 1.

**Initialization Timing 2**

| Parameter                                                   | Symbol        | MIN. | MAX. | Unit |

|-------------------------------------------------------------|---------------|------|------|------|

| Following power application /CE1, CE2 HIGH hold to /CE1 LOW | <b>t</b> MHCL | 300  |      | μs   |

# 2. Partial Refresh

#### 2.1 Standby Mode

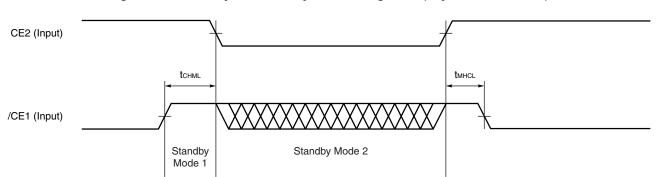

In addition to the regular standby mode (Standby Mode 1) with a 128M bits density, Standby Mode 2, which performs partial refresh, is also provided.

# 2.2 Density Switching

In Standby Mode 2, the densities that can be selected for performing refresh are 32M bits, 16M bits, 8M bits, and 0M bit.

The density for performing refresh can be set with the mode register. Once the refresh density has been set in the mode register, these settings are retained until they are set again, while applying the power supply. However, the mode register setting will become undefined if the power is turned off, so set the mode register again after power application. (For how to perform mode register settings, refer to section **5. Mode Register Settings**.)

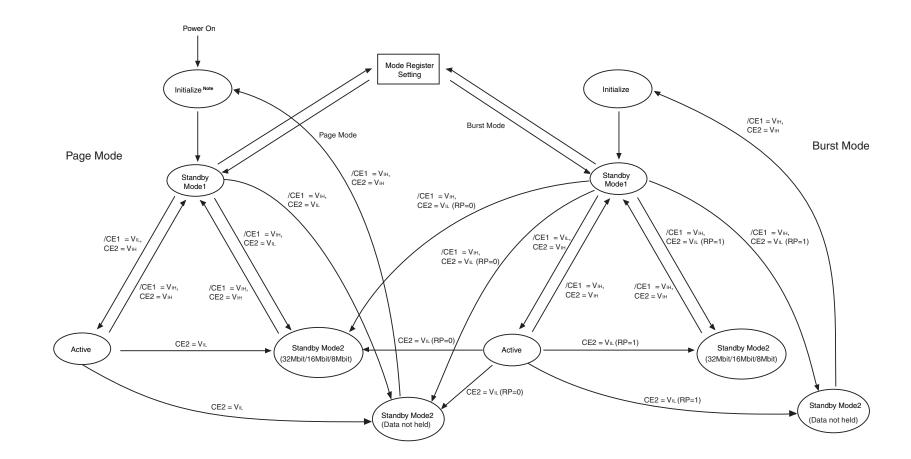

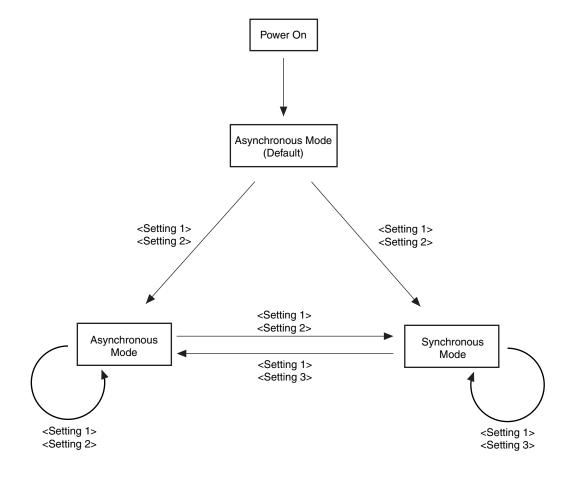

# 2.3 Standby Mode Status Transition

In Standby Mode 1, /CE1 and CE2 are HIGH. In Standby Mode 2, CE2 is LOW. In Standby Mode 2, if 0M bit is set as the density, it is necessary to perform initialization the same way as after applying power, in order to return to normal operation from Standby Mode 2. When the density has been set to 32M bits, 16M bits, or 8M bits in Standby Mode 2, it is not necessary to perform initialization to return to normal operation from Standby Mode 2.

For the timing charts, refer to Figure 10-1. Standby Mode 2 Entry / Exit Timing Chart (Asynchronous Mode), Figure 10-2. Standby Mode 2 (data not held) Entry / Exit Timing Chart (Asynchronous Mode).

12

**Note** Case "Initialization Timing 2" : Following initialization, set mode register.

# 2.4 Addresses for Which Partial Refresh Is Supported

| Data hold density | Correspondence address |

|-------------------|------------------------|

| 32M bits          | 000000H to 1FFFFFH     |

| 16M bits          | 000000H to 0FFFFFH     |

| 8M bits           | 000000H to 07FFFFH     |

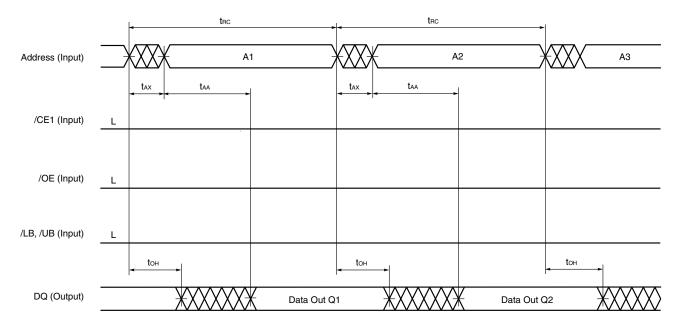

# 3. Page Read Operation

For the timing charts, refer to Figure 7-10. Asynchronous Page Read Cycle Timing Chart.

# 3.1 Features of Page Read Operation

| Features                             | Item                    |

|--------------------------------------|-------------------------|

| Page length                          | 16 words                |

| Page read-corresponding addresses    | A3, A2, A1, A0          |

| Page read start address              | Don't care              |

| Page direction                       | Don't care              |

| Interrupt during page read operation | Enabled <sup>Note</sup> |

\* Note /CE1 = HIGH, or any change in address A4 or higher will initiate a new read access specified as taa or tace.

#### 3.2 Page Length

16 words is supported as the page lengths. Page length is not necessary to set through Mode Register.

#### 3.3 Page-Corresponding Addresses

The 16 words page read-enabled addresses are A3, A2, A1, and A0. Fix addresses other than A3, A2, A1, and A0 during page read operation.

#### 3.4 Page Start Address

Since random page read is supported, any address (A3, A2, A1 and A0 with the 16 words page) can be used as the page read start address.

#### 3.5 Page Direction

Since random page read is possible, there is not restriction on the page direction.

## 3.6 Interrupt during Page Read Operation

When generating an interrupt during page read, make /CE1 HIGH or change A4 and higher addresses.

#### 3.7 When Page Read is not Used

Since random page read is supported, even when not using page read, random access is possible as usual.

# 4. Burst Operation

Burst operation is valid when burst mode is set through mode register.

# 4.1 Features of Burst Operation

| Function         | Features                  |

|------------------|---------------------------|

| Burst Length     | 8, 16, Continuous         |

| Read Latency     | 5, 6, 7, 8, 9, 10         |

| Write Latency    | 4, 5, 6, 7, 8, 9          |

| Burst Sequence   | Linear                    |

| Single Write     | Single Write, Burst Write |

| Valid Clock Edge | Rising Edge, Falling Edge |

# 4.2 Burst Length

Burst length is the number of word to be read or written during synchronous burst read/write operation as the result of a single address latch cycle. It can be set on 8, 16words boundary or continuous for entire address through Mode Register Set sequence. Starting from initial address being latched, device internal address counter assign +1 to the previous address until reaching the end of boundary address. After completing read data out or write data latch for the set burst length, operation automatically end except for continuous burst. When continuous burst length is set, read /write is endless unless it is terminated by the rising edge of /CE1.

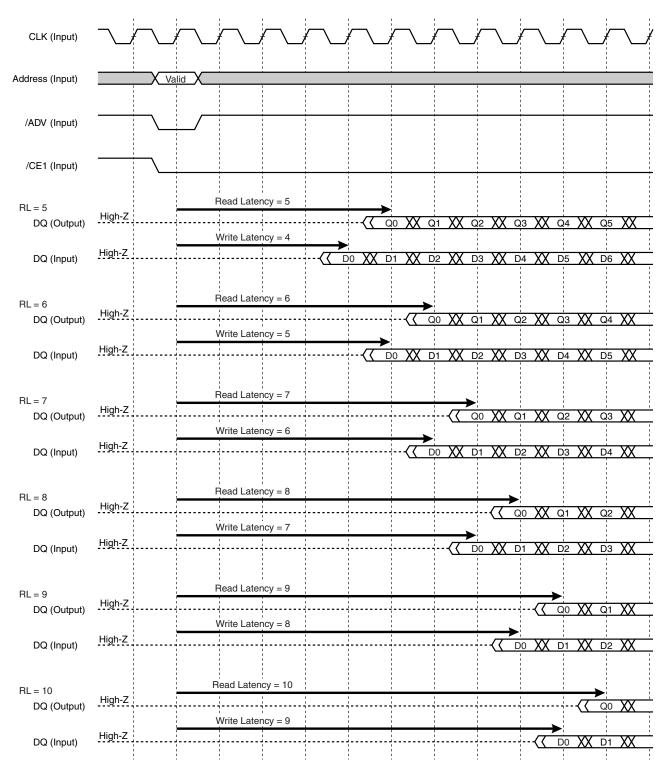

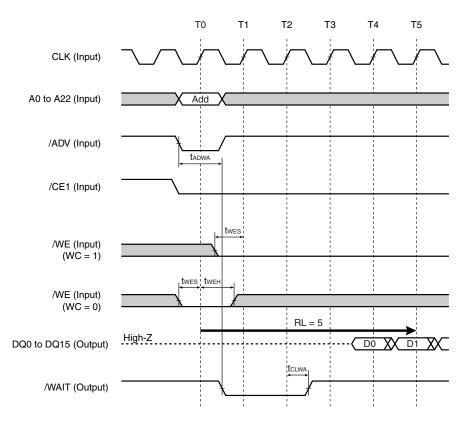

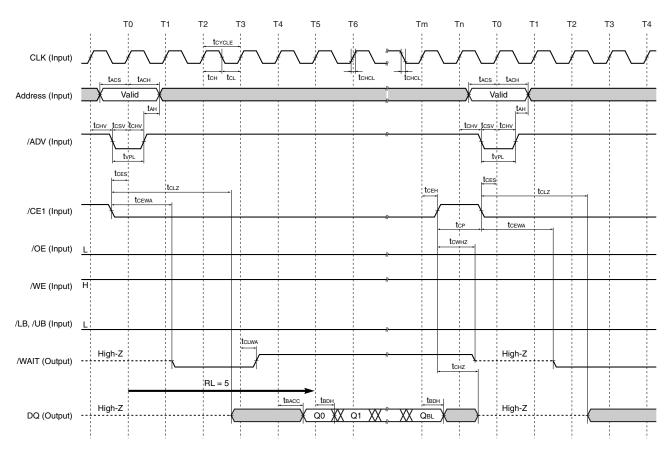

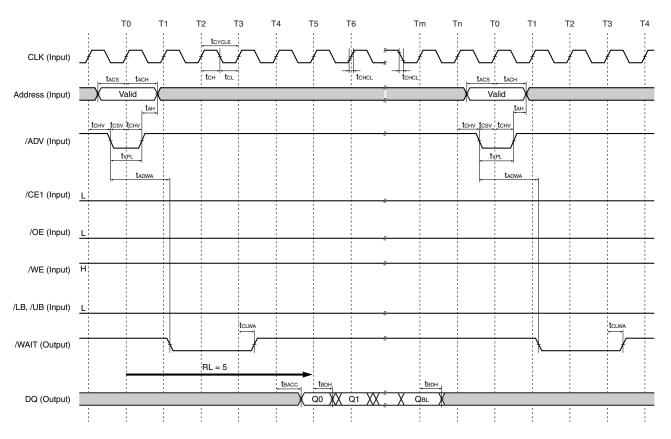

# 4.3 Latency

Read Latency (RL) is the number of clock cycles between the address being latched and first read data becoming available during synchronous burst read operation. It is set through Mode Register Set sequence after power application. Once RL is set through Mode Register Set sequence, write latency, that is the number of clock cycles between address being latched and first write data being latched, is automatically set to RL–1.

| Grade        | Clock     | Asynchronous<br>access time | Read Latency      | Write Latency Note |

|--------------|-----------|-----------------------------|-------------------|--------------------|

|              | Frequency | access time                 |                   |                    |

| -E9X         | <108 MHz  | 70 ns                       | 8, 9, 10          | 7, 8, 9            |

| -E10X        |           | 85 ns                       | 10                | 9                  |

| -E9X, -E11X  | <83 MHz   | 70 ns                       | 7, 8, 9, 10       | 6, 7, 8, 9         |

| -E10X, -E12X |           | 85 ns                       | 8, 9, 10          | 7, 8, 9            |

| -E9X, -E11X  | <66 MHz   | 70 ns                       | 6, 7, 8, 9, 10    | 5, 6, 7, 8, 9      |

| -E10X, -E12X |           | 85 ns                       | 7, 8, 9, 10       | 6, 7, 8, 9         |

| -E9X, -E11X  | <52 MHz   | 70 ns                       | 5, 6, 7, 8, 9, 10 | 4, 5, 6, 7, 8, 9   |

| -E10X, -E12X |           | 85 ns                       | 5, 6, 7, 8, 9, 10 | 4, 5, 6, 7, 8, 9   |

# Latency Count

Note Write Latency = Read Latency-1

Figure 4-1. Latency Definition

16

#### ★ 4.4 Single Write

NEC

Single write operation is a single-word length synchronous write operation. The  $\mu$ PD46128512-X is supporting two type of synchronous write operation, "Burst Read & Single Write" and "Burst Read & Burst Write", configurable with SW bit in the mode register. When the device set to the "Burst Read & Single Write" operation mode, the burst length at the synchronous write operation is always fixed to single word length regardless of the burst length (BL) setting in the mode register, however, BL setting is still effective in synchronous read operation (Refer to **5. Mode Register Settings**).

Refer to Figure 8-8. Synchronous Burst Write Cycle Timing Chart (/WE level Control), Figure 8-9. Synchronous Burst Write Cycle Timing Chart (/WE single clock control), Figure 8-10. Synchronous Single Write Timing Chart.

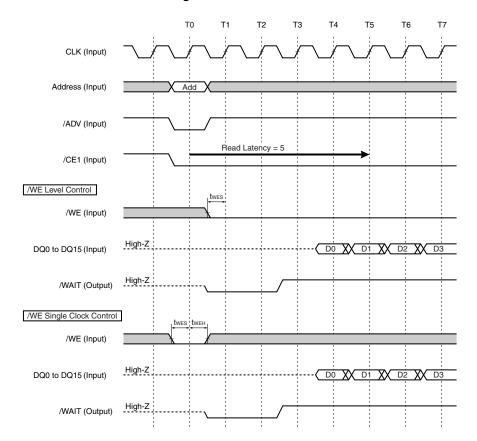

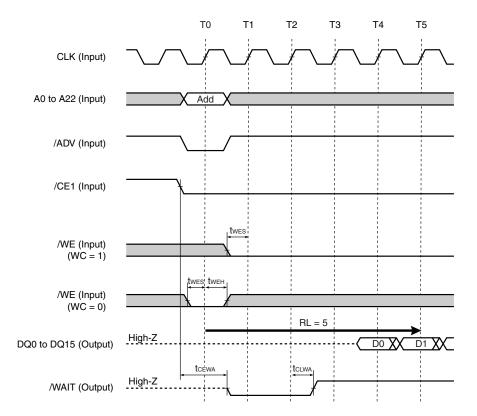

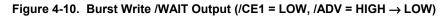

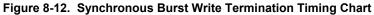

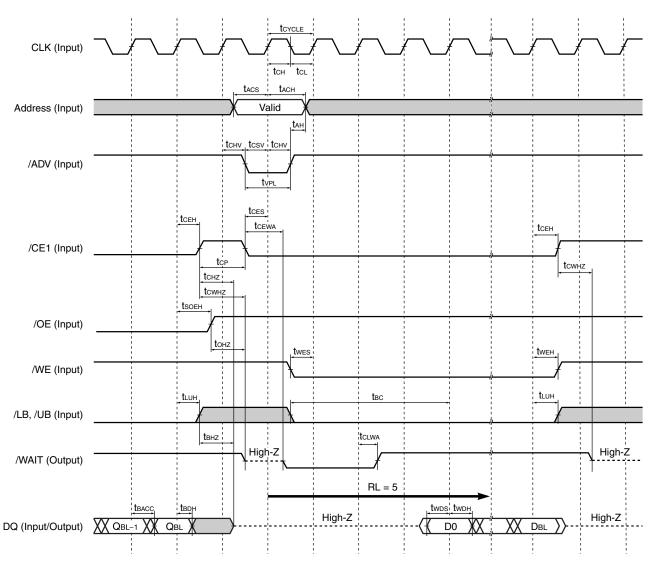

#### ★ 4.5 /WE Control

The µPD46128512-X is supporting two type of timing control with /WE input signal, "/WE level control" and "/WE single clock control" configurable with WC bit in the mode register at synchronous write operation. In case of /WE level controlling, /WE must be asserted LOW before the 2nd clock input timing (T1).

Refer to Figure 8-8. Synchronous Burst Write Cycle Timing Chart (/WE level Control), Figure 8-9. Synchronous Burst Write Cycle Timing Chart (/WE single clock control).

#### Figure 4-2. /WE Control

Preliminary Data Sheet M17507EJ2V0DS

#### ★ 4.6 Burst Read Suspend/Resume

A burst read operation can be suspended by bringing /OE signal from LOW to HIGH during the burst read operation. The /OE signal must be required to meet the specified setup / hold time to the clock which the data being suspended. Once the /OE is brought to HIGH, output data turns to be high impedance state after specific time duration.

The burst read suspend will be effective after outputting first read data, or after outputting dummy wait cycles in case of dummy wait cycling insertion at continuous burst read mode.

The burst suspend mode will be resumed by re-asserting /OE to LOW, and the first output data is from the same address location as of being suspended.

Figure 4-3. Burst Read Suspend/Resume

# NEC

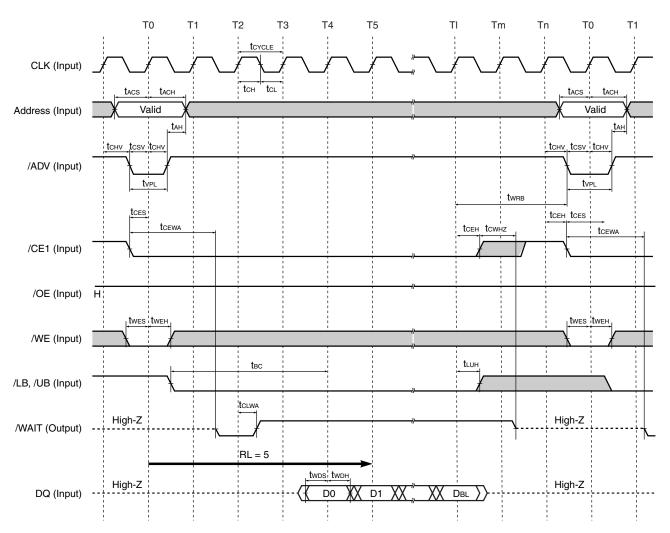

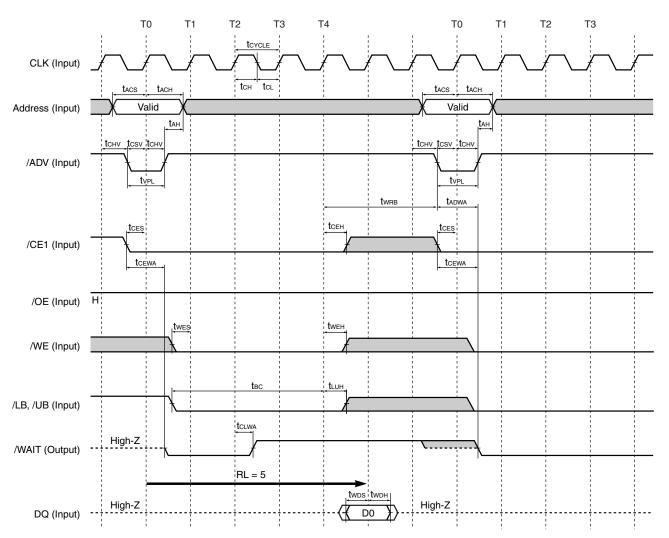

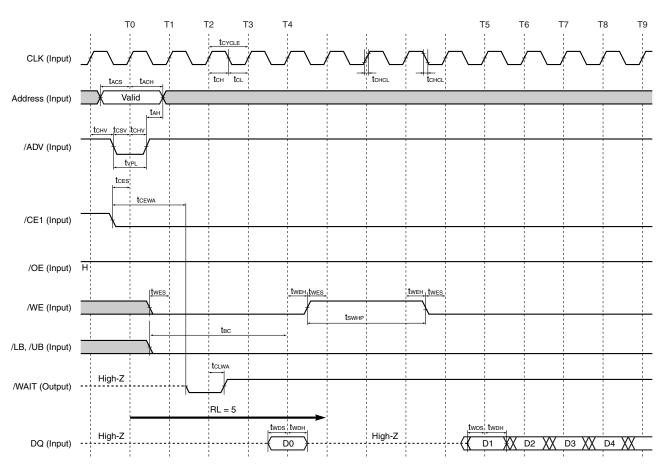

#### ★ 4.7 Burst Write Suspend/Resume

A burst write operation can be suspended by bringing /WE signal from LOW to HIGH during the burst write operation. The /WE signal must be required to meet the specified setup / hold time to the clock which the data being suspended. The burst write suspend will be effective after inputting first write data.

The burst suspend mode will be resumed by re-asserting /WE to LOW, and the first write data is written to the same address location as of being suspended. Burst write suspend or resume is available only when WC = 1(/WE level control) is set to the mode register (refer to **Table 5-2. Mode Register Definition (5th Bus Cycle)**.

#### Figure 4-4. Burst Write Suspend/Resume

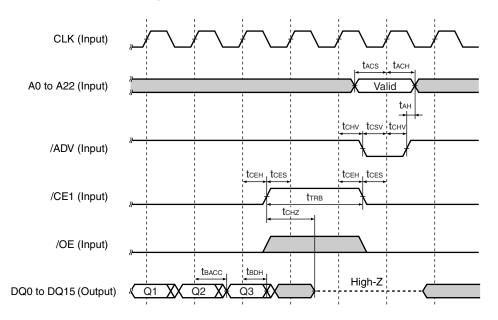

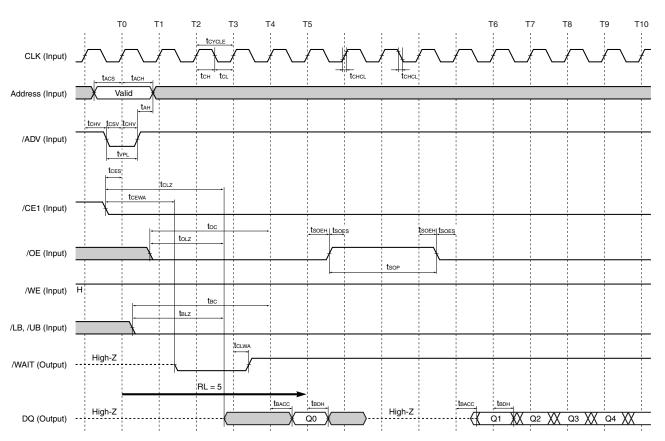

#### 4.8 Burst Read Termination

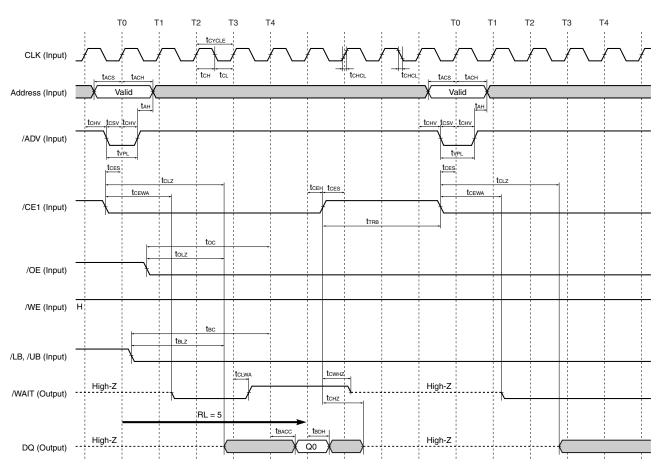

Burst read termination can be performed by transferring /CE1 LOW to HIGH during the burst read. When continuous burst length is set, burst read is endless unless it is terminated. Be sure to terminate a burst read after outputting the first read access data.

In order to guarantee the last data output, the specified minimum value of /CE1 = LOW hold time (tceH) against clock edge must be satisfied. In order to perform next operation after burst read termination, the specified minimum value of Burst Read Termination recovery time (tTRB) must be satisfied.

Figure 4-5. Burst Read Termination

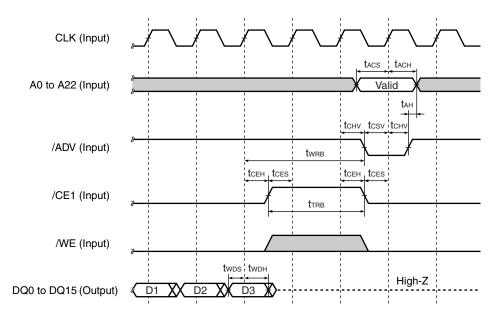

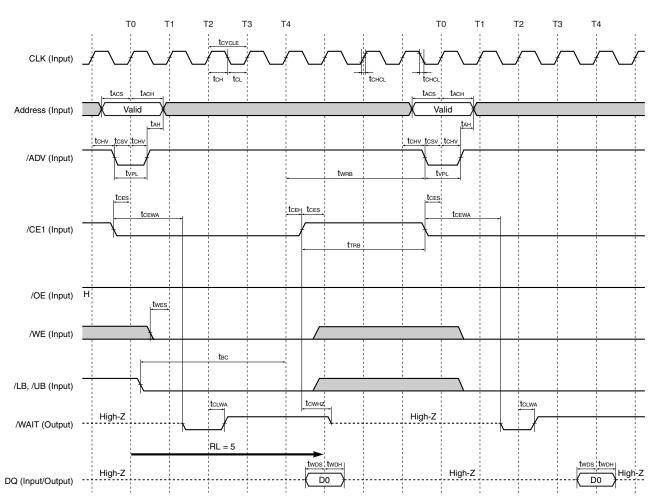

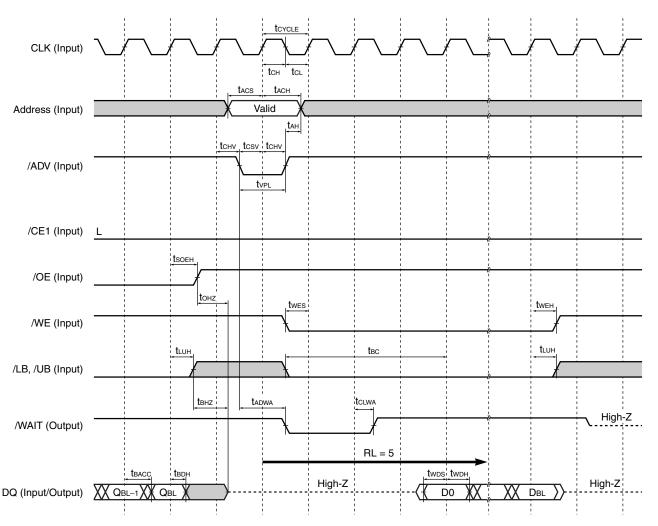

# 4.9 Burst Write Termination

Burst write termination can be performed by transferring /CE1 LOW to HIGH during the burst write. When continuous burst length is set, burst write is endless unless it is terminated. Be sure to terminate a burst write after latching the first write data.

In order to guarantee the last write data is latched, the specified minimum value of /CE1 = LOW hold time against clock edge must be satisfied. In order to perform next operation after burst write termination, the specified minimum value of Burst Write Termination recovery time (tTRB) must be satisfied.

Figure 4-6. Burst Write Termination

# NEC

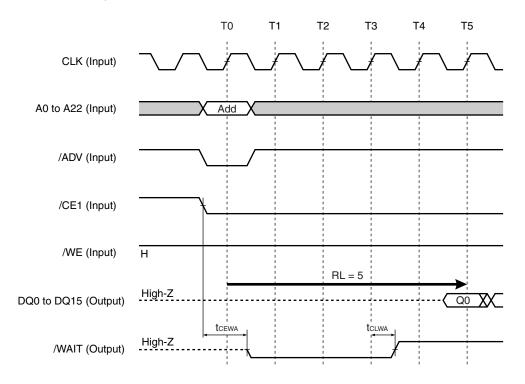

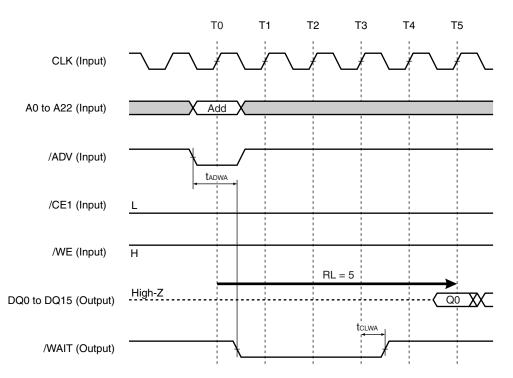

# 4.10 /WAIT

# ★ 4.10.1 Feature of /WAIT Output

The /WAIT output signal indicates the internal status, busy (LOW) or ready (HIGH), during the burst read and burst write operation.

The /WAIT output state changes depend on the /CE1 and /ADV condition. When /CE1 held entire LOW, the /WAIT output corresponds with /ADV state and turns to LOW by /ADV assertion. The /WAIT output stays high impedance at standby mode (/CE1 = HIGH) and turns to LOW at active mode brought by /CE1 assertion.

The /WAIT output will be asserted to LOW after specific time duration triggered by falling edge of /CE1, or falling edge of /ADV when /CE1 held entire LOW. When the /WAIT output LOW, it indicates the output data is not valid at the next clock cycle.

The /WAIT output asserts HIGH one clock cycle before the valid data output.

The /WAIT output retains the same state as of the clock cycle right before being suspended with /OE brought to HIGH.

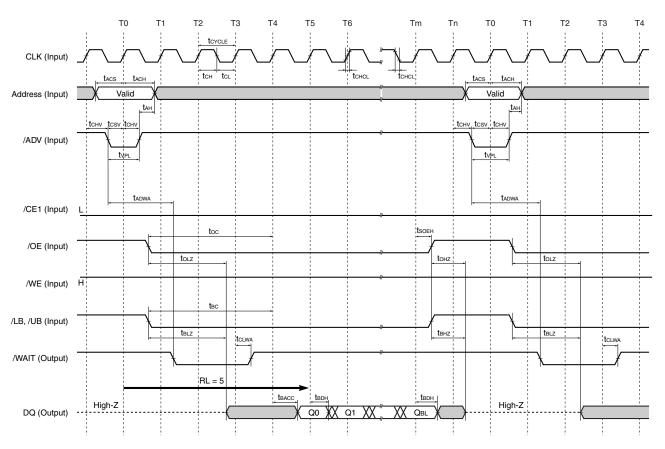

Figure 4-7. Burst Read /WAIT Output (/CE1 = HIGH  $\rightarrow$  LOW)

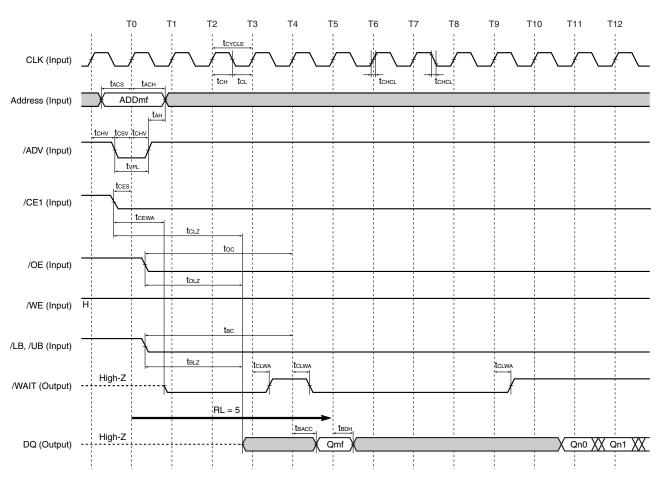

#### Figure 4-8. Burst Read /WAIT Output (/CE1 = LOW, /ADV = HIGH $\rightarrow$ LOW)

The /WAIT output will be asserted to LOW after specific time duration from the falling edge of the /CE1, or falling edge of the /ADV when /CE1 held LOW at burst write operation. When the /WAIT output LOW, it indicates the input data can not be accepted at the next clock cycle. The /WAIT output asserts HIGH one clock cycle before the valid data input. The /WAIT output retains the same state as of the clock cycle right before being suspended with /WE brought to HIGH. The /WAIT output always stay high impedance state under asynchronous mode setting.

Figure 4-9. Burst Write /WAIT Output (/CE1 = HIGH  $\rightarrow$  LOW)

Preliminary Data Sheet M17507EJ2V0DS

# 4.10.2 Dummy Wait Cycles at Continuous Burst Operation

In continuous burst operation, dummy wait cycles may be needed when a burst sequence crosses the first 16-word boundary. Whether dummy wait cycles is needed or not depends on start address and the number of dummy wait cycles depends on Read Latency (See **Table 4-1. Burst Sequence** and **4-2. Dummy Wait Cycles and Read Latency**). During the dummy cycle period, /WAIT output LOW.

| Start   | Burst length = 8 | Burst length = 16                     | Continuous                                              |

|---------|------------------|---------------------------------------|---------------------------------------------------------|

| Address | Linear           | Linear                                | Linear                                                  |

| xx00 H  | 0-1-2-3-4-5-6-7  | 0-1-2-3-4-5-6-7-8-9-10-11-12-13-14-15 | 0-1-2-3-4-5-6-7-8-9-10-11-12-13-14-15                   |

| xx01 H  | 1-2-3-4-5-6-7-0  | 1-2-3-4-5-6-7-8-9-10-11-12-13-14-15-0 | 1-2-3-4-5-6-7-8-9-10-11-12-13-14-15-16                  |

| xx02 H  | 2-3-4-5-6-7-0-1  | 2-3-4-5-6-7-8-9-10-11-12-13-14-15-0-1 | 2-3-4-5-6-7-8-9-10-11-12-13-14-15-16-17                 |

| xx03 H  | 3-4-5-6-7-0-1-2  | 3-4-5-6-7-8-9-10-11-12-13-14-15-0-1-2 | 3-4-5-6-7-8-9-10-11-12-13-14-15-16-17-18                |

| xx04 H  | 4-5-6-7-0-1-2-3  | 4-5-6-7-8-9-10-11-12-13-14-15-0-1-2-3 | 4-5-6-7-8-9-10-11-12-13-14-15-16-17-18-19               |

| xx05 H  | 5-6-7-0-1-2-3-4  | 5-6-7-8-9-10-11-12-13-14-15-0-1-2-3-4 | 5-6-7-8-9-10-11-12-13-14-15-16-17-18-19-20              |

| xx06 H  | 6-7-0-1-2-3-4-5  | 6-7-8-9-10-11-12-13-14-15-0-1-2-3-4-5 | 6-7-8-9-10-11-12-13-14-15-16-17-18-19-20-21             |

| xx07 H  | 7-0-1-2-3-4-5-6  | 7-8-9-10-11-12-13-14-15-0-1-2-3-4-5-6 | 7-8-9-10-11-12-13-14-15-16-17-18-19-20-21-22            |

| xx08 H  |                  | 8-9-10-11-12-13-14-15-0-1-2-3-4-5-6-7 | 8-9-10-11-12-13-14-15-16-17-18-19-20-21-22-23           |

| xx09 H  |                  | 9-10-11-12-13-14-15-0-1-2-3-4-5-6-7-8 | 9-10-11-12-13-14-15-16-17-18-19-20-21-22-23-24          |

| xx0A H  |                  | 10-11-12-13-14-15-0-1-2-3-4-5-6-7-8-9 | 10-11-12-13-14-15-16-17-18-19-20-21-22-23-24-25         |

| xx0B H  |                  | 11-12-13-14-15-0-1-2-3-4-5-6-7-8-9-10 | 11-12-13-14-15- <b>W</b> -16-17-18-19-20-21-22-23-24-25 |

| xx0C H  |                  | 12-13-14-15-0-1-2-3-4-5-6-7-8-9-10-11 | 12-13-14-15- <b>W-W</b> -16-17-18-19-20-21-22-23-24-25  |

| xx0D H  |                  | 13-14-15-0-1-2-3-4-5-6-7-8-9-10-11-12 | 13-14-15- <b>W-W-W</b> -16-17-18-19-20-21-22-23-24-25   |

| xx0E H  |                  | 14-15-0-1-2-3-4-5-6-7-8-9-10-11-12-13 | 14-15- <b>W-W-W-W</b> -16-17-18-19-20-21-22-23-24-25    |

| xx0F H  |                  | 15-0-1-2-3-4-5-6-7-8-9-10-11-12-13-14 | 15- <b>W-W-W-W-W-</b> 16-17-18-19-20-21-22-23-24-25     |

| xx10 H  |                  |                                       | 16-17-18-19-20-21-22-23-24-25-26                        |

| xx11 H  |                  |                                       | 17-18-19-20-21-22-23-24-25-26-27                        |

|         |                  |                                       |                                                         |

| xxnB H  |                  |                                       | -xxnB -xxnC-xxnD-xxnE-xxnF- <b>W</b> -xx(n+1)0-xx(n+1)1 |

| xxnC H  |                  |                                       | -xxnC-xxnD-xxnE-xxnF- <b>W-W</b> -xx(n+1)0-xx(n+1)1     |

| xxnD H  |                  |                                       | -xxnD-xxnE-xxnF- <b>W-W-</b> xx(n+1)0-xx(n+1)1          |

| xxnE H  |                  |                                       | -xxnE-xxnF- <b>W-W-W-W</b> -xx(n+1)0-xx(n+1)1-xx(n+1)2  |

| xxnF H  |                  |                                       | -xxnF- <b>W-W-W- W-W</b> -xx(n+1)0-xx(n+1)1-xx(n+1)2    |

|         |                  |                                       |                                                         |

Remarks 1. The above table assumes Read Latency is set 5. W shows Dummy Wait Cycles.

2. Address is in HEX.

\*

|   |         |                |                |                |                | -                                                                     |

|---|---------|----------------|----------------|----------------|----------------|-----------------------------------------------------------------------|

|   | Start   | Read Latency                                                          |

|   | Address | = 5            | = 6            | <br>= 9        | = 10           | = n                                                                   |

| * |         | (Write Latency                                                        |

|   |         | = 4)           | = 5)           | = 6)           | = 7)           | = n–1)                                                                |

|   | xxx0 H  | No wait        | No wait        | <br>No wait    | No wait        | No wait                                                               |

|   | xxx1 H  | No wait        | No wait        | <br>No wait    | No wait        | No wait                                                               |

|   | xxx2 H  | No wait        | No wait        | <br>No wait    | No wait        | No wait                                                               |

|   | xxx3 H  | No wait        | No wait        | <br>No wait    | No wait        | No wait                                                               |

|   | xxx4 H  | No wait        | No wait        | <br>No wait    | No wait        | No wait                                                               |

|   | xxx5 H  | No wait        | No wait        | <br>No wait    | No wait        | No wait                                                               |

|   | xxx6 H  | No wait        | No wait        | <br>No wait    | 1 cycle        | (n–9) Wait cycles are needed after boundary data output (n = 10).     |

|   | xxx7 H  | No wait        | No wait        | <br>1 cycle    | 2 cycle        | (n–8) Wait cycles are needed after<br>boundary data output. (n =/> 9) |

|   | xxx8 H  | No wait        | No wait        | <br>2 cycle    | 3 cycle        | (n–7) Wait cycles are needed after<br>boundary data output. (n =/> 8) |

|   | xxx9 H  | No wait        | No wait        | <br>3 cycle    | 4 cycle        | (n–6) Wait cycles are needed after<br>boundary data output. (n =/> 7) |

|   | xxxA H  | No wait        | 1 cycle        | <br>4 cycle    | 5 cycle        | (n–5) Wait cycles are needed after<br>boundary data output. (n =/> 6) |

|   | xxxB H  | 1 cycle        | 2 cycle        | <br>5 cycle    | 6 cycle        | (n–4) Wait cycles are needed after<br>boundary data output. (n =/> 5) |

|   | xxxC H  | 2 cycle        | 3 cycle        | <br>6 cycle    | 7 cycle        | (n–3) Wait cycles are needed after<br>boundary data output. (n =/> 5) |

|   | xxxD H  | 3 cycle        | 4 cycle        | <br>7 cycle    | 8 cycle        | (n–2) Wait cycles are needed after<br>boundary data output. (n =/> 5) |

|   | xxxE H  | 4 cycle        | 5 cycle        | <br>8 cycle    | 9 cycle        | (n–1) Wait cycles are needed after<br>boundary data output. (n =/> 5) |

|   | xxxF H  | 5 cycle        | 6 cycle        | <br>9 cycle    | 10 cycle       | n Wait cycles are needed after<br>boundary data output. (n =/> 5)     |

Table 4-2. Dummy Wait Cycles and Read Latency

**Remark** Address is in HEX.

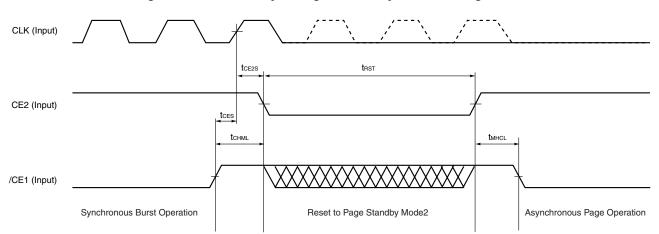

## 4.11 Reset Function from Synchronous Burst Mode to Asynchronous Page Mode

Even during the burst operation mode, the  $\mu$  PD46128512-X has the reset feature of changing synchronous burst mode to asynchronous page mode.

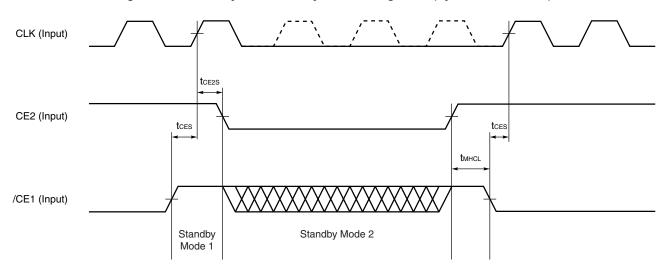

This reset is achieved by toggling CE2 signal HIGH  $\rightarrow$  LOW  $\rightarrow$  HIGH.

This reset to asynchronous page mode can be enable / disable with mode register setting.

Since the CE2 signal originally controls partial refresh function, the partial refresh operation can also be performed during the reset operation according to the density specified in the mode register. Please refer to the timing diagram and requirement below. Note that the timing requirement differs with the partial refresh density.

In case when the reset to asynchronous page mode is disabled in the mode register, only the partial refresh operation can be performed with CE2 signal toggling. Refer to **Figure 2-1**. **Standby Mode State Machine**.

Figure 4-11. Reset Entry Timing Chart to Asynchronous Page Mode

| Parameter                                                        | Symbol        | MIN. | MAX. | Unit | Note |

|------------------------------------------------------------------|---------------|------|------|------|------|

| Reset to asynchronous page and standby mode2 entry               | <b>t</b> CHML | 0    |      | ns   |      |

| /CE1 HIGH to CE2 LOW                                             |               |      |      |      |      |

| Reset to asynchronous page and standby mode2 to normal operation | <b>t</b> MHCL | 30   |      | ns   | 1    |

| CE2 HIGH to /CE1 LOW                                             |               | 300  |      | μs   | 2    |

| /CE1 = HIGH setup time to CLK                                    | tces          | 5    |      | ns   |      |

| CE2 = LOW hold time to CLK                                       | tce2s         | 1    |      | ns   |      |

| Reset time to asynchronous page mode                             | <b>t</b> RST  | 70   |      | ns   |      |

Notes 1. In case the density for partial refresh are 32M bits / 16M bits / 8M bits in standby mode2

2. In case the density for partial refresh is 0M bits in standby mode2

# NEC

# 5. Mode Register Settings

The µPD46128512-X has several modes, Page Read mode, Burst Read mode, Burst write mode, Single Write mode, Asynchronous Write mode, Deep Power Down mode, Partial Refresh mode.

Mode Resister setting defines Partial Refresh Density, Burst Length, Latency, Burst Sequence, Write mode (Burst or Single), Valid Clock Edge, Support burst write suspend/resume or not .

The several modes can be set using mode register. Since the initial value of the mode register at power application is undefined, be sure to set the mode register after initialization at power application.

#### 5.1 Mode Register Setting Method

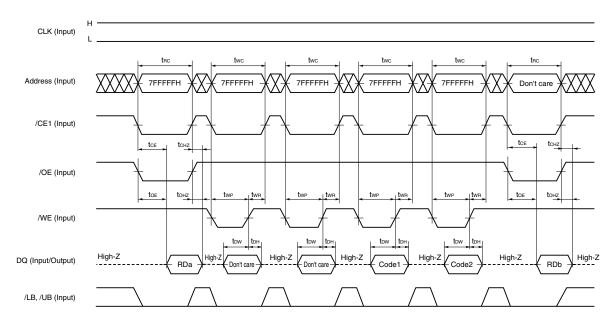

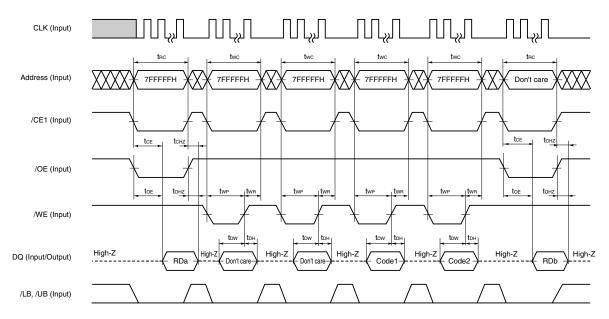

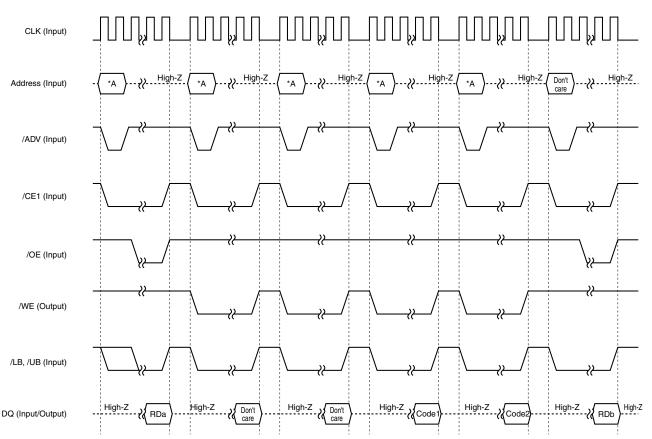

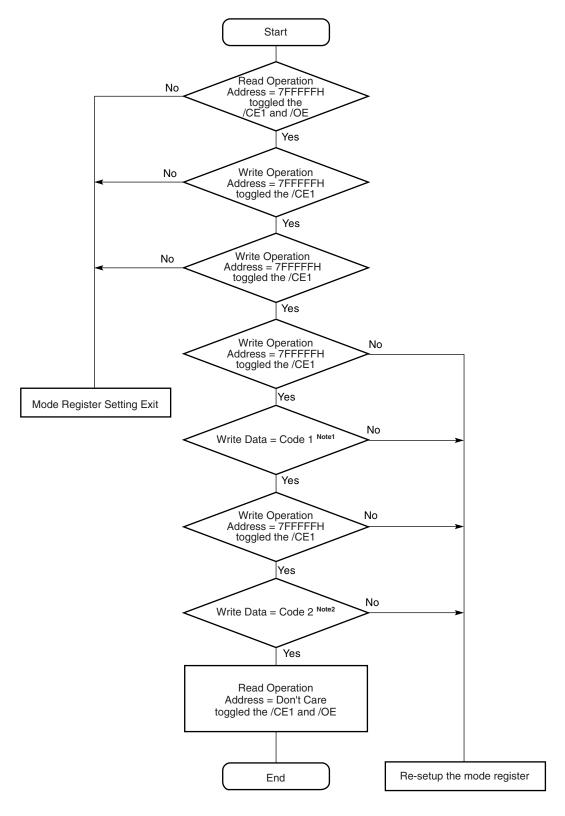

To set each mode, write any data twice, write specific data twice, read any address in succession after the highest address (7FFFFH) is read (6 cycles in total).

| Cycle     | Operation     | Address    | Data                              |

|-----------|---------------|------------|-----------------------------------|

| 1st cycle | Read 7FFFFH F |            | Read Data (RDa)                   |

| 2nd cycle | Write         | 7FFFFH     | RDa <sup>Note</sup> or Don't care |

| 3rd cycle | Write         | 7FFFFH     | RDa <sup>Note</sup> or Don't care |

| 4th cycle | Write         | 7FFFFH     | Code 1                            |

| 5th cycle | Write         | 7FFFFH     | Code 2                            |

| 6th cycle | Read          | Don't care | Read Data (RDb)                   |

**Note** In order to hold the highest address (7FFFFH) cell data during mode register setting, be sure to set the same data with 1st cycle read data in the 2nd and 3rd cycle (write cycle).

Commands are written to the command register. The command register is used to latch the addresses and data required for executing commands, and it does not have an exclusive memory area.

For the timing chart and flow chart, refer to Figure 9-1. Mode Register Setting Timing Chart (Asynchronous Timing + CLK fixed LOW/HIGH), Figure 9-2. Mode Register Setting Timing Chart (Asynchronous Timing + toggle CLK), Figure 9-3. Mode Register Setting Timing Chart (Synchronous Timing), Figure 9-4. Mode Register Setting Flow Chart. Table 5-1, Table 5-2 shows the commands and command sequences.

#### 5.2 Cautions for Setting Mode Register

Since, for the mode register setting, the internal counter status is judged by toggling /CE1 and /OE, toggle /CE1 at every cycle during entry (one read cycle, four write cycles and one read cycle), and toggle /OE like /CE1 at the first and the 6th read cycles.

If incorrect addresses or data are written, or if addresses or data are written in the incorrect order, the setting of the mode register is not performed correctly.

Cancellation of the mode register setting must be performed before the write in the 3rd bus cycle is determined. Cancellation in the 4th bus cycle or later should not be performed. If performed, data and previous register setting are not guaranteed, so the mode register must be re-setup after the 6th bus cycle is complete.

When the highest address (7FFFFH) is read consecutively two or more times, the mode register setting entries are not performed correctly. Mode setting is available after power application and read or write operation other than the highest address (7FFFFH) are performed.

Once the several modes have been set in the mode register, these settings are retained until they are set again, while applying the power supply. However, the mode register setting will become undefined except page mode (M = 1) if the power is turned off, so set the mode register again after power application. For the timing chart and flow chart, refer Figure 9-1. Mode Register Setting Timing Chart (Asynchronous Timing + CLK fixed LOW/HIGH), Figure 9-2. Mode Register Setting Timing Chart (Asynchronous Timing + toggle CLK), Figure 9-3. Mode Register Setting Timing Chart (Synchronous Timing), Figure 9-4. Mode Register Setting Flow Chart.

| Data Code   | Symbol | Function                | Value     | Description                      |

|-------------|--------|-------------------------|-----------|----------------------------------|

| DQ1, DQ0    | PS     | Partial Refresh Density | 00        | 32M bit                          |

|             |        |                         | 01        | 16M bit                          |

|             |        |                         | 10        | 8M bit                           |

|             |        |                         | 11        | 0M bit                           |

| DQ4 to DQ2  | BL     | Burst Length            | 010       | 8 word                           |

|             |        |                         | 011       | 16 word                          |

|             |        |                         | 111       | Continuous                       |

|             |        |                         | Others    | Reserved                         |

| DQ5         | М      | Function Mode           | 0         | Burst                            |

|             |        |                         | 1         | Page                             |

| DQ6         | VE     | Valid Clock Edge        | 0         | Falling Edge                     |

|             |        |                         | 1         | Rising Edge                      |

| DQ15 to DQ7 | -      | _                       | 111111111 | Reserved (All "1" are necessary) |

Table 5-1. Mode Register Definition (4th Bus Cycle)

| Table 5-2. | Mode | Register | Definition | (5th | Bus Cycle) |

|------------|------|----------|------------|------|------------|

|            | mouc | Register | Deminion   | (our | Dus Oycic) |

| Data Code   | Symbol | Function           | Value    | Description                          |

|-------------|--------|--------------------|----------|--------------------------------------|

| DQ2 to DQ0  | RL     | Read Latency       | 010      | 5 (Write Latency = 4)                |

|             |        | (Write Latency)    | 011      | 6 (5)                                |

|             |        |                    | 100      | 7 (6)                                |

|             |        |                    | 101      | 8 (7)                                |

|             |        |                    | 110      | 9 (8)                                |

|             |        |                    | 111      | 10 (9)                               |

|             |        |                    | Others   | Reserved                             |

| DQ3         | SW     | Single Write       | 0        | Burst Read & Burst Write             |

|             |        |                    | 1        | Burst Read & Single Write            |

| DQ4         | WC     | /WE Control        | 0        | Single clock control without suspend |

|             |        |                    | 1        | Level control with suspend           |

| DQ6, DQ5    | -      | _                  | 11       | Reserved (All "1" are necessary)     |

| DQ7         | RP     | Reset to Page mode | 0        | Reset available to Page mode         |

|             |        |                    | 1        | Reset not available to Page mode     |

| DQ15 to DQ8 | -      | -                  | 11111111 | Reserved (All "1" are necessary)     |

#### 5.3 Partial Refresh Density

The density for performing refresh in power down mode can be set with mode register. Setting DQ1 and DQ0 to 00 at the 4th bus cycle sets a partial refresh density of 32 M-bit hold; setting DQ1 and DQ0 to 01 at the 4th bus cycle sets a partial refresh density of 16 M-bit hold; setting DQ1 and DQ0 to 10 at the 4th bus cycle sets a partial refresh density of 8 M-bit hold; and setting DQ1 and DQ0 to 11 at the 4th bus cycle sets a partial refresh density of 0 (no hold).

Since the Partial Refresh mode is not entered unless CE2 = LOW, when partial refresh is not used, it is not necessary to set the mode register.

#### 5.4 Burst Length

Sets the burst length in the burst mode. Setting DQ4 to DQ2 to 010 at the 4th bus sets 8word of burst length; setting DQ4 to DQ2 to 011 at the 4th bus cycle sets 16word of burst length; setting DQ4 to DQ2 to 111 at the 4th bus cycle sets continuous of burst length

#### 5.5 Function Mode

Select function mode. Setting DQ5 to 0 at the 4th bus sets a function mode of burst and setting DQ5 to 1 at the 4th bus sets a function mode of page. After power application, page mode is set as an initial state.

#### 5.6 Valid Clock Edge

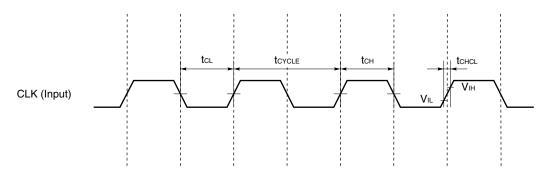

Select valid clock edge (Rising edge or Falling edge) in the burst mode. Setting DQ6 to 0 at the 4th bus cycle sets clock falling edge; setting DQ6 to 1 at the 4th bus cycle sets clock rising edge.

#### 5.7 Read Latency (Write Latency)

Sets the number of clock cycles (latency) between the address input and the output of the first data in the burst read mode, the address input and the write data input in the burst write mode. Setting DQ2 to DQ0 to 010 at the 5th bus cycle sets read latency of 5; setting DQ2 to DQ0 to 011 at the 5th bus sets read latency of 6; setting DQ2 to DQ0 to 100 at the 5th bus sets read latency of 7; setting DQ2 to DQ0 to 101 at the 5th bus sets read latency of 8; setting DQ2 to DQ0 to 110 at the 5th bus sets read latency of 9; setting DQ2 to DQ0 to 111 at the 5th bus sets read latency of 10. Once specific RL is set through Mode Register Setting sequence, write latency, that is the number of clock cycles between address input and first write data input, is automatically set to RL-1.

For the latency count, refer to Figure 4-1. Latency Definition

#### 5.8 Single Write

Sets the write mode. Setting DQ3 to 0 at the 5th bus cycle sets burst write mode; setting DQ3 to 1 at the 5th bus cycle sets single write mode.

#### 5.9 /WE Control

Sets the /WE timing in burst write operation and burst write suspend / resume available or not. Setting DQ4 to 0 at the 5th bus cycle sets /WE single clock control, and burst write suspend / resume are not supported. In single clock control, /WE is available at the 1st clock edge of /ADV = LOW; setting DQ4 to 1 at the 5th bus cycle sets /WE level control, and burst write suspend / resume are supported. In level control, /WE is sure to transfer LOW to HIGH after latching last write data in burst write operation.

Refer to Figure 8-8. Synchronous Burst Write Cycle Timing Chart (/WE level Control), Figure 8-9. Synchronous Burst Write Cycle Timing Chart (/WE single clock control), Figure 8-11. Synchronous Burst Write Suspend Timing Chart.

#### 5.10 Reset to Page Mode

Sets the Reset function from synchronous burst mode to asynchronous page mode. Setting DQ7 to 0 at the 5th bus cycle sets reset available from synchronous burst mode to asynchronous page mode. Setting DQ7 to 1 at the 5th bus cycle sets reset unavailable.

#### 5.11 Reserved Bits

Reserved bits must be 1 because reserved bits are used for internal test mode entry. Be sure to set DQ15 to DQ7 to 1 at the 4th and DQ15 to DQ8 and DQ6 and DQ5 at the 5th bus cycles.

#### ★ 5.12 Cautions for Timing Chart of Setting Mode Register

Timing charts for setting mode register are following 3 methods.

<Setting 1> Setting method by CLK fixed HIGH or LOW at asynchronous timing (asynchronous timing) <Setting 2> Setting method by toggling CLK at asynchronous timing (asynchronous timing+ toggle CLK) <Setting 3> Setting method at synchronous timing (synchronous timing)

For timing chart, refer to Figure 9-1. Mode Register Setting Timing Chart (asynchronous timing+ CLK fixed LOW/HIGH), Figure 9-2. Mode Register Setting Timing Chart (asynchronous timing+ toggle CLK), Figure 9-3. Mode Register Setting Timing Chart (synchronous timing).

It is recommended to set Mode Register contents through <Setting 1>, since <Setting 1> is used regardless of device status, asynchronous or synchronous.

<Setting 2> procedure can be performed when the device is in the asynchronous (page) mode. In case the mode register setting is possible only with <Setting 2> procedure, "reset to page" function using the CE2 signal toggling will be required in changing the operation from synchronous (burst) mode to asynchronous (page) mode. (Refer to **4.11 Reset Function from Synchronous Burst Mode to Asynchronous Page Mode**)

<Setting 3> procedure can be performed when the device is in the synchronous (burst) mode.

Figure 5-1. Mode Register Setting State Machine

# 6. Electrical Specifications

# **Absolute Maximum Ratings**

| Parameter                     | Symbol | Condition | Rating                       | Unit |

|-------------------------------|--------|-----------|------------------------------|------|

| Supply voltage                | Vcc    |           | -0.5 <sup>Note</sup> to +2.5 | V    |

| Supply voltage for Output     | VccQ   |           | -0.5 <sup>Note</sup> to +2.5 | V    |

| Input / Output voltage        | VT     |           | -0.5 <sup>Note</sup> to 2.5  | V    |

| Operating ambient temperature | TA     |           | -30 to +85                   | °C   |

| Storage temperature           | Tstg   |           | -55 to +125                  | °C   |

Note -1.0 V (MIN.) (Pulse width: 30 ns)

Caution Exposing the device to stress above those listed in Absolute Maximum Rating could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Parameter                     | Symbol                | Condition | MIN.       | MAX.    | Unit |

|-------------------------------|-----------------------|-----------|------------|---------|------|

| Supply voltage                | Vcc Note1             |           | 1.7        | 2.0     | V    |

| Supply voltage for Output     | VccQ <sup>Note1</sup> |           | 1.7        | 2.0     | V    |

| Input HIGH voltage            | VIH                   |           | 0.8Vcc     | Vcc+0.3 | V    |

| Input LOW voltage             | VIL                   |           | -0.3 Note2 | 0.2Vcc  | V    |

| Operating ambient temperature | TA                    |           | -30        | +85     | °C   |

Notes 1. Use same voltage condition (Vcc = VccQ)

2. -0.5 V (MIN.) (Pulse width: 30 ns)

# Capacitance (T<sub>A</sub> = 25°C, f = 1 MHz)

| Parameter                  | Symbol | Test condition | MIN. | TYP. | MAX. | Unit |

|----------------------------|--------|----------------|------|------|------|------|

| Input capacitance          | CIN    | $V_{IN} = 0 V$ |      |      | 8    | pF   |

| Input / Output capacitance | CDQ    | $V_{DQ} = 0 V$ |      |      | 10   | pF   |

Remarks 1. VIN: Input voltage, VDQ: Input / Output voltage

**2.** These parameters are not 100% tested.

| Parameter Symbol       |       | Test con                                                           | Density of           | MIN.           | TYP. <sup>Note1</sup> | MAX.    | Unit   |    |

|------------------------|-------|--------------------------------------------------------------------|----------------------|----------------|-----------------------|---------|--------|----|

|                        |       |                                                                    |                      | data hold      |                       |         |        |    |

| Input leakage current  | Lu    | V <sub>IN</sub> = 0 V to V <sub>CC</sub>                           |                      | -1.0           |                       | +1.0    | μA     |    |

| DQ leakage current     | Ilo   | $V_{DQ}$ = 0 V to V <sub>CC</sub> Q, /CE1                          | = V <sub>IH</sub> or |                | -1.0                  |         | +1.0   | μA |

|                        |       | $WE = V_{IL} \text{ or } OE = V_{IH}$                              |                      |                |                       |         |        |    |

| Operating supply       | ICCA1 | $/CE1 = V_{IL}, I_{DQ} = 0 \text{ mA}, Cycle time = 70 \text{ ns}$ |                      |                |                       |         | 60     | mA |

| current                |       | Asynchronous mode                                                  | Cycle time = 85 ns   |                |                       |         | 50     |    |

|                        | ICCA2 | /CE1 = VIL, Frequency =                                            |                      |                |                       | 50      | mA     |    |

|                        |       | IDQ = 0 mA, burst length                                           | = 1,                 |                |                       |         |        |    |

|                        |       | Synchronous mode                                                   |                      |                |                       |         |        |    |

| Operating supply Burst | Іссаз | /CE1 = V <sub>IL</sub> , Frequency = 83MHz, RL = 7,                |                      |                |                       |         | 30     | mA |

| current                |       | IDQ = 0 mA, burst length                                           |                      |                |                       |         |        |    |

| Standby supply current | ISB1  | $/CE1 \ge V_{CC} - 0.2 V, CE2$                                     | 128M bits Note2      |                | 80                    | 250     | μA     |    |

|                        | ISB2  | $/CE1 \ge V_{CC} - 0.2 V, CE2$                                     | 32M bits Note2       |                | T.B.D.                | T.B.D.  |        |    |

|                        |       |                                                                    |                      | 16M bits Note2 |                       | T.B.D.  | T.B.D. |    |

|                        |       |                                                                    |                      | 8M bits Note2  |                       | T.B.D.  | T.B.D. |    |

|                        |       |                                                                    |                      | 0M bit         |                       | 15      | 65     |    |

| Output HIGH voltage    | Vон   | Iон <b>= -0.5 mA</b>                                               |                      |                | 0.8VccQ               |         |        | V  |

| Output LOW voltage     | Vol   | IoL = 1 mA                                                         |                      |                |                       | 0.2VccQ | V      |    |

#### DC Characteristics (Recommended Operating Conditions Unless Otherwise Noted)

**Notes 1.** TYP. means reference value measured at  $T_A = 25^{\circ}C$ . This value is not a guarantee value.

**2.** The current measured more than 30 ms after standby mode entry (/CE1 changes from LOW to HIGH). It is specified as 2 mA (MAX.) in case of less than 30 ms after /CE1 transition.

Remark VIN: Input voltage, VDQ: Input / Output voltage

# AC Characteristics (Recommended Operating Conditions Unless Otherwise Noted)

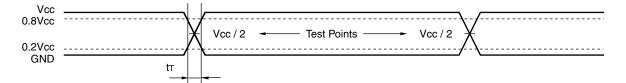

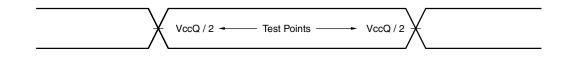

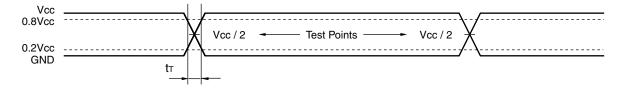

# AC Test Conditions

#### [For DQ pins]

#### Input Waveform (Rise and Fall Time $\leq$ 3 ns)

| Parameter       | Symbol | Test Condition                                      | MAX. | Unit |

|-----------------|--------|-----------------------------------------------------|------|------|

| Transition time | tτ     | The transition time from $0.8V_{CC}$ to $0.2V_{CC}$ | 3    | ns   |

|                 |        | and from 0.2Vcc to 0.8Vcc                           |      |      |

#### **Output Waveform**

## Output Load

30 pF

#### [For all other input pins]

# Input Waveform (Rise and Fall Time $\leq$ 3 ns)

| Parameter       | Symbol | Test Condition                                      | MAX. | Unit |

|-----------------|--------|-----------------------------------------------------|------|------|

| Transition time | tτ     | The transition time from $0.8V_{CC}$ to $0.2V_{CC}$ | 3    | ns   |

|                 |        | and from 0.2Vcc to 0.8Vcc                           |      |      |

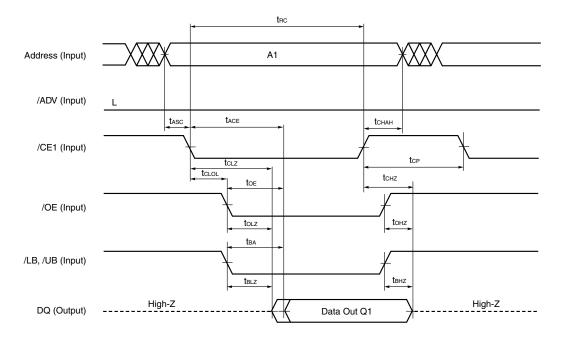

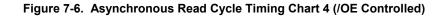

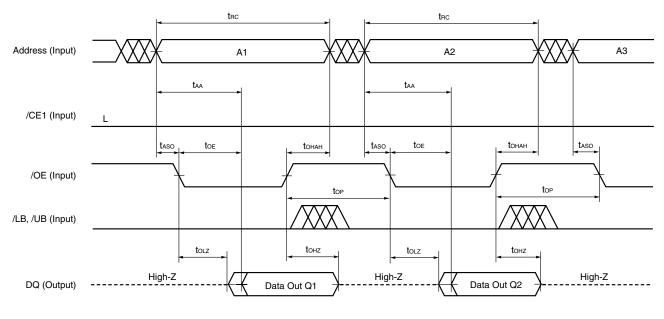

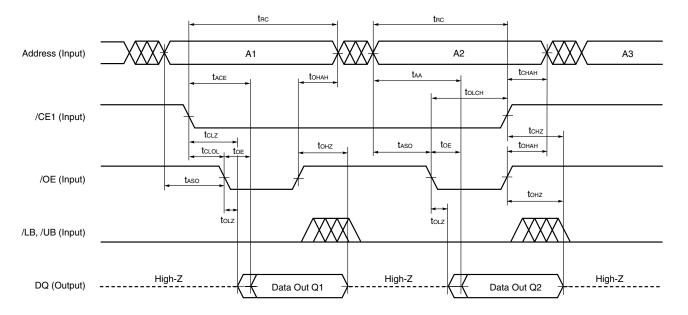

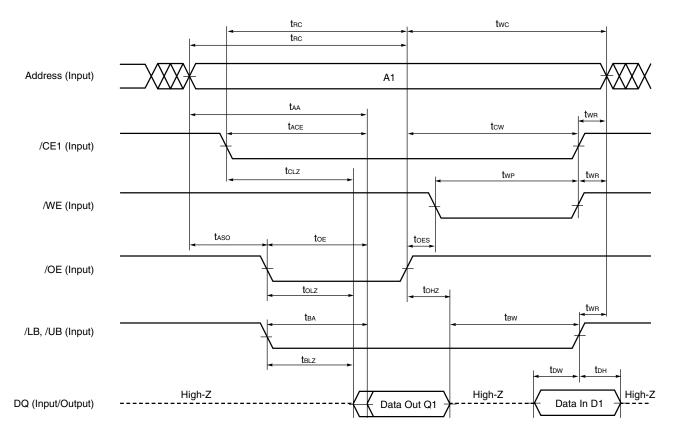

# 7. Asynchronous AC Specification, Timing Chart

# Asynchronous Read Cycle

| Parameter                            | Symbol -E9X, -E11X |      | -E10X, -E12X |      | Unit    | Note |   |

|--------------------------------------|--------------------|------|--------------|------|---------|------|---|

|                                      |                    | MIN. | MAX.         | MIN. | MAX.    |      |   |

| Read cycle time                      | <b>t</b> RC        | 70   |              | 85   |         | ns   | 1 |

| Address access time                  | taa                |      | 70           |      | 85      | ns   |   |

| /CE1 access time                     | <b>t</b> ACE       |      | 70           |      | 85      | ns   |   |

| /OE to output valid                  | toe                |      | 45           |      | 60      | ns   |   |

| /LB, /UB to output valid             | tва                |      | 45           |      | 60      | ns   |   |

| Output hold from address change      | tон                | 3    |              | 3    |         | ns   |   |

| Page read cycle time                 | <b>t</b> PRC       | 20   |              | 25   |         | ns   |   |

| Page access time                     | <b>t</b> PAA       |      | 20           |      | 25      | ns   |   |

| /CE1 to output in low impedance      | tclz               | 10   |              | 10   |         | ns   | 2 |

| /OE to output in low impedance       | tolz               | 5    |              | 5    |         | ns   |   |

| /LB, /UB to output in low impedance  | <b>t</b> BLZ       | 5    |              | 5    |         | ns   |   |

| /CE1 to output in high impedance     | tснz               |      | 9            |      | 9       | ns   |   |

| /OE to output in high impedance      | tонz               |      | 9            |      | 9       | ns   |   |

| /LB, /UB to output in high impedance | tвнz               |      | 9            |      | 9       | ns   |   |

| Address set to /CE1 LOW              | tasc               | –15  |              | -15  |         | ns   |   |

| Address invalid time                 | tax                |      | 15           |      | 15      | ns   | 3 |

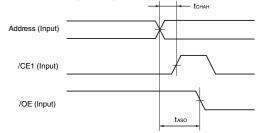

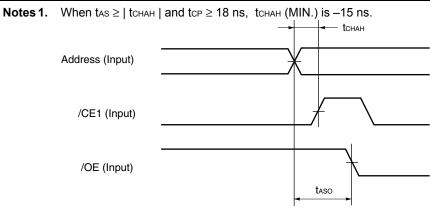

| Address set to /OE LOW               | taso               | 0    |              | 0    |         | ns   |   |

| /OE HIGH to address hold             | tонан              | -5   |              | -5   |         | ns   |   |

| /CE1 HIGH to address hold            | <b>t</b> снан      | 0    |              | 0    |         | ns   | 4 |

| /CE1 LOW to /OE LOW                  | <b>t</b> CLOL      | -5   | +10,000      | -5   | +10,000 | ns   |   |

| /OE LOW to /CE1 HIGH                 | <b>t</b> olch      | 45   |              | 60   |         | ns   |   |

| Address set to /ADV HIGH             | tasv               | 7    |              | 7    |         | ns   |   |

| /ADV HIGH to address hold            | tан                | 3    |              | 3    |         | ns   |   |

| /ADV LOW pulse width                 | tvpl               | 7    |              | 7    |         | ns   |   |

| /CE1 HIGH pulse width                | tc₽                | 10   |              | 10   |         | ns   |   |

| /LB, /UB HIGH pulse width            | tвр                | 10   |              | 10   |         | ns   |   |

| /OE HIGH pulse width                 | top                | 10   | 10,000       | 10   | 10,000  | ns   | 5 |

| /OE HIGH to /WE set                  | toes               | 10   | 10,000       | 10   | 10,000  | ns   | ] |

| /WE HIGH to /OE set                  | tоен               | 10   | 10,000       | 10   | 10,000  | ns   | ] |

Notes 1. Output load: 30 pF

2. Output load: 5 pF

- 3. tax (MAX.) is applied while /CE1, /OE and /ADV are being hold at LOW.

- 4. When taso  $\geq$  | tchah |, tchah (MIN.) is -15 ns.

5. top, toes and toeh (MAX.) are applied while /CE1 is being hold at LOW.

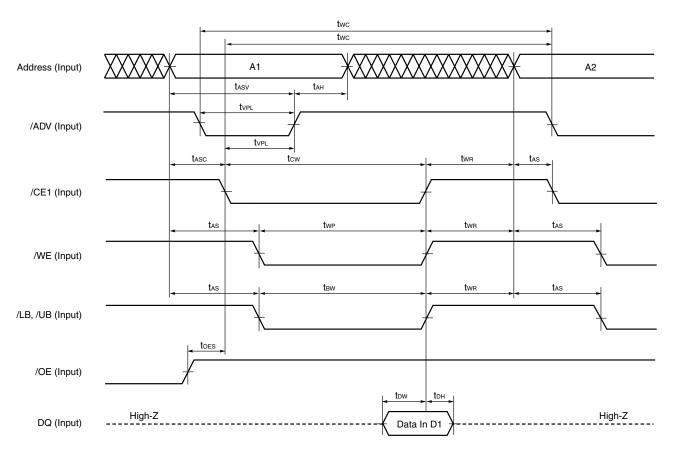

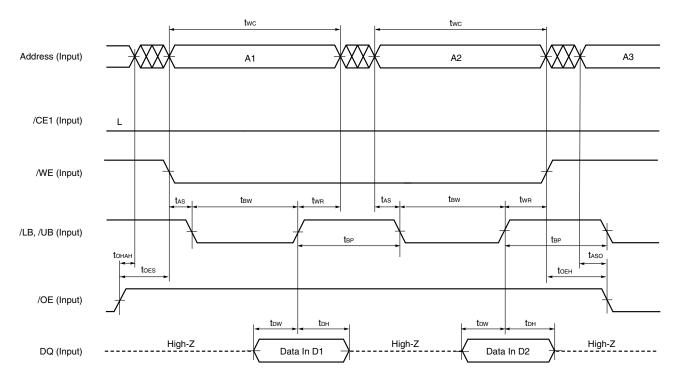

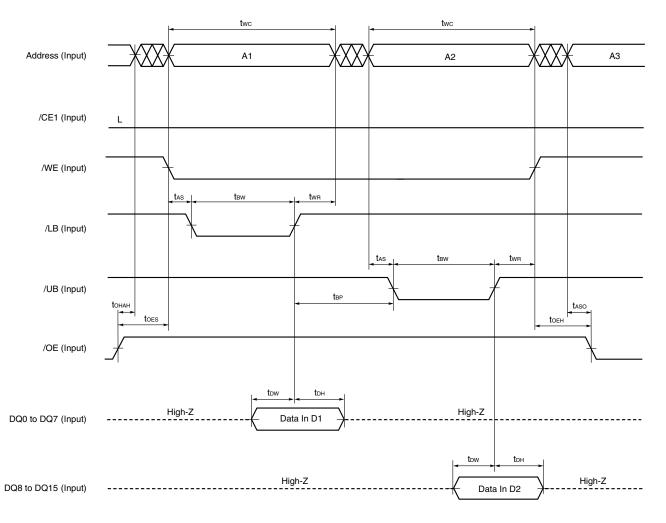

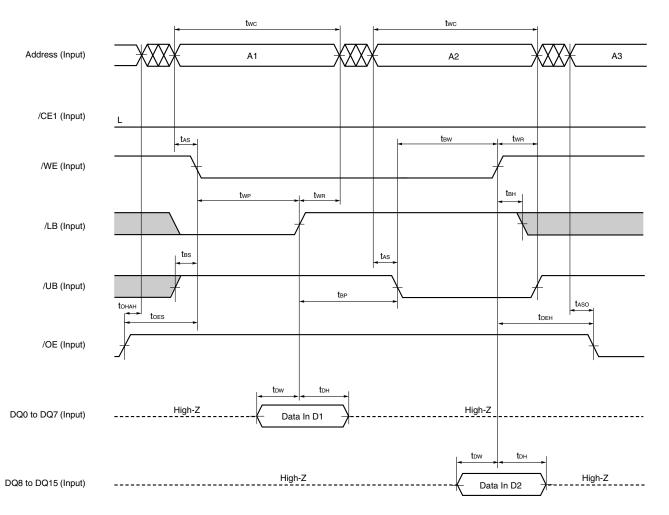

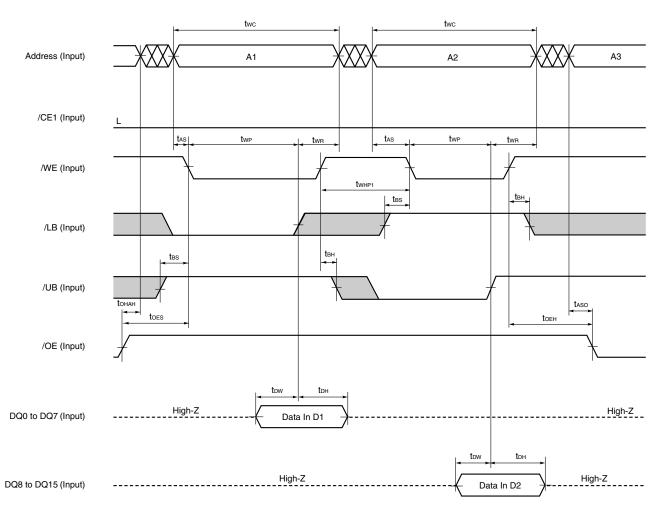

#### Asynchronous Write Cycle

| Parameter                                                  | Symbol | -E9X, | -E9X, -E11X |      | X, -E12X | Unit | Note |

|------------------------------------------------------------|--------|-------|-------------|------|----------|------|------|

|                                                            |        | MIN.  | MAX.        | MIN. | MAX.     |      |      |

| Write cycle time                                           | twc    | 70    |             | 85   |          | ns   |      |

| /CE1 to end of write                                       | tcw    | 50    |             | 60   |          | ns   |      |

| Address valid to end of write                              | taw    | 55    |             | 60   |          | ns   |      |

| /LB, /UB to end of write                                   | tвw    | 50    |             | 60   |          | ns   |      |

| Write pulse width                                          | twp    | 50    |             | 55   |          | ns   |      |

| Write recovery time                                        | twr    | 0     |             | 0    |          | ns   |      |

| Write recovery time (/WE = HIGH $\rightarrow$ /CE1 = HIGH) | twнсн  | 0     | 10,000      | 0    | 10,000   | ns   |      |

| /CE1 pulse width                                           | tcp    | 10    |             | 10   |          | ns   |      |

| /LB, /UB HIGH pulse width                                  | tвр    | 10    |             | 10   |          | ns   |      |

| /WE HIGH pulse width                                       | twнp   | 10    |             | 10   |          | ns   |      |

| /WE HIGH pulse width (/CE1 = LOW)                          | twhp1  | 10    | 10,000      | 10   | 10,000   | ns   |      |

| Address setup time                                         | tas    | 0     |             | 0    |          | ns   |      |

| /CE1 HIGH to address hold                                  | tснан  | 0     |             | 0    |          | ns   | 1    |

| /LB, /UB HIGH to address hold                              | tвнан  | 0     |             | 0    |          | ns   |      |

| /LB, /UB byte mask setup time                              | tвs    | 0     |             | 0    |          | ns   |      |

| /LB, /UB byte mask hold time                               | tвн    | 0     |             | 0    |          | ns   |      |

| /LB, /UB byte mask over wrap time                          | tвwo   | 30    |             | 30   |          | ns   |      |

| Data valid to end of write                                 | tow    | 25    |             | 25   |          | ns   |      |

| Data hold time                                             | tон    | 0     |             | 0    |          | ns   |      |

| Address set to /ADV HIGH                                   | tasv   | 7     |             | 7    |          | ns   |      |

| /ADV HIGH to address hold                                  | tан    | 3     |             | 3    |          | ns   |      |

| /ADV LOW pulse width                                       | tvpl   | 7     |             | 7    |          | ns   |      |

| /OE HIGH to /WE set                                        | toes   | 10    | 10,000      | 10   | 10,000   | ns   | 2    |

| /WE HIGH to /OE set                                        | tоен   | 10    | 10,000      | 10   | 10,000   | ns   | ]    |

2. toes and toeh (MAX.) are applied while /CE1 is being hold at LOW.

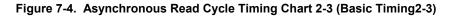

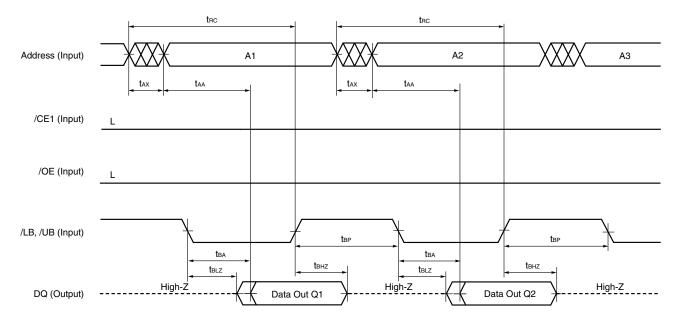

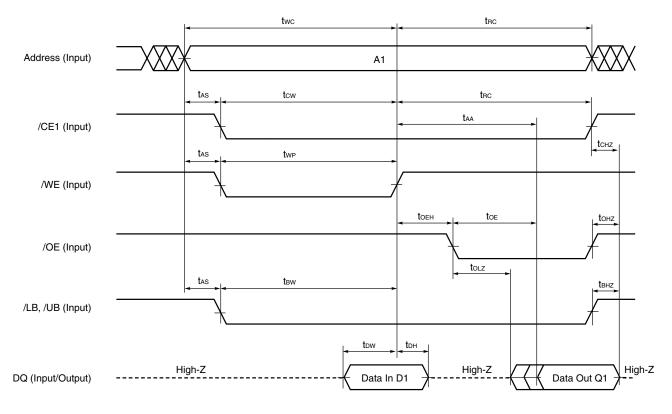

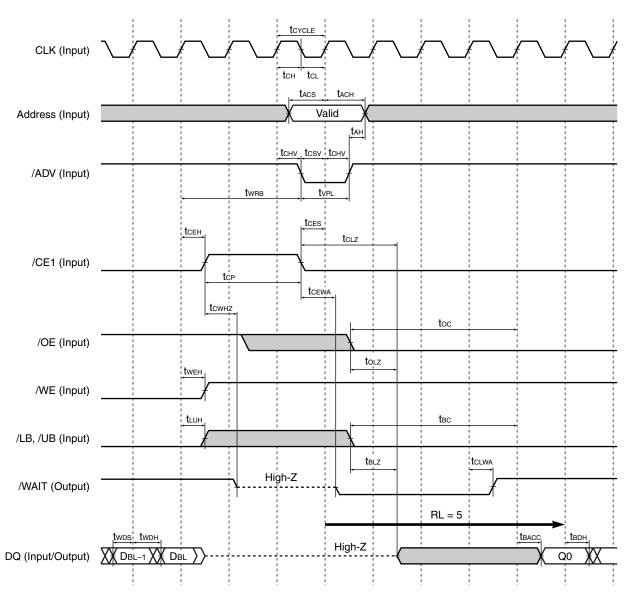

Figure 7-1. Asynchronous Read Cycle Timing Chart 1 (Basic Timing1)

2. CLK should be fixed HIGH or LOW.

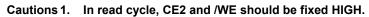

Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

2. CLK should be fixed HIGH or LOW.

Preliminary Data Sheet M17507EJ2V0DS

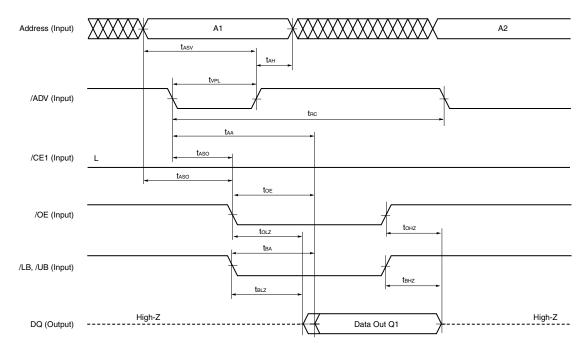

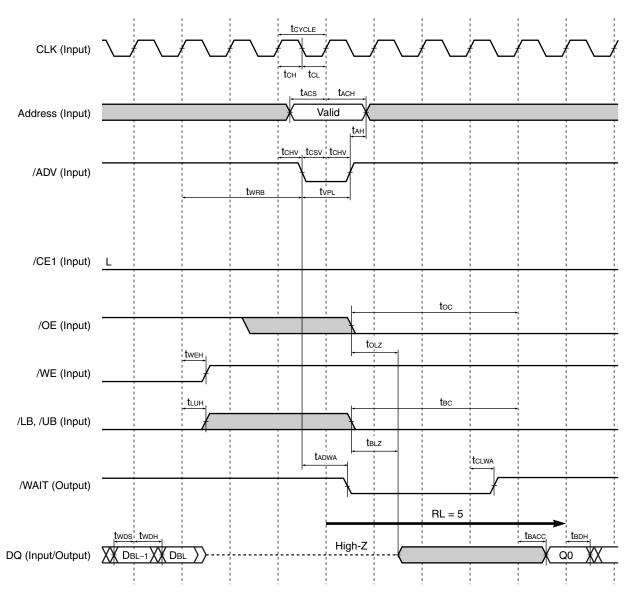

Figure 7-3. Asynchronous Read Cycle Timing Chart 2-2 (Basic Timing2-2)

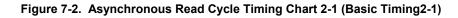

#### Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

2. CLK should be fixed HIGH or LOW.

#### Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

2. CLK should be fixed HIGH or LOW.

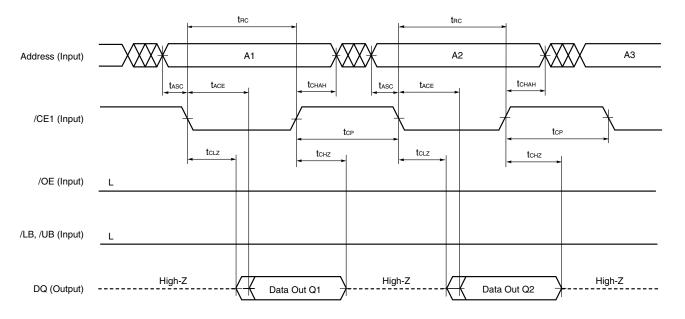

### Figure 7-5. Asynchronous Read Cycle Timing Chart 3 (/CE1 Controlled)

Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

2. /ADV should be fixed LOW or toggled HIGH  $\rightarrow$  LOW  $\rightarrow$  HIGH. CLK should be fixed HIGH or LOW.

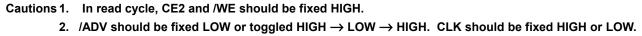

#### Figure 7-7. Asynchronous Read Cycle Timing Chart 5 (/CE1, /OE Controlled)

Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

2. /ADV should be fixed LOW or toggled HIGH → LOW → HIGH. CLK should be fixed HIGH or LOW.

Figure 7-8. Asynchronous Read Cycle Timing Chart 6 (Address Controlled)

Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

2. /ADV should be fixed LOW or toggled HIGH  $\rightarrow$  LOW  $\rightarrow$  HIGH. CLK should be fixed HIGH or LOW.

## Figure 7-9. Asynchronous Read Cycle Timing Chart 7 (/LB, /UB Controlled)

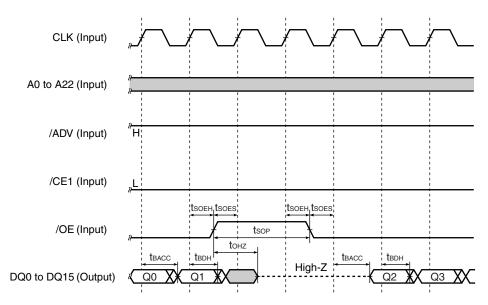

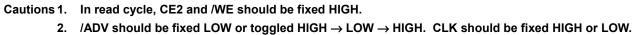

Figure 7-10. Asynchronous Page Read Cycle Timing Chart

Cautions 1. In read cycle, CE2 and /WE should be fixed HIGH.

- 2. /LB and /UB should be fixed LOW.

- 3. /ADV should be fixed LOW. CLK should be fixed HIGH or LOW.

- 4. Fix /CE1 and /OE to LOW throughout a page operation.

- 5. Arbitrary order and combination of A0-A3 is possible in the page operation.

- \*

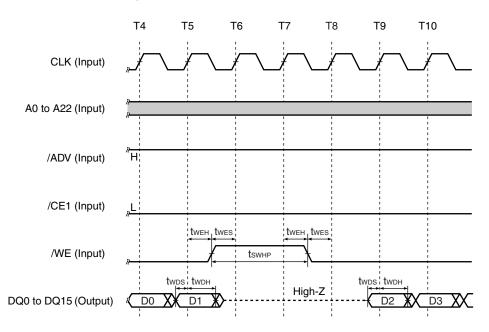

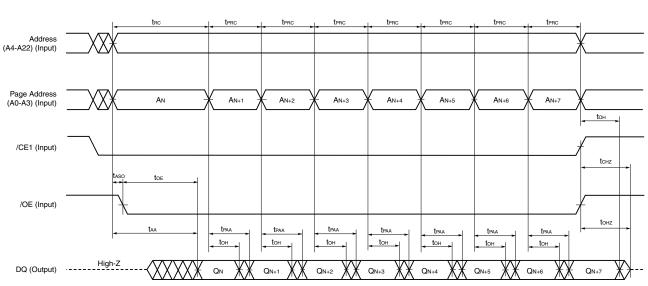

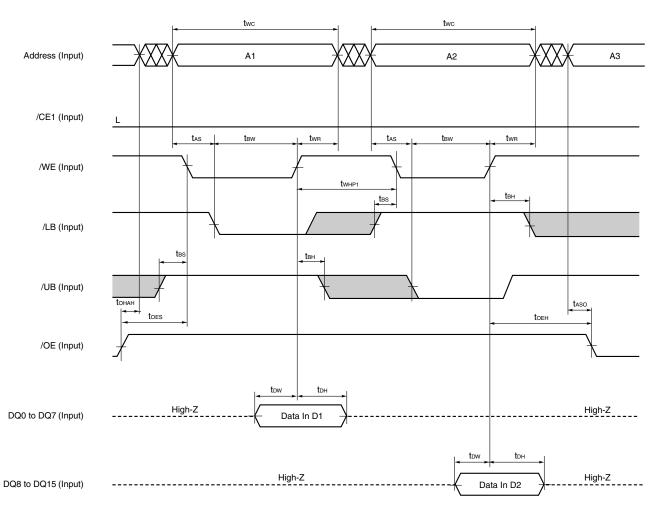

## Figure 7-11. Asynchronous Write Cycle Timing Chart 1 (Basic Timing1)

- Cautions 1. During address transition, at least one of pins /CE1 and /WE, or both of /LB and /UB pins should be inactivated.

- 2. Do not input data to the DQ pins while they are in the output state.

- 3. In write cycle, CE2 and /OE should be fixed HIGH.

- 4. CLK should be fixed HIGH or LOW.

- ★ **Remark** Write operation is done during the overlap time of LOW of following signals.

- /CE1

- /WE

- /LB and/or /UB

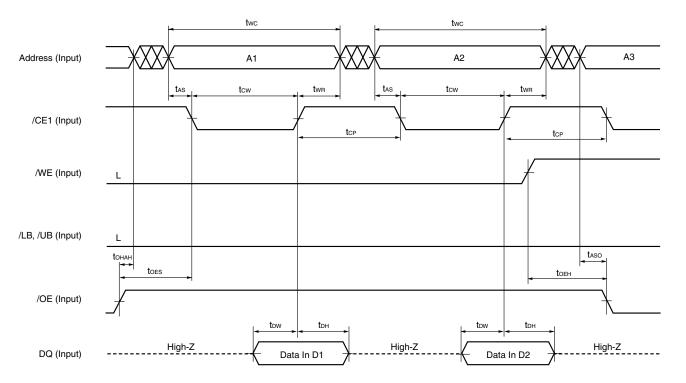

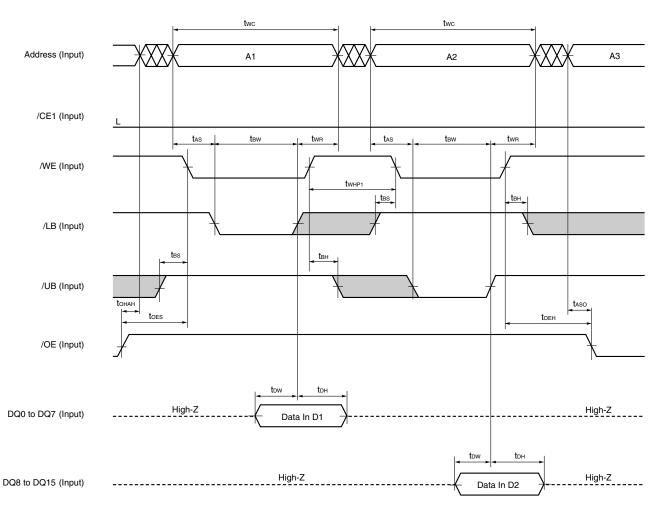

## Figure 7-12. Asynchronous Write Cycle Timing Chart 2 (Basic Timing2)

- Cautions 1. During address transition, at least one of pins /CE1 and /WE, or both of /LB and /UB pins should be inactivated.

- 2. Do not input data to the DQ pins while they are in the output state.

- 3. In write cycle, CE2 and /OE should be fixed HIGH.

- 4. CLK should be fixed HIGH or LOW.

- **Remark** Write operation is done during the overlap time of LOW of following signals.

- /CE1

- /WE

- /LB and/or /UB

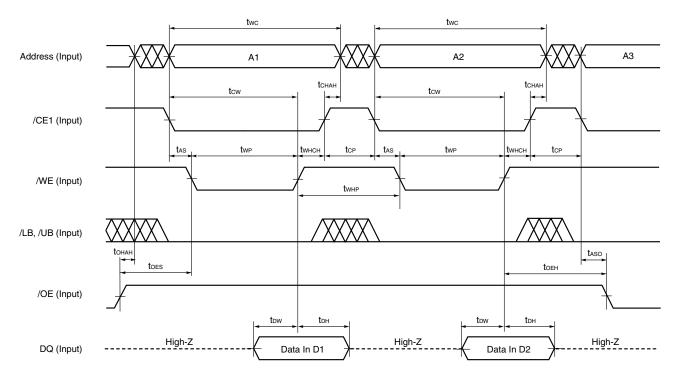

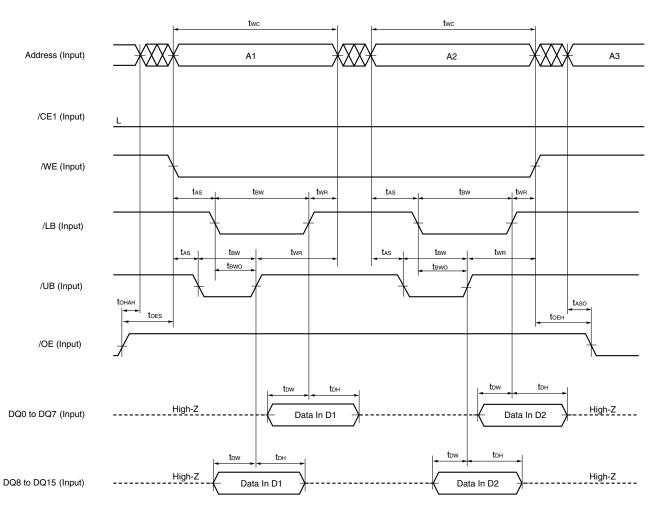

## Figure 7-13. Asynchronous Write Cycle Timing Chart 3 (/CE1 Controlled)

- Cautions 1. During address transition, at least one of pins /CE1 and /WE, or both of /LB and /UB pins should be inactivated.

- 2. Do not input data to the DQ pins while they are in the output state.

- 3. In write cycle, CE2 and /OE should be fixed HIGH.

- 4. /ADV should be fixed LOW or toggled HIGH  $\rightarrow$  LOW  $\rightarrow$  HIGH. CLK should be fixed HIGH or LOW.

- **Remark** Write operation is done during the overlap time of LOW of following signals.

- /CE1

- /WE

- /LB and/or /UB

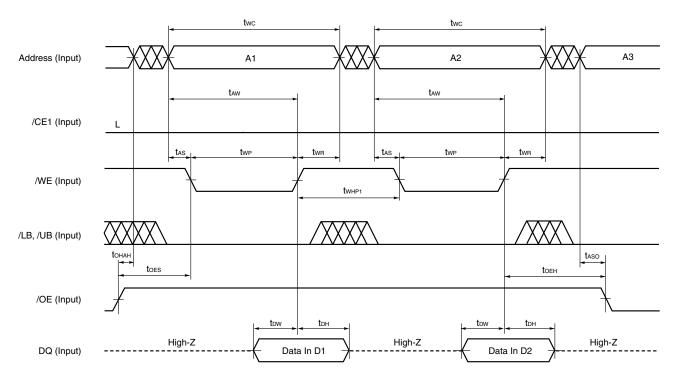

### Figure 7-14. Asynchronous Write Cycle Timing Chart 4 (/WE Controlled)

- Cautions 1. During address transition, at least one of pins /CE1 and /WE, or both of /LB and /UB pins should be inactivated.

- 2. Do not input data to the DQ pins while they are in the output state.

- 3. In write cycle, CE2 and /OE should be fixed HIGH.