## **Features**

- ARM7TDMI® ARM® Thumb® Processor Core

- High-performance 32-bit RISC

- High-density 16-bit Thumb Instruction Set

- Leader in MIPS/Watt

- Embedded ICE (In Circuit Emulation)

- 4 Kbytes Internal RAM

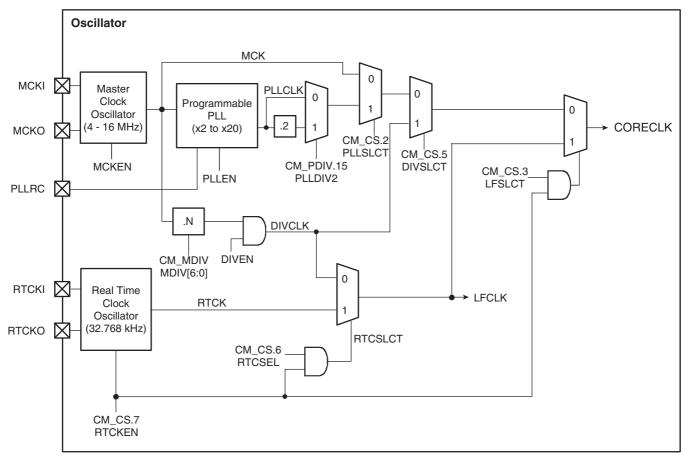

- Clock Manager (CM) with Programmable PLL

- PLL Multiplier from x2 to x20

- 32.768 kHz Oscillator for Low-power Operation

- Master Clock Divider/multiplier

- Fully Programmable External Bus Interface (EBI) through Advanced Memory Controller (AMC)

- Maximum External Address Space of 16 Mbytes, Up to Six Chip Select Lines

- 8-level Priority, Vectored Interrupt Controller

- Individually Maskable, Two External Interrupts including One Fast Interrupt Line

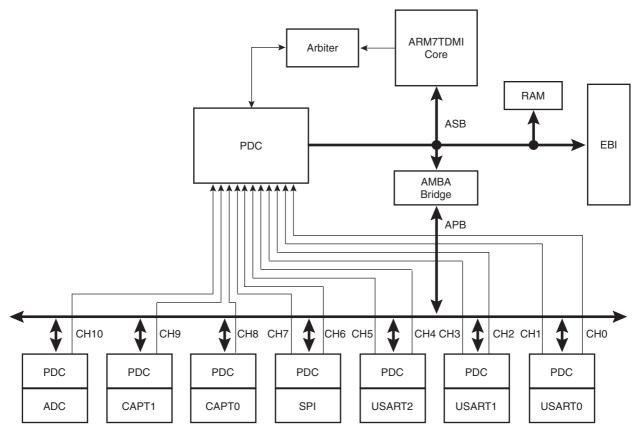

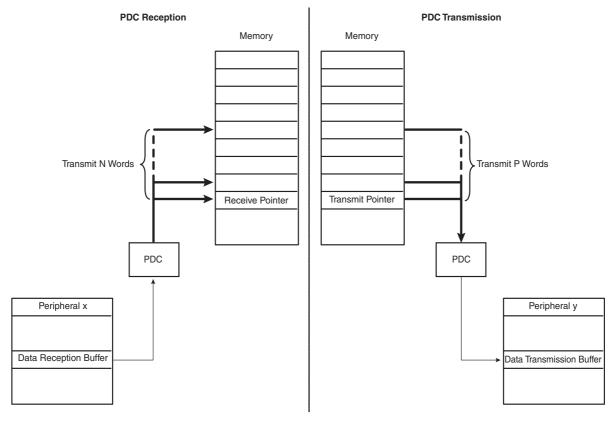

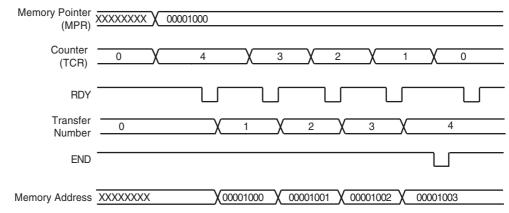

- 11-channel Peripheral Data Controller (PDC)

- 49 Programmable I/O Lines

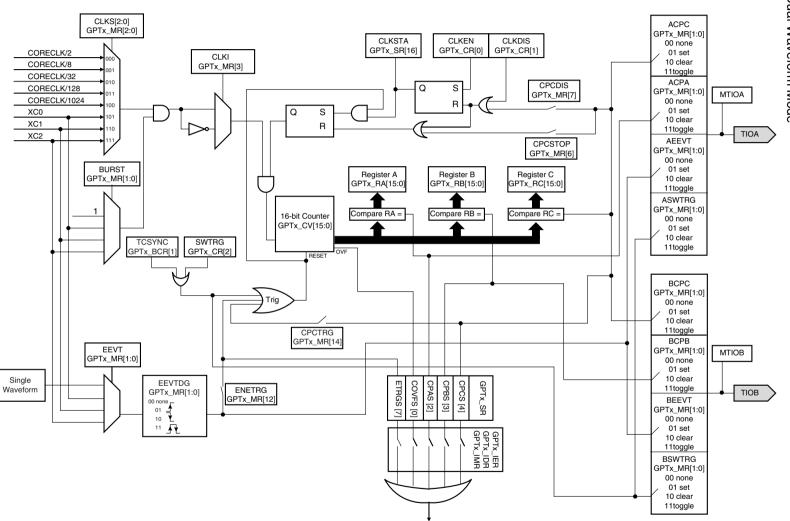

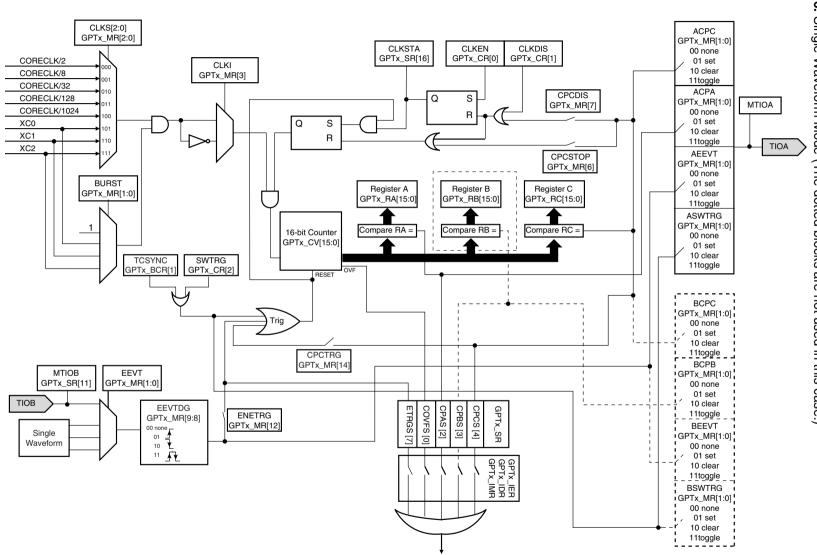

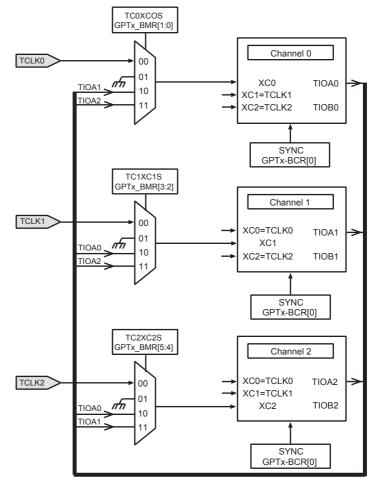

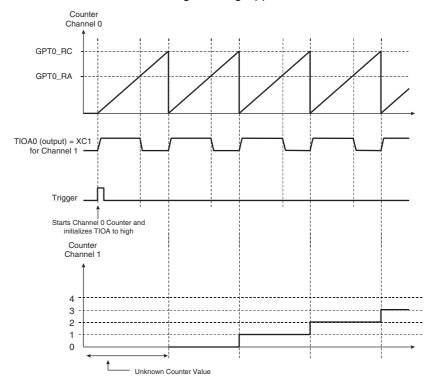

- One 3-channel 16-bit General Purpose Timers (GPT)

- Three Configurable Modes: Counter, PWM, Capture

- Three Multi-purpose I/O Pins Per Channel

- Four 16-bit Simple Timers (ST)

- 4-channel 16-bit Pulse Width Modulation (PWM)

- Two 16-bit Capture Modules (CAPT)

- CAN Controller 2.0A and 2.0B Full CAN (16 Buffers)

- Three USARTs

- Six Peripheral Data Controller (PDC) Channels

- Support for Up to 9-bit Data Lengths

- Support for J1587 Protocol and LIN (Software) Protocols

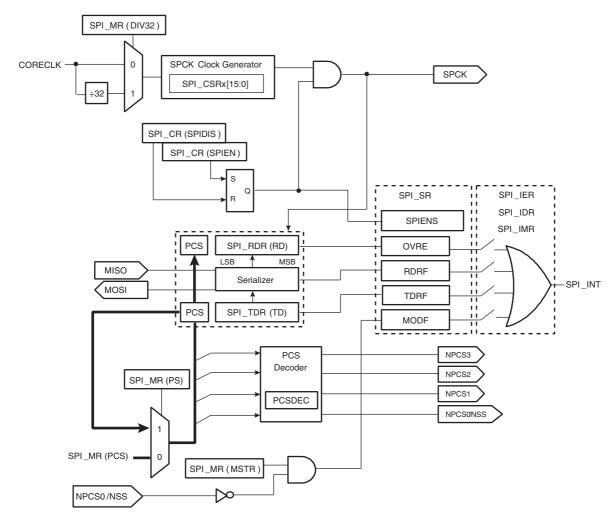

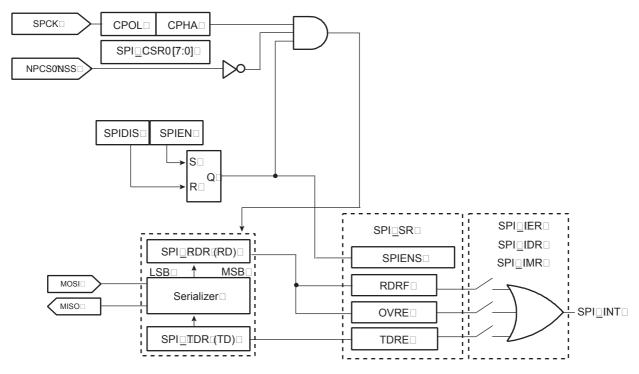

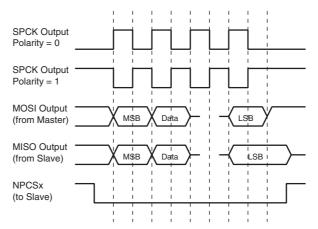

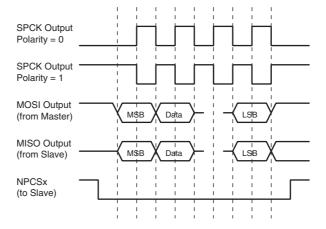

- Master SPI Interface

- Two Peripheral Data Controller (PDC) Channels

- 8- to 16-bit Programmable Data Length

- Four External Chip Select Lines

- One 8-channel 10-bit Analog-to-digital Converter (ADC)

- One Peripheral Data Controller (PDC) Channel

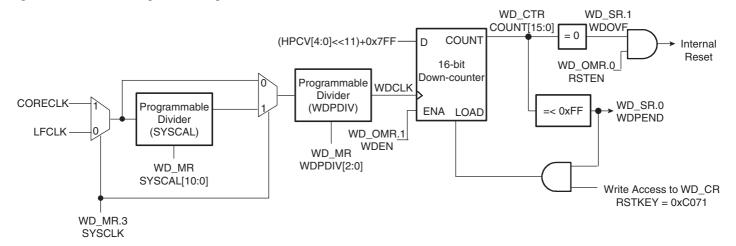

- Programmable Watch Timer (WT)

- Programmable Watchdog (WD)

- Power Management Controller (PMC)

- CPU and Peripherals Can Be Deactivated Individually

- Fully Static Operation Up to 40 MHz

- 3.0V to 3.6V Core, Memory and Analog Voltage Range

- 3.0 V to 5.5V Compliant I/Os

- -40° to +85°C Operating Temperature Range

- Available in a 144-pin LQFP

# AT91 ARM<sup>®</sup> Thumb<sup>®</sup>-based Microcontroller

# AT91SAM7A1

# 1. Description

The AT91SAM7A1 is a member of the Atmel Smart Automotive Microcontrollers product family, based on the ARM7TDMI embedded processor. This processor has a high-performance 32-bit RISC architecture with a high-density 16-bit instruction set and very low power consumption.

In addition, a large number of internally banked registers result in very fast exception handling, making the device ideal for real-time control applications.

The AT91SAM7A1 has a direct connection to off-chip memory, including Flash, through the fully-programmable External Bus Interface.

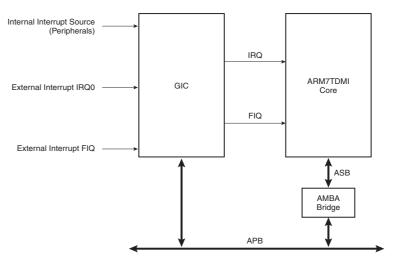

An 8-level priority vectored Interrupt Controller in conjunction with the Peripheral Data Controller significantly improves the real-time performance of the device. The device is manufactured using high-density CMOS technology.

By combining the ARM7TDMI processor with an on-chip RAM and a wide range of peripheral functions on a monolithic chip, the AT91SAM7A1 is a powerful device that provides a flexible, cost-effective solution to many compute-intensive embedded control applications in the automotive and industrial world.

# 2. Pin Configuration

The AT91SAM7A1 is available in a 144-lead LQFP package.

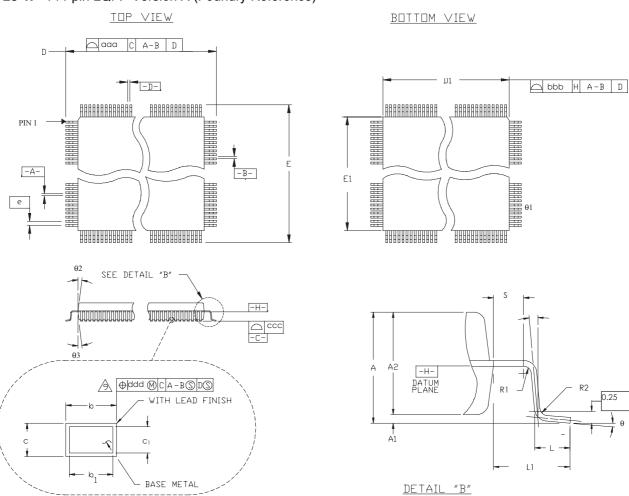

# 2.1 144-lead LQFP Package

Figure 2-1 shows the orientation of the 144-lead LQFP package.

A detailed mechanical description is given in the section Mechanical Characteristics.

Figure 2-1. 144-lead LQFP Package

# 2.2 144-lead LQFP Package Pinout

Table 2-1.

AT91SAM7A1 Pinout for 144-lead LQFP Package

| Pin | Name             | Pin | Name           | Pin | Name        | Pin | Name         |

|-----|------------------|-----|----------------|-----|-------------|-----|--------------|

| 1   | D0               | 37  | ADD11          | 73  | GND5V (I/O) | 109 | ANAOIN1      |

| 2   | D8               | 38  | ADD12          | 74  | PIOA2       | 110 | ANA0IN2      |

| 3   | D1               | 39  | ADD13          | 75  | PIOA3       | 111 | ANA0IN3      |

| 4   | D9               | 40  | ADD14          | 76  | VDD5V (I/O) | 112 | ANAOIN4      |

| 5   | VDD3V (I/O)      | 41  | ADD15          | 77  | PIOA4       | 113 | ANA0IN5      |

| 6   | GND3V (I/O+CORE) | 42  | GND3V (IO)     | 78  | PIOA5       | 114 | ANAOIN6      |

| 7   | VDD3V (I/O+CORE) | 43  | VDD3V (CORE)   | 79  | PIOA6       | 115 | ANA0IN7      |

| 8   | D2               | 44  | VDD5V (IO)     | 80  | PIOA7       | 116 | GND3V (ANA)  |

| 9   | D10              | 45  | IRQ0           | 81  | PIOA8       | 117 | VDD3V (PLL)  |

| 10  | D3               | 46  | FIQ            | 82  | PIOA9       | 118 | MCKI         |

| 11  | D11              | 47  | T0TIOA0/MPIO   | 83  | GND5V (I/O) | 119 | МСКО         |

| 12  | D4               | 48  | T0TIOB0/MPIO   | 84  | PIOA10      | 120 | PLLRC        |

| 13  | D12              | 49  | T0TCLK0/MPIO   | 85  | PIOA11      | 121 | GND3V (PLL)  |

| 14  | D5               | 50  | T0TIOA1/MPIO   | 86  | PIOA12      | 122 | VDD3V (RTCK) |

| 15  | D13              | 51  | T0TIOB1/MPIO   | 87  | PIOA13      | 123 | RTCKI        |

| 16  | D6               | 52  | T0TCLK1/MPIO   | 88  | PIOA14      | 124 | RTCKO        |

| 17  | D14              | 53  | T0TIOA2/MPIO   | 89  | PIOA15      | 125 | GND3V (RTCK) |

| 18  | D7               | 54  | T0TIOB2/MPIO   | 90  | PIOA16      | 126 | VDD3V (I/O)  |

| 19  | D15              | 55  | GND5V (I/O)    | 91  | PIOA17      | 127 | GND3V (CORE) |

| 20  | ADD17            | 56  | T0TCLK2/MPIO   | 92  | PWM0/MPIO   | 128 | GND3V (I/O)  |

| 21  | ADD16            | 57  | TXD0/MPIO      | 93  | VDD5V (I/O) | 129 | SCANEN       |

| 22  | NWR0/NWE         | 58  | RXD0/MPIO      | 94  | PWM1/MPIO   | 130 | TEST         |

| 23  | ADD19            | 59  | SCK0/MPIO      | 95  | PWM2/MPIO   | 131 | TMS          |

| 24  | ADD18            | 60  | TXD1/MPIO      | 96  | PWM3/MPIO   | 132 | TDO          |

| 25  | ADD7             | 61  | RXD1/MPIO      | 97  | CAPT0/MPIO  | 133 | TDI          |

| 26  | ADD6             | 62  | SCK1/MPIO      | 98  | CAPT1/MPIO  | 134 | TCK          |

| 27  | GND3V (I/O+CORE) | 63  | VDD5V (I/O)    | 99  | NRESET      | 135 | NWAIT        |

| 28  | VDD3V (I/O+CORE) | 64  | SPCK/MPIO      | 100 | CANRX0      | 136 | ADD21/CS6    |

| 29  | ADD2             | 65  | MISO/MPIO      | 101 | CANTX0      | 137 | NCS3         |

| 30  | ADD3             | 66  | MOSI/MPIO      | 102 | TXD2/MPIO   | 138 | NCS2         |

| 31  | ADD4             | 67  | NPCS0/NSS/MPIO | 103 | RXD2/MPIO   | 139 | NWR1/NUB     |

| 32  | ADD5             | 68  | NPCS1/MPIO     | 104 | SCK2/MPIO   | 140 | ADD0/NLB     |

| 33  | ADD8             | 69  | NPCS2/MPIO     | 105 | GND5V (I/O) | 141 | NCS1         |

| 34  | ADD20/CS7        | 70  | NPCS3/MPIO     | 106 | VDD3V (ANA) | 142 | NOE/NRD      |

| 35  | ADD9             | 71  | PIOA0          | 107 | VREFP0      | 143 | NCS0         |

| 36  | ADD10            | 72  | PIOA1          | 108 | ANAOINO     | 144 | ADD1         |

# 3. Signal Description

Table 3-1.Pin Description

| Signal Name            | Function                                | Type <sup>(1)</sup> | Level <sup>(1)</sup> | Comments                                                                                                                                       |

|------------------------|-----------------------------------------|---------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                         | EBI <sup>(2)</sup>  |                      |                                                                                                                                                |

| ADD[19:1]              | External address bus                    | 0                   | (Z)                  | The EBI is tri-stated when NRESET is at a logical low level. Internal pull-downs on data bus bits. ADD20 and ADD21 are address lines at reset. |

| ADD0/NLB               | External address line/Lower byte enable | 0                   | L (Z)                |                                                                                                                                                |

| ADD20/CS7              | External address line/Chip select       | 0                   | H (Z)                |                                                                                                                                                |

| ADD21/CS6              | External address line/Chip select       | 0                   | H (Z)                |                                                                                                                                                |

| D[15:0] <sup>(3)</sup> | External data bus                       | I/O                 | (Z)                  |                                                                                                                                                |

| NOE/NRD                | Output enable                           | 0                   | L (Z)                |                                                                                                                                                |

| NWR0/NWE               | Write enable                            | 0                   | L (Z)                |                                                                                                                                                |

| NCS[3:0]               | Chip select lines                       | 0                   | L (Z)                |                                                                                                                                                |

| NWR1/NUB               | Upper byte enable                       | 0                   | L (Z)                |                                                                                                                                                |

| NWAIT                  | Wait input                              | 1                   | L                    | Internal pull-up (must be connected to VCC or leave unconnected for normal operation if functionality not used)                                |

|                        |                                         | GIC                 | 1                    |                                                                                                                                                |

| IRQ0                   | External interrupt line                 | 1                   |                      |                                                                                                                                                |

| FIQ                    | Fast interrupt line                     | 1                   |                      |                                                                                                                                                |

|                        | Po                                      | wer-on Res          | set                  |                                                                                                                                                |

| NRESET                 | Hardware reset input                    | I                   | L                    | Schmitt input with internal filter                                                                                                             |

|                        | N                                       | laster Cloc         | k                    |                                                                                                                                                |

| MCKI                   | Master clock input                      | 1                   |                      | Connected to external crystal (4 to 16 MHz)                                                                                                    |

| МСКО                   | Master clock output                     | 0                   |                      |                                                                                                                                                |

| PLLRC                  | PLL RC network input                    | 1                   |                      |                                                                                                                                                |

|                        | Re                                      | al-time Clo         | ck                   |                                                                                                                                                |

| RTCKI                  | 32.768 kHz clock input                  | 1                   |                      | Connected to external 32.768 kHz crystal                                                                                                       |

| RTCKO                  | 32.768 kHz clock output                 | 0                   |                      |                                                                                                                                                |

|                        | 1                                       | UPIO                | 1                    |                                                                                                                                                |

| UPIO[17:0]             | Unified I/O                             | I/O (I)             | (Z)                  | General purpose I/O                                                                                                                            |

|                        | ,                                       | USART0              | I.                   |                                                                                                                                                |

| SCK0/MPIO              | USART0 clock line                       | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                                                                           |

| RXD0/MPIO              | USART0 receive line                     | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                                                                           |

| TXD0/MPIO              | USART0 transmit line                    | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                                                                           |

|                        |                                         | USART1              | 1                    |                                                                                                                                                |

| SCK1/MPIO              | USART1 clock line                       | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                                                                           |

Table 3-1. Pin Description (Continued)

| Signal Name      | Function                           | Type <sup>(1)</sup> | Level <sup>(1)</sup> | Comments                                                                                |

|------------------|------------------------------------|---------------------|----------------------|-----------------------------------------------------------------------------------------|

| RXD1/MPIO        | USART1 receive line                | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

| TXD1/MPIO        | USART1 transmit line               | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

|                  |                                    | USART2              |                      |                                                                                         |

| SCK2/MPIO        | USART2 clock line                  | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

| RXD2/MPIO        | USART2 receive line                | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

| TXD2/MPIO        | USART2 transmit line               | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

|                  |                                    | Capture             |                      |                                                                                         |

| CAPT[1:0]/MPIO   | Capture input                      | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

|                  |                                    | PWM                 |                      |                                                                                         |

| PWM[3:0]/MPIO    | Pulse Width Modulation output      | I/O (I)             | (Z)                  | Multiplexed with general purpose I/O                                                    |

|                  |                                    | Timer 0             |                      |                                                                                         |

| T0TIOA[2:0]/MPIO | Capture/waveform I/O               | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

| T0TIOB[2:0]/MPIO | Trigger/waveform I/O               | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

| T0TCLK[2:0]/MPIO | External clock/trigger/input       | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

|                  |                                    | ADC                 |                      |                                                                                         |

| ANAIN[7:0]       | Analog input                       | I                   |                      |                                                                                         |

| VREFP            | Positive voltage reference         | 1                   |                      |                                                                                         |

|                  |                                    | SPI                 | •                    |                                                                                         |

| SPCK/MPIO        | SPI clock line                     | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

| MISO/MPIO        | SPI master in slave out            | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

| MOSI/MPIO        | SPI master out slave in            | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

| NPCS[3:1]/MPIO   | SPI chip select                    | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

| NPCS0/NSS/MPIO   | SPI chip select (master and slave) | I/O (I)             | (Z)                  | Multiplexed with a general purpose I/O                                                  |

|                  |                                    | CAN0                |                      |                                                                                         |

| CANRX0           | CAN0 receive line                  | 1                   | L                    |                                                                                         |

| CANTX0           | CAN0 transmit line                 | 0                   | L (H)                |                                                                                         |

|                  |                                    | JTAG                |                      |                                                                                         |

| SCANEN           | Scan enable (Factory test)         | 1                   | н                    | Internal pull-down (must be connected to GND or leave unconnected for normal operation) |

| TDI              | Test Data In                       | 1                   |                      | Schmitt trigger, internal pull-up                                                       |

| TDO              | Test Data Out                      | 0                   |                      |                                                                                         |

| TMS              | Test Mode Select                   | I                   |                      | Schmitt trigger, internal pull-up                                                       |

| TCK              | Test Clock                         | I                   |                      | Schmitt trigger, internal pull-up                                                       |

| TEST             | Factory test                       | 1                   | Н                    | Internal pull-down (must be connected to GND or leave unconnected for normal operation) |

|                  | Power S                            | Supply and          | Ground               |                                                                                         |

| VDD3V (CORE)     | 3.3V for core                      | -                   |                      |                                                                                         |

Table 3-1. Pin Description (Continued)

| Signal Name      | Function                             | Type <sup>(1)</sup> | Level <sup>(1)</sup> | Comments |

|------------------|--------------------------------------|---------------------|----------------------|----------|

| GND3V (CORE)     | Ground for core                      | -                   |                      |          |

| VDD3V (I/O+CORE) | 3.3V for core and 3V I/O             | -                   |                      |          |

| GND3V (I/O+CORE) | Ground for core and 3V I/O           | -                   |                      |          |

| VDD3V (RTCK)     | 3.3V for RTCK oscillator             | -                   |                      |          |

| GND3V (RTCK)     | Ground for RTCK oscillator           | -                   |                      |          |

| VDD3V (PLL)      | 3.3V for PLL and master oscillator   | -                   |                      |          |

| GND3V (PLL)      | Ground for PLL and master oscillator | -                   |                      |          |

| VDD3V (ANA)      | 3.3V for analog cells                | -                   |                      |          |

| GND3V (ANA)      | Analog Ground for analog cells       | -                   |                      |          |

| VDD3V (I/O)      | 3.3V for functional I/O              | -                   |                      |          |

| GND3V (I/O)      | Ground for functional I/O            | -                   |                      |          |

| VDD5V (I/O)      | 3.3V to 5V for functional I/O        | -                   |                      |          |

| GND5V (I/O)      | Ground for functional I/O            | -                   |                      |          |

Notes:

- 1. Values in brackets are values at reset: H (high level), L (low level), Z (tri-state), I (input), O (output).

- 2. The EBI bus (address bus A[21:0], data bus D[15:0] and control lines NOE/NRD, NWR0/NWE, NWR1/NUB and NCS[3:0]) is tri-stated when NRESET is at logical 0. This allows external equipment to access the external memory devices (e.g., for Flash programming). It is up to the application to add an external pull-up on the chip select lines in order to avoid EBI conflicts at reset.

- 3. The EBI data bus D[15:0] has an internal pull-down.

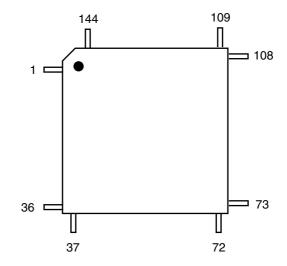

# 4. Block Diagram

Figure 4-1. AT91SAM7A1 Block Diagram

## 5. Product Overview

# 5.1 Register Considerations

## 5.1.1 Enable/Disable/Status Registers

In order to reduce code size and subsequently increase speed when accessing internal peripherals, most of the registers have been split into three address locations:

- The first address location (Enable or Set Register) is used to set a bit to a logical 1.

- The second address location (Disable or Clear Register) is used to set a bit to a logical 0.

- The third address location (Status register or Mask Register) gives the current state of the bit

To set a bit to a logical 1 in the Status or Mask Register, a write command in the Enable or Set Register must be performed with the corresponding bit at a logical 1.

To set a bit to a logical 0 in the Status or Mask Register, a write command in the Disable or Clear Register must be performed with the corresponding bit at a logical 1.

## 5.1.2 Example

Supposing that the US0\_PSR register value is 0x00000000. To enable the RXD and SCK pins as PIOs in the USART0 block, 0x00050000 must be written in the US0\_PER register. The value read in the US0\_PSR register will be 0x00050000.

Now if the software wants to disable the RXD pin as a PIO (i.e. enable it for USART0 use), a write access to the US0\_PDR register with the value 0x00040000 must be performed. The new value read in the US0\_PSR register will be 0x00010000.

## 5.1.3 Key Access to Registers

Some bits in registers can be set to a value (0 or 1) only if the right key is written at the same time.

## 5.1.3.1 Example 1

The TESTEN bit in the SFM\_TM register can be set to a logical 0 or 1 only if the KEY[15:0] bits are equal to 0xD64A.

To enable test mode, 0xD64A0002 must be written in the SFM\_TM register.

To disable test mode, 0xD64A0000 must be written in the SFM\_TM register.

## 5.1.3.2 Example 2

To set the RTCKEN bit in the CM\_CS register to logical 1, a write access to the CM\_CE register must be done with a value of 0x23050080.

To set the RTCKEN bit in the CM\_CS register to logical 0, a write access to the CM\_CD register must be done with a value of 0x18070080.

## 5.2 Power Consumption

## 5.2.1 Working Modes

The AT91SAM7A1 microcontroller provides different working modes.

Table 5-1. Working Modes

| Mode                 | Note                                                                                                                                                                                                                                                                                                                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-power Mode (LPM) | The master clock oscillator, the PLL and the internal divider are switched off. The real time oscillator is enabled. The low frequency clock is selected from the real time oscillator and used as a system clock (i.e., 32.768 kHz used for GIC, WD, WT, ST and any peripheral needed for interrupt generation). CORECLK = RTCK, LFCLK = RTCK |

| Slow Mode (SLM)      | The PLL is switched off. The system clock is the master clock (CORECLK = MCK) or the master clock divided by $\beta$ (CORECLK = MCK/ $\beta$ , $\beta$ in the range [2:256]).                                                                                                                                                                  |

| Operational (OPE)    | Master oscillator and PLL are enabled. The system clock is the clock from the PLL, CORECLK = $\alpha$ x MCK ( $\alpha$ in the range [x2:x20])                                                                                                                                                                                                  |

## 5.2.2 Low-power Mode

Low-power mode is defined as the state in which:

- Master clock oscillator and PLL are stopped

- Low frequency oscillator (32.768 kHz) is used as an internal system clock for core and all peripherals (CORECLK = RTCK, LFCLK = RTCK)

The total power dissipation of the AT91SAM7A1 embedded system, when in low power mode, is estimated to be 170  $\mu$ W maximum, at an operating voltage of 3.3V, over the operating temperature range. Additional conditions are: ARM core stopped, PDC stopped, all modules disabled except ST0, ST1, WT, WD and PMC working at 32.768 kHz.

### 5.2.3 Slow Mode

Slow mode is defined as the state in which:

- Master clock oscillator is enabled, divided by  $\beta$  ( $\beta$  in the range [2:256]) and used as the system clock (CORECLK = MCK or MCK/ $\beta$ )

- The low frequency clock can still be used as low frequency clock for peripherals (LFCLK = RTCK or MCK/β)

The total power dissipation of the AT91SAM7A1 embedded system, when in halt mode, is estimated to be 78 mW with CORECLK = MCK, at an operating voltage of 3.3V, over the operating temperature range and with ARM core and modules working at CORECLK frequency = 4 MHz. With CORECLK = MCK/64, total power dissipation is estimated at 4 mW, at an operating voltage of 3.3V, over the operating temperature range and with ARM core and modules working at CORECLK frequency = 62.5 kHz (i.e., 4 MHz/64).

#### 5.2.4 Operational Mode

Operational mode is defined as the state in which:

- Master clock oscillator and PLL are enabled, system clock is taken from the PLL output (CORECLK =  $\alpha$  x MCK, where  $\alpha$  is in the range [2:20])

- The Low frequency clock can still be used as low frequency clock for peripherals (LFCLK = RTCK or MCK/ $\beta$ ,  $\beta$  in the range [2:256])

The total power dissipation of the AT91SAM7A1 embedded system, when in operational mode, is estimated to be 605 mW maximum, at an operating voltage of 3.3V, over the operat-

ing temperature range and with ARM core and modules working at CORECLK frequency = 32 MHz (i.e., MCK = 4 MHz, PLL multiplier = 8).

## 5.3 Reset

The application must ensure a reset of at least 5 ms to allow time for the system clock to stabilize (CORECLK).

The 32.768 kHz clock (RTCK) will be stabilized 300 ms after the reset is asserted. Software should not use or program the peripherals (WD, WT, ST) which are using this clock until it is stabilized.

## 5.4 Electrical Characteristics

Table 5-2. AT91SAM7A1 Pin Connections for 144-lead LQFP Package

| Pin | Name             | Pad     | Pin | Name           | Pad    | Pin | Name        | Pad    | Pin | Name         | Pad      |

|-----|------------------|---------|-----|----------------|--------|-----|-------------|--------|-----|--------------|----------|

| 1   | D0               | PC3B01D | 37  | ADD11          | PC3T02 | 73  | GND5V (I/O) |        | 109 | ANA0IN1      | AIMUX1   |

| 2   | D8               | PC3B01D | 38  | ADD12          | PC3T02 | 74  | PIOA2       | MC5B04 | 110 | ANA0IN2      | AIMUX1   |

| 3   | D1               | PC3B01D | 39  | ADD13          | PC3T02 | 75  | PIOA3       | MC5B04 | 111 | ANA0IN3      | AIMUX1   |

| 4   | D9               | PC3B01D | 40  | ADD14          | PC3T02 | 76  | VDD5V (I/O) |        | 112 | ANA0IN4      | AIMUX1   |

| 5   | VDD3V (I/O)      |         | 41  | ADD15          | PC3T02 | 77  | PIOA4       | MC5B03 | 113 | ANA0IN5      | AIMUX1   |

| 6   | GND3V (I/O+CORE) |         | 42  | GND3V (IO)     |        | 78  | PIOA5       | MC5B03 | 114 | ANA0IN6      | AIMUX1   |

| 7   | VDD3V (I/O+CORE) |         | 43  | VDD3V (CORE)   |        | 79  | PIOA6       | MC5B03 | 115 | ANA0IN7      | AIMUX1   |

| 8   | D2               | PC3B01D | 44  | VDD5V (IO)     |        | 80  | PIOA7       | MC5B03 | 116 | GND3V (ANA)  |          |

| 9   | D10              | PC3B01D | 45  | IRQ0           | MC5D00 | 81  | PIOA8       | MC5B03 | 117 | VDD3V (PLL)  |          |

| 10  | D3               | PC3B01D | 46  | FIQ            | MC5D00 | 82  | PIOA9       | MC5B03 | 118 | MCKI         | OSC16M   |

| 11  | D11              | PC3B01D | 47  | T0TIOA0/MPIO   | MC5B01 | 83  | GND5V (I/O) |        | 119 | мско         | OSC16M   |

| 12  | D4               | PC3B01D | 48  | T0TIOB0/MPIO   | MC5B01 | 84  | PIOA10      | MC5B02 | 120 | PLLRC        | PLL080M1 |

| 13  | D12              | PC3B01D | 49  | T0TCLK0/MPIO   | MC5B01 | 85  | PIOA11      | MC5B02 | 121 | GND3V (PLL)  |          |

| 14  | D5               | PC3B01D | 50  | T0TIOA1/MPIO   | MC5B01 | 86  | PIOA12      | MC5B01 | 122 | VDD3V (RTCK) |          |

| 15  | D13              | PC3B01D | 51  | T0TIOB1/MPIO   | MC5B01 | 87  | PIOA13      | MC5B01 | 123 | RTCKI        | OSC33K   |

| 16  | D6               | PC3B01D | 52  | T0TCLK1/MPIO   | MC5B01 | 88  | PIOA14      | MC5B01 | 124 | RTCKO        | OSC33K   |

| 17  | D14              | PC3B01D | 53  | T0TIOA2/MPIO   | MC5B01 | 89  | PIOA15      | MC5B01 | 125 | GND3V (RTCK) |          |

| 18  | D7               | PC3B01D | 54  | T0TIOB2/MPIO   | MC5B01 | 90  | PIOA16      | MC5B01 | 126 | VDD3V (I/O)  |          |

| 19  | D15              | PC3B01D | 55  | GND5V (I/O)    |        | 91  | PIOA17      | MC5B01 | 127 | GND3V (CORE) |          |

| 20  | ADD17            | PC3T02  | 56  | T0TCLK2/MPIO   | MC5B01 | 92  | PWM0/MPIO   | MC5B01 | 128 | GND3V (I/O)  |          |

| 21  | ADD16            | PC3T02  | 57  | TXD0/MPIO      | MC5B01 | 93  | VDD5V (I/O) |        | 129 | SCANEN       | PC3D01D  |

| 22  | NWR0/NWE         | PC3B02  | 58  | RXD0/MPIO      | MC5B01 | 94  | PWM1/MPIO   | MC5B01 | 130 | TEST         | PC3D01D  |

| 23  | ADD19            | PC3T02  | 59  | SCK0/MPIO      | MC5B01 | 95  | PWM2/MPIO   | MC5B01 | 131 | TMS          | PC3D21U  |

| 24  | ADD18            | PC3T02  | 60  | TXD1/MPIO      | MC5B01 | 96  | PWM3/MPIO   | MC5B01 | 132 | TDO          | PC3T03   |

| 25  | ADD7             | PC3T02  | 61  | RXD1/MPIO      | MC5B01 | 97  | CAPT0/MPIO  | MC5B01 | 133 | TDI          | PC3D21U  |

| 26  | ADD6             | PC3T02  | 62  | SCK1/MPIO      | MC5B01 | 98  | CAPT1/MPIO  | MC5B01 | 134 | TCK          | PC3D21U  |

| 27  | GND3V (I/O+CORE) |         | 63  | VDD5V (I/O)    |        | 99  | NRESET      | MC5D20 | 135 | NWAIT        | PC3D01U  |

| 28  | VDD3V (I/O+CORE) |         | 64  | SPCK/MPIO      | MC5B01 | 100 | CANRX0      | MC5D00 | 136 | ADD21/CS6    | PC3T02   |

| 29  | ADD2             | PC3T02  | 65  | MISO/MPIO      | MC5B01 | 101 | CANTX0      | MC5O01 | 137 | NCS3         | PC3T02   |

| 30  | ADD3             | PC3T02  | 66  | MOSI/MPIO      | MC5B01 | 102 | TXD2/MPIO   | MC5B01 | 138 | NCS2         | PC3T02   |

| 31  | ADD4             | PC3T02  | 67  | NPCS0/NSS/MPIO | MC5B01 | 103 | RXD2/MPIO   | MC5B01 | 139 | NWR1/NUB     | PC3B02   |

| 32  | ADD5             | PC3T02  | 68  | NPCS1/MPIO     | MC5B01 | 104 | SCK2/MPIO   | MC5B01 | 140 | ADD0/NLB     | PC3T02   |

| 33  | ADD8             | PC3T02  | 69  | NPCS2/MPIO     | MC5B01 | 105 | GND5V (I/O) |        | 141 | NCS1         | PC3T02   |

| 34  | ADD20/CS7        | PC3T02  | 70  | NPCS3/MPIO     | MC5B01 | 106 | VDD3V (ANA) |        | 142 | NOE/NRD      | PC3B02   |

| 35  | ADD9             | PC3T02  | 71  | PIOA0          | MC5B04 | 107 | VREFP0      | ANAIN  | 143 | NCS0         | PC3T02   |

| 36  | ADD10            | PC3T02  | 72  | PIOA1          | MC5B04 | 108 | ANA0IN0     | AIMUX1 | 144 | ADD1         | PC3T02   |

Note: Pins 7, 28 and 43, i.e. VDD3V (CORE) and VDD3V (I/O + CORE), are internally connected together.

Note: Pins 6, 27 and 127, i.e. GND3V (CORE) and GND3V (I/O + CORE), are internally connected together.

Note: Pins K6, K4 and H4, i.e. VDD3V (CORE) and VDD3V (I/O + CORE), are internally connected together.

Note: Pins G4, J4 and D6, i.e. GND3V (CORE) and GND3V (I/O + CORE), are internally connected together.

Pad types are given in Table 5-3 below.

**Table 5-3.** Pad Types

| Pad          | Туре                                                          | DTPDHL <sup>(1)</sup> | DTPDLH <sup>(2)</sup> | TPDHL <sup>(3)</sup> | TPDLH <sup>(4)</sup> | Output<br>Current    |

|--------------|---------------------------------------------------------------|-----------------------|-----------------------|----------------------|----------------------|----------------------|

| MC5B01       | 5 V CMOS bidirectional pad                                    | 0.144 ns/pF           | 0.131 ns/pF           | 2.327 ns             | 2.192 ns             | 2 mA AC<br>2 mA DC   |

| MC5B02       | 5 V CMOS bidirectional pad                                    | 0.072 ns/pF           | 0.066 ns/pF           | 2.298 ns             | 2.179 ns             | 4 mA AC<br>4 mA DC   |

| MC5B03       | 5 V CMOS bidirectional pad                                    | 0.036 ns/pF           | 0.033 ns/pF           | 2.727 ns             | 2.034 ns             | 8 mA AC<br>8 mA DC   |

| MC5B04       | 5 V CMOS bidirectional pad                                    | 0.018 ns/pF           | 0.017 ns/pF           | 3.265 ns             | 2.449 ns             | 16 mA AC<br>16 mA DC |

| MC5O01       | 5 V CMOS output pad                                           | 0.144 ns/pF           | 0.131 ns/pF           | 2.310 ns             | 2.174 ns             | 2 mA AC<br>2 mA DC   |

| MC5D00       | 5 V CMOS non-inverting input pad                              |                       |                       |                      |                      |                      |

| MC5D20       | 5 V CMOS schmitt non-inverting input pad                      |                       |                       |                      |                      |                      |

| PC3D01D      | 3 V CMOS non-inverting input pad with pull-<br>down resistor  |                       |                       |                      |                      |                      |

| PC3D01U      | 3 V CMOS non-inverting input pad with pull-<br>up resistor    |                       |                       |                      |                      |                      |

| PC3D21       | 3 V CMOS schmitt non-inverting input pad                      |                       |                       |                      |                      |                      |

| PC3D21U      | 3V CMOS schmitt non-inverting input pad with pull-up resistor |                       |                       |                      |                      |                      |

| PC3T01       | 3 V CMOS three state output pad                               | 0.120 ns/pF           | 0.116 ns/pF           | 1.357 ns             | 1.011 ns             | 2 mA AC<br>0.3 mA DC |

| PC3T02       | 3 V CMOS three state output pad                               | 0.060 ns/pF           | 0.058 ns/pF           | 1.002 ns             | 0.781 ns             | 4 mA AC<br>0.3 mA DC |

| PC3T03       | 3 V CMOS three state output pad                               | 0.040 ns/pF           | 0.039 ns/pF           | 0.943 ns             | 0.800 ns             | 6 mA AC<br>0.3 mA DC |

| PC3B01D      | 3 V CMOS bidirectional pad with pull-down resistor            | 0.118 ns/pF           | 0.116 ns/pF           | 1.357 ns             | 1.040 ns             | 2 mA AC<br>0.3 mA DC |

| PC3B01       | 3 V CMOS non-inverting bidirectional pad                      | 0.120 ns/pF           | 0.116 ns/pF           | 1.372 ns             | 1.033 ns             | 2 mA AC<br>0.3 mA DC |

| PC3B02       | 3 V CMOS non-inverting bidirectional pad                      | 0.060 ns/pF           | 0.058 ns/pF           | 1.010 ns             | 0.789 ns             | 6 mA AC<br>0.3 mA DC |

| PC3B03       | 3 V CMOS non-inverting bidirectional pad                      | 0.040 ns/pF           | 0.039 ns/pF           | 0.948 ns             | 0.808 ns             | 6 mA AC<br>0.3 mA DC |

| OSCK33       | 32.768 kHz crystal oscillator pad                             |                       |                       |                      |                      |                      |

| OSC16M       | 2-6 MHz crystal oscillator pad                                |                       |                       |                      |                      |                      |

| PLL080M<br>1 | 20 MHz to 80 MHz single pad Phase-<br>Locked Loop             |                       |                       |                      |                      |                      |

| AIMUX1       | Analog input pad                                              |                       |                       |                      |                      |                      |

- Notes: 1. Differential (load-dependent) propagation delay, high-to-low or high impedance-to-low ( $V_{DD} = 3.3 \text{ V}$ , Temp. = 25°C, Input Slope = 1 ns)

- 2. Differential (load-dependent) propagation delay, low-to-high or high impedance-to-high ( $V_{DD} = 3.3 \text{ V}$ , Temp. = 25°C, Input

- 3. Propagation delay, high-to-low ( $V_{DD}=3.3~V$ , Temp. = 25°C, Input Slope = 1 ns) 4. Propagation delay, low-to-high ( $V_{DD}=3.3~V$ , Temp. = 25°C, Input Slope = 1 ns)

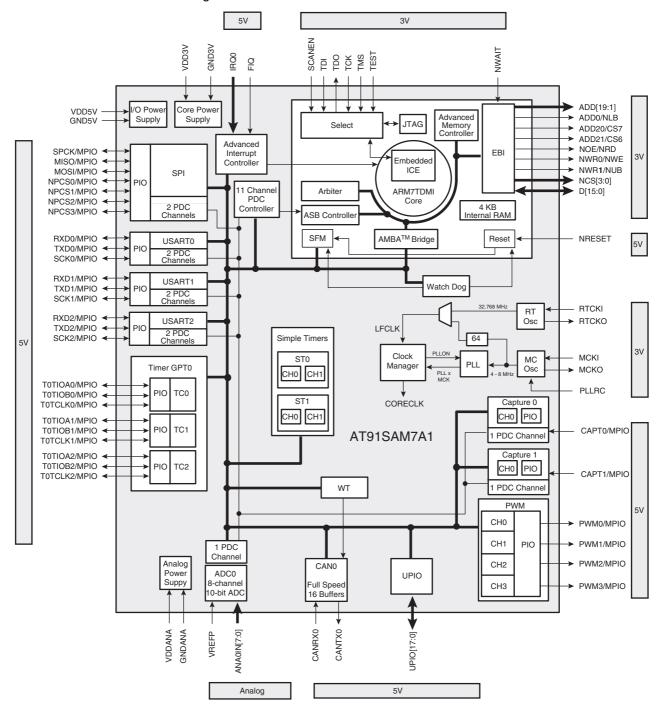

## 5.4.1 Propagation Delay

The propagation delay time shown in Table 5-3, "Pad Types," on page 12, is the time in nanoseconds from the 50% point of the input to the 50% point of the output.

Figure 5-1. Propagation Delay

# 6. Clocks

## 6.1 Crystals

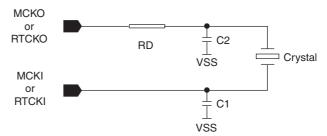

Crystals with 10 pF load capacitance can be directly connected to the oscillator pads. Nevertheless, it is recommended to implement the circuitry as described hereafter and in Figure 6-1 below.

Figure 6-1. Circuitry for 10 pF Load Capacitance

If the crystal recommended capacitor Cx is greater than 10 pF, then C1 and C2 must be added. Cx can be approximated to:  $Cx = (C1 \times C2)/(C1 + C2)$ .

Value of resistor RD depends on crystal frequency and manufacturer. Typical values of RD are given in Table 6-1 (values should be adjusted in the application environment).

**Table 6-1.** Typical Crystal Series Resistor

| Signal | RD    | Conditions                              |

|--------|-------|-----------------------------------------|

| мско   | 0 Ω   | Crystal: CP12A-4MHz-S1-4085-1050 (NDK®) |

| RTCKO  | 10 kΩ | Crystal: MC-306 32.768K-A (EPSON®)      |

## 6.2 Phase Locked Loop

The AT91SAM7A1 microcontroller integrates a programmable PLL. The PLL requires an external RC network as described hereafter and in Figure 6-2 below.

Figure 6-2. External RC Network

The optimum response with a simple RC filter is obtained when:

Equation1:

$$0.4 < \sqrt{\left(\frac{K_0 \times I_P}{n \times (C_3 + C_4)}\right)} \times \frac{R \times C_4}{2} < 1 \text{ with an optimum value of } 0.707$$

14

## Where:

- $\bullet$  K<sub>0</sub> is the PLL V<sub>CO</sub> gain (typ 105.10<sup>6</sup> Hz/V, min 65.10<sup>6</sup> Hz/V, max 172.10<sup>6</sup> Hz/V)

- $I_P$  is the peak current delivered by the charge pump into the filter (typ. 350  $\mu A$ , min. 50  $\mu A$ , max. 800  $\mu A$ )

- n is the division ratio of the divider (i.e., PLL multiplication factor)

Stability can be improved with an additional capacitor  $C_3$ . The value of  $C_3$  must be chosen so that:

Equation 2:

$$4 < \frac{C_4}{C_3} < 15$$

Equation 3:

$$\sqrt{\left(\frac{K_0 \times I_p}{n \times (C_3 + C_4)}\right)} \leq \frac{\Pi \times f_{CKR}}{5}$$

## Where:

• f<sub>CKR</sub> is the PLL input frequency (i.e., MCK).

Phase jitter for the PLL is 200 ps typical.

## 6.2.1 PLL Characteristics

Table 6-2. PLL Characteristics

| Code             | Parameter            | Conditions     | Min  | Тур | Max    | Unit  |

|------------------|----------------------|----------------|------|-----|--------|-------|

| f <sub>CKR</sub> | Input frequency      |                | 0.02 |     | 30     | MHz   |

| f <sub>CK</sub>  | Output frequency     |                | 20   |     | 30     | MHz   |

| Wlow             | Duty cycle           |                |      | 50  |        | %     |

| J <sub>CK</sub>  | Jitter               | With ratio 1:1 |      | 200 |        | ps    |

| n                | Division ratio       |                | 1:1  |     | 1:1024 |       |

| K <sub>0</sub>   | V <sub>CO</sub> gain |                | 65   | 105 | 172    | MHz/V |

| I <sub>P</sub>   | CHP current          |                | 50   | 350 | 800    | mA    |

# 6.3 Clock Timings

## 6.3.1 Master Clock

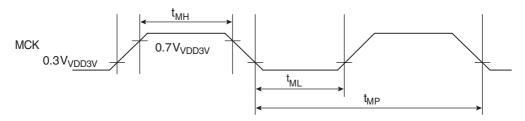

The master clock is the clock generated by the master clock oscillator. The master clock (MCK) characteristics are given in Table 6-3.

Table 6-3. Master Clock Timings

| Symbol            | Parameter                   | Minimum                | Typical                | Maximum                | Unit |

|-------------------|-----------------------------|------------------------|------------------------|------------------------|------|

| 1/t <sub>MP</sub> | Master oscillator frequency | 4000                   |                        | 16000                  | kHz  |

| t <sub>MP</sub>   | Master clock period         | 62.5                   |                        | 250                    | ns   |

| t <sub>MH</sub>   | Master clock high time      | 0.40 x t <sub>MP</sub> | 0.50 x t <sub>MP</sub> | 0.60 x t <sub>MP</sub> | ns   |

| t <sub>ML</sub>   | Master clock low time       | 0.40 x t <sub>MP</sub> | 0.50 x t <sub>MP</sub> | 0.60 x t <sub>MP</sub> | ns   |

Figure 6-3. Master Clock Waveform

## 6.3.2 32.768 kHz Frequency Clock

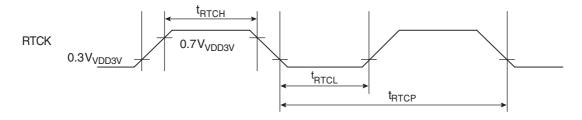

The 32.768 kHz clock is the clock generated by the real time clock oscillator. The real time clock (RTCK) characteristics are given below in Table 6-4.

Table 6-4. Low Frequency Clock Timings

| Symbol              | Parameter                                          | Minimum                  | Typical                  | Maximum                  | Unit |

|---------------------|----------------------------------------------------|--------------------------|--------------------------|--------------------------|------|

| 1/t <sub>RTCP</sub> | 32.768kHz oscillator frequency                     |                          | 32.768                   |                          | kHz  |

| t <sub>RTCP</sub>   | 32.768kHz clock period                             |                          | 30517.58                 |                          | ns   |

| t <sub>RTCH</sub>   | 32.768kHz clock high time                          | 0.40 x t <sub>RTCP</sub> | 0.50 x t <sub>RTCP</sub> | 0.60 x t <sub>RTCP</sub> | ns   |

| t <sub>RTCL</sub>   | 32.768kHz clock low time                           | 0.40 x t <sub>RTCP</sub> | 0.50 x t <sub>RTCP</sub> | 0.60 x t <sub>RTCP</sub> | ns   |

| Dt <sub>RTCP</sub>  | Duty cycle (t <sub>RTCH</sub> /t <sub>RTCP</sub> ) | 40                       | 50                       | 60                       | %    |

Figure 6-4. 32.768 kHz Clock Waveform

## 6.3.3 Core Clock

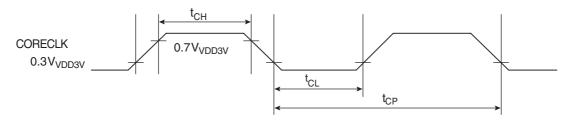

The core clock is the clock used in the system for the core and peripheral. The core clock (CORECLK) characteristics are given in Table 6-5.

Table 6-5.Core Clock Timings

| Symbol            | Parameter                                      | Minimum                |                        | Maximum                | Unit |

|-------------------|------------------------------------------------|------------------------|------------------------|------------------------|------|

| 1/t <sub>CP</sub> | Core clock frequency                           | 32.768                 |                        | 40000                  | kHz  |

| t <sub>CP</sub>   | Core clock period                              | 25                     |                        | 30517.58               | ns   |

| t <sub>CH</sub>   | Core clock high time                           | 0.40 x t <sub>CP</sub> | 0.50 x t <sub>CP</sub> | 0.60 x t <sub>CP</sub> | ns   |

| t <sub>CL</sub>   | Core clock low time                            | 0.40 x t <sub>CP</sub> | 0.50 x t <sub>CP</sub> | 0.60 x t <sub>CP</sub> | ns   |

| Dt <sub>CP</sub>  | Duty cycle (t <sub>CH</sub> /t <sub>CP</sub> ) | 40                     | 50                     | 60                     | %    |

Figure 6-5. Core Clock Waveform

## 6.4 Internal Oscillator Characteristics

## 6.4.1 Core Clock Oscillator

Table 6-6. Core Clock Oscillator

| Code            | Parameter                               | Conditions          | Min | Тур               | Max                | Unit |

|-----------------|-----------------------------------------|---------------------|-----|-------------------|--------------------|------|

| Du              | Duty cycle                              | Crystal @ 4 MHz     | 40  | 50                | 60                 | %    |

| Opf             | Operating frequency                     |                     | 4   |                   | 16                 | MHz  |

| t <sub>SU</sub> | Startup time                            | Crystal @ 4 MHz     |     |                   | 10                 | ms   |

| t <sub>SU</sub> | Startup time                            | Crystal @ 8 MHz     |     |                   | 5 <sup>(1)</sup>   | ms   |

| C1              | Internal capacitance (MCKI/GND)         |                     |     | 10                |                    | pF   |

| C2              | Internal capacitance (MCKO/GND)         |                     |     | 10                |                    | pF   |

| CL              | Equivalent load capacitance (MCKI/MCKO) |                     |     | 5                 |                    | pF   |

| DL              | Drive level                             |                     |     |                   | 50 <sup>(1)</sup>  | W    |

| Rs              | Equivalent Series Resistance            | Fundamental @ 8 Mhz |     |                   | 100 <sup>(1)</sup> |      |

| Rs              | Equivalent Series Resistance            | Fundamental @ 4 Mhz |     |                   | 50 <sup>(1)</sup>  |      |

| Cs              | Shunt capacitance                       | Crystal             |     |                   | 6                  | pF   |

| CL              | Load capacitance                        | Crystal @ 4 MHz     |     | 10 <sup>(1)</sup> |                    | pF   |

| Cm              | Motional capacitance                    | Crystal @ 4 MHz     |     |                   | 3 <sup>(1)</sup>   | fF   |

Note: 1. These values are not characterized.

## 6.4.2 Real Time Clock Oscillator

Table 6-7. Real Time Clock Oscillator

| Code | Parameter                                 | Conditions           | Min | Тур | Max | Unit |

|------|-------------------------------------------|----------------------|-----|-----|-----|------|

| Du   | Duty cycle                                | @ 32.768 kHz         | 40  | 50  | 60  | %    |

| tsu  | Startup time                              |                      |     |     | 1.5 | s    |

| C1   | Internal capacitance (RTCKI/GND)          |                      |     | 20  |     | pF   |

| C2   | Internal capacitance (RTCKO/GND)          |                      |     | 20  |     | pF   |

| CL   | Equivalent load capacitance (RTCKI/RTCKO) |                      |     | 10  |     | pF   |

| DL   | Drive level                               |                      |     |     | 1   | μW   |

| Rs   | Series resistance                         | Crystal              |     |     | 60  | kOhm |

| Cs   | Shunt capacitance                         | Crystal              | 0.8 |     | 1.7 | pF   |

|      | Load capacitance                          | Crystal @ 32.768 kHz |     | 10  |     | pF   |

| Cm   | Motional capacitance                      | Crystal @ 32.768 kHz | 1   |     | 4   | fF   |

# 7. Memory Map

The AT91SAM7A1 microcontroller memory space is 4 Gbytes.

When the AT91SAM7A1D microcontroller is reset, the ARM core is in reboot mode to access the external memory (usually a ROM) on NCS0 at address 0x00000000. The internal RAM is located at address 0x00300000.

When the software execute the remap command (write 1 in RCB bit in AMC\_RCR register), the internal RAM is automatically located at address 0x00000000 and the external memory accessed on the NCS0 is located in the memory space from 0x40000000 to 0x7FFFFFF depending on the AMC\_CSR0 register in the Advanced Memory Controller, then the chip is in remap mode.

## 7.1 Reboot Mode

**Table 7-1.** Internal Memory (Reboot Mode)

| Memory Space | Size               | Application             | Abort Generation |

|--------------|--------------------|-------------------------|------------------|

| 0xFFFFFFF    |                    |                         |                  |

|              | 2 Mbytes           | Peripheral devices      | No               |

| 0xFFE00000   |                    |                         |                  |

| 0xFFDFFFFF   |                    |                         |                  |

|              | 4090 Mbytes        | Reserved                | Yes              |

| 0x00400000   |                    |                         |                  |

| 0x003FFFFF   | 1 Mbytes           |                         |                  |

|              | (4 Kbytes repeated | 4 Kbytes internal RAM   | No               |

| 0x00300000   | 256 times)         |                         |                  |

| 0x002FFFFF   |                    |                         |                  |

|              | 1 Mbytes           | Reserved                | No               |

| 0x00200000   |                    |                         |                  |

| 0x001FFFFF   |                    |                         |                  |

|              | 1 Mbytes           | Reserved                | Yes              |

| 0x00100000   |                    |                         |                  |

| 0x000FFFFF   |                    | External mamori: 5:5    |                  |

|              | 1 Mbytes           | External memory on NCS0 | No               |

| 0x00000000   |                    |                         |                  |

# 7.2 Remap Mode

Table 7-2.

Internal Memory (Remap Mode)

| Memory Space | Size               | Application                            | Abort Generation                         |

|--------------|--------------------|----------------------------------------|------------------------------------------|

| 0xFFFFFFF    |                    |                                        |                                          |

|              | 2 Mbytes           | Peripheral devices                     | No                                       |

| 0xFFE00000   |                    |                                        |                                          |

| 0xFFDFFFFF   |                    |                                        |                                          |

|              | 2046 Mbytes        | Reserved                               | Yes                                      |

| 0x80000000   |                    |                                        |                                          |

| 0x7FFFFFF    |                    | Up to 6 external                       |                                          |

|              | 1024 Mbytes        | memories repeated within the page size | Yes, outside of defined page size in the |

|              | 1024 Mbytes        | programmed in the                      | AMC_CSRx                                 |

| 0x40000000   |                    | AMC_CSRx register                      |                                          |

| 0x3FFFFFF    |                    |                                        |                                          |

|              | 1021 Mbytes        | Reserved                               | Yes                                      |

| 0x00300000   |                    |                                        |                                          |

| 0x002FFFFF   |                    |                                        |                                          |

|              | 2 Mbytes           | Reserved                               | No                                       |

| 0x00100000   |                    |                                        |                                          |

| 0x000FFFFF   | 1 Mbytes           |                                        |                                          |

|              | (4 Kbytes repeated | 4 Kbytes internal RAM                  | No                                       |

| 0x00000000   | 256 times)         |                                        |                                          |

## 7.3 External Memories

The AT91SAM7A1 external memories can be relocated in the address space from 0x40000000 to 0x7FFFFFF. The configuration of the base address and the page size of each EBI chip select line (NCS[3:0], CS[7:6]) is done through the Advanced Memory Controller (AMC) registers.

It is to be noted that the two most significant bits of the base address are fixed to 01b allocating these memories in the second of the four Gbytes memory spaces.

The maximum external memory space is 16 Mbytes (i.e. CS[7:6] used as address lines).

Table 7-3. External Memory

| Memory Space                  | Size           | Application             |

|-------------------------------|----------------|-------------------------|

| 0x(01XX <sub>b</sub> )XXFFFFF |                |                         |

| 0 (04)/// )///00000           | Up to 1 Mbytes | External memory on CS7  |

| 0x(01XX <sub>b</sub> )XX00000 |                |                         |

| 0x(01XX <sub>b</sub> )X1FFFFF |                |                         |

| 0x(01XX <sub>b</sub> )XX00000 | Up to 2 Mbytes | External memory on CS6  |

| 0x(01XX <sub>b</sub> )X3FFFFF |                |                         |

|                               | Up to 4 Mbytes | External memory on NCS3 |

| 0x(01XX <sub>b</sub> )XX00000 |                |                         |

| 0x(01XX <sub>b</sub> )X3FFFFF |                |                         |

|                               | Up to 4 Mbytes | External memory on NCS2 |

| 0x(01XX <sub>b</sub> )XX00000 |                |                         |

| 0x(01XX <sub>b</sub> )X3FFFFF |                |                         |

|                               | Up to 4 Mbytes | External memory on NCS1 |

| 0x(01XX <sub>b</sub> )XX00000 |                |                         |

| 0x(01XX <sub>b</sub> )X3FFFFF |                |                         |

|                               | Up to 4 Mbytes | External memory on NCS0 |

| 0x(01XX <sub>b</sub> )XX00000 |                |                         |

# 7.4 Peripheral Resources

The peripheral modules of the AT91SAM7A1 embedded system are listed in Table 7-4.

Table 7-4.Peripheral Resources

| Peripheral              | Address      | IRQ source | PDC Channel | PIO |  |

|-------------------------|--------------|------------|-------------|-----|--|

| AMC                     | 0xFFE00000   | -          | -           |     |  |

| SFM                     | 0xFFF00000   | -          | -           |     |  |

| Watchdog                | 0xFFFA0000   | 2          | -           |     |  |

| Watch Timer             | 0xFFFA4000   | 3          | -           |     |  |

| LICARTO                 | 0 55540000   | _          | RX: Ch0     |     |  |

| USART0                  | 0xFFFA8000   | 4          | TX: Ch1     | 3   |  |

| LICARTA                 | 0. 5554.0000 | _          | RX: Ch2     |     |  |

| USART1                  | 0xFFFAC000   | 5          | TX: Ch3     | 3   |  |

|                         |              | _          | RX: Ch4     | 3   |  |

| USART2                  | 0xFFFB0000   | 6          | TX: Ch5     |     |  |

|                         |              | _          | RX: Ch6     | 7   |  |

| SPI                     | 0xFFFB4000   | 7          | TX: Ch7     |     |  |

| ADC0 (8-channel 10-bit) | 0xFFFC0000   | 10         | Ch10        |     |  |

|                         |              | 12         | -           |     |  |

| GPT0 (3 Channels)       | 0xFFFC8000   | 13         | -           | 9   |  |

|                         |              | 14         | -           | 7   |  |

| PWM (4 Channels)        | 0xFFFD0000   | 16         | -           | 4   |  |

| CAN (16 Channels)       | 0xFFFD4000   | 20         | -           |     |  |

| UPIO                    | 0xFFFD8000   | 21         | -           | 19  |  |

| Capture CAPT0           | 0xFFFDC000   | 22         | Ch8         | 1   |  |

| Capture CAPT1           | 0xFFFE0000   | 23         | Ch9         | 1   |  |

| Simple Timer ST0        | 0xFFFE4000   | 24         | -           |     |  |

| Simple Timer ST1        | 0xFFFE8000   | 25         | -           |     |  |

| CM                      | 0xFFFEC000   | -          | -           |     |  |

| PMC                     | 0xFFFF4000   | -          | -           |     |  |

| PDC                     | 0xFFFF8000   | -          | -           |     |  |

| GIC                     | 0xFFFFF000   | -          | -           |     |  |

# 8. Power Management Block

In order to reduce power consumption, the AT91SAM7A1 microcontroller provides a power management block in some peripherals used to switch on/off the peripheral clocks (peripheral and PIO block).

This function is independent of the Power Management Controller (peripheral) used to switch on/off the ARM7TDMI core and the PDC clocks.

Three registers are provided:

- PERIPHERAL ECR (at peripheral offset 0x0050) enables the clock

- PERIPHERAL\_DCR (at peripheral offset 0x0054) disables the clock

- PERIPHERAL\_PMSR (at peripheral offset 0x0058) gives the status of the clock

Two bits are provided in these registers:

- Bit 0 controls the PIO block of the peripheral

- Bit 1 controls the peripheral function

When the peripheral clock (and/or the PIO clock) is disabled, the clock is immediately stopped. When the clock is re-enabled, the peripheral controller (and/or the PIO controller) resumes action where it left off.

The interrupt registers are common to the peripheral controller and its PIO controller. The clock on the interrupt registers and its associated logic are stopped only if both the peripheral controller clock and the PIO controller clock are stopped.

Table 8-1 lists the different power management blocks.

Table 8-1. AT91SAM7A1 Power Managment Blocks

| Module      | Power Management Block Present Module |                  | Power Management<br>Block Present |  |  |

|-------------|---------------------------------------|------------------|-----------------------------------|--|--|

| AMC         | No                                    | PWM              | Yes                               |  |  |

| SFM         | No                                    | CAN              | Yes                               |  |  |

| Watchdog    | No                                    | UPIO             | Yes                               |  |  |

| Watch Timer | No                                    | CAPT0            | Yes                               |  |  |

| USART0      | Yes                                   | CAPT1            | Yes                               |  |  |

| USART1      | Yes                                   | Simple Timer ST0 | Yes                               |  |  |

| USART2      | Yes                                   | Simple Timer ST1 | Yes                               |  |  |

| SPI         | Yes                                   | СМ               | No                                |  |  |

| ADC0        | Yes                                   | PMC              | Yes                               |  |  |

| GPT0 TC0    | Yes                                   | PDC              | No                                |  |  |

| GPT0 TC1    | Yes                                   | GIC              | No                                |  |  |

| GPT0 TC2    | Yes                                   |                  |                                   |  |  |

# 9. PIO Controller Block

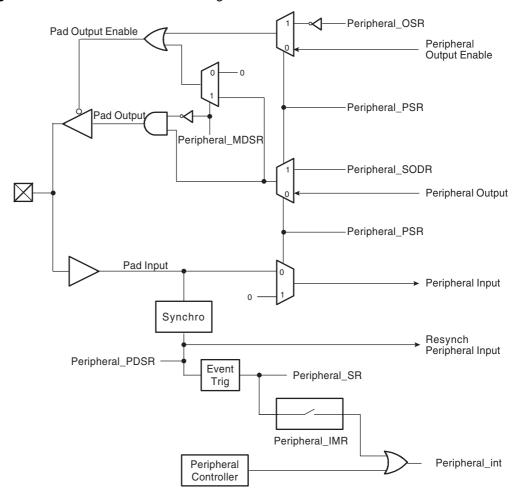

Figure 9-1. PIO Controller Block Diagram

To match different applications, the AT91SAM7A1 peripherals have their dedicated pins multiplexed with general-purpose I/O pins (MPIO).

Table 9-1 lists the modules sharing the dedicated pins with MPIOs.

Table 9-1. PIO Block Multiplexing

| Module      | PIO Block<br>Present | Number of MPIO | Name of PIO Lines |

|-------------|----------------------|----------------|-------------------|

| AMC         | No                   | -              | -                 |

| SFM         | No                   | -              | -                 |

| Watchdog    | No                   | -              | -                 |

| Watch Timer | No                   | -              | -                 |

| USART0      | Yes                  | 3              | TXD0, RXD0, SCK0  |

| USART1      | Yes                  | 3              | TXD1, RXD1, SCK1  |

| USART2      | Yes                  | 3              | TXD2, RXD2, SCK2  |

Table 9-1. PIO Block Multiplexing (Continued)

| Module           | PIO Block<br>Present | Number of MPIO | Name of PIO Lines           |

|------------------|----------------------|----------------|-----------------------------|

| SPI              | Yes                  | 7              | MISO, MOSI, SPCK, NPCS[3:0] |

| ADC0             | No                   | -              | -                           |

| GPT0 TC0         | Yes                  | 3              | TIOA0, TIOB0, TCLK0         |

| GPT0 TC1         | Yes                  | 3              | TIOA1, TIOB1, TCLK1         |

| GPT0 TC2         | Yes                  | 3              | TIOA2, TIOB2, TCLK2         |

| PWM              | Yes                  | 4              | PWM[3:0]                    |

| CAN              | No                   | -              | -                           |

| UPIO             | Yes                  | 18             | UPIO[17:0]                  |

| CAPT0            | Yes                  | 1              | CAPT0                       |

| CAPT1            | Yes                  | 1              | CAPT1                       |

| Simple Timer ST0 | No                   | -              | -                           |

| Simple Timer ST1 | No                   | -              | -                           |

| СМ               | No                   | -              | -                           |

| PMC              | No                   | -              | -                           |

| PDC              | No                   | -              | -                           |

| GIC              | No                   | -              | -                           |

Each PIO block in the peripheral is controlled through the peripheral interface. The PIO block clock is enabled/disabled by the peripheral Power Management Controller (see Table 7-4 on page 22).

## 9.1 Multiplexed I/O Lines

All I/O lines are multiplexed with an I/O signal of the peripheral. After reset, the pin is controlled by the peripheral PIO controller. When a peripheral signal is not used in an application, the corresponding pin can be used as a parallel I/O.

Each parallel I/O line is bi-directional, whether the peripheral defines the signal as input or output.

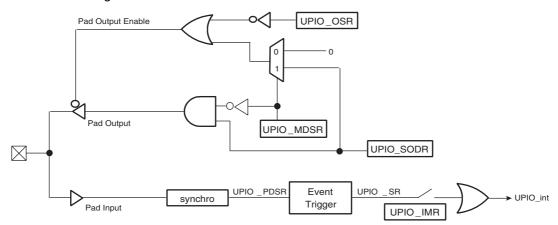

Figure 9-1 on page 24 shows the multiplexing of the peripheral signals with the PIO controller signal.

Each pin of the peripheral can be independently controlled using the Peripheral\_PER (PIO Enable) and Peripheral\_PDR (PIO Disable) registers.

The Peripheral\_PSR (PIO Status) indicates whether the pin is controlled by the peripheral or by the PIO controller block.

## 9.1.1 Output Selection

The user can select the direction of each individual I/O signal (input or output) using the Peripheral\_OER (Output Enable) and Peripheral\_ODR (Output Disable) registers. The output status of the I/O signal can be read in the Peripheral\_OSR (Output Status) register. The direction defined has effect only if the pin is configured to be controlled by the PIO controller block.

#### 9.1.2 I/O Levels

Each pin can be configured to be independently driven high or low. The level is defined in different ways, according to the following conditions.

If a pin is controlled by the PIO controller block and is defined as an output (see Output Selection above), the level is programmed using the Peripheral\_SODR (Set Output Data) and Peripheral\_CODR (Clear Output Data) registers. In this case, the programmed value can be read in the Peripheral\_ODSR (Output Data Status) register.

If a pin is controlled by the PIO controller block and is not defined as an output, the level is determined by the external circuit. If a pin is not controlled by the PIO controller block, the state of the pin is defined by the Peripheral controller. In all cases, the level on the pin can be read in the Peripheral\_PDSR (Pin Data Status) register.

## 9.1.3 Interrupts

Each PIO controller block also provides an internal interrupt signal shared with the peripheral interrupt.

Each PIO can be programmed to generate an interrupt when a level change occurs. This is controlled by the Peripheral\_IER (Interrupt Enable) and Peripheral\_IDR (Interrupt Disable) registers which enable/disable the I/O interrupt (and the peripheral interrupts) by setting/clearing the corresponding bit in the Peripheral\_IMR.

When a change in level occurs, the corresponding bit in the Peripheral\_SR (Interrupt Status) register is set whether the pin is used as a PIO or a peripheral signal and whether it is defined as input or output.

If the corresponding interrupt in Peripheral\_IMR (Interrupt Mask) register is enabled, the PIO interrupt is asserted.

The PIO interrupt is cleared when:

- a write access is performed on the Peripheral\_CISR register (with the corresponding bit set at a logical 1) or

- a read access is performed in the Peripheral\_SR register (if no Peripheral\_CISR register is present in the peripheral)

## 9.1.4 User Interface

Each individual MPIO is associated with a bit position in the PIO controller user interface registers. Each of these registers is 32 bits wide. If a parallel I/O line is not defined, writing to the corresponding bits has no effect. Undefined bits read zero.

#### 9.1.5 Open Drain/Push-pull Output

The PIO can either be configured as an open drain output (only drives a low level) or as a push pull output (drives high and low levels).

When the PIO is configured as open drain (multidriver), an external pull-up is necessary to guarantee a logic level (logical one) when the pin is not being driven.

The PERIPHERAL\_MDER (Multidriver Enable) and PERIPHERAL\_MDDR (Multidriver Disable) registers control this option and respectively configure the I/O as open drain or push pull. The multidriver option can be selected whether the I/O pin is controlled by the PIO controller or the peripheral controller. Bits at logical one in the PERIPHERAL\_MDSR (Multidriver Status) indicate pins configured as open drain.

# 10. Advanced Memory Controller (AMC)

The AT91SAM7A1 microcontroller is provided with an Advanced Memory Controller allowing the software to configure external and internal memory mapping (at boot level).

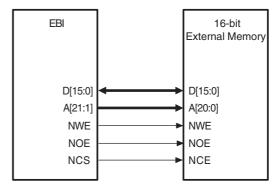

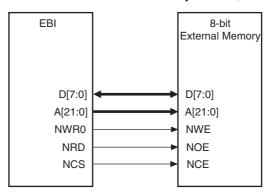

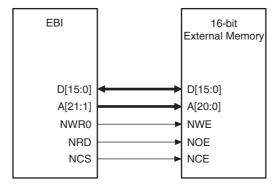

The external 16-bit data bus interface is called the External Bus Interface (EBI) and is the physical layer used to connect external devices to the AT91SAM7A1 microcontroller. Subsequently, the EBI generates the signals which control the access to the external memory or peripheral devices.

The EBI is fully programmable through the Advanced Memory Controller (AMC) and can address up to 16 Mbytes. It has up to six chip selects and a 22-bit address bus.

The AT91SAM7A1 can only boot on a 16-bit external memory device connected to the NCS0 signal. All the other chip select lines (NCS[3:1] and CS[7:6]) can be configured to access 8- or 16-bit memory devices.

## 10.1 Boot on NCS0

By default, the AT91SAM7A1 boots on a 16-bit external memory device connected on NCS0.

At reset, access through NCS0 is configured as follows (in the AMC CSR0 register):

- 8 wait states (WSE = 1, NWS = 7 in AMC\_CSR0)

- 16-bit data bus width (DBW[1:0] = 01<sub>b</sub>)

- Base address is at 0x00000000

- Byte access type is configured as Byte Write Access, BAT = 0

- The number of data float time is 0 (TDF[2:0] = 000<sub>b</sub>)

- The EBI is configured in normal read protocol (DRP = 0 in AMC MCR register)

The user can modify the chip select 0 configuration, programming the AMC\_CSR0 with exact boot memory characteristics. The base address becomes effective after the remap command (set to a logical 1 the RCB in AMC\_RCR), but the other parameters are changed immediately after the write access in the AMC\_CSR0 register.

# 10.2 External Memory Mapping

The memory map associates the internal 32-bit address space with the external 22-bit address bus.

The memory map is defined by programming the base address and page size of the external memories.

If the physical memory device is smaller than the programmed page size, it wraps around and appears to be repeated within the page. The AMC correctly handles any valid access to the memory device within the page.

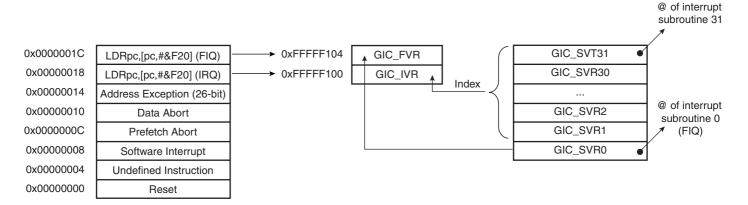

In the event of an access request to an address outside any programmed page, an abort signal is generated. Two types of abort are possible: instruction prefetch abort and data abort. The corresponding exception vector addresses are respectively 0x0000000C and 0x00000010. It is up to the system programmer to program the error handling routine to use in case of an abort (see the ARM7TDMI datasheet for further information).

The AT91SAM7A1 microcontroller must be wired so the NCS0 accesses a non volatile 16-bit memory as shown in Figure 10-6 on page 32 or Figure 10-7 on page 32.

# 10.3 External Memory Device Connection

#### 10.3.1 Data Bus Width

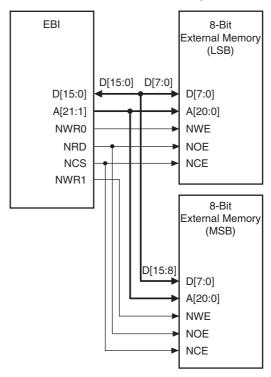

Each chip select can access 8- or 16-bit data bus devices. This option is selected by the DBW[1:0] bits in the corresponding AMC\_CSRx register.

NCS0 is used at reset to access a 16-bit memory device (DBW[1:0] = 01<sub>b</sub>).

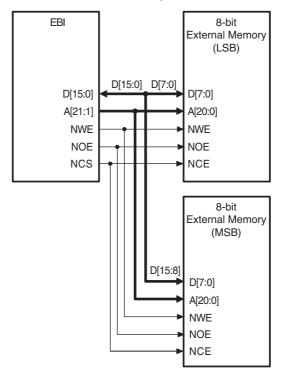

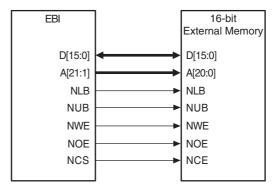

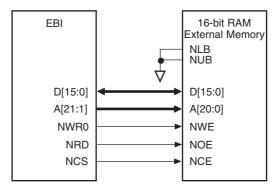

## 10.3.2 Byte Select or Byte Write Access

Each chip select can operate with one of two different types of write access by setting the Byte Access Type (BAT) bit in the corresponding AMC CSRx register.

- Byte select access (BAT = 1): Uses one write signal, one read signal, and two signals to select upper and/or lower memory bank in a 16-bit memory.

- Typically used with 16-bit memories, except when the user wants to connect 2 x 8-bit memories in parallel. In this case, this is considered a 16-bit memory by the AMC.

- Byte write access (BAT = 0): Uses two byte write signals to select two different 8-bit devices and a single read signal. This mode is used at reset to boot on the memory connected on NCS0 (Chip Select 0).

Typically used with 2 x 8-bit memories.

## 10.3.3 Byte Select Access (BAT = 1)

This mode is selected by setting the bit BAT to 1 in AMC\_CSRx registers and is typically used to connect 16-bit devices in a memory page, except when user wants to connect 2 x 8-bit devices in parallel, in that case seen by the AMC this is a 16-bit memory page.

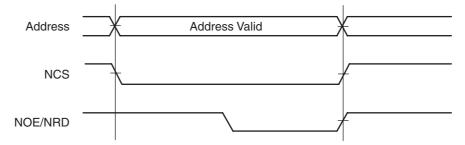

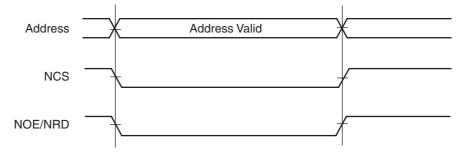

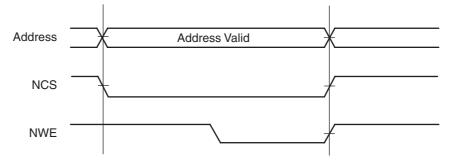

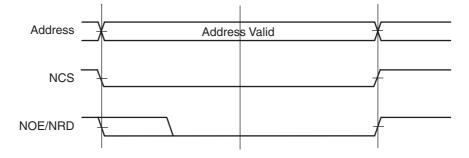

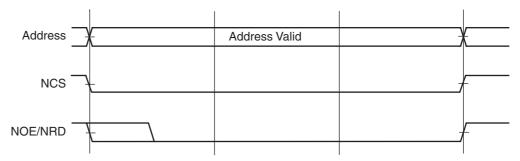

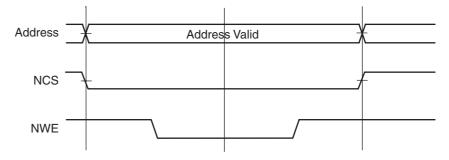

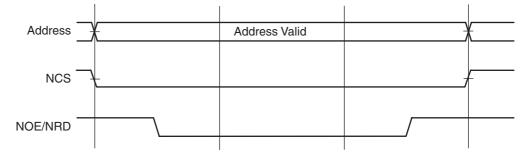

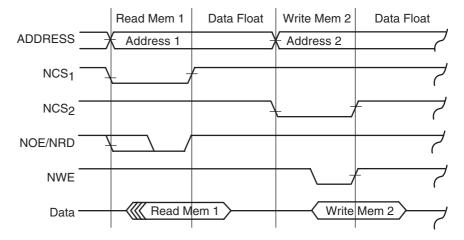

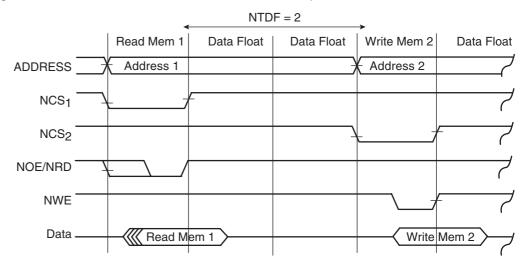

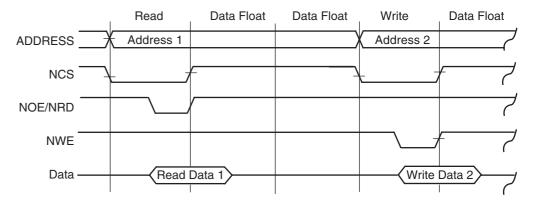

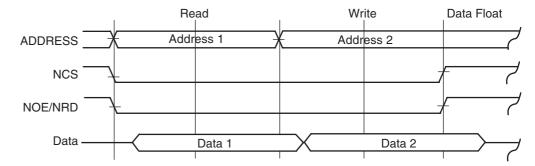

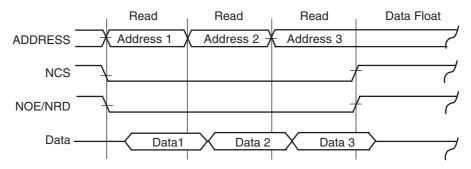

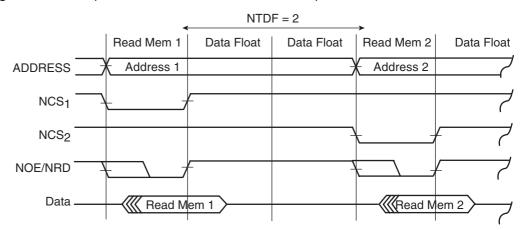

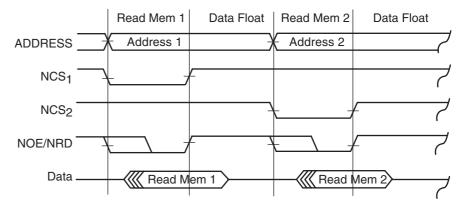

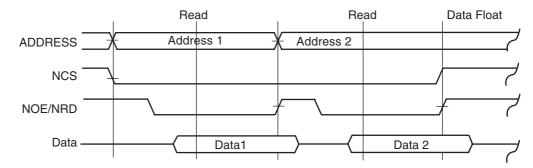

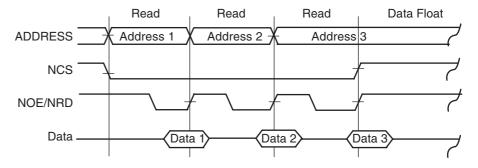

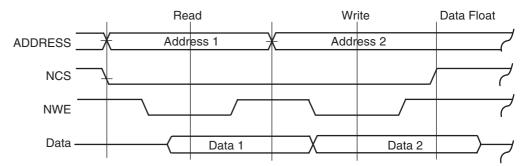

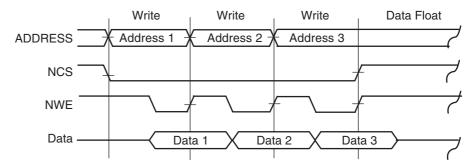

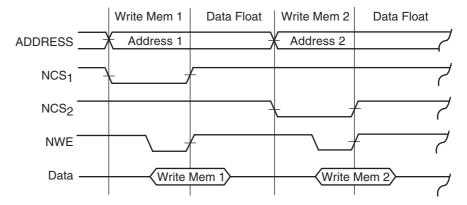

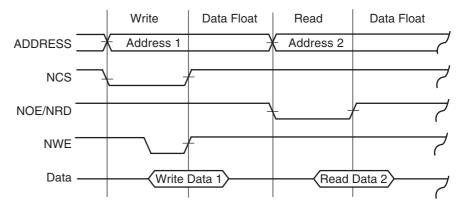

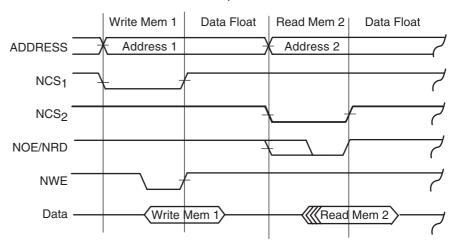

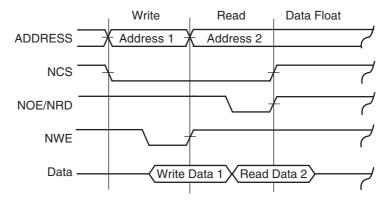

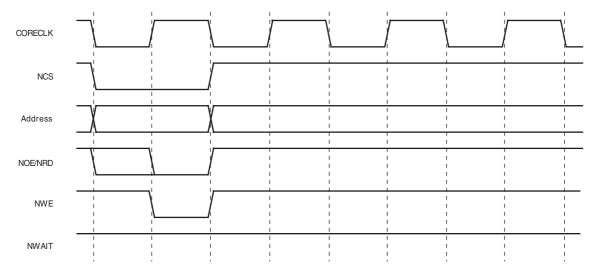

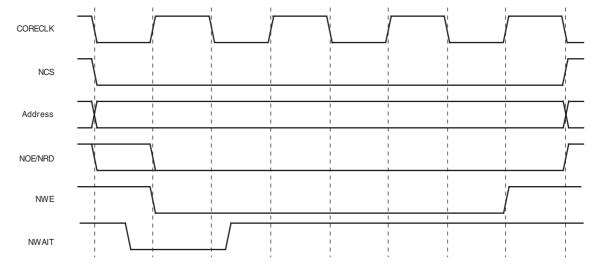

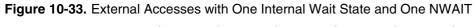

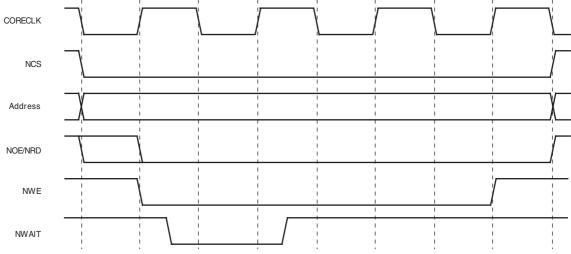

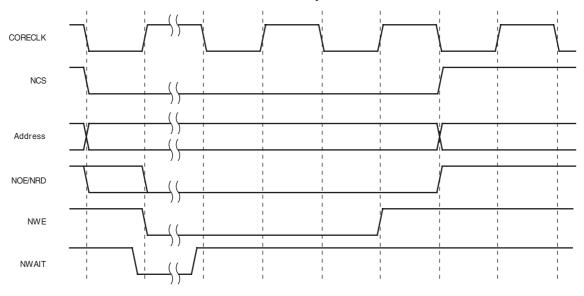

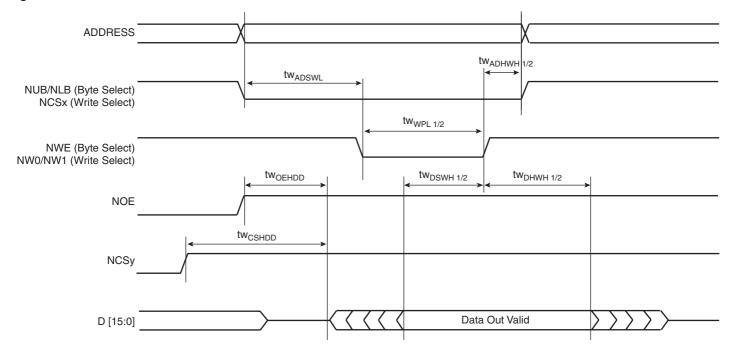

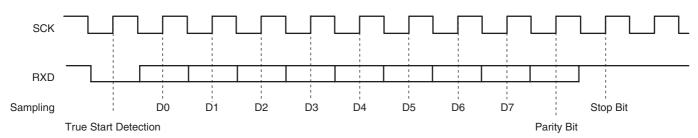

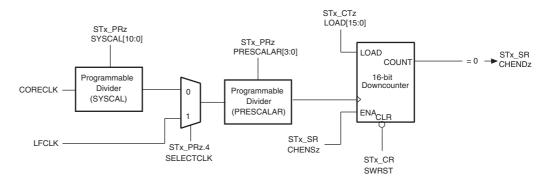

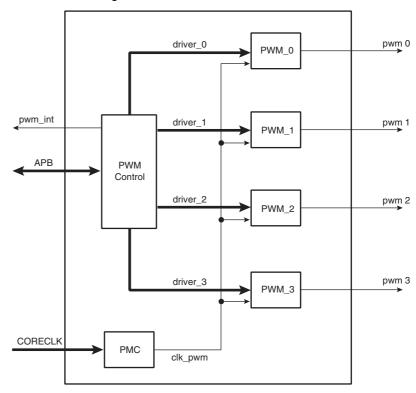

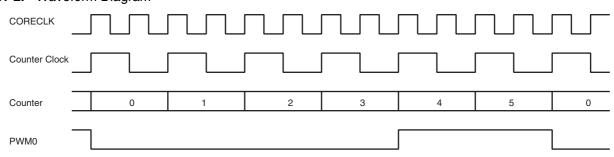

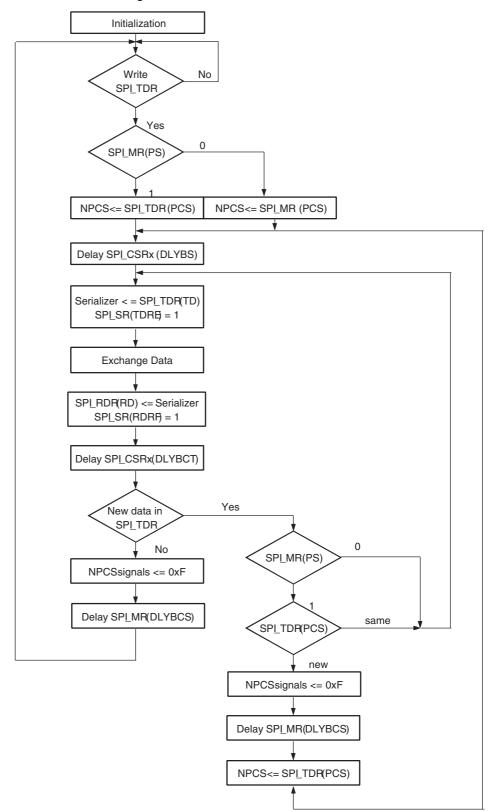

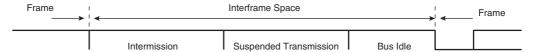

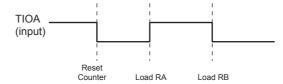

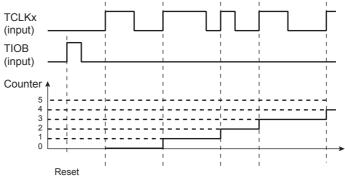

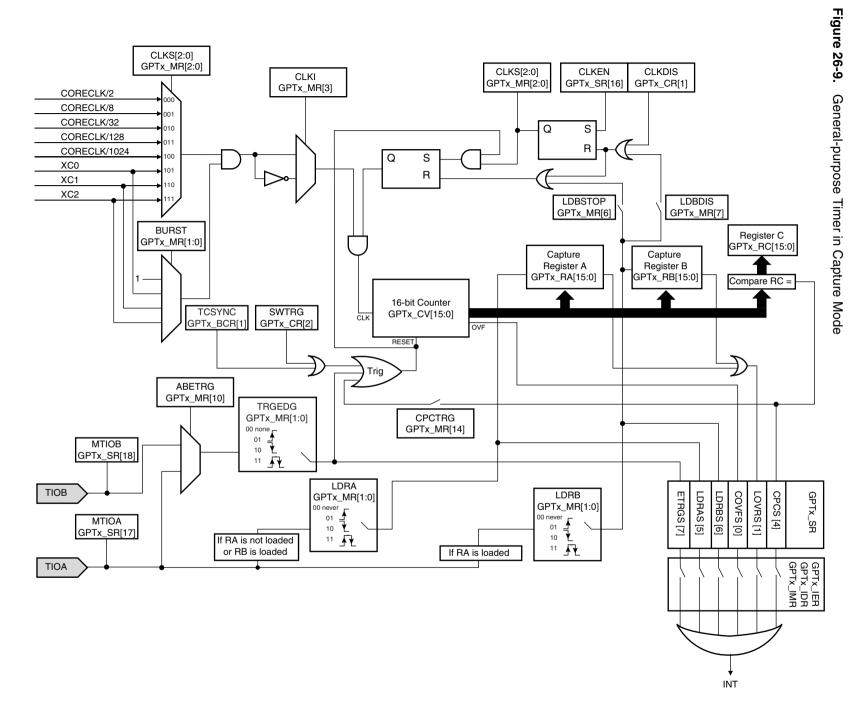

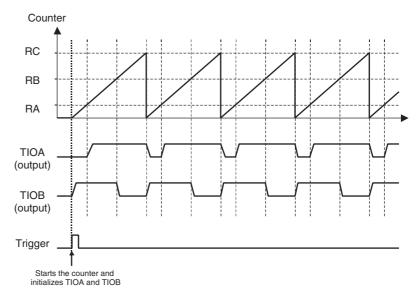

Users can use the upper/lower bank selection signals NUB and NLB to have either an 8-bit or a 16-bit access.