# **IR-enhanced CCD image sensors**

S11510 series

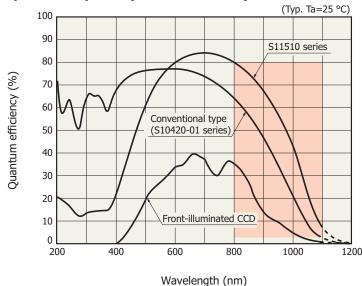

## Enhanced near infrared sensitivity: QE=40% ( $\lambda$ =1000 nm)

The S11510 series is a family of FFT-CCD image sensors for photometric applications that offer improved sensitivity in the near infrared region at wavelengths longer than 800 nm. Our unique technology in laser processing was used to form a MEMS structure on the back side of the CCD. This allows the S11510 series to have much higher sensitivity than our previous products (S10420-01 series).

In addition to having high infrared sensitivity, the S11510 series can be used as an image sensor with a long active area in the direction of the sensor height by binning operation, making it suitable for detectors in Raman spectroscopy. Binning operation also ensures even higher S/N and signal processing speed compared to methods that use an external circuit to add signals digitally.

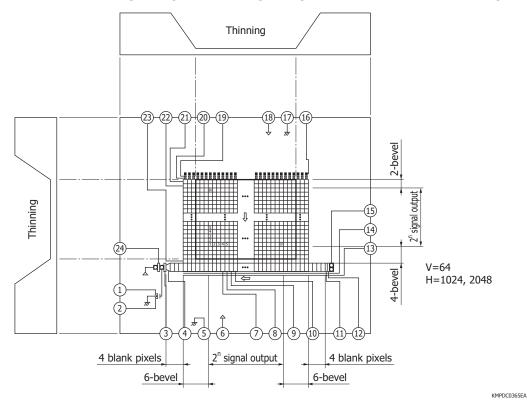

The S11510 series has a pixel size of  $14 \times 14 \, \mu m$  and is available in two image areas of  $14.336 \, (H) \times 0.896 \, (V) \, mm \, (1024) \, M_{\odot}$  $\times$  64 pixels) and 28.672 (H)  $\times$  0.896 (V) mm (2048  $\times$  64 pixels). The S11510 series is pin compatible with the S10420-01 series, and so operates under the same drive conditions.

#### Features

- Applications

- **Enhanced near infrared sensitivity: QE=40% (\lambda=1000 nm)**

- High CCD node sensitivity: 6.5 μV/e<sup>-</sup>

- → High full well capacity and wide dynamic range (with anti-blooming function)

- Pixel size: 14 × 14 μm

- MPP operation

- Raman spectrometers, etc.

#### Spectral response (without window)\*1

KMPDB0324FC

\*1: Spectral response with quartz glass is decreased according to the spectral transmittance characteristic of window material.

### **Selection guide**

| Type no.    | Number of total pixels | Number of active pixels | Active area<br>[mm (H) × mm (V)] | Readout speed<br>max.<br>(MHz) | Applicable<br>driver circuit |

|-------------|------------------------|-------------------------|----------------------------------|--------------------------------|------------------------------|

| S11510-1006 | 1044 × 70              | 1024 × 64               | 14.336 × 0.896                   | 0.5                            | C11287                       |

| S11510-1106 | 2068 × 70              | 2048 × 64               | 28.672 × 0.896                   | 0.5                            | C11287                       |

### **General ratings**

| Parameter              | Specification                                     |

|------------------------|---------------------------------------------------|

| Pixel size             | 14 (H) × 14 (V) μm                                |

| Vertical clock phase   | 2-phase                                           |

| Horizontal clock phase | 4-phase                                           |

| Output circuit         | One-stage MOSFET source follower                  |

| Package                | 24-pin ceramic DIP (refer to dimensional outline) |

| Window                 | Quartz glass                                      |

### **→** Absolute maximum ratings (Ta=25 °C)

| Parameter                               | Symbol                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------------------------|------|------|------|------|

| Operating temperature*2                 | Topr                     | -50  | -    | +50  | °C   |

| Storage temperature                     | Tstg                     | -50  | -    | +70  | °C   |

| Output transistor drain voltage         | Vod                      | -0.5 | -    | +30  | V    |

| Reset drain voltage                     | VRD                      | -0.5 | -    | +18  | V    |

| Over flow drain voltage                 | VOFD                     | -0.5 | -    | +18  | V    |

| Vertical input source voltage           | Visv                     | -0.5 | -    | +18  | V    |

| Horizontal input source voltage         | VISH                     | -0.5 | -    | +18  | V    |

| Over flow gate voltage                  | Vofg                     | -10  | -    | +15  | V    |

| Vertical input gate voltage             | VIG1V, VIG2V             | -10  | -    | +15  | V    |

| Horizontal input gate voltage           | VIG1H, VIG2H             | -10  | -    | +15  | V    |

| Summing gate voltage                    | Vsg                      | -10  | -    | +15  | V    |

| Output gate voltage                     | Vog                      | -10  | -    | +15  | V    |

| Reset gate voltage                      | VRG                      | -10  | -    | +15  | V    |

| Transfer gate voltage                   | VTG                      | -10  | -    | +15  | V    |

| Vertical shift register clock voltage   | VP1V, VP2V               | -10  | -    | +15  | V    |

| Horizontal shift register clock voltage | VP1H, VP2H<br>VP3H, VP4H | -10  | -    | +15  | V    |

<sup>\*2:</sup> Package temperature

### **S11510** series

### **□** Operating conditions (MPP mode, Ta=25 °C)

| Р                               | arameter                                |      | Symbol                       | Min. | Тур. | Max. | Unit     |

|---------------------------------|-----------------------------------------|------|------------------------------|------|------|------|----------|

| Output transistor drain voltage |                                         | Vod  | 23                           | 24   | 25   | V    |          |

| Reset drain voltage             |                                         |      | VRD                          | 11   | 12   | 13   | V        |

| Over flow drain voltage         | ge                                      |      | Vofd                         | 11   | 12   | 13   | V        |

| Over flow gate voltag           | e                                       |      | Vorg                         | 0    | 12   | 13   | V        |

| Output gate voltage             |                                         |      | Vog                          | 4    | 5    | 6    | V        |

| Substrate voltage               |                                         |      | Vss                          | -    | 0    | -    | V        |

|                                 | Input source                            |      | VISV, VISH                   | -    | Vrd  | -    | V        |

| Test point                      | Vertical input gate                     |      | VIG1V, VIG2V                 | -9   | -8   | -    | V        |

| Ī                               | Horizontal input gat                    |      |                              | -9   | -8   | -    | V        |

| Voution shift wasistay          | ala als valta a a                       | High | VP1VH, VP2VH                 | 4    | 6    | 8    | V        |

| Vertical shift register         | clock voltage                           | Low  | VP1VL, VP2VL                 | -9   | -8   | -7   | V        |

| 9                               |                                         | High | VР1НН, VР2НН<br>VР3НН, VР4НН | 4    | 6    | 8    | V        |

| Horizontal Shift regist         | Horizontal shift register clock voltage |      | VP1HL, VP2HL<br>VP3HL, VP4HL | -6   | -5   | -4   | V        |

| Cumanain a gata valta a         |                                         | High | Vsgh                         | 4    | 6    | 8    | V        |

| Summing gate voltage            |                                         | Low  | Vsgl                         | -6   | -5   | -4   | V        |

| Reset gate voltage High Low     |                                         | High | VRGH                         | 4    | 6    | 8    | V        |

|                                 |                                         | Low  | VRGL                         | -6   | -5   | -4   | <b>V</b> |

| Transfer gate voltage           |                                         | High | VTGH                         | 4    | 6    | 8    | V        |

| mansier gate voltage            | Transfer gate voltage Low               |      | VTGL                         | -9   | -8   | -7   | <b>V</b> |

| External load resistan          | ice                                     |      | RL                           | 90   | 100  | 110  | kΩ       |

### **➡** Electrical characteristics (Ta=25 °C)

| Parameter                    |                        | Symbol     | Min.    | Тур.    | Max. | Unit |

|------------------------------|------------------------|------------|---------|---------|------|------|

| Signal output frequency      |                        | fc         | -       | 0.25    | 0.5  | MHz  |

| Vertical shift register      | -1006                  | CP1V, CP2V | -       | 600     | -    | nE   |

| capacitance                  | -1106                  | CPIV, CP2V | -       | 1200    | -    | pF   |

| Horizontal shift register    | -1006                  | Ср1н, Ср2н | -       | 80      | -    | nE   |

| capacitance                  | -1106                  | Срзн, Ср4н | -       | 160     | -    | pF   |

| Summing gate capacitance     |                        | Csg        | -       | 10      | -    | pF   |

| Reset gate capacitance       | Reset gate capacitance |            | -       | 10      | -    | pF   |

| Transfer gate capacitance    | -1006                  | Стс        | -       | 30      | -    | pF   |

| Transfer gate capacitance    | -1106                  |            | -       | 60      | -    | Pi   |

| Charge transfer efficiency*3 |                        | CTE        | 0.99995 | 0.99999 | -    | -    |

| DC output level              |                        | Vout       | 17      | 18      | 19   | V    |

| Output impedance             |                        | Zo         | -       | 10      | -    | kΩ   |

| Power consumption*4          |                        | Р          | -       | 4       | -    | mW   |

<sup>\*3:</sup> Charge transfer efficiency per pixel, measured at half of the full well capacity \*4: Power consumption of the on-chip amplifier plus load resistance

3

#### **Electrical and optical characteristics (Ta=25 °C, unless otherwise noted)**

| Param                      | neter        | Symbol | Min.  | Тур.        | Max. | Unit                    |

|----------------------------|--------------|--------|-------|-------------|------|-------------------------|

| Saturation output voltage  |              | Vsat   | -     | Fw × Sv     | -    | V                       |

| Full well capacity         | Vertical     | Fw     | 50    | 60          | -    | ke-                     |

| Full well capacity         | Horizontal   |        | 250   | 300         | -    |                         |

| CCD node sensitivity       |              | Sv     | 5.5   | 6.5         | 7.5  | μV/e⁻                   |

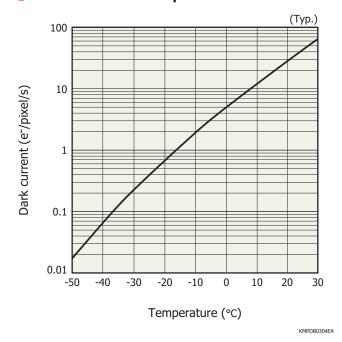

| Dark current*5             |              | DS     | -     | 50          | 200  | e <sup>-</sup> /pixel/s |

| Readout noise*6            |              | Nr     | -     | 6           | 15   | e⁻ rms                  |

| Dynamic range*7            | Line binning | DR     | 41700 | 50000       | -    | -                       |

| Spectral response range    |              | λ      | -     | 200 to 1100 | -    | nm                      |

| Photo response non-uniform | mity*8       | PRNU   | -     | ±3          | ±10  | %                       |

<sup>\*5:</sup> Dark current nearly doubles for every 5 to 7 °C increase in temperature.

Photo response non-uniformity =  $\frac{\text{Fixed pattern noise (peak to peak)}}{\text{Signal}} \times 100 \text{ [%]}$

#### Dark current vs. temperature

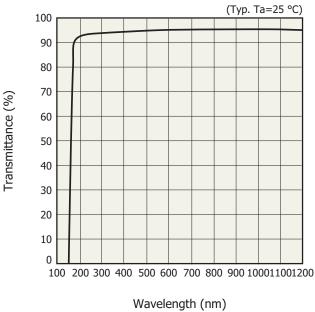

#### Spectral transmittance characteristic of window material

KMPDB030

#### Window material

| Type no.      | Window material |

|---------------|-----------------|

| S11510 series | Quartz glass*9  |

\*9: Resin sealing

<sup>\*6:</sup> Temperature: -40 °C, readout frequency: 20 kHz

<sup>\*7:</sup> Dynamic range (DR) = Full well capacity / Readout noise

<sup>\*8:</sup> Measured at one-half of the saturation output (full well capacity) using LED light (peak emission wavelength: 660 nm)

### **▶** Device structure (conceptual drawing of top view in dimensional outline)

### **S11510** series

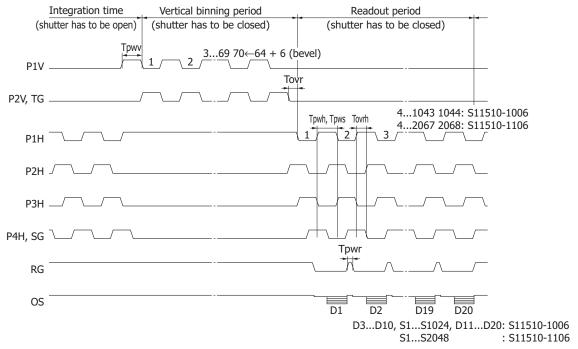

### Timing chart (line binning)

KMPDC0355EA

| Paran              | neter                 | Symbol     | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------|------------|------|------|------|------|

| D1V D2V TC         | Pulse width*10        | Tpwv       | 6    | 8    | -    | μs   |

| P1V, P2V, TG       | Rise and fall time*10 | Tprv, Tpfv | 20   | -    | -    | ns   |

|                    | Pulse width*10        | Tpwh       | 1000 | 2000 | -    | ns   |

| D1U D2U D2U D4U    | Rise and fall time*10 | Tprh, Tpfh | 10   | -    | -    | ns   |

| P1H, P2H, P3H, P4H | Pulse overlap time    | Tovrh      | 500  | 1000 | -    | ns   |

|                    | Duty ratio*10         | -          | 40   | 50   | 60   | %    |

|                    | Pulse width*10        | Tpws       | 1000 | 2000 | -    | ns   |

| SG                 | Rise and fall time*10 | Tprs, Tpfs | 10   | -    | -    | ns   |

| 30                 | Pulse overlap time    | Tovrh      | 500  | 1000 | -    | ns   |

|                    | Duty ratio*10         | -          | 40   | 50   | 60   | %    |

| RG                 | Pulse width           | Tpwr       | 100  | 1000 | -    | ns   |

| KG .               | Rise and fall time    | Tprr, Tpfr | 5    | -    | -    | ns   |

| TG-P1H             | Overlap time          | Tovr       | 1    | 2    | -    | μs   |

<sup>\*10:</sup> Symmetrical clock pulses should be overlapped at 50% of maximum amplitude.

### **S11510** series

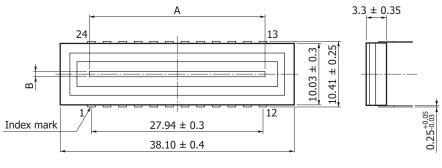

### - Dimensional outline (unit: mm)

| Typo no     | Active area |           |  |  |

|-------------|-------------|-----------|--|--|

| Type no.    | Α           | В         |  |  |

| S11510-1006 | 14.336 (H)  | 0.896 (V) |  |  |

| S11510-1106 | 28.672 (H)  | 0.896 (V) |  |  |

KMPDA0265EA

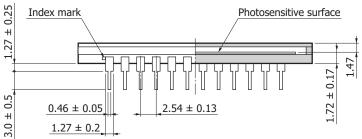

#### **Pin connections**

| Pin no. | Symbol | Function                             | Remark (standard operation) |

|---------|--------|--------------------------------------|-----------------------------|

| 1       | OS     | Output transistor source             | RL=100 kΩ                   |

| 2       | OD     | Output transistor drain              | +24 V                       |

| 3       | OG     | Output gate                          | +5 V                        |

| 4       | SG     | Summing gate                         | Same pulse as P4H           |

| 5       | SS     | Substrate                            | GND                         |

| 6       | RD     | Reset drain                          | +12 V                       |

| 7       | P4H    | CCD horizontal register clock-4      |                             |

| 8       | P3H    | CCD horizontal register clock-3      |                             |

| 9       | P2H    | CCD horizontal register clock-2      |                             |

| 10      | P1H    | CCD horizontal register clock-1      |                             |

| 11      | IG2H   | Test point (horizontal input gate-2) | -8 V                        |

| 12      | IG1H   | Test point (horizontal input gate-1) | -8 V                        |

| 13      | OFG    | Over flow gate                       | +12 V                       |

| 14      | OFD    | Over flow drain                      | +12 V                       |

| 15      | ISH    | Test point (horizontal input source) | Connect to RD               |

| 16      | ISV    | Test point (vertical input source)   | Connect to RD               |

| 17      | SS     | Substrate                            | GND                         |

| 18      | RD     | Reset drain                          | +12 V                       |

| 19      | IG2V   | Test point (vertical input gate-2)   | -8 V                        |

| 20      | IG1V   | Test point (vertical input gate-1)   | -8 V                        |

| 21      | P2V    | CCD vertical register clock-2        |                             |

| 22      | P1V    | CCD vertical register clock-1        |                             |

| 23      | TG     | Transfer gate                        | Same pulse as P2V           |

| 24      | RG     | Reset gate                           |                             |

### **CCD** image sensors

#### **S11510** series

#### Precaution for use (electrostatic countermeasures)

- When handling CCD sensors, always wear a wrist strap and also anti-static clothing, gloves, and shoes, etc. The wrist strap should have a protective resistor (about 1  $M\Omega$ ) on the side closer to the body and be grounded properly. Using a wrist strap having no protective resistor is hazardous because you may receive an electrical shock if electric leakage occurs.

- Avoid directly placing these sensors on a work bench that may carry an electrostatic charge.

- Provide ground lines with the work bench and work floor to allow static electricity to discharge.

- Ground the tools used to handle these sensors, such as tweezers and soldering irons.

It is not always necessary to provide all the electrostatic measures stated above. Implement these measures according to the amount of damage that occurs.

#### Driver circuit for CCD image sensor (S11510 series) C11287 [sold separately]

The C11287 is a driver circuit designed for HAMAMATSU CCD image sensors S11510 series. The C11287 can be used in spectrometers, etc. when combined with the CCD image sensor.

#### Features

- **■** Built-in 14-bit A/D converter

- Interface to computer: USB 2.0

- Power supply: USB bus power operation

Information furnished by HAMAMATSU is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omissions. Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein. Type numbers of products listed in the specification sheets or supplied as samples may have a suffix "(X)" which means tentative specifications or a suffix "(Z)" which means developmental specifications. ©2010 Hamamatsu Photonics K.K.

### **HAMAMATSU**

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, P.O.Box 6910, Bridgewater, N.J. 08807-0910, U.S.A., Telephone: (1) 908-231-0960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, P-82211 Herrsching am Ammersee, Germany, Telephone: (49) 8152-375-0, Fax: (49) 8152-265-8

France: Hamamatsu Photonics France S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 10, Fax: 33-(1) 69 53 71 10

United Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire AL7 1BW, United Kingdom, Telephone: (44) 1707-294888, Fax: (44) 1707-325777

North Europe: Hamamatsu Photonics Norden AB: Smidesvägen 12, SE-171 41 Solna, Sweden, Telephone: (46) 8-509-031-00, Fax: (46) 8-509-031-01

Italy: Hamamatsu Photonics Italia S.R.L.: Strada della Moia, 1 int. 6, 20020 Arese, (Milano), Italy, Telephone: (39) 02-935-81-733, Fax: (39) 02-935-81-741