## RE46C141

CMOS Photoelectric Smoke Detector ASIC with Interconnect

**Product Specification**

#### **General Description**

The RE46C141 is low power CMOS photoelectric type smoke detector IC. With minimal external components this circuit will provide all the required features for a photoelectric type smoke detector.

The design incorporates a gain selectable photo amplifier for use with an infrared emitter/detector pair. An internal oscillator strobes power to the smoke detection circuitry for 100us every 8.1 seconds to keep standby current to a minimum. If smoke is sensed the detection rate is increased to verify an alarm condition. A high gain mode is available for push button chamber testing.

A check for a low battery condition and chamber integrity is performed every 32 seconds when in standby. The temporal horn pattern supports the NFPA 72 emergency evacuation signal.

An interconnect pin allows multiple detectors to be connected such that when one units alarms, all units will sound.

Utilizing low power CMOS technology the RE46C141 was designed for use in smoke detectors that comply with Underwriters Laboratory Specification UL217 and UL268.

### **Features**

- Internal Power On Reset

- Low Quiescent Current Consumption

- Available in 16L PDIP or 16L N SOIC

- ESD Protection on all Pins

- Interconnect up to 40 Detectors

- Temporal Horn Pattern

- Low Battery and Chamber Test

- Compatible with Motorola MC145012

- Available in Standard Packaging or RoHS Compliant Pb Free Packaging.

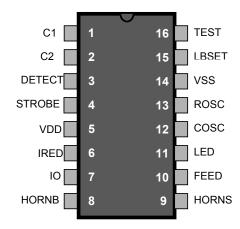

## Pin Configuration

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                           | SYMBOL          | VALUE                | UNITS |

|-------------------------------------|-----------------|----------------------|-------|

| Supply Voltage                      | $V_{DD}$        | 12.5                 | V     |

| Input Voltage Range Except FEED, IO | $V_{in}$        | $3$ to $V_{dd} + .3$ | V     |

| FEED Input Voltage Range            | $V_{infd}$      | -10 to +22           | V     |

| IO Input Voltage Range              | $V_{io1}$       | 3 to 17              | V     |

| Input Current except FEED           | l <sub>in</sub> | 10                   | mA    |

| Operating Temperature               | $T_A$           | -25 to 75            | °C    |

| Storage Temperature                 | $T_{STG}$       | -55 to 125           | °C    |

| Maximum Junction Temperature        | $T_{J}$         | 150                  | °C    |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and operation at these conditions for extended periods may affect device reliability.

This product utilizes CMOS technology with static protection; however proper ESD prevention procedures should be used when handling this product. Damage can occur when exposed to extremely high static electrical charge.

## DC Electrical Characteristics at TA = -25° to 75°C, VDD=9V, Typical Application (unless otherwise noted)

|                                |                    | Test    |                                                                      | Limits |     |      |       |

|--------------------------------|--------------------|---------|----------------------------------------------------------------------|--------|-----|------|-------|

| Parameter                      | Symbol             | Pin     | Test Conditions                                                      | Min    | Тур | Max  | Units |

| Supply Voltage                 | $V_{DD}$           | 5       | Operating                                                            | 6      |     | 12   | V     |

| Supply Current                 | I <sub>DD1</sub>   | 5       | Configured as in Figure 2, COSC=VSS                                  |        | 4   | 6    | uA    |

|                                | I <sub>DD2</sub>   | 5       | Configured as in Figure 2, VDD=12V, COSC=VSS                         |        | 5.5 | 8    | uA    |

|                                | I <sub>DD3</sub>   | 5       | Configured as in Figure 2,<br>STROBE on, IRED off, VDD=12V           |        |     | 2    | mA    |

|                                | I <sub>DD4</sub>   | 5       | Configured as in Figure 2,<br>STROBE on, IRED on, VDD=12V,<br>Note 1 |        |     | 3    | mA    |

| Input Voltage High             | $V_{IH1}$          | 10      | FEED                                                                 | 6.2    | 4.5 |      | V     |

|                                | $V_{IH2}$          | 7       | No Local Alarm, IO as an Input                                       | 3.2    |     |      | V     |

|                                | $V_{IH4}$          | 16      | TEST                                                                 | 8.5    |     |      | V     |

| Input Voltage Low              | $V_{IL1}$          | 10      | FEED                                                                 |        | 4.5 | 2.7  | V     |

|                                | V <sub>IL2</sub>   | 7       | No Local Alarm, IO as an Input                                       |        |     | 1.5  | V     |

|                                | $V_{IL4}$          | 16      | TEST                                                                 |        |     | 7    | V     |

| Input Leakage Low              | I <sub>IL1</sub>   | 1,2,3   | VDD=12V, COSC=12V, STROBE active                                     |        |     | -100 | nA    |

|                                | I <sub>IL2</sub>   | 12,15   | VDD=12V, Vin=VSS                                                     |        |     | -100 | nA    |

|                                | I <sub>IL3</sub>   | 16      | VDD=12V, Vin=VSS                                                     |        |     | -1   | uA    |

|                                | I <sub>LFD</sub>   | 10      | FEED=-10V                                                            |        |     | -50  | uA    |

| Input Leakage High             | I <sub>IH1</sub>   | 1,2     | VDD=12V, Vin=VDD, STROBE active                                      |        |     | 100  | nA    |

|                                | I <sub>IH2</sub>   | 3,12,15 | VDD=12V, Vin=VDD                                                     |        |     | 100  | nA    |

|                                | I <sub>HFD</sub>   | 10      | FEED=22V                                                             |        |     | 50   | uA    |

| Input Pull Down Current        | I <sub>PD1</sub>   | 16      | Vin=VDD                                                              | .25    |     | 10   | uA    |

|                                | I <sub>PDIO1</sub> | 7       | Vin=VDD                                                              | 20     |     | 80   | uA    |

|                                | I <sub>PDIO2</sub> | 7       | Vin=17V, VDD=12                                                      |        |     | 140  | uA    |

| Output Leakage Current<br>Low  | I <sub>OZL1</sub>  | 11,13   | Output Off, Output=VSS                                               |        |     | -1   | uA    |

| Output Leakage Current<br>High | I <sub>OZH1</sub>  | 11,13   | Output Off, Output=VDD                                               |        |     | 1    | uA    |

Note 1: Does not include Q3 emitter current.

# DC Electrical Characteristics (continued) at TA= -25° to 75°, VDD=9V, Typical Application (unless otherwise noted)

|                               |                     | Test  |                                                      | Limits                    |                     |                           |       |

|-------------------------------|---------------------|-------|------------------------------------------------------|---------------------------|---------------------|---------------------------|-------|

| Parameter                     | Symbol              | Pin   | Test Conditions                                      | Min                       | Тур                 | Max                       | Units |

| Output Voltage Low            | V <sub>OL1</sub>    | 8,9   | Iol=16mA, VDD=6.5V                                   |                           |                     | 1                         | V     |

|                               | V <sub>OL2</sub>    | 13    | Iol=5mA, VDD=6.5V                                    |                           | .5                  |                           | V     |

|                               | V <sub>OL3</sub>    | 11    | Iol=10mA, VDD=6.5V                                   |                           |                     | .6                        | V     |

| Output Voltage High           | V <sub>Oh1</sub>    | 8,9   | Ioh=-16mA, VDD=6.5V                                  | 5.5                       |                     |                           | V     |

| Output Current                | I <sub>IOH1</sub>   | 7     | Alarm, Vio=Vdd-2V or Vio=0V                          | -4                        |                     | -16                       | mA    |

|                               | I <sub>IODMP</sub>  | 7     | At Conclusion of Local Alarm or Test, Vio=1V         | 5                         |                     |                           | mA    |

| Low Battery Alarm Voltage     | $V_{LB}$            | 5     | R14=100K, R15=47K                                    | 6.9                       | 7.2                 | 7.5                       | V     |

| Output Voltage                | V <sub>STOF</sub>   | 4     | STROBE off, VDD=12V,<br>lout=-1uA                    | V <sub>DD</sub> 1         |                     |                           | V     |

|                               | V <sub>STON</sub>   | 4     | STROBE on, VDD=9V<br>lout= 100uA to 500uA            | V <sub>DD</sub> - 5.3     | V <sub>DD</sub> - 5 | V <sub>DD</sub> - 4.7     | V     |

|                               | $V_{IREDOF}$        | 6     | IRED off, VDD=12V, lout=1uA                          |                           |                     | .1                        | V     |

|                               | V <sub>IREDON</sub> | 6     | IRED on, VDD=9V<br>lout=0 to -6mA, Ta=25C            | 2.25                      | 3.1                 | 3.75                      | V     |

| Common Mode Voltage           | V <sub>CM1</sub>    | 1,2,3 | Local smoke, Push to Test or<br>Chamber Test, Note 1 | .5                        |                     | V <sub>DD</sub> -2        | V     |

| Smoke Comparator<br>Reference | $V_{ref}$           | ī     | Internal Reference                                   | V <sub>DD</sub> -<br>3.85 |                     | V <sub>DD</sub> -<br>3.15 | V     |

| Temperature Coefficient       | TC <sub>ST</sub>    | 4     | VDD=6V to 12V, STROBE Output Voltage                 |                           | .01                 |                           | %/°C  |

|                               | TC <sub>IRED</sub>  | 6     | VDD=6V to 12V, IRED Output Voltage                   |                           | .3                  |                           | %/°C  |

| Line Regulation               | $\Delta V_{STON}$   | 4,5   | Active, VDD=6V to 12V                                |                           | -50                 |                           | dB    |

|                               | $\Delta V_{IREDON}$ | 6,5   | Active, VDD=6V to 12V                                |                           | -30                 |                           | dB    |

Note 1: Not production tested

Typical values are for design information and are not guaranteed.

Limits over the specified temperature range are not production tested and are based on characterization data.

# AC Electrical Characteristics at TA =-25° to 75°, VDD=9V, VSS=0V, Component Values from Figure 2; R9=100K $\Omega$ , R12=10M $\Omega$ , C5= 1.5nF(unless otherwise noted)

|                         |                     | Test |                                                                       | Limits |          |      |       |

|-------------------------|---------------------|------|-----------------------------------------------------------------------|--------|----------|------|-------|

| Parameter               | Symbol              | Pin  | Test Conditions                                                       | Min    | Тур      | Max  | Units |

| Oscillator Period       | T <sub>POSC</sub>   | 12   | No Alarm Condition, Note 2                                            | 7.1    | 7.9      | 8.6  | mS    |

| LED and STROBE On Time  | T <sub>ON1</sub>    | 11,4 | Operating                                                             | 7.1    | 7.9      | 8.6  | mS    |

| LED Period              | T <sub>PLED1</sub>  | 11   | Standby, No Alarm                                                     | 28.8   | 32.4     | 35.2 | S     |

|                         | T <sub>PLED2</sub>  | 11   | Local Alarm Condition                                                 | .45    | .5       | .55  | S     |

|                         | T <sub>PLED4</sub>  | 11   | Remote Alarm Only                                                     | LE     | D IS NOT | ON   | S     |

| STROBE and IRED Pulse   | T <sub>PER1</sub>   | 4,6  | Standby, No Alarm                                                     | 7.3    | 8.1      | 8.8  | S     |

| Period                  | T <sub>PER1A</sub>  | 4,6  | Standby, After 1 Valid Smoke<br>Sample                                | 1.8    | 2        | 2.2  | S     |

|                         | T <sub>PER1B</sub>  | 4,6  | Standby, After 2 Consecutive Valid Smoke Samples                      | .9     | 1        | 1.1  | S     |

|                         | T <sub>PER2</sub>   | 4,6  | In Local Alarm – (3 Consecutive Valid Smoke Samples)                  | .9     | 1        | 1.1  | S     |

|                         | T <sub>PER3</sub>   | 4,6  | In Remote Alarm                                                       | 7.3    | 8.1      | 8.8  | S     |

|                         | T <sub>PER4</sub>   | 4,6  | Pushbutton Test                                                       |        | 250      |      | mS    |

|                         | T <sub>PER5</sub>   | 4,6  | Chamber Test or Low Battery<br>Test, no Alarms                        | 28.8   |          | 35.2 | S     |

| IRED On Time            | T <sub>ON2</sub>    | 6    | Operating, Note 2                                                     | 94     | 104      | 115  | uS    |

| Horn On Time            | T <sub>HON1</sub>   | 8,9  | Operating, Alarm Condition, Note 1                                    | 450    | 500      | 550  | mS    |

|                         | T <sub>HON2</sub>   | 8,9  | Low Battery or Failed Chamber<br>Test , No Alarm                      | 7.1    | 7.9      | 8.6  | mS    |

| Horn Off Time           | T <sub>HOF1</sub>   | 8,9  | Operating, Alarm Condition, Note 1                                    | 450    | 500      | 550  | mS    |

|                         | T <sub>HOF2</sub>   | 8,9  | Operating, Alarm Condition, Note 1                                    | 1.35   | 1.5      | 1.65 | S     |

|                         | T <sub>HOF3</sub>   | 8,9  | Low Battery or Failed Chamber Test, No Alarm                          | 28.8   | 32.4     | 35.2 | S     |

| IO Charge Dump Duration | T <sub>IODMP</sub>  | 7    | At Conclusion of Local Alarm or Test                                  | .68    |          | 1.1  | S     |

| IO Delay                | T <sub>IODLY1</sub> | 7    | From Start of Local Alarm to IO Active                                |        | 0        |      | S     |

| IO Filter               | T <sub>IOFILT</sub> | 7    | IO pulse width guaranteed to be filtered. IO as Input, No Local Alarm |        |          | 450  | mS    |

| Remote Alarm Delay      | T <sub>IODLY2</sub> | 7    | No Local Alarm, From IO Active Horn Active                            | .9     |          | 1.65 | S     |

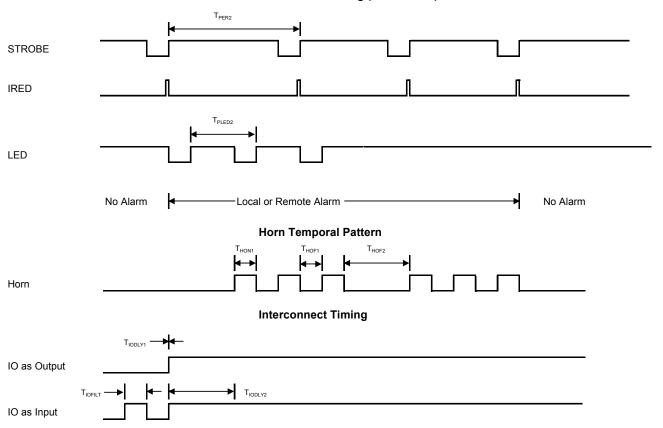

Note 1 - See timing diagram for Horn Temporal Pattern

Typical values are for design information and are not guaranteed.

Limits over the specified temperature range are not production tested and are based on characterization data.

Note 2 - T<sub>POSC</sub> and T<sub>ON2</sub> are 100% production tested. All other timing is guaranteed by functional testing.

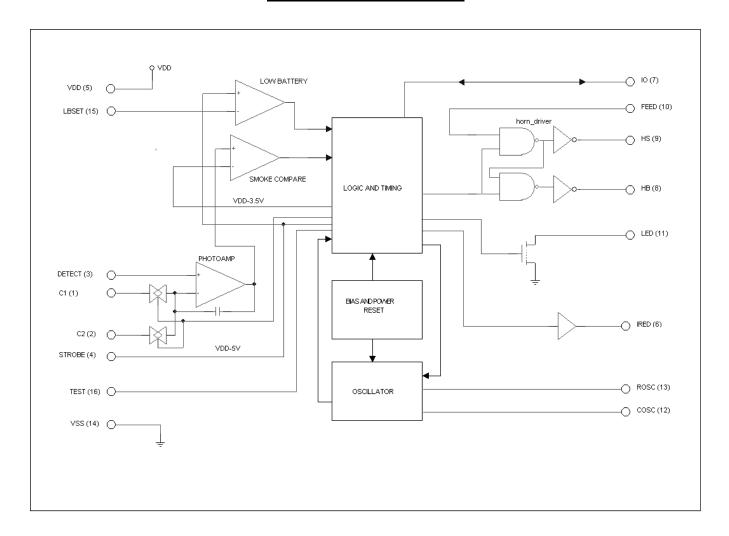

## **Functional Block Diagram**

Figure 1

## **PIN DESCRIPTIONS**

| PIN# | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                          |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | C1       | The capacitor connected to this pin sets the photo amplifier gain (high) for the push-to-test and chamber sensitivity test. The size of this capacitor will depend on the chamber background reflections. A=1+ (C1/10) where C1 is in pF. The gain should be <10000. |

| 2    | C2       | The capacitor connected to this pin sets the photo amplifier gain (normal) during standby. The value of this capacitor will depend on the smoke sensitivity required. A=1+ (C2/10) where C2 is in pF.                                                                |

| 3    | DETECT   | Positive input to the photo amplifier. This input is normally connected to the cathode of an external photo diode operated at zero bias.                                                                                                                             |

| 4    | STROBE   | Regulated output voltage of VDD-5 which is active during a test for smoke. This output is the negative side of the photo amplifier circuitry.                                                                                                                        |

| 5    | VDD      | Connect to the positive supply voltage                                                                                                                                                                                                                               |

| 6    | IRED     | Provides a regulated pulsed output voltage pre-driver for the infrared emitter. This output usually drives the base of an NPN transistor.                                                                                                                            |

| 7    | Ю        | This bidirectional pin provides the capability to interconnect many detectors in a single system. This pin has an internal pull-down device.                                                                                                                         |

| 8    | НВ       | This pin is connected to the metal electrode of a piezoelectric transducer.                                                                                                                                                                                          |

| 9    | HS       | HS is a complementary output to HB and connects to the ceramic electrode of the piezoelectric transducer.                                                                                                                                                            |

| 10   | FEED     | Usually connected to the feedback electrode through a current limiting resistor. If not used this pin must be connected to VDD or VSS.                                                                                                                               |

| 11   | LED      | Open drain NMOS output used to drive a visible LED.                                                                                                                                                                                                                  |

| 12   | cosc     | A capacitor connected to this pin with parallel resistor sets the internal clock low time which is approximately the clock period.                                                                                                                                   |

| 13   | ROSC     | A resistor between this pin and pin 12 (COSC) sets the internal clock high time. This also sets the IRED pulse width (100-200uS).                                                                                                                                    |

| 14   | VSS      | Connect to the negative supply voltage.                                                                                                                                                                                                                              |

| 15   | LBSET    | This input is connected to a VDD reference voltage to set the low battery warning voltage.                                                                                                                                                                           |

| 16   | TEST     | This input is used to invoke two test modes. This input has an internal pull-down.                                                                                                                                                                                   |

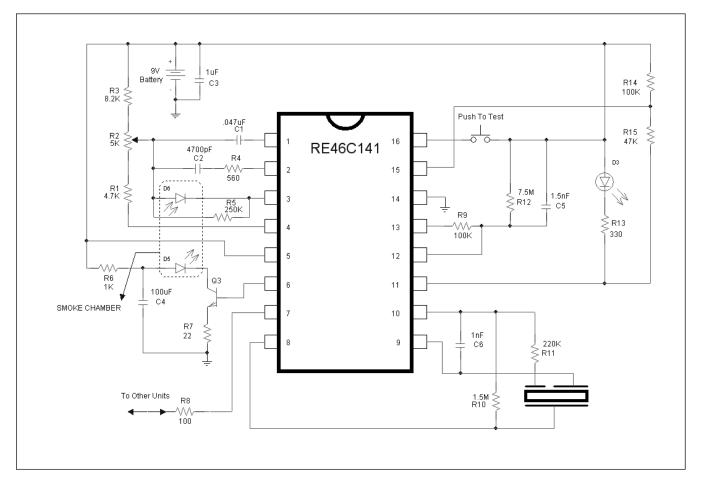

## **Typical Application**

Figure 2

#### Notes:

- 1. C3 should be located as close as possible to the device power pins.

- 2. C3 is typical for an alkaline battery. This capacitance should be increased to 4.7uF or greater for a carbon battery.

- 3. R10, R11 and C6 are typical values and may be adjusted to maximize sound pressure.

#### CIRCUIT DESCRIPTION AND APPLICATION NOTES

Note: All timing references are nominal. See electrical characteristics for limits.

Standby Internal Timing – With the external components specified in the typical application figure for ROSC and COSC the internal oscillator has a nominal period of 7.9mS. Normally the analog circuitry is powered down to minimize standby current (typically 4uA at 9V). Once every 8.1 seconds the detection circuitry (normal gain) is powered up for 7.9mS. Prior to completion of the 7.9mS period the IRED pulse is active for 100uS. At the conclusion of this 7.9mS period the photo amplifier is compared to an internal reference to determine the chamber status and latched. If a smoke condition is present the period to the next detection decreases and additional checks are made. Three consecutive smoke detections will cause the device to go into alarm and the horn circuit and interconnect will be active.

Once every 32 seconds the status of the battery voltage is checked. This status is checked and latched at the conclusion of the LED pulse. In addition, once every 32 seconds the chamber is activated and using the high gain mode (capacitor C1) a check of the chamber is made by amplifying background reflections. If either the low battery or the photo chamber test fails the horn will chirp for 7.9mS every 32 seconds.

The oscillator period is determined by the values of R9, R12 and C5 (see typical application FIG 2). The oscillator period  $T=T_R+T_F$  where  $T_R=.6931 * R12 * C5$  and  $T_F=.6931 * R9 * C5$

<u>Smoke Detection Circuitry</u> – A comparator compares the photo amp output to an internal reference voltage. If the required number of consecutive smoke conditions is met the device will go into local alarm and the horn will be active. In local alarm the C2 gain is internally increased by ~10% to provide alarm hysteresis.

<u>Push to Test Operation</u> – If the TEST input pin is activated (Vih) then, after one internal clock cycle, the smoke detection rate increases to once every 250mS. In this mode the high gain capacitor C1 is selected and background reflections are used to simulate a smoke condition. After the required consecutive detections the device will go into a local alarm condition. When the TEST input is deactivated (Vil) and after one clock cycle the normal gain capacitor C1 is selected. The detection rate continues at once every 250mS until 3 consecutive no smoke conditions are detected. At this point the device returns to standby timing.

<u>LED Operation</u> – In standby the LED is pulsed on for 7.9mS every 32 Seconds. In a local alarm condition or the push to test alarm the LED pulse frequency is increased to once every 0.5 seconds. In the case of a remote alarm the LED not active.

<u>Interconnect Operation</u> – The bidirectional IO pin allows for interconnection of multiple detectors. In a local alarm condition this pin is driven high immediately through a constant current source. Shorting this output to ground will not cause excessive current. The IO is ignored as an input during a local alarm.

The IO pin also has an NMOS discharge device that is active for 1 second after the conclusion of any type of local alarm. This device helps to quickly discharge any capacitance associated with the interconnect line.

If a remote active high signal is detected the device goes into remote alarm and the horn will be active. Internal protection circuitry allows for the signaling unit to have a higher supply voltage than the signaled unit without excessive current draw.

The interconnect input has a 500mS nominal digital filter. This allows for interconnection to other types of alarms (carbon monoxide for example) that may have a pulsed interconnect signal.

### RE46C141

#### **CMOS Photoelectric Smoke Detector ASIC with Interconnect** Product Specification

Low Battery and Chamber Test – In standby an internal reference is compared to the voltage divided VDD supply. Low battery status is latched at the conclusion of the LED pulse. The horn will chirp for 7.9ms every 32 seconds until the low battery condition no longer exists. In standby a chamber test is also performed every 32 seconds by switching to the high gain capacitor C1 and sensing the photo chamber background reflections. Two consecutive chamber tests failures will also cause the horn to chirp for 7.9mS every 32 seconds. The low battery chirp occurs next to the LED pulse and the failed chamber test chirp 16.2 seconds later. The low battery and chamber tests are not performed in a local or remote alarm condition. The low battery alarm threshold is approximately equal to ((5\*R15)/R14)+5 where R15 and R16 are in the same units.

<u>Diagnostic Mode</u> – In addition to the normal function of the TEST input a special diagnostic mode is available for calibration and test of the smoke detector. Taking the TEST pin below VSS and sourcing ~300uA out of the pin for 1 clock cycle will enable the diagnostic mode. In the diagnostic mode some of the pin functions are redefined. Refer to the table below for redefined pin functions in the diagnostic mode. In addition in this mode STROBE is always enabled and the IRED is pulsed at the clock rate of 10.5mS nominal.

| Pin Name | Pin Number | Description                                                                                                                                                                                                                                       |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ю        | 7          | Disabled as an output. A high on this pin directs the photo amplifier output to pin C1 (1) or C2 (2), determined by the level on LBSET (15). Amplification occurs during the IRED active time.                                                    |

| LBSET    | 15         | If IO is high then this pin controls the gain capacitor that is used. If LBSET is low then normal gain is selected and the photo amp output appears on C1 (1). If LBSET is high then high gain is selected and the photo amp output is on C2 (2). |

| FEED     | 10         | If LBSET (15) is low then taking this input high will enable hysteresis, which is a nominal 10% gain increase in normal gain mode.                                                                                                                |

| COSC     | 12         | If desired this pin can be driven by an external clock.                                                                                                                                                                                           |

| HORNB    | 8          | This pin becomes the smoke integrator output. A high level indicates that an alarm condition has been detected.                                                                                                                                   |

| LED      | 11         | The LED pin is used as a low battery indicator. For VDD above the low battery threshold the open drain NMOS is off. If VDD falls below the threshold the NMOS turns on.                                                                           |

## **Timing Diagrams**

## Standby Timing, No Alarm (not to scale) Oscillator Internal Clock T<sub>PER1</sub> T<sub>ON1</sub> STROBE **IRED** T<sub>PLED1</sub> LED Low Supply or Chamber Test Failure LED Low BatteryTest $T_{HON3}$ Low BatteryWarning Chirp Low Battery Warning Chirp Horn

Chamber Test and Warning is Offset from Low Battery Test and Warning by 21.5 Seconds

$T_{HOF3}$

## Timing Diagrams (continued)

#### Local Alarm Timing (not to scale)

#### Notes:

- 1. Smoke is not sampled when the horn is active. Horn cycle is self completing in local alarm but not in remote alarm.

- 2. Low battery warning chirp is suppressed in local or remote alarm.

- 3. IO Dump active only in local alarm, inactive if external alarm.

## RE46C141

CMOS Photoelectric Smoke Detector ASIC with Interconnect Product Specification

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.