## 30 W Digital Audio Amplifier with Integrated ADC

## **Digital Amplifier Features**

- Fully Integrated Power MOSFETs

- No Heatsink Required

- Programmable Power Foldback on Thermal Warning

- High Efficiency

- ♦ > 100 dB Dynamic Range

- ♦ < 0.1% THD+N @ 1 W

- Configurable Outputs (10% THD+N)

- 1 x 30 W into 4  $\Omega$ , Parallel Full-Bridge

- 2 x 15 W into 8 Ω, Full-Bridge

- 2 x 7 W into 4 Ω, Half-Bridge + 1 x 15 W into 8 Ω, Full-Bridge

- Built-In Protection with Error Reporting

- Overcurrent / Undervoltage / Thermal Overload Shutdown

- Thermal Warning Reporting

- PWM Popguard<sup>®</sup> for Half-Bridge Mode

- Click-free Start-up

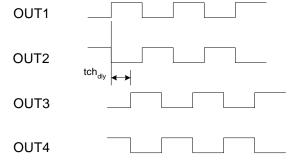

- Programmable Channel Delay for System Noise & Radiated Emissions Management

## **ADC Features**

- Stereo, 24-bit, 48 kHz Conversion

- Multi-bit Architecture

- 95 dB Dynamic Range (A-wtd)

- ◆ -86 dB THD+N

- Supports 2 Vrms Input with Passive Components

### **System Features**

- Asynchronous 2-channel Digital Serial Port

- 32 kHz to 96 kHz Input Sample Rates

- Operation with On-chip Oscillator Driver or Applied SYS\_CLK at 18.432, 24.576 or 27.000 MHz

- Integrated Sample Rate Converter (SRC)

- Eliminates Clock-jitter Effects

- Input Sample Rate Independent Operation

- Simplifies System Integration

- Spread Spectrum PWM Modulation

- Reduces EMI Radiated Energy

- Low Quiescent Current

## (Features continued on page 2)

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

Copyright © Cirrus Logic, Inc. 2008 (All Rights Reserved)

### **Software Mode System Features**

- Digital Audio Processing

- 5 Programmable Parametric EQ Filters

- Selectable High-pass Filter

- Bass/Treble Tone Control

- Adaptive Loudness Compensation

- 2-channel Mixer

- 2.1 Bass Management

- 24 dB/octave Linkwitz-Riley Crossover Filters

- De-emphasis Filter

- Selectable Serial Audio Interface Formats

- Left-justified up to 24-bit

- I<sup>2</sup>S up to 24-bit

- Right-justified 16-, 18-, 20-, 24-bits

- Digital Serial Connection to Additional CS4525 or DACs for Subwoofer

- Digital Interface to External Lip-sync Delay

- PWM Switch Rate Shifting Eliminates AM Frequency Interference

- Digital Volume Control with Soft Ramp

- +24 to -103 dB in 0.5 dB steps

- Programmable Peak Detect and Limiter

- ♦ 2-Channel Logic-level PWM Output

- Programmable Channel Mapping

- Can Drive an External PWM Amplifier, Headphone Amplifier, or Line-out Amplifier

- Integrated Headphone Detection

- Flexible Power Output Configurations

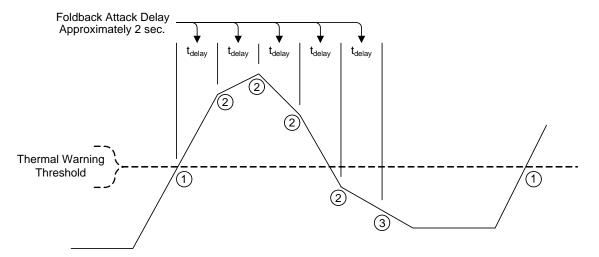

- Thermal Foldback for Interruption-free Power-stage Protection

- Supports Internal and External Power Stages

- Operation from On-chip Oscillator Driver or Applied Systems Clock

- ♦ Supports I<sup>2</sup>C<sup>®</sup> Host Control Interface

#### Hardware Mode System Features

- 2-Channel Stereo Full Bridge Power Outputs

- Analog and Digital Inputs

- I<sup>2</sup>S and Left-justified Serial Input Formats

- Thermal Foldback for Interruption-free Protection of Internal Power Stage

- Operation from Applied Systems Clock

- External Mute Input

#### **Common Applications**

- Integrated Digital TV's

- Flat Panel TV Monitors

- Computer/TV Monitors

- Mini/Micro Shelf Systems

- Digital Powered Speakers

- Portable Docking Stations

- Computer Desktop Audio

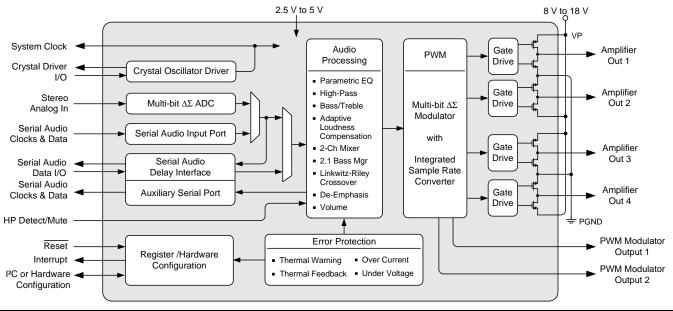

### **General Description**

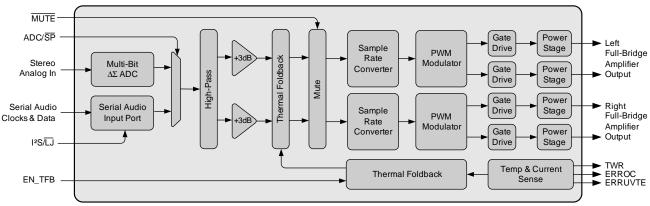

The CS4525 is a stereo analog or digital input PWM high efficiency Class D amplifier audio system with an integrated stereo analog-to-digital (A/D) converter. The stereo power amplifiers can deliver up to 15 W per channel into 8  $\Omega$  speakers from a small space-saving 48-pin QFN package. The PWM amplifier can achieve greater than 85% efficiency. The package is thermally enhanced for optimal heat dissipation which eliminates the need for a heatsink.

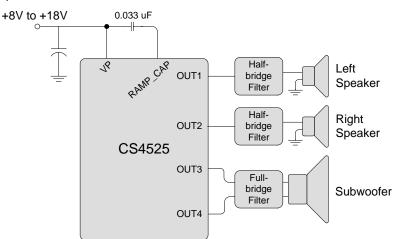

The power stage outputs can be configured as two fullbridge channels for 2 x 15 W operation, two half-bridge channels and one full-bridge channel for 2 x 7 W + 1 x 15 W operation, or one parallel full-bridge channel for 1 x 30 W operation. The CS4525 integrates on-chip over-current, under-voltage, and over-temperature protection and error reporting as well as a thermal warning indicator and programmable foldback of the output power to allow cooling.

The main digital serial port on the CS4525 can support asynchronous operation with the integrated on-chip sample rate converter (SRC) which eases system integration. The SRC allows for a fixed PWM switching frequency regardless of incoming sample rate as well as optimal clocking for the A/D modulators.

An on-chip oscillator driver eliminates the need for an external crystal oscillator circuit, reducing overall design cost and conserving circuit board space. The CS4525 automatically uses the on-chip oscillator driver in the absence of an applied master clock.

The CS4525 is available in a 48-pin QFN package in Commercial grade (0° to +70° C). The CRD4525-Q1 4-layer, 1 oz. copper and CRD4525-D1 2-layer, 1 oz. copper customer reference designs are also available.

Please refer to "Ordering Information" on page 97 for complete ordering information.

| 1. PIN DESCRIPTIONS - SOFTWARE MODE                                           | 8    |

|-------------------------------------------------------------------------------|------|

| 2. PIN DESCRIPTIONS - HARDWARE MODE                                           | 10   |

| 2.1 Digital I/O Pin Characteristics                                           | 12   |

| 3. TYPICAL CONNECTION DIAGRAMS                                                |      |

| 4. TYPICAL SYSTEM CONFIGURATION DIAGRAMS                                      | . 15 |

| 5. CHARACTERISTICS AND SPECIFICATIONS                                         | . 18 |

| 6. APPLICATIONS                                                               | . 26 |

| 6.1 Software Mode                                                             | . 26 |

| 6.1.1 System Clocking                                                         | . 26 |

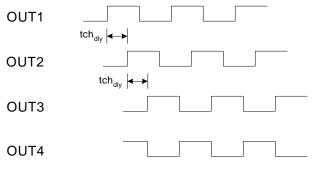

| 6.1.1.1 SYS_CLK Input Clock Mode                                              | . 26 |

| 6.1.1.2 Crystal Oscillator Mode                                               | . 27 |

| 6.1.2 Power-Up and Power-Down                                                 | 28   |

| 6.1.2.1 Power-Up Sequence                                                     | . 28 |

| 6.1.2.2 Power-Down Sequence                                                   | . 28 |

| 6.1.3 Input Source Selection                                                  | . 29 |

| 6.1.4 Digital Sound Processing                                                | . 29 |

| 6.1.4.1 Pre-Scaler                                                            | . 30 |

| 6.1.4.2 Digital Signal Processing High-Pass Filter                            | 30   |

| 6.1.4.3 Channel Mixer                                                         | 30   |

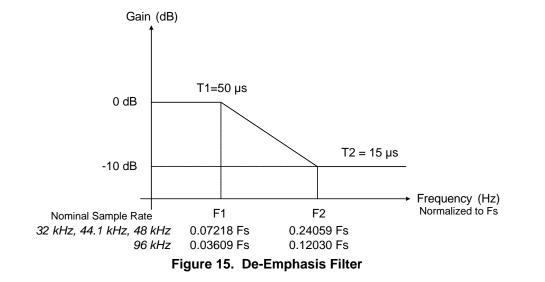

| 6.1.4.4 De-Emphasis                                                           | 31   |

| 6.1.4.5 Tone Control                                                          | 31   |

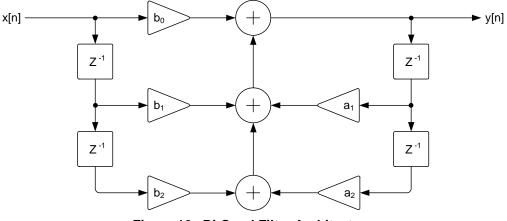

| 6.1.4.6 Parametric EQ                                                         | 33   |

| 6.1.4.7 Adaptive Loudness Compensation                                        | 34   |

| 6.1.4.8 Bass Management                                                       | 35   |

| 6.1.4.9 Volume and Muting Control                                             | . 36 |

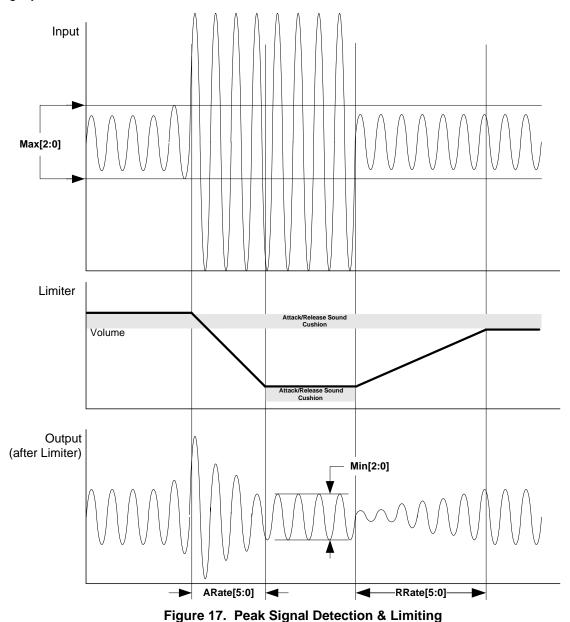

| 6.1.4.10 Peak Signal Limiter                                                  | 37   |

| 6.1.4.11 Thermal Limiter                                                      | . 39 |

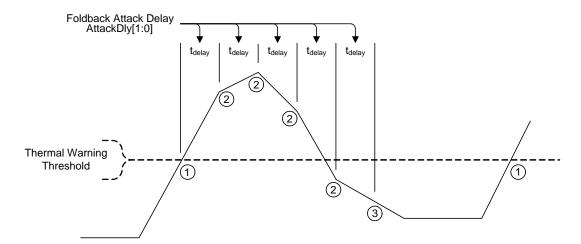

| 6.1.4.12 Thermal Foldback                                                     | 40   |

| 6.1.4.13 2-Way Crossover & Sensitivity Control                                | 42   |

| 6.1.5 Auxiliary Serial Output                                                 | 43   |

| 6.1.6 Serial Audio Delay & Warning Input Port                                 | 44   |

| 6.1.6.1 Serial Audio Delay Interface                                          | . 44 |

| 6.1.6.2 External Warning Input Port                                           | . 44 |

| 6.1.7 Powered PWM Outputs                                                     |      |

| 6.1.7.1 Output Channel Configurations                                         |      |

| 6.1.7.2 PWM Popguard Transient Control                                        | . 45 |

| 6.1.8 Logic-Level PWM Outputs                                                 | . 46 |

| 6.1.8.1 Recommended PWM_SIG Power-Up Sequence for an External PWM Amplifier   |      |

| 6.1.8.2 Recommended PWM_SIG Power-Down Sequence for an External PWM Amplifier |      |

| 6.1.8.3 Recommended PWM_SIG Power-Up Sequence for Headphone & Line-Out        |      |

| 6.1.8.4 Recommended PWM_SIG Power-Down Sequence for Headphone & Line-Out      |      |

| 6.1.8.5 PWM_SIG Logic-Level Output Configurations                             |      |

| 6.1.9 PWM Modulator Configuration                                             |      |

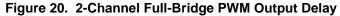

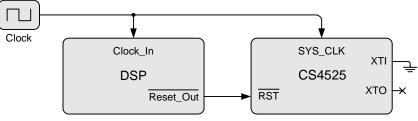

| 6.1.9.1 PWM Channel Delay                                                     |      |

| 6.1.9.2 PWM AM Frequency Shift                                                |      |

| 6.1.10 Headphone Detection & Hardware Mute Input                              |      |

| 6.1.11 Interrupt Reporting                                                    |      |

| 6.1.12 Automatic Power Stage Shut-Down                                        |      |

| 6.2 Hardware Mode                                                             |      |

| 6.2.1 System Clocking                                                         |      |

| 6.2.2 Power-Up and Power-Down                                                 |      |

| 6.2.2.1 Power-Up Sequence                                                     | 54   |

##

| 6.2.2.2 Power-Down Sequence                                                   |      |

|-------------------------------------------------------------------------------|------|

| 6.2.3 Input Source Selection                                                  |      |

| 6.2.4 PWM Channel Delay                                                       |      |

| 6.2.5 Digital Signal Flow                                                     |      |

| 6.2.5.1 High-Pass Filter                                                      |      |

| 6.2.5.2 Mute Control                                                          |      |

| 6.2.5.3 Warning and Error Reporting                                           | . 56 |

| 6.2.6 Thermal Foldback                                                        | . 57 |

| 6.2.7 Automatic Power Stage Shut-Down                                         | . 58 |

| 6.3 PWM Modulators and Sample Rate Converters                                 |      |

| 6.4 Output Filters                                                            |      |

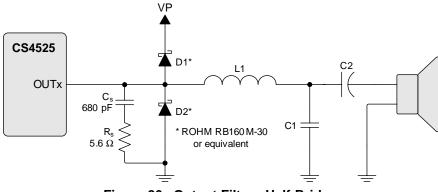

| 6.4.1 Half-Bridge Output Filter                                               |      |

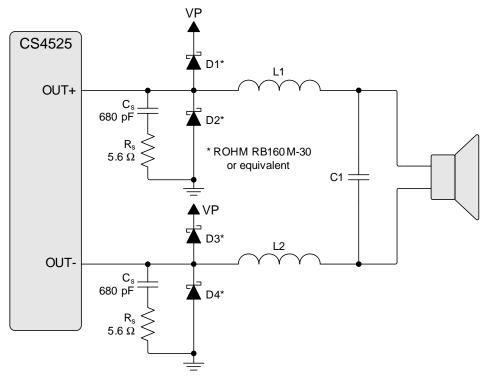

| 6.4.2 Full-Bridge Output Filter (Stereo or Parallel)                          |      |

| 6.5 Analog Inputs                                                             |      |

| 6.6 Serial Audio Interfaces                                                   |      |

| 6.6.1 I <sup>2</sup> S Data Format                                            |      |

| 6.6.2 Left-Justified Data Format                                              |      |

|                                                                               |      |

| 6.6.3 Right-Justified Data Format                                             |      |

| 6.7 Integrated VD Regulator                                                   | . 63 |

| 6.8 I <sup>2</sup> C Control Port Description and Timing                      | . 64 |

| 7. PCB LAYOUT CONSIDERATIONS                                                  |      |

| 7.1 Power Supply, Grounding                                                   |      |

| 7.2 Output Filter Layout                                                      |      |

| 7.3 QFN Thermal Pad                                                           |      |

| 8. REGISTER QUICK REFERENCE                                                   | . 66 |

| 9. REGISTER DESCRIPTIONS                                                      | . 69 |

| 9.1 Clock Configuration (Address 01h)                                         | . 69 |

| 9.1.1 SYS_CLK Output Enable (EnSysClk)                                        |      |

| 9.1.2 SYS_CLK Output Divider (DivSysClk)                                      |      |

| 9.1.3 Clock Frequency (ClkFreq[1:0])                                          |      |

| 9.1.4 HP_Detect/Mute Pin Active Logic Level (HP/MutePol)                      |      |

| 9.1.5 HP_Detect/Mute Pin Mode (HP/Mute)                                       |      |

| 9.1.6 Modulator Phase Shifting (PhaseShift)                                   |      |

| 9.1.7 AM Frequency Shifting (FreqShift)                                       |      |

| 9.2 Input Configuration (Address 02h)                                         |      |

|                                                                               |      |

| 9.2.1 Input Source Selection (ADC/SP)                                         |      |

| 9.2.2 ADC High-Pass Filter Enable (EnAnHPF)                                   |      |

| 9.2.3 Serial Port Sample Rate (SPRate[1:0]) - Read Only                       |      |

| 9.2.4 Input Serial Port Digital Interface Format (DIF [2:0])                  |      |

| 9.3 AUX Port Configuration (Address 03h)                                      |      |

| 9.3.1 Enable Aux Serial Port (EnAuxPort)                                      |      |

| 9.3.2 Delay & Warning Port Configuration (DlyPortCfg[1:0])                    |      |

| 9.3.3 Aux/Delay Serial Port Digital Interface Format (AuxI <sup>2</sup> S/LJ) |      |

| 9.3.4 Aux Serial Port Right Channel Data Select (RChDSel[1:0])                |      |

| 9.3.5 Aux Serial Port Left Channel Data Select (LChDSel[1:0])                 |      |

| 9.4 Output Configuration (Address 04h)                                        | . 73 |

| 9.4.1 Output Configuration (OutputCfg[1:0])                                   | . 73 |

| 9.4.2 PWM Signals Output Data Select (PWMDSel[1:0])                           | . 73 |

| 9.4.3 Channel Delay Settings (OutputDly[3:0])                                 |      |

| 9.5 Foldback and Ramp Configuration (Address 05h)                             |      |

| 9.5.1 Select VP Level (SelectVP)                                              |      |

| 9.5.2 Enable Thermal Foldback (EnTherm)                                       |      |

| 9.5.3 Lock Foldback Adjust (LockAdj)                                          |      |

| 9.5.4 Foldback Attack Delay (AttackDly[1:0])                                  |      |

| 3.3.4 FUIUDALK ALLALK DEIAY (ALLALKDIY[1.0])                                  | . 75 |

| 9.5.5 Enable Foldback Floor (EnFloor)                                       |      |

|-----------------------------------------------------------------------------|------|

| 9.5.6 Ramp Speed (RmpSpd[1:0])                                              |      |

| 9.6 Mixer / Pre-Scale Configuration (Address 06h)                           |      |

| 9.6.1 Pre-Scale Attenuation (PreScale[2:0])                                 |      |

| 9.6.2 Right Channel Mixer (RChMix[1:0])                                     |      |

| 9.6.3 Left Channel Mixer (LChMix[1:0])                                      |      |

| 9.7 Tone Configuration (Address 07h)                                        |      |

| 9.7.1 De-Emphasis Control (DeEmph)                                          |      |

| 9.7.2 Adaptive Loudness Compensation Control (Loudness)                     |      |

| 9.7.3 Digital Signal Processing High-Pass Filter (EnDigHPF)                 | . 77 |

| 9.7.4 Treble Corner Frequency (TrebFc[1:0])                                 | . 77 |

| 9.7.5 Bass Corner Frequency (BassFc[1:0])                                   | . 77 |

| 9.7.6 Tone Control Enable (EnToneCtrl)                                      | . 77 |

| 9.8 Tone Control (Address 08h)                                              | . 78 |

| 9.8.1 Treble Gain Level (Treb[3:0])                                         | . 78 |

| 9.8.2 Bass Gain Level (Bass[3:0])                                           |      |

| 9.9 2.1 Bass Manager/Parametric EQ Control (Address 09h)                    |      |

| 9.9.1 Freeze Controls (Freeze)                                              |      |

| 9.9.2 Hi-Z PWM_SIG Outputs (HiZPSig)                                        |      |

| 9.9.3 Bass Cross-Over Frequency (BassMgr[2:0])                              |      |

| 9.9.4 Enable Channel B Parametric EQ (EnChBPEq)                             |      |

| 9.9.5 Enable Channel A Parametric EQ (EnChAPEq)                             |      |

| 9.10 Volume and 2-Way Cross-Over Configuration (Address 55h)                |      |

| 9.10.1 Soft Ramp and Zero Cross Control (SZCMode[1:0])                      |      |

| 9.10.2 Enable 50% Duty Cycle for Mute Condition (Mute50/50)                 |      |

| 9.10.3 Auto-Mute (AutoMute)                                                 |      |

| 9.10.4 Enable 2-Way Crossover (En2Way)                                      |      |

| 9.10.5 2-Way Cross-Over Frequency (2WayFreq[2:0])                           |      |

| 9.11 Channel A & B: 2-Way Sensitivity Control (Address 56h)                 |      |

| 9.11.1 Channel A and Channel B Low-Pass Sensitivity Adjust (LowPass[3:0])   |      |

| 9.11.2 Channel A and Channel B High-Pass Sensitivity Adjust (HighPass[3:0]) |      |

| 9.12 Master Volume Control (Address 57h)                                    |      |

|                                                                             |      |

| 9.12.1 Master Volume Control (MVol[7:0])                                    |      |

| 9.13 Channel A and B Volume Control (Address 58h & 59h)                     |      |

| 9.13.1 Channel X Volume Control (ChXVol[7:0])                               |      |

| 9.14 Sub Channel Volume Control (Address 5Ah)                               |      |

| 9.14.1 Sub Channel Volume Control (SubVol[7:0])                             |      |

| 9.15 Mute/Invert Control (Address 5Bh)                                      |      |

| 9.15.1 ADC Invert Signal Polarity (InvADC)                                  |      |

| 9.15.2 Invert Channel PWM Signal Polarity (InvChX)                          |      |

| 9.15.3 Invert Sub PWM Signal Polarity (InvSub)                              |      |

| 9.15.4 ADC Channel Mute (MuteADC)                                           |      |

| 9.15.5 Independent Channel A & B Mute (MuteChX)                             |      |

| 9.15.6 Sub Channel Mute (MuteSub)                                           |      |

| 9.16 Limiter Configuration 1 (Address 5Ch)                                  |      |

| 9.16.1 Maximum Threshold (Max[2:0])                                         |      |

| 9.16.2 Minimum Threshold (Min[2:0])                                         |      |

| 9.16.3 Peak Signal Limit All Channels (LimitAll)                            |      |

| 9.16.4 Peak Detect and Limiter Enable (EnLimiter)                           |      |

| 9.17 Limiter Configuration 2 (Address 5Dh)                                  | . 87 |

| 9.17.1 Limiter Release Rate (RRate[5:0])                                    | . 87 |

| 9.18 Limiter Configuration 3 (Address 5Eh)                                  |      |

| 9.18.1 Enable Thermal Limiter (EnThLim)                                     |      |

| 9.18.2 Limiter Attack Rate (ARate[5:0])                                     |      |

|                                                                             |      |

| 9.19 Power Control (Address 5Fh)                        | 88 |

|---------------------------------------------------------|----|

| 9.19.1 Automatic Power Stage Retry (AutoRetry)          | 88 |

| 9.19.2 Enable Over-Current Protection (EnOCProt)        | 88 |

| 9.19.3 Select VD Level (SelectVD)                       |    |

| 9.19.4 Power Down ADC (PDnADC)                          | 88 |

| 9.19.5 Power Down PWM Power Output X (PDnOutX)          | 89 |

| 9.19.6 Power Down (PDnAll)                              | 89 |

| 9.20 Interrupt (Address 60h)                            |    |

| 9.20.1 SRC Lock State Transition Interrupt (SRCLock)    |    |

| 9.20.2 ADC Overflow Interrupt (ADCOvfl)                 |    |

| 9.20.3 Channel Overflow Interrupt (ChOvfl)              |    |

| 9.20.4 Amplifier Error Interrupt Bit (AmpErr)           |    |

| 9.20.5 Mask for SRC State (SRCLockM)                    |    |

| 9.20.6 Mask for ADC Overflow (ADCOvfIM)                 |    |

| 9.20.7 Mask for Channel X and Sub Overflow (ChOvflM)    |    |

| 9.20.8 Mask for Amplifier Error (AmpErrM)               |    |

| 9.21 Interrupt Status (Address 61h) - Read Only         |    |

| 9.21.1 SRC State Transition (SRCLockSt)                 |    |

| 9.21.2 ADC Overflow (ADCOvflSt)                         |    |

| 9.21.3 Sub Overflow (SubOvflSt)                         |    |

| 9.21.4 Channel X Overflow (ChXOvflSt)                   |    |

| 9.21.5 Ramp-Up Cycle Complete (RampDone)                |    |

| 9.22 Amplifier Error Status (Address 62h) - Read Only   |    |

| 9.22.1 Over-Current Detected On Channel X (OverCurrX)   |    |

| 9.22.2 External Amplifier State (ExtAmpSt)              |    |

| 9.22.3 Under Voltage / Thermal Error State (UVTE[1:0])  |    |

| 9.23 Device I.D. and Revision (Address 63h) - Read Only | 94 |

| 9.23.1 Device Identification (DeviceID[4:0])            |    |

| 9.23.2 Device Revision (RevID[2:0])                     |    |

| 10. PARAMETER DEFINITIONS                               |    |

| 11. REFERENCES                                          |    |

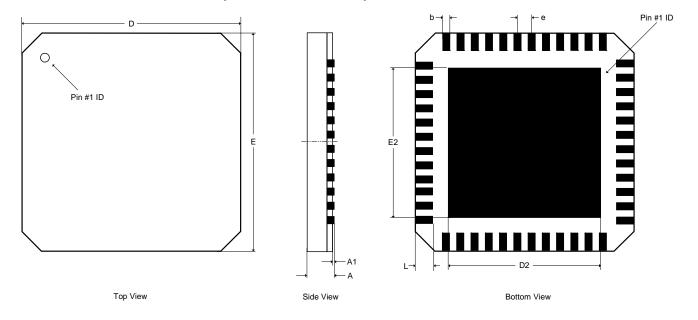

| 12. PACKAGE DIMENSIONS                                  |    |

| 13. THERMAL CHARACTERISTICS                             |    |

| 13.1 Thermal Flag                                       |    |

| 14. ORDERING INFORMATION                                | 97 |

| 15. REVISION HISTORY                                    |    |

|                                                         |    |

## LIST OF FIGURES

| Figure 1.Typical Connection Diagram - Software Mode          |  |

|--------------------------------------------------------------|--|

| Figure 2. Typical Connection Diagram - Hardware Mode         |  |

| Figure 3.Typical System Configuration 1                      |  |

| Figure 4.Typical System Configuration 2                      |  |

| Figure 5. Typical System Configuration 3                     |  |

| Figure 6.Typical System Configuration 4                      |  |

| Figure 7.Serial Audio Input Port Timing                      |  |

| Figure 8.AUX Serial Port Interface Master Mode Timing        |  |

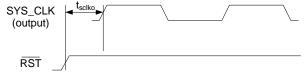

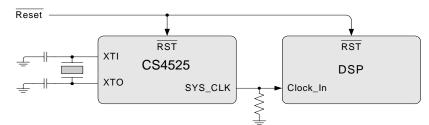

| Figure 9.SYS_CLK Timing from Reset                           |  |

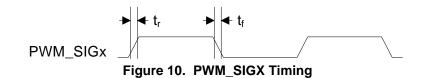

| Figure 10.PWM_SIGX Timing                                    |  |

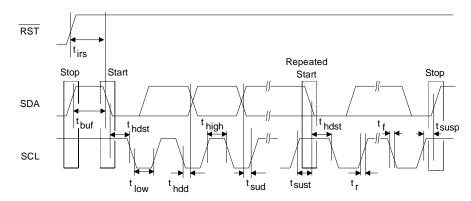

| Figure 11.Control Port Timing - I <sup>2</sup> C             |  |

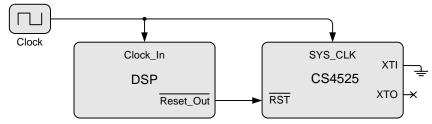

| Figure 12. Typical SYS_CLK Input Clocking Configuration      |  |

| Figure 13. Typical Crystal Oscillator Clocking Configuration |  |

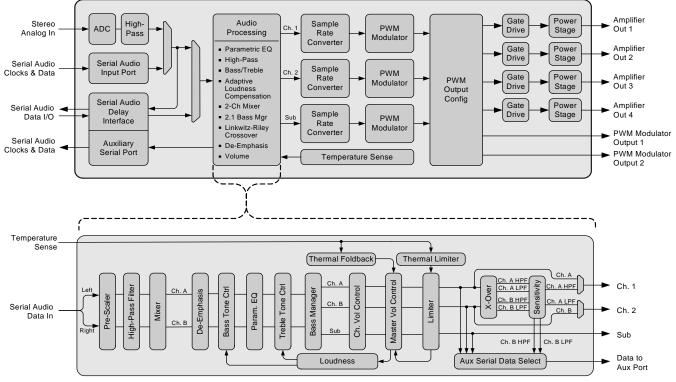

| Figure 14.Digital Signal Flow                                |  |

| Figure 15.De-Emphasis Filter                                 |  |

|                                                              |  |

| Figure 16.Bi-Quad Filter Architecture                   | 33 |

|---------------------------------------------------------|----|

| Figure 17.Peak Signal Detection & Limiting              |    |

| Figure 18.Foldback Process                              |    |

| Figure 19. Popguard Connection Diagram                  |    |

| Figure 20.2-Channel Full-Bridge PWM Output Delay        | 50 |

| Figure 21.3-Channel PWM Output Delay                    | 50 |

| Figure 22. Typical SYS_CLK Input Clocking Configuration |    |

| Figure 23.Hardware Mode PWM Output Delay                |    |

| Figure 24.Hardware Mode Digital Signal Flow             | 56 |

| Figure 25.Foldback Process                              |    |

| Figure 26.Output Filter - Half-Bridge                   |    |

| Figure 27.Output Filter - Full-Bridge                   |    |

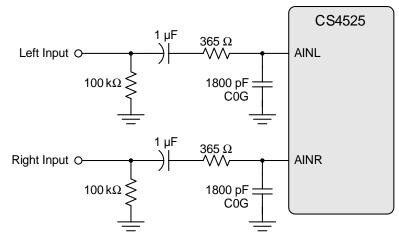

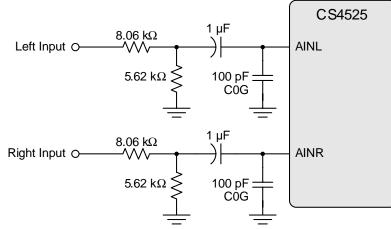

| Figure 28.Recommended Unity Gain Input Filter           |    |

| Figure 29.Recommended 2 V <sub>RMS</sub> Input Filter   |    |

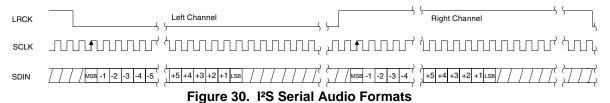

| Figure 30.I <sup>2</sup> S Serial Audio Formats         |    |

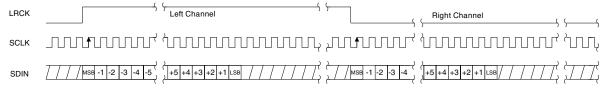

| Figure 31.Left-Justified Serial Audio Formats           |    |

| Figure 32.Right-Justified Serial Audio Formats          |    |

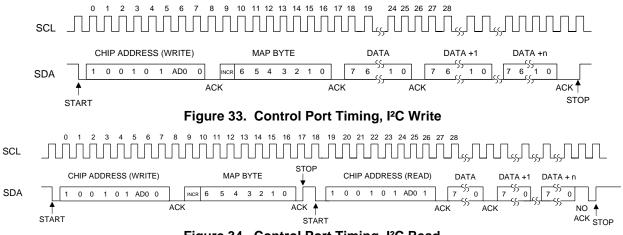

| Figure 33.Control Port Timing, I <sup>2</sup> C Write   |    |

| Figure 34.Control Port Timing, I <sup>2</sup> C Read    |    |

|                                                         |    |

## LIST OF TABLES

| Table 1. I/O Power Rails                                              | 12 |

|-----------------------------------------------------------------------|----|

| Table 2. Bass Shelving Filter Corner Frequencies                      | 31 |

| Table 3. Treble Shelving Filter Corner Frequencies                    | 32 |

| Table 4. Bass Management Cross-Over Frequencies                       | 35 |

| Table 5. 2-Way Cross-Over Frequencies                                 | 42 |

| Table 6. Auxiliary Serial Port Data Output                            | 43 |

| Table 7. Nominal Switching Frequencies of the Auxiliary Serial Output | 43 |

| Table 8. PWM Power Output Configurations                              | 45 |

| Table 9. Typical Ramp Times for Various VP Voltages                   |    |

| Table 10. PWM Logic-Level Output Configurations                       | 49 |

| Table 11. PWM Output Switching Rates and Quantization Levels          | 51 |

| Table 12. Output of PWM_SIG Outputs                                   | 52 |

| Table 13. SYS_CLK Frequency Selection                                 |    |

| Table 14. Input Source Selection                                      | 55 |

| Table 15. Serial Audio Interface Format Selection                     |    |

| Table 16. Thermal Foldback Enable Selection                           | 57 |

| Table 17. PWM Output Switching Rates and Quantization Levels          |    |

| Table 18. Low-Pass Filter Components - Half-Bridge                    | 59 |

| Table 19. DC-Blocking Capacitors Values - Half-Bridge                 | 59 |

| Table 20. Low-Pass Filter Components - Full-Bridge                    | 60 |

| Table 21. Power Supply Configuration and Settings                     | 63 |

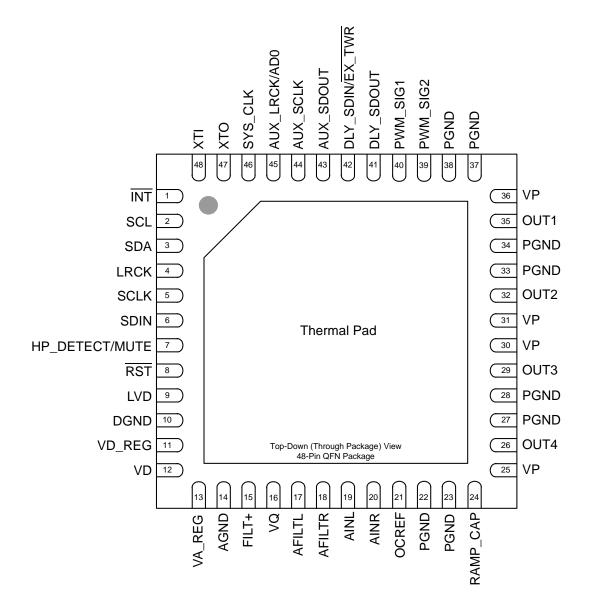

1. PIN DESCRIPTIONS - SOFTWARE MODE

| Pin Name           | Pin Description |                                                                                                                                                                |  |  |  |  |

|--------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| INT                | 1               | Interrupt (Output) - Indicates an interrupt condition has occurred.                                                                                            |  |  |  |  |

| SCL                | 2               | Control Port Clock (Input) - Serial clock for the I <sup>2</sup> C control port.                                                                               |  |  |  |  |

| SDA                | 3               | ontrol Data (Input/Output) - Bi-directional data I/O for the I <sup>2</sup> C control port.                                                                    |  |  |  |  |

| LRCK               | 4               | Left Right Clock ( <i>Input</i> ) - Determines which channel, Left or Right, is currently active on the serial audio data line.                                |  |  |  |  |

| SCLK               | 5               | rial Clock (Input) - Serial bit clock for the serial audio interface.                                                                                          |  |  |  |  |

| SDIN               | 6               | rial Audio Data Input (Input) - Input for two's complement serial audio data.                                                                                  |  |  |  |  |

| HP_DETECT/<br>MUTE | 7               | <b>Headphone Detect / Mute</b> ( <i>Input</i> ) - Headphone detection or mute input signal as configured via the I <sup>2</sup> C control port.                |  |  |  |  |

| RST                | 8               | <b>Reset</b> ( <i>Input</i> ) - The device enters a low power mode and all internal registers are reset to their default settings when this pin is driven low. |  |  |  |  |

#

| LVD                          | 9                                                                                                              | <b>VD Voltage Level Indicator</b> ( <i>Input</i> ) - Identifies the voltage level attached to VD. When applying 5.0 V to VD, LVD must be connected to VD. When applying 2.5 V or 3.3 V to VD, LVD must be DGND.                                               |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DGND                         | 10                                                                                                             | Digital Ground (Input) - Ground for the internal logic and digital I/O.                                                                                                                                                                                       |  |  |  |

| VD_REG                       | 11                                                                                                             | Core Logic Power ( <i>Output</i> ) - Internally generated low voltage power supply for digital logic.                                                                                                                                                         |  |  |  |

| VD                           | 12                                                                                                             | <b>Power</b> ( <i>Input</i> ) - Positive power supply for the internal regulators and digital I/O.                                                                                                                                                            |  |  |  |

| VA_REG                       | 13                                                                                                             | Analog Power (Output) - Internally generated positive power for the analog section and I/O.                                                                                                                                                                   |  |  |  |

| AGND                         | 14                                                                                                             | nalog Ground (Input) - Ground reference for the internal analog section and I/O.                                                                                                                                                                              |  |  |  |

| FILT+                        | 15                                                                                                             | <b>Positive Voltage Reference</b> ( <i>Output</i> ) - Positive reference voltage for the internal ADC sampling ircuits.                                                                                                                                       |  |  |  |

| VQ                           | 16                                                                                                             | Common Mode Voltage (Output) - Filter connection for internal common mode voltage.                                                                                                                                                                            |  |  |  |

| AFILTL<br>AFILTR             | 17<br>18                                                                                                       | Antialias Filter Connection (Output) - Antialias filter connection for ADC inputs.                                                                                                                                                                            |  |  |  |

| AINL<br>AINR                 | 19<br>20                                                                                                       | <b>Analog Input</b> ( <i>Input</i> ) - The full-scale input level is specified in the ADC Analog Characteristics specification table.                                                                                                                         |  |  |  |

| OCREF                        | 21                                                                                                             | Over Current Reference Setting (Input) - Sets the reference for over current detection.                                                                                                                                                                       |  |  |  |

| PGND                         | 22,23<br>27,28<br>33,34<br>37,38                                                                               | <b>F Ground</b> ( <i>Input</i> ) - Ground for the individual output power half-bridge devices.                                                                                                                                                                |  |  |  |

| RAMP_CAP                     | 24                                                                                                             | <b>Output Ramp Capacitor</b> ( <i>Input</i> ) - Used by the PWM Popguard Transient Control to suppress th initial pop in half-bridge-configured outputs.                                                                                                      |  |  |  |

| VP                           | 25,30,<br>31,36                                                                                                | High Voltage Power (Input) - High voltage power supply for the individual half-bridge devices                                                                                                                                                                 |  |  |  |

| OUT4<br>OUT3<br>OUT2<br>OUT1 | 26<br>29<br>32<br>35                                                                                           | <b>PWM Output</b> ( <i>Output</i> ) - Amplified PWM power outputs.                                                                                                                                                                                            |  |  |  |

| PWM_SIG2<br>PWM_SIG1         | 39<br>40                                                                                                       | Logic Level PWM Output (Output) - Logic Level PWM switching signals.                                                                                                                                                                                          |  |  |  |

| DLY_SDOUT                    | 41                                                                                                             | Delay Serial Audio Data Out (Output) - Output for two's complement serial audio data.                                                                                                                                                                         |  |  |  |

| DLY_SDIN/<br>EX_TWR          | 42                                                                                                             | <b>Delay Serial Audio Data Input</b> ( <i>Input</i> ) - Input for two's complement serial audio data.<br><b>External Thermal Warning</b> ( <i>Input</i> ) - Input for an external thermal warning signal. Configurable via the I <sup>2</sup> C control port. |  |  |  |

| AUX_SDOUT                    | 43 <b>Auxiliary Port Serial Audio Data Out</b> ( <i>Output</i> ) - Output for two's complement auxiliary data. |                                                                                                                                                                                                                                                               |  |  |  |

| AUX_SCLK                     | 44                                                                                                             | Auxiliary Port Serial Clock (Output) - Serial clock for the auxiliary port serial interface.                                                                                                                                                                  |  |  |  |

| AUX_LRCK/<br>AD0             | 45                                                                                                             | Auxiliary Port Left Right Clock ( <i>Output</i> ) - Determines which channel, Left or Right, is currently active on the serial audio data line.<br>AD0 ( <i>Input</i> ) - Sets the LSB of the I <sup>2</sup> C device address. Sensed on the release of RST.  |  |  |  |

| SYS_CLK                      | 46                                                                                                             | <b>System Clock</b> ( <i>Input/Output</i> ) -Clock source for the internal logic, processing, and modulators. This pin should be connected to through a $10k\Omega$ to ground when unused.                                                                    |  |  |  |

| ХТО                          | 47                                                                                                             | Crystal Oscillator Output (Output) - Crystal oscillator driver output.                                                                                                                                                                                        |  |  |  |

| XTI                          | 48                                                                                                             | Crystal Oscillator Input (Input) - Crystal oscillator driver input.                                                                                                                                                                                           |  |  |  |

| Thermal Pad                  | -                                                                                                              | <b>Thermal Pad</b> - Thermal relief pad for optimized heat dissipation. See "QFN Thermal Pad" on page 65 for more information.                                                                                                                                |  |  |  |

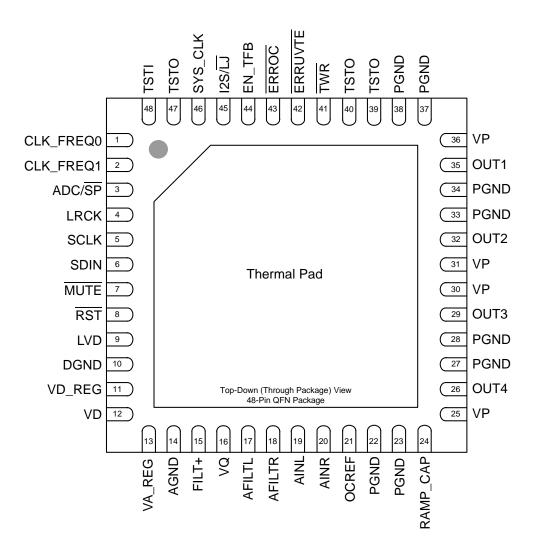

| Pin Name               | Pin #  | Pin Description                                                                                                                                                                     |  |  |  |

|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CLK_FREQ0<br>CLK_FREQ1 | 1<br>2 | <b>Clock Frequency</b> ( <i>Input</i> ) - Determines the frequency of the clock expected to be driven into the SYS_CLK pin. CLK_FREQ1 must be connected to DGND.                    |  |  |  |

| ADC/SP                 | 3      | <b>ADC/Serial Port</b> <i>(Input)</i> - Selects between the Analog to Digital Converter and the Serial Port for audio input. Selects the ADC when high or the serial port when low. |  |  |  |

| LRCK                   | 4      | Left Right Clock ( <i>Input</i> ) - Determines which channel, Left or Right, is currently active on the serial audio data line.                                                     |  |  |  |

| SCLK                   | 5      | al Clock (Input) - Serial bit clock for the serial audio interface.                                                                                                                 |  |  |  |

| SDIN                   | 6      | Serial Audio Data Input (Input) - Input for two's complement serial audio data.                                                                                                     |  |  |  |

| MUTE                   | 7      | <b>Mute</b> ( <i>Input</i> ) - The PWM outputs will output silence as a 50% duty cycle signal when this pin is driven low.                                                          |  |  |  |

| RST                    | 8      | <b>Reset</b> ( <i>Input</i> ) - The device enters a low power mode and all internal registers are reset to their default settings when this pin is driven low.                      |  |  |  |

##

| LVD                          | 9                                | <b>VD Voltage Level Indicator</b> ( <i>Input</i> ) - Identifies the voltage level attached to VD. When applying 5.0 V to VD, LVD must be connected to VD. When applying 2.5 V or 3.3 V to VD, LVD must be connected to DGND. |  |  |  |

|------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DGND                         | 10                               | Digital Ground (Input) - Ground for the internal logic and I/O.                                                                                                                                                              |  |  |  |

| VD_REG                       | 11                               | Core Logic Power (Output) - Internally generated low voltage power supply for digital logic.                                                                                                                                 |  |  |  |

| VD                           | 12                               | <b>Digital Power</b> ( <i>Input</i> ) - Positive power supply for the internal regulators and digital I/O.                                                                                                                   |  |  |  |

| VA_REG                       | 13                               | Analog Power (Output) - Internally generated positive power for the analog section and I/O.                                                                                                                                  |  |  |  |

| AGND                         | 14                               | Analog Ground (Input) - Ground reference for the internal analog section and I/O.                                                                                                                                            |  |  |  |

| FILT+                        | 15                               | <b>Positive Voltage Reference</b> ( <i>Output</i> ) - Positive reference voltage for the internal ADC sampling sircuits.                                                                                                     |  |  |  |

| VQ                           | 16                               | Common Mode Voltage (Output) - Filter connection for internal common mode voltage.                                                                                                                                           |  |  |  |

| AFILTL<br>AFILTR             | 17<br>18                         | Antialias Filter Connection ( <i>Output</i> ) - Antialias filter connection for ADC inputs.                                                                                                                                  |  |  |  |

| AINL<br>AINR                 | 19<br>20                         | <b>Analog Input</b> ( <i>Input</i> ) - The full-scale input level is specified in the ADC Analog Characteristics specification table.                                                                                        |  |  |  |

| OCREF                        | 21                               | Over Current Reference Setting (Input) - Sets the reference for over current detection.                                                                                                                                      |  |  |  |

| PGND                         | 22,23<br>27,28<br>33,34<br>37,38 | <b>Power Ground</b> ( <i>Input</i> ) - Ground for the individual output power half-bridge devices.                                                                                                                           |  |  |  |

| RAMP_CAP                     | 24                               | Output Ramp Capacitor (Input) - This pin should be connected directly to VP in hardware n                                                                                                                                    |  |  |  |

| VP                           | 25,30,<br>31,36                  | High Voltage Power (Input) - High voltage power supply for the individual half-bridge devices.                                                                                                                               |  |  |  |

| OUT4<br>OUT3<br>OUT2<br>OUT1 | 26<br>29<br>32<br>35             | <b>PWM Output</b> ( <i>Output</i> ) - Amplified PWM power outputs.                                                                                                                                                           |  |  |  |

| TSTO                         | 39<br>40                         | <b>Test Output</b> ( <i>Output</i> ) - These pins are outputs used for the Logic Level PWM switching signals available only in software mode. They must be left unconnected for hardware mode operation.                     |  |  |  |

| TWR                          | 41                               | Thermal Warning Output (Output) - Thermal warning output.                                                                                                                                                                    |  |  |  |

| ERRUVTE                      | 42                               | <b>Thermal and Undervoltage Error Output</b> ( <i>Output</i> ) - Error flag for thermal shutdown and undervoltage.                                                                                                           |  |  |  |

| ERROC                        | 43                               | Overcurrent Error Output (Output) - Overcurrent error flag.                                                                                                                                                                  |  |  |  |

| EN_TFB                       | 44                               | Enable Thermal Feedback (Input) - Enables the thermal foldback feature when high.                                                                                                                                            |  |  |  |

| I2S/LJ                       | 45                               | <b>I<sup>2</sup>S/Left Justified</b> ( <i>Input</i> ) - Selects between I <sup>2</sup> S and Left-Justified data format for the serial input port. Selects I <sup>2</sup> S when high and LJ when low.                       |  |  |  |

| SYS_CLK                      | 46                               | System Clock (Input/Output) -Clock source for the delta-sigma modulators.                                                                                                                                                    |  |  |  |

| TSTO                         | 47                               | <b>Test Output</b> ( <i>Output</i> ) - This pin is an output used for the crystal oscillator driver available only in software mode. It must be left unconnected for normal hardware mode operation.                         |  |  |  |

| TSTI                         | 48                               | <b>Test Input</b> ( <i>Input</i> ) - This pin is an input used for the crystal oscillator driver available only in software mode. It must be tied to digital ground for normal hardware mode operation.                      |  |  |  |

| Thermal Pad                  | -                                | <b>hermal Pad</b> - Thermal relief pad for optimized heat dissipation. See "QFN Thermal Pad" on uge 65 for more information.                                                                                                 |  |  |  |

### 2.1 Digital I/O Pin Characteristics

The logic level for each input is set by its corresponding power supply and should not exceed the maximum ratings.

| Power     | Pin    | Pin Name     | I/O          | Driver                    | Receiver                     |

|-----------|--------|--------------|--------------|---------------------------|------------------------------|

| 11.7      | Number |              |              |                           |                              |

| Software  | Mode   |              |              |                           |                              |

| VD        | 1      | INT          | Output       | 2.5 V-5.0 V, Open Drain   |                              |

|           | 2      | SCL          | Input        | -                         | 2.5 V-5.0 V, with Hysteresis |

|           | 3      | SDA          | Input/Output | 2.5 V-5.0 V, Open Drain   | 2.5 V-5.0 V, with Hysteresis |

|           | 7      | HP_DETECT    | Input        | -                         | 2.5 V-5.0 V                  |

|           |        | MUTE         | Input        | -                         | 2.5 V-5.0 V                  |

|           | 41     | DLY_SDOUT    | Output       | 2.5 V-5.0 V, CMOS         | -                            |

|           | 42     | DLY_SDIN     | Input        | -                         | 2.5 V-5.0 V                  |

|           |        | EX_TWR       | Input        | -                         | 2.5 V-5.0 V                  |

|           | 43     | AUX_SDOUT    | Output       | 2.5 V-5.0 V, CMOS         | -                            |

|           | 44     | AUX_SCLK     | Output       | 2.5 V-5.0 V, CMOS         | -                            |

|           | 45     | AUX_LRCK     | Output       | 2.5 V-5.0 V, CMOS         | -                            |

| VD_REG    | 39     | PWM_SIG2     | Output       | 2.5 V, CMOS               | -                            |

|           | 40     | PWM_SIG1     | Output       | 2.5 V, CMOS               | -                            |

| Hardware  | Mode   |              | •            |                           |                              |

| VD        | 1      | CLK_FREQ0    | Input        | _                         | 2.5 V-5.0 V                  |

|           | 2      | CLK_FREQ1    | Input        | -                         | 2.5 V-5.0 V                  |

|           | 3      | ADC/SP       | Input        | -                         | 2.5 V-5.0 V                  |

|           | 7      | MUTE         | Input        | -                         | 2.5 V-5.0 V                  |

|           | 41     | TWR          | Output       | 2.5 V-5.0 V, Open Drain   | -                            |

|           | 42     | ERRUVTE      | Output       | 2.5 V-5.0 V, Open Drain   | -                            |

|           | 43     | ERROC        | Output       | 2.5 V-5.0 V, Open Drain   | -                            |

|           | 44     | EN_TFB       | Input        | -                         | 2.5 V-5.0 V                  |

|           | 45     | <br>I²S/LJ   | Input        | -                         | 2.5 V-5.0 V                  |

| All Modes |        |              |              |                           |                              |

| VD        | 4      | LRCK         | Input        | -                         | 2.5 V-5.0 V                  |

|           | 5      | SCLK         | Input        | -                         | 2.5 V-5.0 V                  |

|           | 6      | SDIN         | Input        | -                         | 2.5 V-5.0 V                  |

|           | 8      | RST          | Input        | -                         | 2.5 V-5.0 V                  |

|           | 9      | LVD          | Input        |                           | 2.5 V-5.0 V                  |

|           | 46     | SYS_CLK      | Input/Output | 2.5 V-5.0 V, CMOS         | 2.5 V-5.0 V                  |

| VP        | 26     | OUT4         | Output       | 8.0 V-18.0 V Power MOSFET | -                            |

| VI        | 20     | OUT3         | Output       | 8.0 V-18.0 V Power MOSFET |                              |

|           | 32     | OUT2         | Output       | 8.0 V-18.0 V Power MOSFET |                              |

| -         | 35     | OUT2<br>OUT1 | Output       | 8.0 V-18.0 V Power MOSFET |                              |

Table 1. I/O Power Rails

CS4525

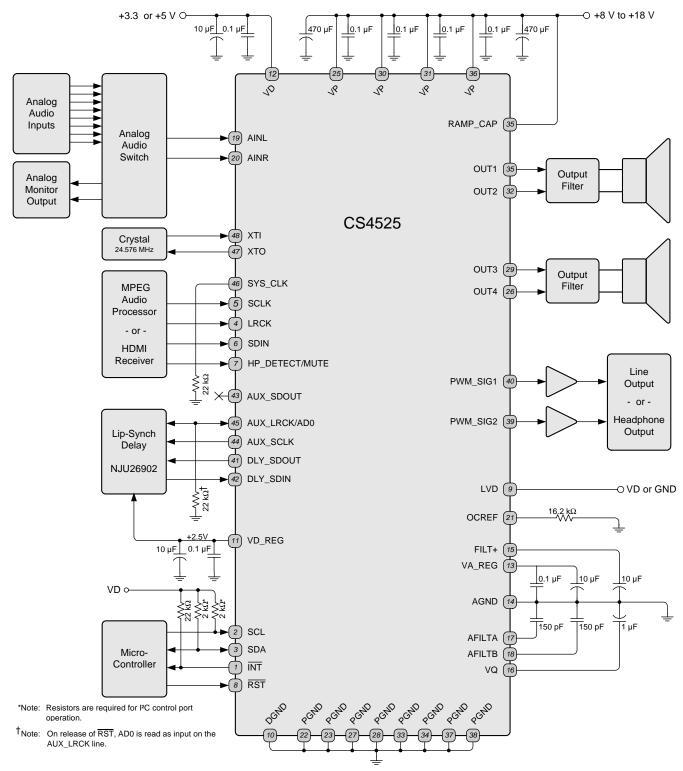

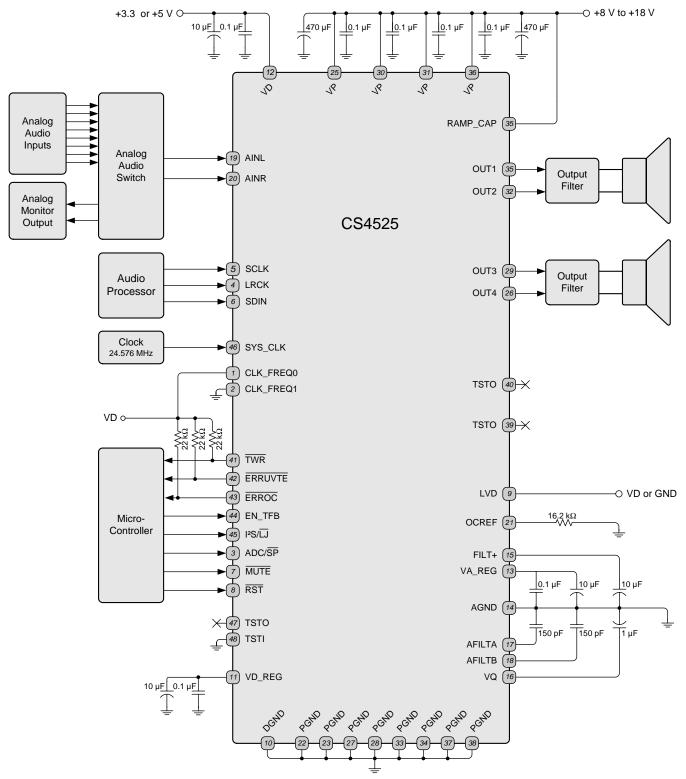

## 3. TYPICAL CONNECTION DIAGRAMS

Figure 1. Typical Connection Diagram - Software Mode

Figure 2. Typical Connection Diagram - Hardware Mode

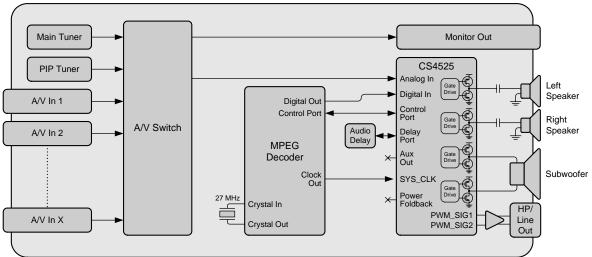

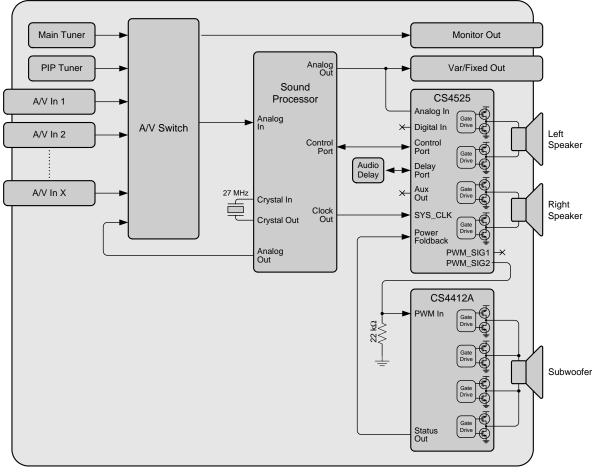

## 4. TYPICAL SYSTEM CONFIGURATION DIAGRAMS

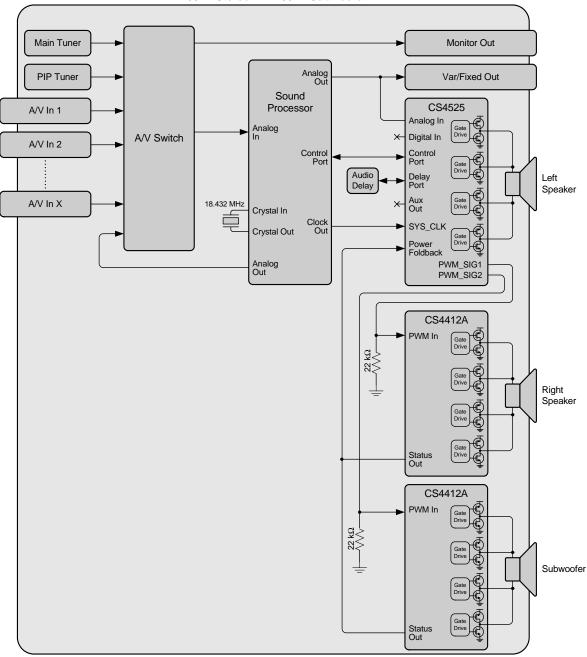

2 x 7 W Stereo + 1 x 15 W Subwoofer

Figure 3. Typical System Configuration 1

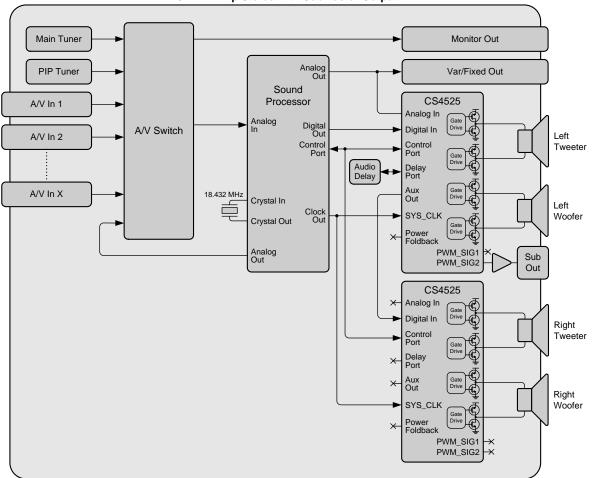

2 x 15 W Stereo + 1 x 30 W Subwoofer

2 x 30 W Stereo + 1 x 30 W Subwoofer

Figure 5. Typical System Configuration 3

2 x 15 W Bi-Amp Stereo with Subwoofer Output

Figure 6. Typical System Configuration 4

## 5. CHARACTERISTICS AND SPECIFICATIONS

## **RECOMMENDED OPERATING CONDITIONS**

AGND = DGND = PGND = 0 V; all voltages with respect to ground.

| Parameters                       | Symbol         | Min   | Nom | Max   | Units |

|----------------------------------|----------------|-------|-----|-------|-------|

| DC Power Supply                  |                |       |     |       |       |

| Digital and Analog Core (Note 1) | VD             | 2.375 | 2.5 | 2.625 | V     |

|                                  | VD             | 3.135 | 3.3 | 3.465 | V     |

|                                  | VD             | 4.75  | 5.0 | 5.25  | V     |

| Amplifier Outputs                | VP             | 8.0   | -   | 18.0  | V     |

| Temperature                      |                |       |     |       |       |

| Ambient Temperature              | T <sub>A</sub> | 0     | -   | +70   | °C    |

| Junction Temperature             | Т <sub>Ј</sub> | 0     | -   | +125  | °C    |

**Notes:** 1. For VD = 2.5 V, VA\_REG and VD\_REG must be connected to VD. See section 6.7 on page 63 for details.

## **ABSOLUTE MAXIMUM RATINGS**

AGND = DGND = PGND = 0 V; all voltages with respect to ground.

| Parameters                |                                  | Symbol           | Min        | Max          | Units |

|---------------------------|----------------------------------|------------------|------------|--------------|-------|

| DC Power Supply           |                                  |                  |            |              |       |

| Power Stage               | Outputs Switching and Under Load | VP               | -0.3       | 19.8         | V     |

| Power Stage               | No Output Switching              | VP               | -0.3       | 23.0         | V     |

| Digital and Analog Core   |                                  | VD               | -0.3       | 6.0          | V     |

| Inputs                    |                                  |                  | •          |              |       |

| Input Current             | (Note 2)                         | l <sub>in</sub>  | -          | ±10          | mA    |

| Analog Input Voltage      | (Note 3)                         | V <sub>INA</sub> | AGND - 0.7 | VA_REG + 0.7 | V     |

| Digital Input Voltage     | (Note 3)                         | V <sub>IND</sub> | -0.3       | VD + 0.4     | V     |

| Temperature               |                                  |                  |            |              |       |

| Ambient Operating Tempera | ature - Power Applied            |                  |            |              |       |

|                           | Commercial                       | T <sub>A</sub>   | -20        | +85          | °C    |

| Storage Temperature       |                                  | T <sub>stg</sub> | -65        | +150         | °C    |

**WARNING:** Operation at conditions beyond the Recommended Operating Conditions may affect device reliability, and functional operation beyond Recommended Operating Conditions is not implied.

- **Notes:** 2. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCR latch-up.

- 3. The maximum over/under voltage is limited by the input current.

## **ANALOG INPUT CHARACTERISTICS**

Test Conditions (unless otherwise specified): AGND = DGND = PGND = 0 V; All voltages with respect to ground;  $T_A = 25^{\circ}C$ ; VD = 3.3 V; Input Signal: 1 kHz sine wave through the recommended passive input filter shown in Figure 28 on page 61; Capacitor values connected to AFILTA, AFILTB, FILT+, VQ, VD\_REG, and VA\_REG as shown in Figure 1 on page 13; Sample Frequency = 48 kHz; 10 Hz to 20 kHz Measurement Bandwidth; Power outputs in power-down state (PDnOut1 = 1, PDnOut2 = 1, PDnOut3/4 = 1).

| Parameter                         |                    | Min      | Тур      | Max      | Unit   |

|-----------------------------------|--------------------|----------|----------|----------|--------|

| Dynamic Range (Note 4)            | A-weighted         | 90       | 95       | -        | dB     |

|                                   | unweighted         | 87       | 92       | -        | dB     |

| Total Harmonic Distortion + Noise | -1 dB              | -        | -86      | -77      | dB     |

|                                   | -20 dB             | -        | -72      | -        | dB     |

|                                   | -60 dB             | -        | -32      | -        | dB     |

| DC Accuracy                       |                    |          |          |          |        |

| Interchannel Gain Mismatch        |                    | -        | 0.05     | -        | dB     |

| Gain Drift                        |                    | -        | ±100     | -        | ppm/°C |

| Interchannel Isolation            |                    | -        | 90       | -        | dB     |

| Full-scale Input Voltage          | VD = 2.5V (Note 5) | 0.786*VD | 0.827*VD | 0.868*VD | Vpp    |

|                                   | VD = 3.3V          | 0.590*VD | 0.621*VD | 0.652*VD | Vpp    |

|                                   | VD = 5.0V          | 0.398*VD | 0.419*VD | 0.440*VD | Vpp    |

| Input Impedance                   | (Note 6)           | 40       | -        | -        | kΩ     |

**Notes:** 4. Referred to the typical full-scale voltage

- 5. For VD = 2.5 V, VA\_REG and VD\_REG must be connected to VD. See section 6.7 on page 63 for details.

- 6. Measured between AINx and AGND.

## ADC DIGITAL FILTER CHARACTERISTICS

| 0.4948<br>0<br>- | dB                  |

|------------------|---------------------|

|                  |                     |

| -                |                     |

|                  | Fs                  |

| -                | dB                  |

| Fs -             | s                   |

|                  |                     |

| 7 -              | Hz                  |

| 2 -              | Hz                  |

| ) -              | Deg                 |

| 0.17             | dB                  |

| Fs -             | S                   |

|                  | .2 -<br>) -<br>0.17 |

Notes: 7. Filter response is clock dependent and scales with the ADC sampling frequency (Fs). With a 27.000 MHz or 24.576 MHz XTAL/SYS\_CLK, Fs is equal to the applied clock divided by 512. With an 18.432 MHz XTAL/SYS\_CLK, Fs is equal to the applied clock divided by 384.

## **PWM POWER OUTPUT CHARACTERISTICS**

Test Conditions (unless otherwise specified): AGND = DGND = PGND = 0 V; All voltages with respect to ground;  $T_A = 25^{\circ}C$ ; VD = 3.3 V; VP = 18 V;  $R_L = 8 \Omega$  for full-bridge,  $R_L = 4 \Omega$  for half-bridge and parallel full-bridge; OutputDly[3:0] = 1111; PhaseShift = 1 for half-bridge, PhaseShift = 0 for full-bridge and parallel full-bridge; Input Signal: full-scale 997 Hz sine wave through serial audio input port, 48 kHz sample rate; Capacitor values connected to AFILTA, AFILTB, FILT+, VQ, VD\_REG, and VA\_REG as shown in Figure 1 on page 13; PWM Switch Rate = 384 kHz; 10 Hz to 20 kHz Measurement Bandwidth; Performance measurements taken through AES17 filter.

| Parameters                                   | Symbol              | Conditions                                                                     | Min | Тур          | Max | Units    |

|----------------------------------------------|---------------------|--------------------------------------------------------------------------------|-----|--------------|-----|----------|

| Power Output per Channel                     |                     | THD+N < 10%                                                                    | _   | 15           | _   | W        |

| Stereo Full-Bridge                           |                     | THD+N < 1%                                                                     | -   | 12           | -   | Ŵ        |

| Half-Bridge                                  | Po                  | THD+N < 10%                                                                    | -   | 7            | -   | W        |

| Tail-bluge                                   |                     | THD+N < 1%                                                                     | -   | 5.5          | -   | W        |

| Parallel Full-Bridge                         |                     | THD+N < 10%<br>THD+N < 1%                                                      | -   | 30<br>23.5   | -   | W<br>W   |

| Total Harmonic Distortion + Noise            |                     |                                                                                |     |              |     |          |

| Stereo Full-Bridge                           |                     | $P_0 = 1 W$                                                                    | -   | 0.05         | -   | %        |

|                                              | THD+N               | $P_O = 0 \text{ dBFS} = 11.3 \text{ W}$<br>$P_O = 1 \text{ W}$                 | -   | 0.10<br>0.12 | -   | %<br>%   |

| Half-Bridge                                  |                     | $P_0 = 1 \text{ W}$<br>$P_0 = 0 \text{ dBFS} = 5.0 \text{ W}$                  | -   | 0.12         | -   | %        |

|                                              |                     | $P_0 = 1 W$                                                                    | -   | 0.1          | -   | %        |

| Parallel Full-Bridge                         |                     | P <sub>O</sub> = 0 dBFS = 22.6 W                                               | -   | 0.3          | -   | %        |

| Dynamic Range                                |                     |                                                                                |     |              |     |          |

| Stereo Full-Bridge                           |                     | $P_0 = -60 \text{ dBFS}$ , A-Weighted                                          | -   | 102          | -   | dB       |

|                                              | DYR                 | $P_O = -60 \text{ dBFS}$ , Unweighted<br>$P_O = -60 \text{ dBFS}$ , A-Weighted | -   | 99<br>99     | -   | dB<br>dB |

| Half-Bridge                                  | DIK                 | $P_0 = -60 \text{ dBFS}$ , Unweighted                                          | -   | 99<br>96     | -   | dB       |

|                                              |                     | $P_{O} = -60 \text{ dBFS}, \text{ A-Weighted}$                                 | -   | 102          | -   | dB       |

| Parallel Full-Bridge                         |                     | $P_0 = -60 \text{ dBFS}$ , Unweighted                                          | -   | 99           | -   | dB       |

| MOSFET On Resistance                         | R <sub>DS(ON)</sub> | $I_d = 0.5 \text{ A}, T_J = 50^{\circ}\text{C}$                                | -   | 280          | -   | mΩ       |

| Efficiency                                   | h                   | $P_0 = 2 \times 15 \text{ W}, \text{ R}_L = 8 \Omega$                          | -   | 85           | -   | %        |

| Minimum Output Pulse Width                   | PW <sub>min</sub>   | No Load                                                                        | -   | 50           | -   | ns       |

| Rise Time of OUTx                            | t <sub>r</sub>      | Resistive Load                                                                 | -   | 20           | -   | ns       |

| Fall Time of OUTx                            | t <sub>f</sub>      | Resistive Load                                                                 | -   | 20           | -   | ns       |

| PWM Output Over-Current Error Trigger Point  |                     | $T_A = 25^{\circ}C$ , OCREF = 16.2 k $\Omega$                                  | -   | 2.5          | -   | Α        |

|                                              | I <sub>CE</sub>     | $T_A = 25^{\circ}C$ , OCREF = 18 k $\Omega$                                    | -   | 2.1          | -   | А        |

|                                              |                     | $T_A = 25^{\circ}C$ , OCREF = 22 k $\Omega$                                    | -   | 1.7          | -   | A        |

| Junction Thermal Warning Trigger Point       | T <sub>TW</sub>     |                                                                                | -   | 105          | -   | °C       |

| Junction Thermal Error Trigger Point         | T <sub>TE</sub>     |                                                                                | -   | 125          | -   | °C       |

| VP Under-Voltage Error Falling Trigger Point | V <sub>UVFALL</sub> | $T_A = 25^{\circ}C$                                                            | -   | 4.7          | 4.9 | V        |

| VP Under-Voltage Error Rising Trigger Point  | V <sub>UVRISE</sub> | $T_A = 25^{\circ}C$                                                            | -   | 4.95         | 5.4 | V        |

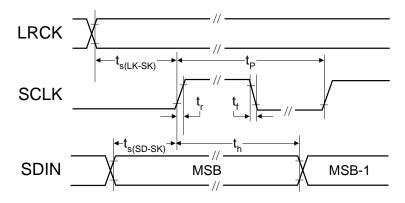

## SERIAL AUDIO INPUT PORT SWITCHING SPECIFICATIONS

AGND = DGND = PGND = 0 V;  $T_A = 25^{\circ}C$ ; VD = 3.3 V; Inputs: Logic 0 = DGND; Logic 1 = VD.

| Parameters                              | Symbol                      | Min                                  | Nominal | Max                 | Units |

|-----------------------------------------|-----------------------------|--------------------------------------|---------|---------------------|-------|

|                                         |                             | 28.5                                 | 32      | 35.2                | kHz   |

| Supported Input Sample Pates            | E                           | 39.5                                 | 44.1    | 52.8                | kHz   |

| Supported Input Sample Rates            | F <sub>SI</sub>             | 39.5                                 | 48      | 52.8                | kHz   |

|                                         |                             | 86.4                                 | 96      | 105.6               | kHz   |

| LRCK Duty Cycle                         |                             | 45                                   | -       | 55                  | %     |

| SCLK Frequency (Note 8                  | ),(Note 9) 1/t <sub>p</sub> | F <sub>SI</sub> *2*N <sub>bits</sub> | -       | F <sub>CLK</sub> /3 | Hz    |

| SCLK Duty Cycle                         |                             | 45                                   | -       | 55                  | %     |

| LRCK Setup Time Before SCLK Rising Edge | t <sub>s(LK-SK)</sub>       | 40                                   | -       | -                   | ns    |

| SDIN Setup Time Before SCLK Rising Edge | t <sub>s(SD-SK)</sub>       | 25                                   | -       | -                   | ns    |

| SDIN Hold Time After SCLK Rising Edge   | t <sub>h</sub>              | 10                                   | -       | -                   | ns    |

| RST pin Low Pulse Width                 | (Note 10)                   | 1                                    | -       | -                   | ms    |

Notes: 8. F<sub>CLK</sub> is the frequency of the crystal connected to the XTI/XTO pins or the input SYS\_CLK signal.

- 9. N<sub>bits</sub> is the number of bits per sample of the serial digital input.

- 10. After powering up the CS4525, RST should be held low until the power supplies and clocks are stable.

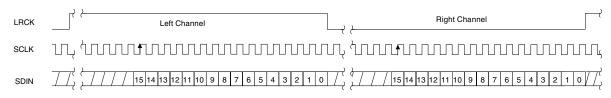

Figure 7. Serial Audio Input Port Timing

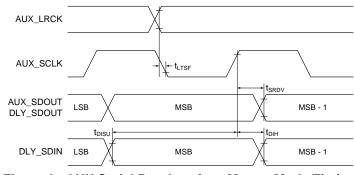

## **AUX SERIAL AUDIO I/O PORT SWITCHING SPECIFICATIONS**

| Pa                      | rameters                                    | Symbol             | Min                                     | Тур                   | Max                                     | Units |

|-------------------------|---------------------------------------------|--------------------|-----------------------------------------|-----------------------|-----------------------------------------|-------|

| Input Source: Analog    | Inputs (Internal ADC)                       |                    |                                         |                       |                                         |       |

| Output Sample Rate      | ClkFreq[1:0] = '00'                         |                    | -                                       | F <sub>CLK</sub> /384 | -                                       | Hz    |

| (Note 16)               | ClkFreq[1:0] = '01'                         | F <sub>SO</sub>    | -                                       | F <sub>CLK</sub> /512 | -                                       | Hz    |

|                         | ClkFreq[1:0] = '10'                         |                    | -                                       | F <sub>CLK</sub> /512 | -                                       | Hz    |

| AUX_LRCK Duty Cycle     |                                             |                    | -                                       | 50                    | -                                       | %     |

| AUX_LRCK Period         |                                             |                    | -                                       | 1/F <sub>SO</sub>     | -                                       | S     |

| AUX_SCLK Frequency      | ClkFreq[1:0] = '00'                         |                    | -                                       | 48*F <sub>SO</sub>    | -                                       | Hz    |

| (Note 16)               | ClkFreq[1:0] = '01'                         | F <sub>SCLKO</sub> | -                                       | 64*F <sub>SO</sub>    | -                                       | Hz    |

|                         | ClkFreq[1:0] = '10'                         |                    | -                                       | 64*F <sub>SO</sub>    | -                                       | Hz    |

| AUX_SCLK Duty Cycle     |                                             |                    | -                                       | 50                    | -                                       | %     |

| AUX_SCLK Period         |                                             |                    | -                                       | 1/F <sub>SCLKO</sub>  | -                                       | S     |

| Input Source: Serial A  | udio Input Port                             |                    |                                         |                       |                                         |       |

| Output Sample Rate      | F <sub>S-In</sub> = 32kHz, 44.1 kHz, 48 kHz | F                  | -                                       | F <sub>SI</sub>       | -                                       | Hz    |

|                         | F <sub>S-In</sub> = 96 kHz                  | F <sub>SO</sub>    | -                                       | F <sub>SI</sub> /2    | -                                       | Hz    |

| AUX_LRCK Duty Cycle     | (Note 13)                                   |                    | 45                                      | -                     | 55                                      | %     |

| AUX_LRCK Period         | (Note 12, 13)                               |                    | T <sub>SI</sub> - T <sub>CLK</sub>      | T <sub>SI</sub>       | T <sub>SI</sub> + T <sub>CLK</sub>      | S     |

| AUX_SCLK Frequency      | F <sub>S-In</sub> = 32kHz, 44.1 kHz, 48 kHz |                    | -                                       | F <sub>SCLKI</sub>    | -                                       | Hz    |

| (Note 14)               | F <sub>S-In</sub> = 96 kHz                  |                    | -                                       | F <sub>SCLKI</sub> /2 | -                                       | Hz    |

| AUX_SCLK Duty Cycle     |                                             |                    | 30                                      | -                     | 70                                      | %     |

| AUX_SCLK Period         | F <sub>S-In</sub> = 32kHz, 44.1 kHz, 48 kHz |                    | T <sub>SCLKI</sub> - T <sub>CLK</sub>   | T <sub>SCLKI</sub>    | T <sub>SCLKI</sub> + T <sub>CLK</sub>   | S     |

| (Note 13, 14)           | F <sub>S-In</sub> = 96 kHz                  |                    | 2*T <sub>SCLKI</sub> - T <sub>CLK</sub> | 2*T <sub>SCLKI</sub>  | 2*T <sub>SCLKI</sub> + T <sub>CLK</sub> | S     |

| Input Source: Analog    | Inputs or Serial Audio Input F              | Port               |                                         |                       |                                         |       |

| AUX_LRCK Rising Edge t  | o AUX_SCLK Falling Edge                     | t <sub>LTSF</sub>  | -                                       | -                     | 20                                      | ns    |

| AUX_SCLK Rising Edge to | o Data Output Valid                         | t <sub>SRDV</sub>  | -                                       | -                     | T <sub>CLK</sub> + 20                   | ns    |

| DLY_SDIN Setup Time Be  | fore AUX_SCLK Rising Edge                   | t <sub>DIS</sub>   | 25                                      | -                     | -                                       | ns    |

| DLY_SDIN Hold Time Afte | r AUX_SCLK Rising Edge                      | t <sub>DIH</sub>   | 10                                      | -                     | -                                       | ns    |

**Notes:** 11.  $F_{CLK}$  is the frequency of the crystal connected to the XTI/XTO pins or the input SYS\_CLK signal. T<sub>CLK</sub> = 1/F<sub>CLK</sub>.

- 12.  $F_{SI}$  is the frequency of the input LRCK signal.  $T_{SI} = 1/F_{SI}$

- 13. May vary during normal operation.

- 14.  $F_{SCLKI}$  is the frequency of the input SCLK signal.  $T_{SCLKI} = 1/F_{SCLKI}$ .

## **XTI SWITCHING SPECIFICATIONS**