# ardware Manua

# R8C/2H Group, R8C/2J Group Hardware Manual

RENESAS MCU R8C FAMILY / R8C/2x SERIES

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Technology Corp. without notice. Please review the latest information published by Renesas Technology Corp. through various means, including the Renesas Technology Corp. website (http://www.renesas.com).

Rev.1.00

Revision Date: Mar 28, 2008

Renesas Technology www.renesas.com

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

#### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

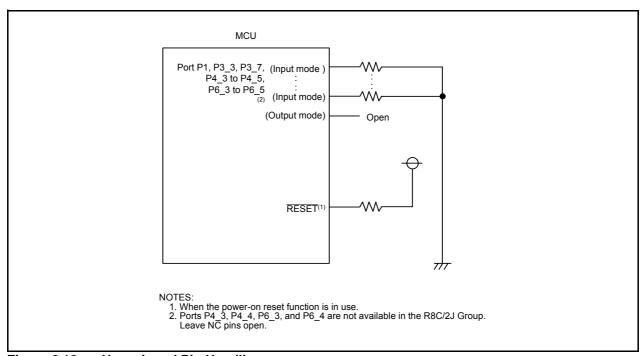

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

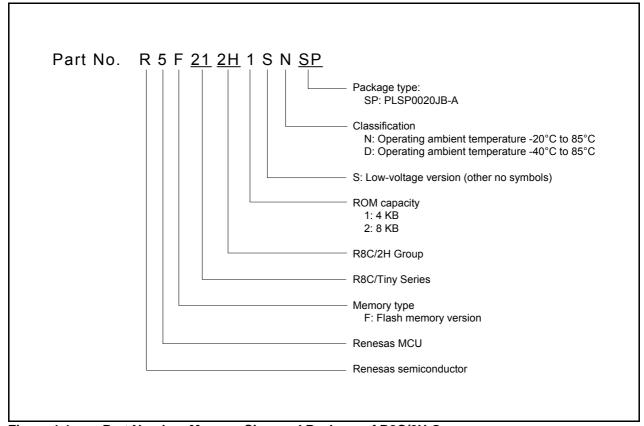

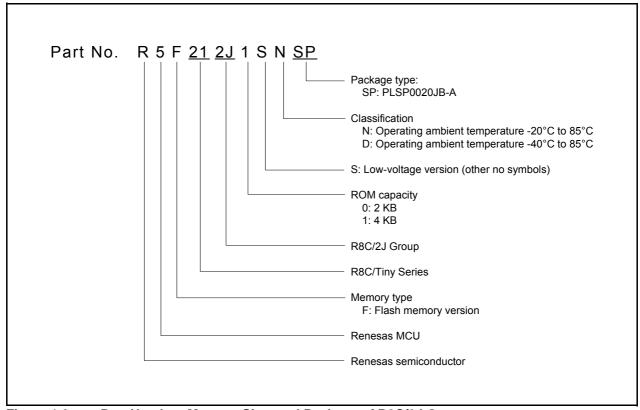

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different part numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different part numbers, implement a system-evaluation test for each of the products.

# How to Use This Manual

# 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual.

The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the R8C/2H Group, R8C/2J Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site.

| Document Type    | Description                                         | Document Title       | Document No.  |

|------------------|-----------------------------------------------------|----------------------|---------------|

| Datasheet        | Hardware overview and electrical characteristics    | R8C/2H Group,        | REJ03B0217    |

|                  |                                                     | R8C/2J Group         |               |

|                  |                                                     | Datasheet            |               |

| Hardware manual  | Hardware specifications (pin assignments,           | R8C/2H Group,        | This hardware |

|                  | memory maps, peripheral function                    | R8C/2J Group         | manual        |

|                  | specifications, electrical characteristics, timing  | Hardware Manual      |               |

|                  | charts) and operation description                   |                      |               |

|                  | Note: Refer to the application notes for details on |                      |               |

|                  | using peripheral functions.                         |                      |               |

| Software manual  | Description of CPU instruction set                  | R8C/Tiny Series      | REJ09B0001    |

|                  |                                                     | Software Manual      |               |

| Application note | Information on using peripheral functions and       | Available from Rene  | esas          |

|                  | application examples                                | Technology Web site. |               |

|                  | Sample programs                                     |                      |               |

|                  | Information on writing programs in assembly         |                      |               |

|                  | language and C                                      |                      |               |

| Renesas          | Product specifications, updates on documents,       |                      |               |

| technical update | etc.                                                |                      |               |

# 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

#### (1) Register Names, Bit Names, and Pin Names

Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories.

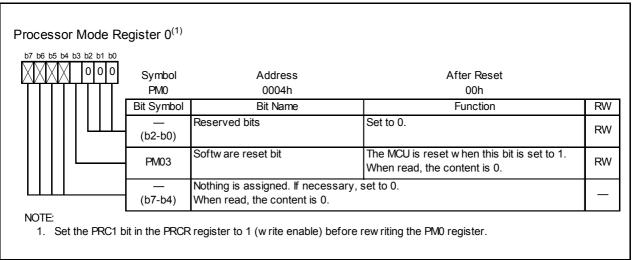

Examples the PM03 bit in the PM0 register

P3\_5 pin, VCC pin

#### (2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h Decimal: 1234

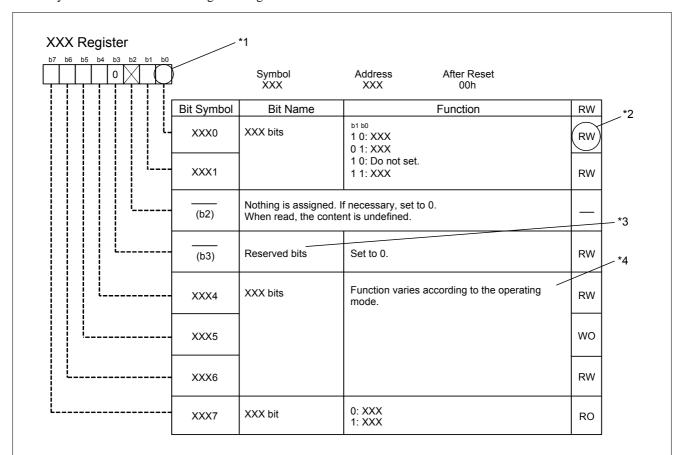

### 3. Register Notation

The symbols and terms used in register diagrams are described below.

\*1

Blank: Set to 0 or 1 according to the application.

0: Set to 0.

1: Set to 1.

X: Nothing is assigned.

\*2

RW: Read and write.

RO: Read only.

WO: Write only.

-: Nothing is assigned.

\*3

• Reserved bit

Reserved bit. Set to specified value.

\*4

• Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

# 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                     |

|--------------|-----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter  |

| bps          | bits per second                               |

| CRC          | Cyclic Redundancy Check                       |

| DMA          | Direct Memory Access                          |

| DMAC         | Direct Memory Access Controller               |

| GSM          | Global System for Mobile Communications       |

| Hi-Z         | High Impedance                                |

| IEBus        | Inter Equipment Bus                           |

| I/O          | Input / Output                                |

| IrDA         | Infrared Data Association                     |

| LSB          | Least Significant Bit                         |

| MSB          | Most Significant Bit                          |

| NC           | Non-Connect                                   |

| PLL          | Phase Locked Loop                             |

| PWM          | Pulse Width Modulation                        |

| SIM          | Subscriber Identity Module                    |

| UART         | Universal Asynchronous Receiver / Transmitter |

| VCO          | Voltage Controlled Oscillator                 |

All trademarks and registered trademarks are the property of their respective owners.

# **Table of Contents**

| SFR Pag | ge Reference                                               | B - 1 |

|---------|------------------------------------------------------------|-------|

| 1. O    | verview                                                    | 1     |

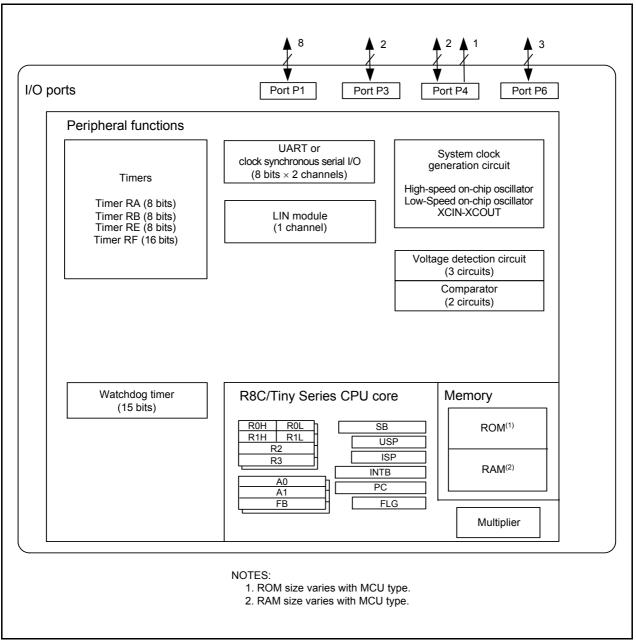

| 1.1     | Features                                                   | 1     |

| 1.1.1   | Applications                                               |       |

| 1.1.2   | Specifications                                             | 1     |

| 1.2     | Product List                                               |       |

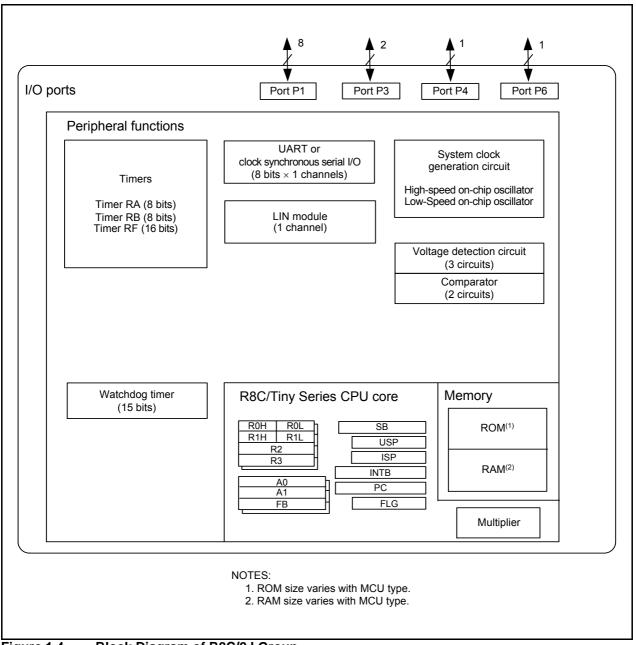

| 1.3     | Block Diagram                                              | 6     |

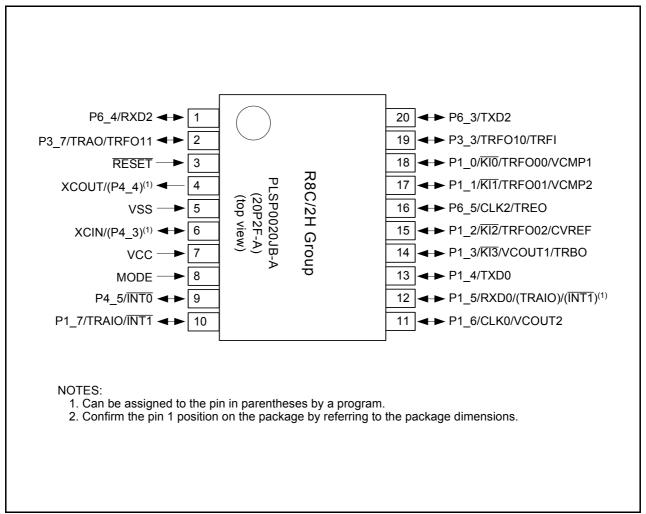

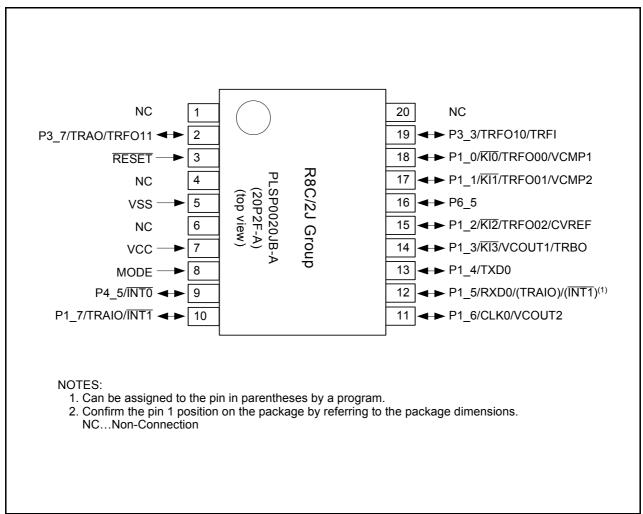

| 1.4     | Pin Assignment                                             | 8     |

| 1.5     | Pin Functions                                              | 12    |

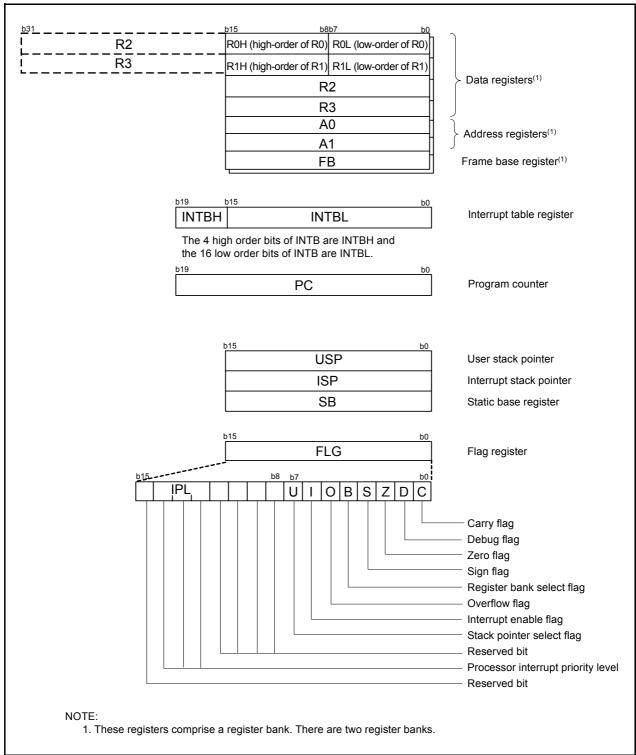

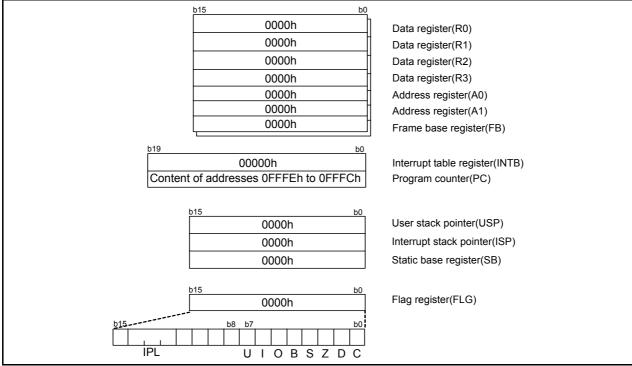

| 2. Ce   | entral Processing Unit (CPU)                               | 14    |

| 2.1     | Data Registers (R0, R1, R2, and R3)                        |       |

| 2.2     | Address Registers (A0 and A1)                              | 15    |

| 2.3     | Frame Base Register (FB)                                   | 15    |

| 2.4     | Interrupt Table Register (INTB)                            |       |

| 2.5     | Program Counter (PC)                                       | 15    |

| 2.6     | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) |       |

| 2.7     | Static Base Register (SB)                                  |       |

| 2.8     | Flag Register (FLG)                                        |       |

| 2.8.1   | Carry Flag (C)                                             |       |

| 2.8.2   | Debug Flag (D)                                             |       |

| 2.8.3   | Zero Flag (Z)                                              |       |

| 2.8.4   | Sign Flag (S)                                              |       |

| 2.8.5   | .6                                                         |       |

| 2.8.6   | Overflow Flag (O)                                          |       |

| 2.8.7   | Interrupt Enable Flag (I)                                  | 16    |

| 2.8.8   | 5 . 7                                                      |       |

| 2.8.9   | 1 , , ,                                                    |       |

| 2.8.1   | 0 Reserved Bit                                             | 16    |

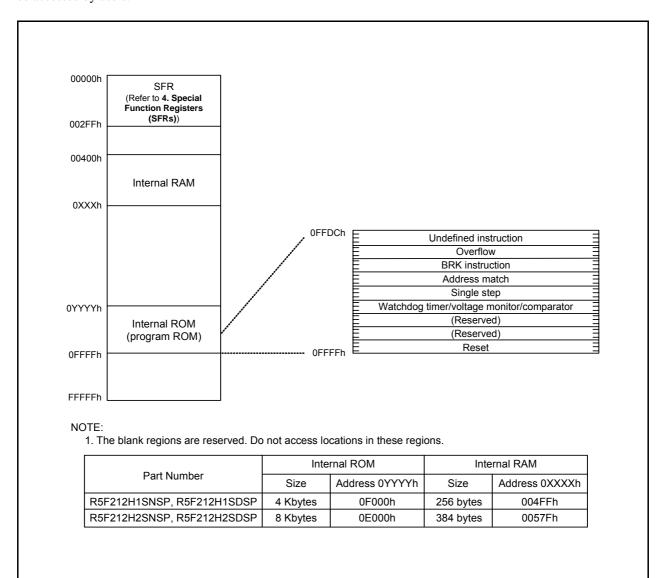

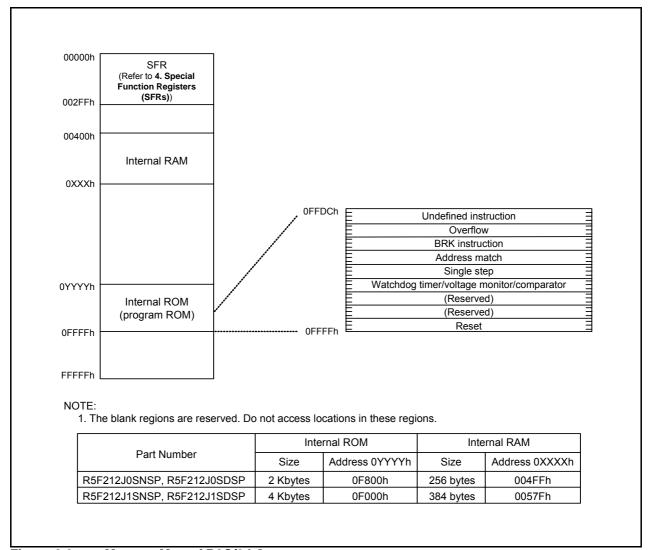

| 3. M    | emory                                                      | 17    |

| 4. Sp   | pecial Function Registers (SFRs)                           | 19    |

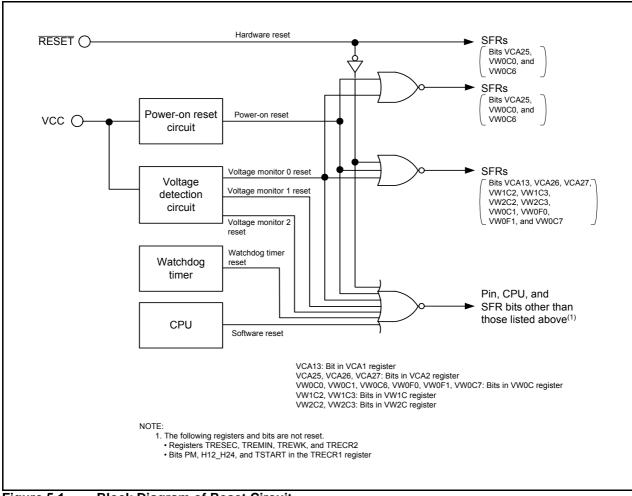

| 5. Re   | esets                                                      | 31    |

| 5.1     | Hardware Reset                                             |       |

| 5.1.1   | When Power Supply is Stable                                |       |

| 5.1.2   | Power On                                                   |       |

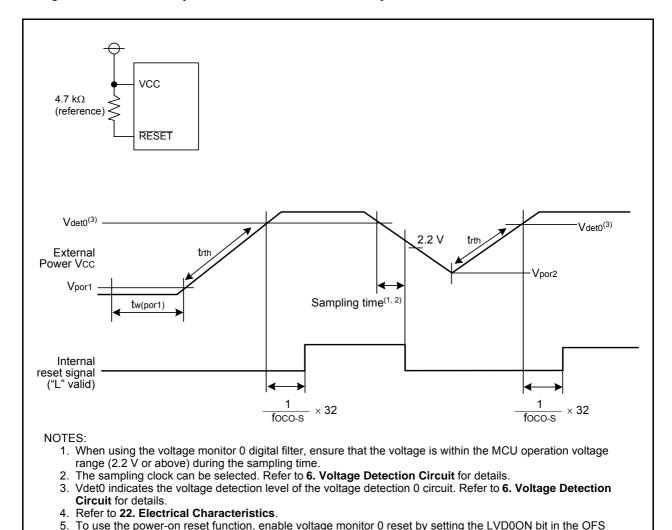

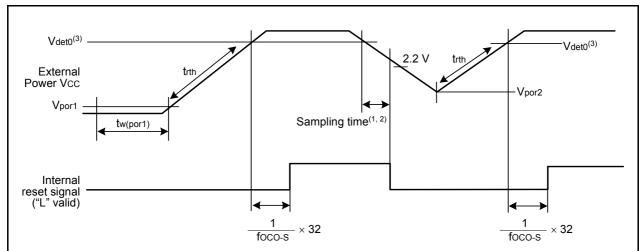

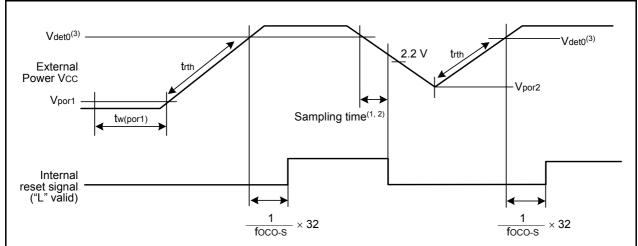

| 5.2     | Power-On Reset Function                                    |       |

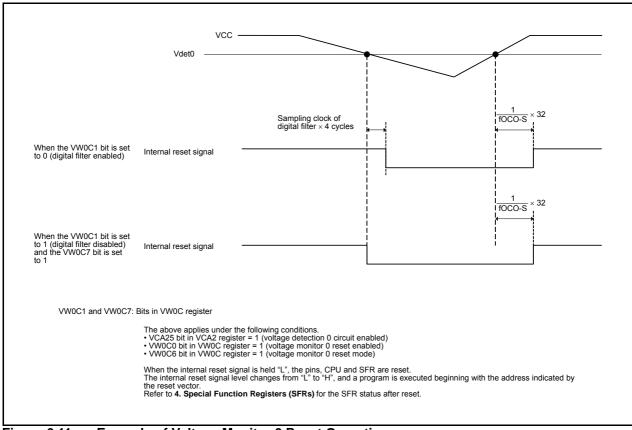

| 5.3     | Voltage Monitor 0 Reset                                    | 37    |

| 5.4     | Voltage Monitor 1 Reset                                    |       |

| 5.5     | Voltage Monitor 2 Reset                                    |       |

| 5.6     | Watchdog Timer Reset                                       |       |

| 5.7     | Software Reset                                             |       |

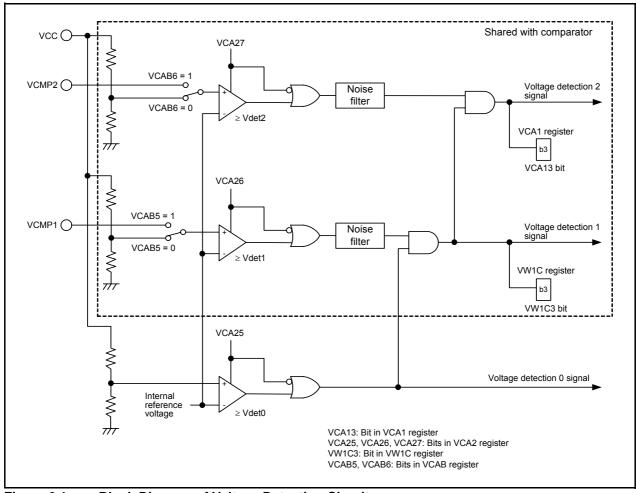

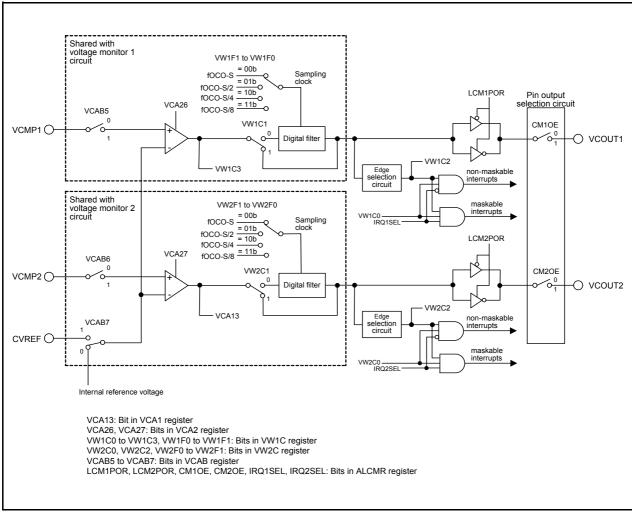

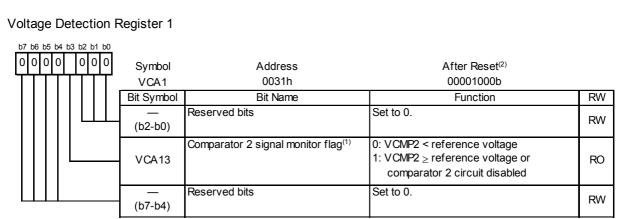

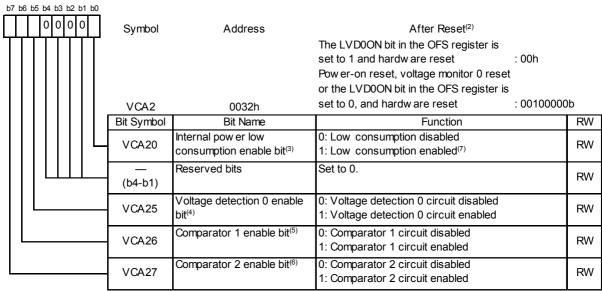

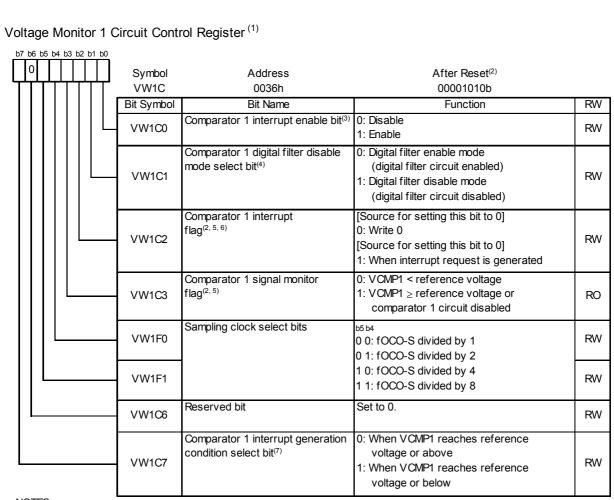

| 6. Vo   | oltage Detection Circuit                                   | 39    |

| 6.1     | VCC Input Voltage                                          | 47    |

| 611     | Monitoring Vdet()                                          | 47    |

| 6.1.2        | Monitoring Vdet1                                        | 47 |

|--------------|---------------------------------------------------------|----|

| 6.1.3        | Monitoring Vdet2                                        | 47 |

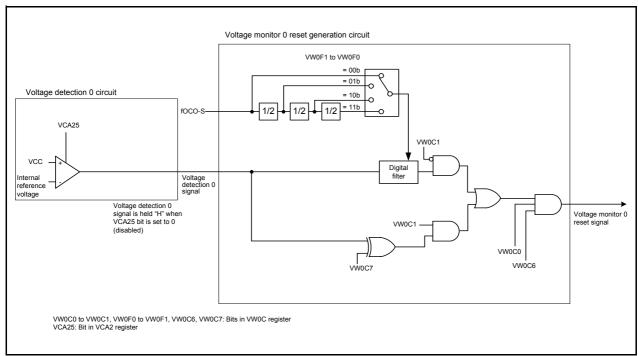

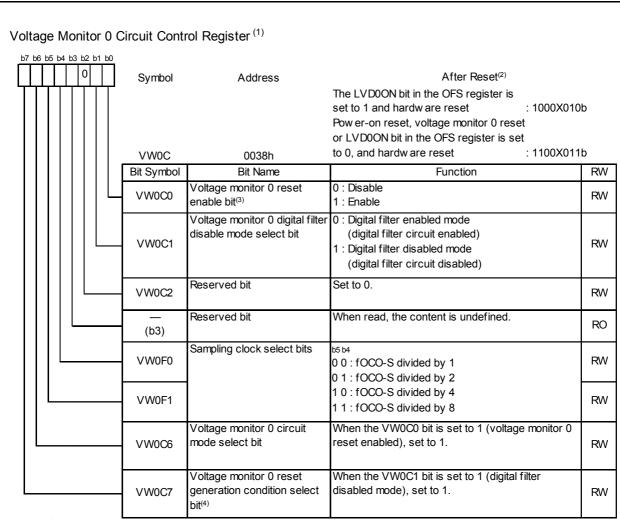

| 6.2          | Voltage Monitor 0 Reset                                 |    |

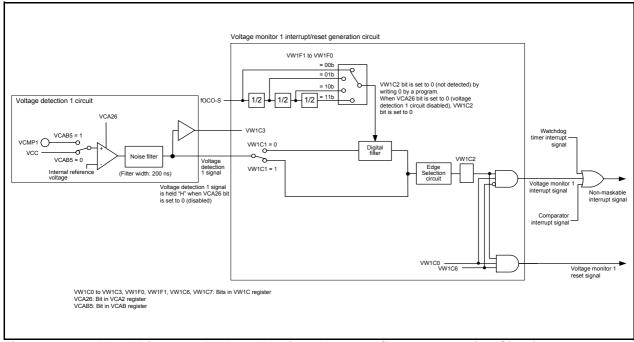

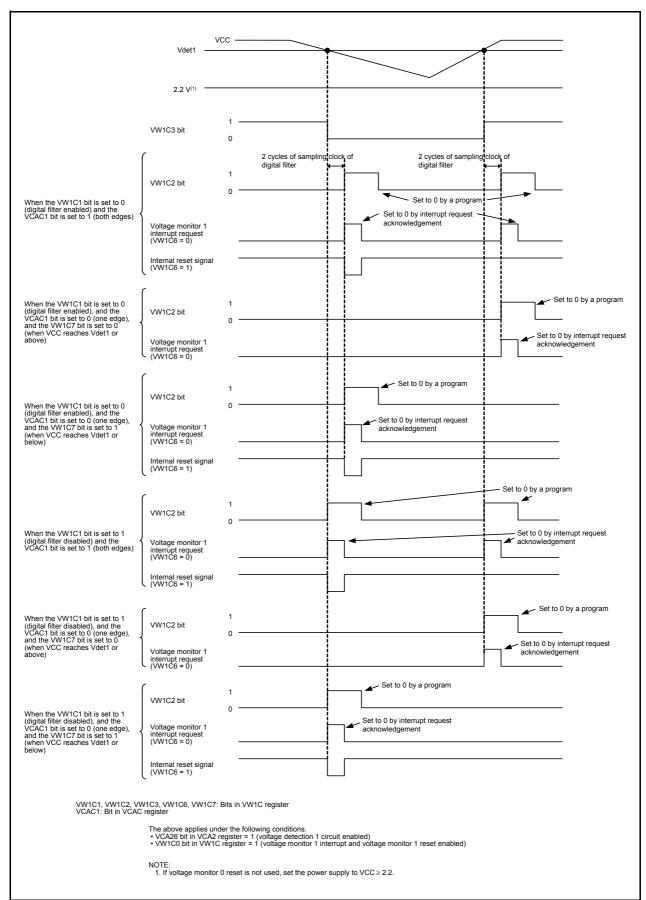

| 6.3          | Voltage Monitor 1 Interrupt and Voltage Monitor 1 Reset |    |

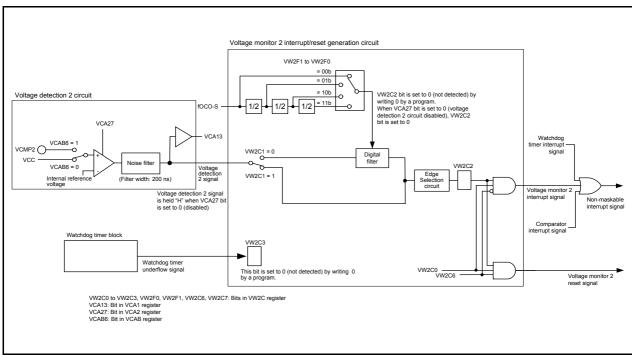

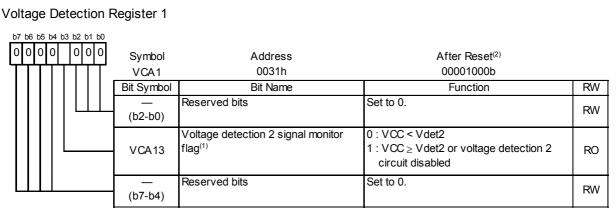

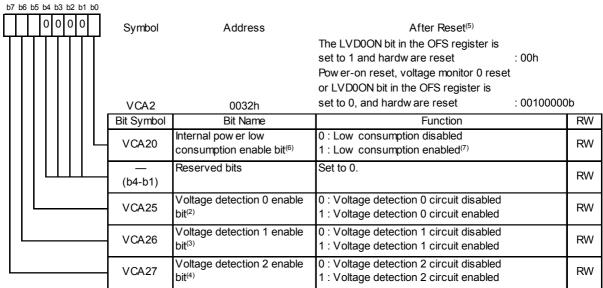

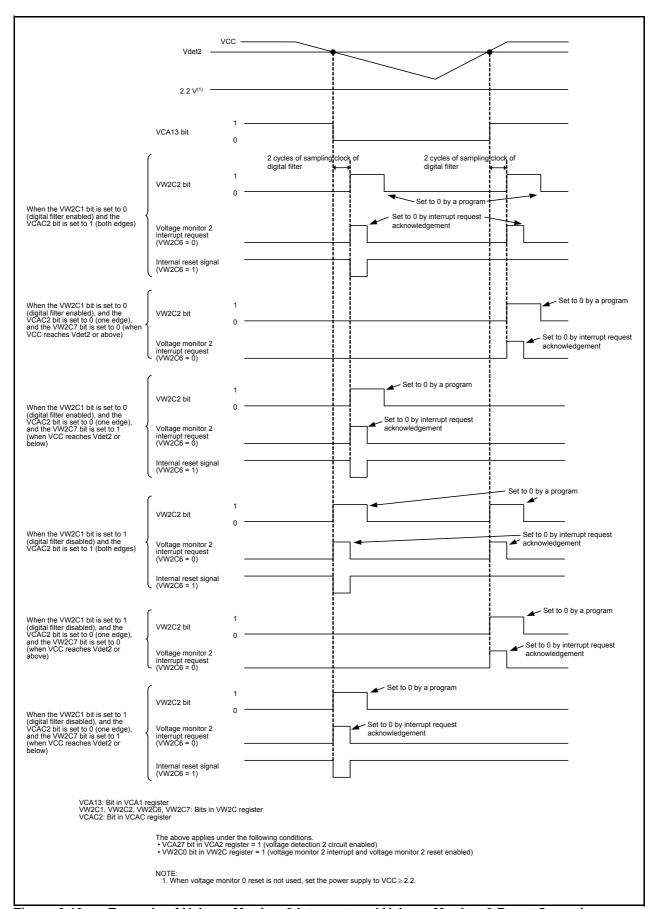

| 6.4          | Voltage Monitor 2 Interrupt and Voltage Monitor 2 Reset | 51 |

| 7. Co        | mparator                                                | 53 |

| 7.1          | Overview                                                |    |

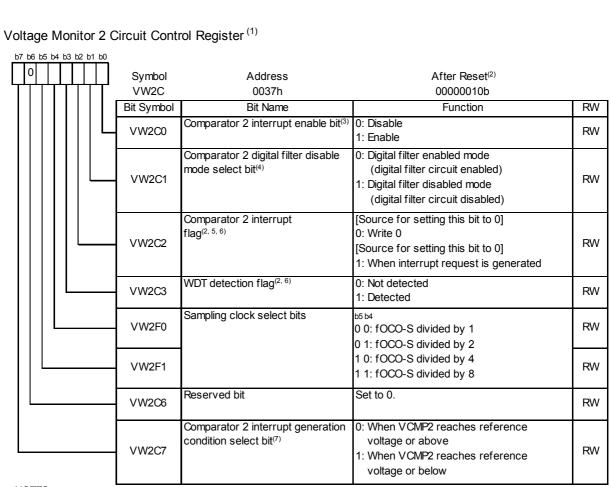

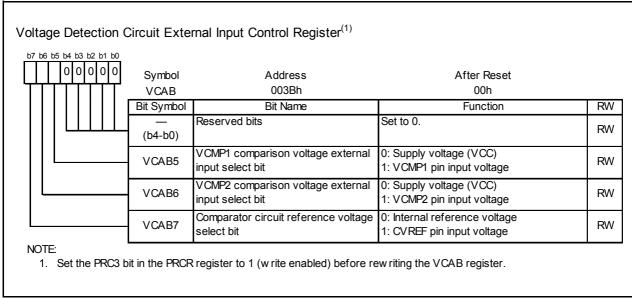

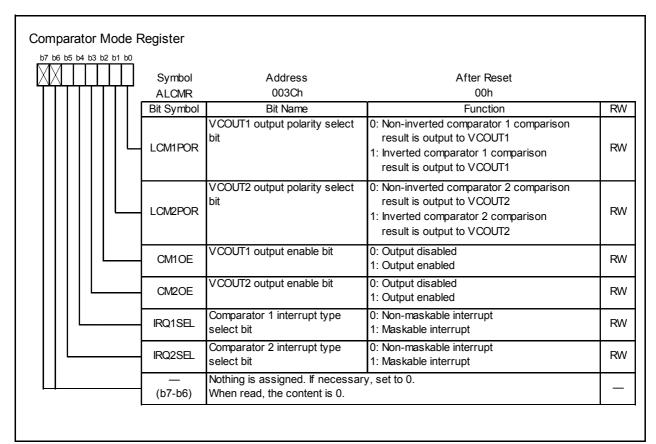

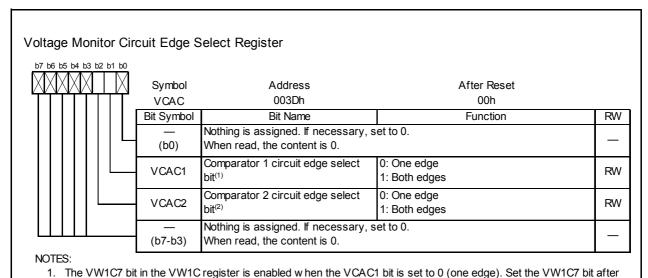

| 7.2          | Register Description                                    |    |

| 7.3          | Monitoring Comparison Results                           |    |

| 7.3.1        | Monitoring Comparator 1                                 |    |

| 7.3.2        | Monitoring Comparator 2                                 |    |

| 7.4          | Functional Description                                  |    |

| 7.4.1        | Comparator 1                                            |    |

| 7.4.2        | Comparator 2                                            | 66 |

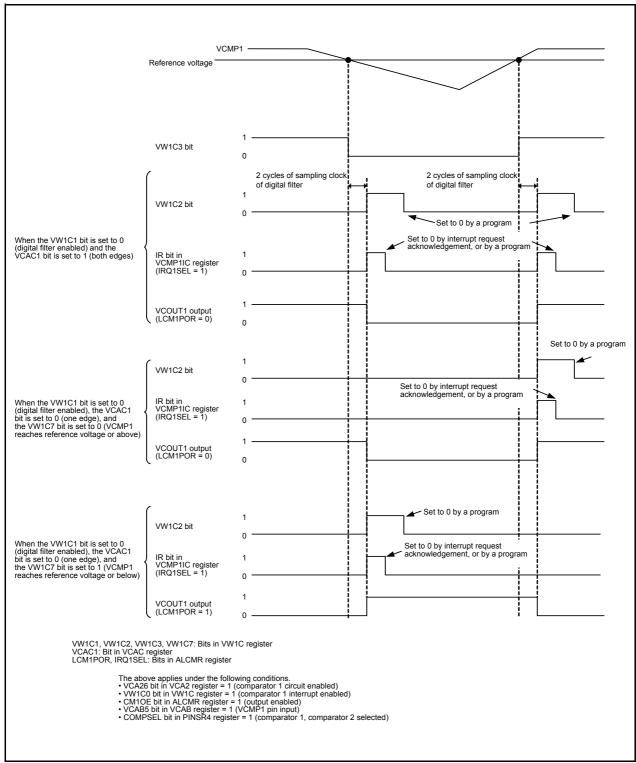

| 7.5          | Comparator 1 and Comparator 2 Interrupts                |    |

| 7.5.1        | Non-Maskable Interrupts                                 |    |

| 7.5.2        | Maskable Interrupts                                     | 69 |

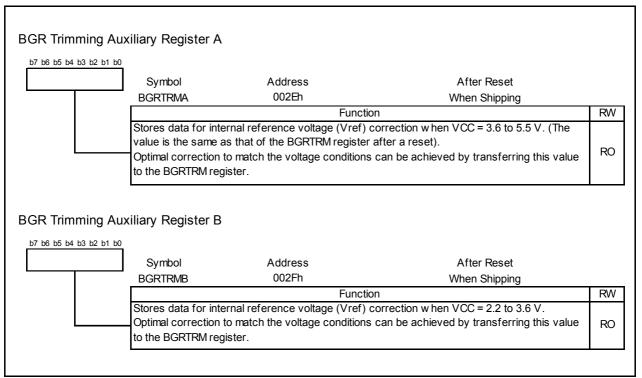

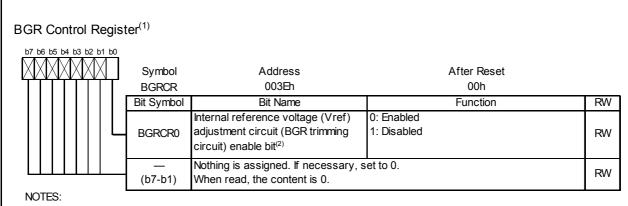

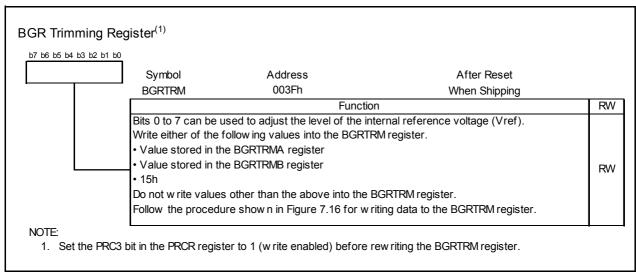

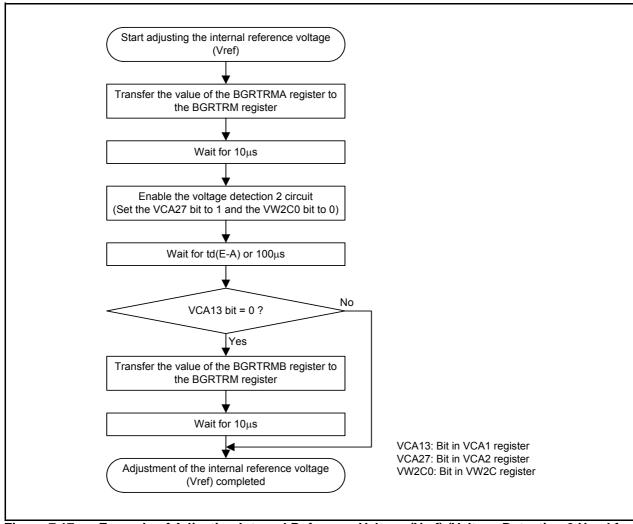

| 7.6          | Adjusting Internal Reference Voltage (Vref)             |    |

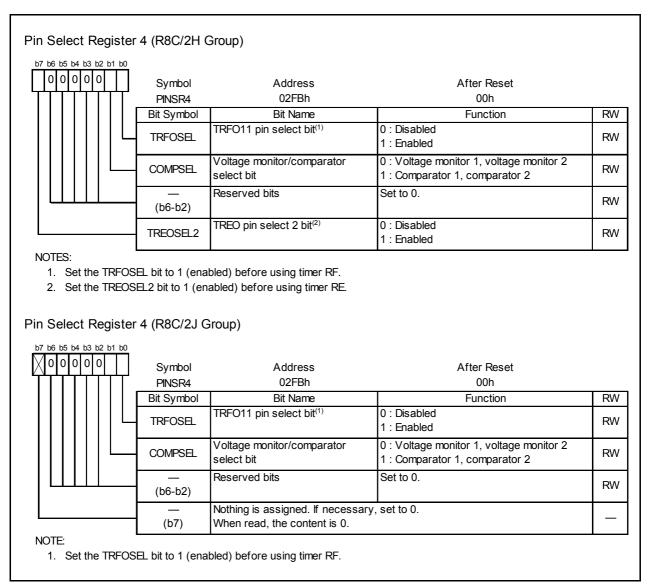

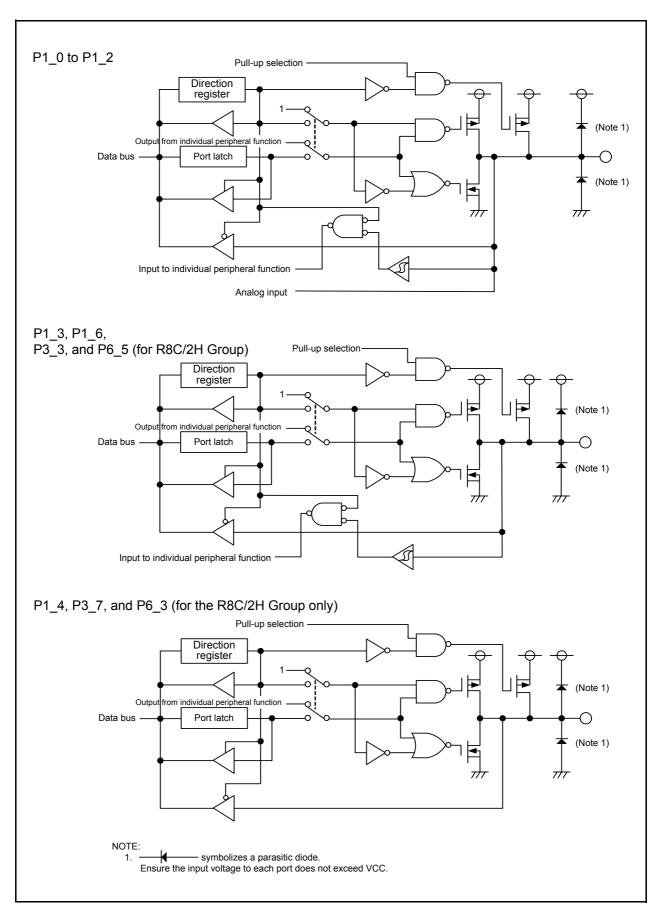

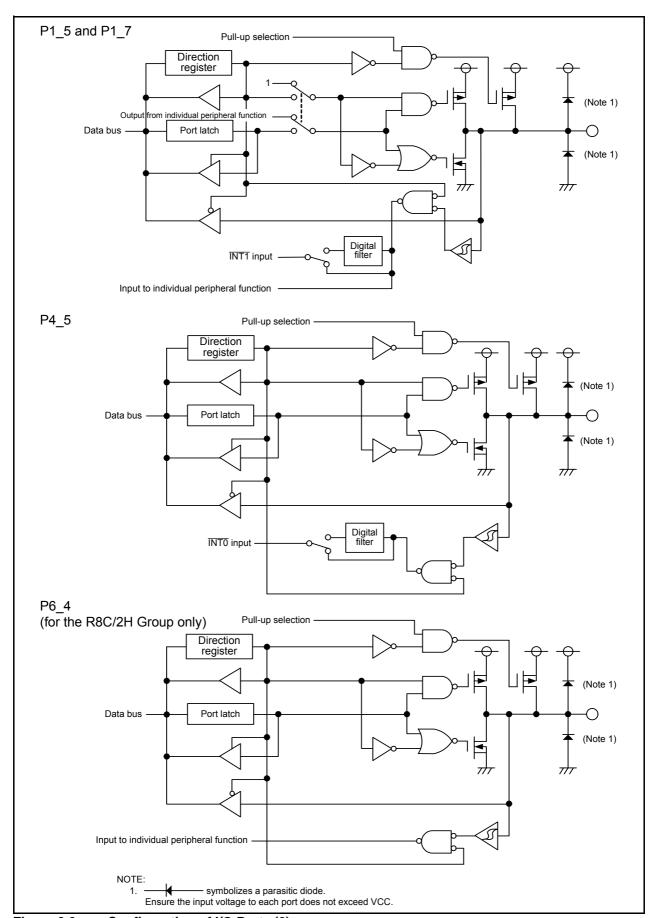

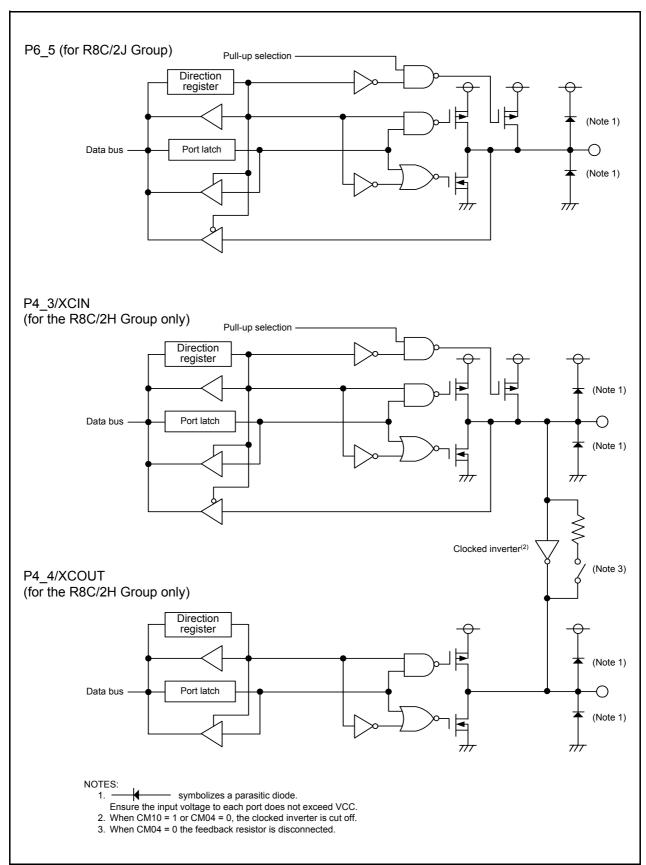

| 8. I/O       | Ports                                                   | 72 |

|              | Functions of I/O Ports                                  |    |

| 8.1<br>8.2   | Effect on Peripheral Functions                          |    |

|              | •                                                       |    |

| 8.3<br>8.4   | Pins Other than Programmable I/O Ports  Port Setting    |    |

| 8.5          | Unassigned Pin Handling                                 |    |

|              |                                                         |    |

| 8.6<br>8.6.1 | Notes on I/O Ports                                      |    |

|              |                                                         |    |

| 9. Pro       | ocessor Mode                                            |    |

| 9.1          | Processor Modes                                         | 91 |

| 10. Bu       | s                                                       | 92 |

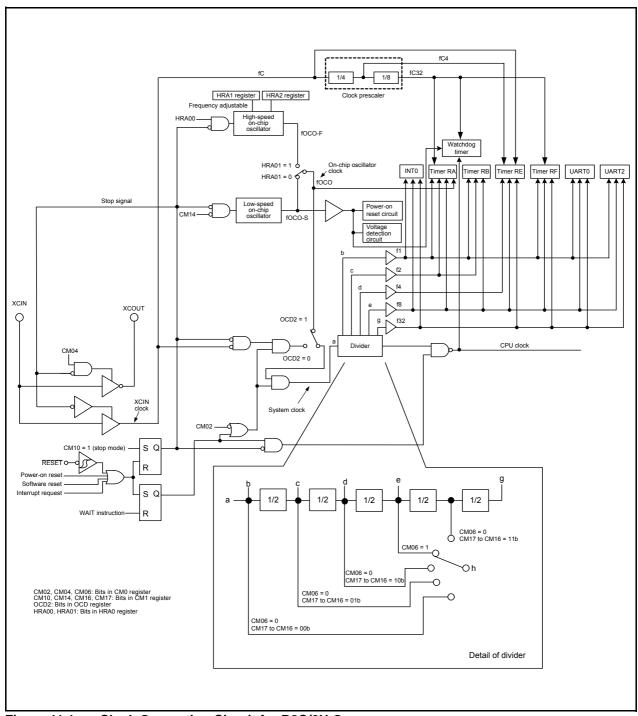

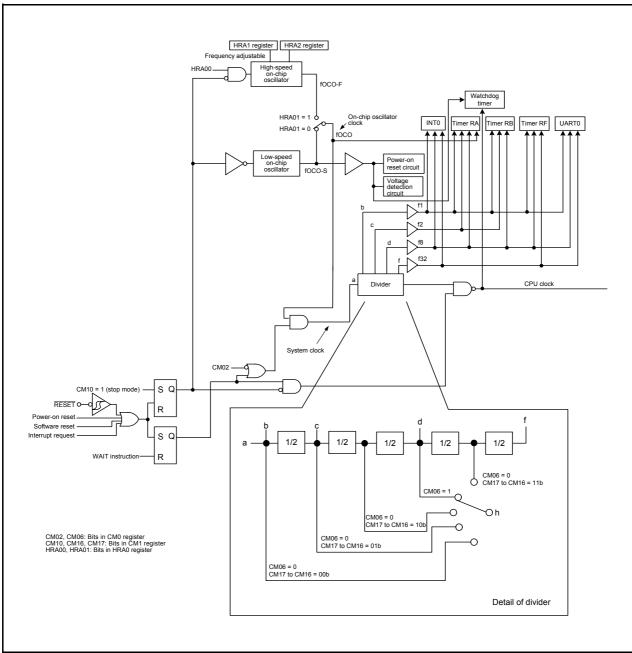

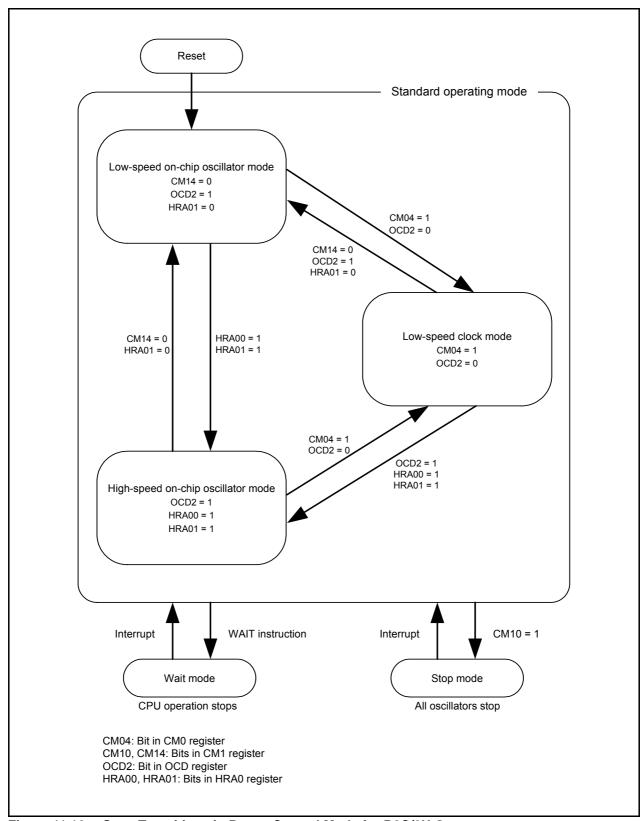

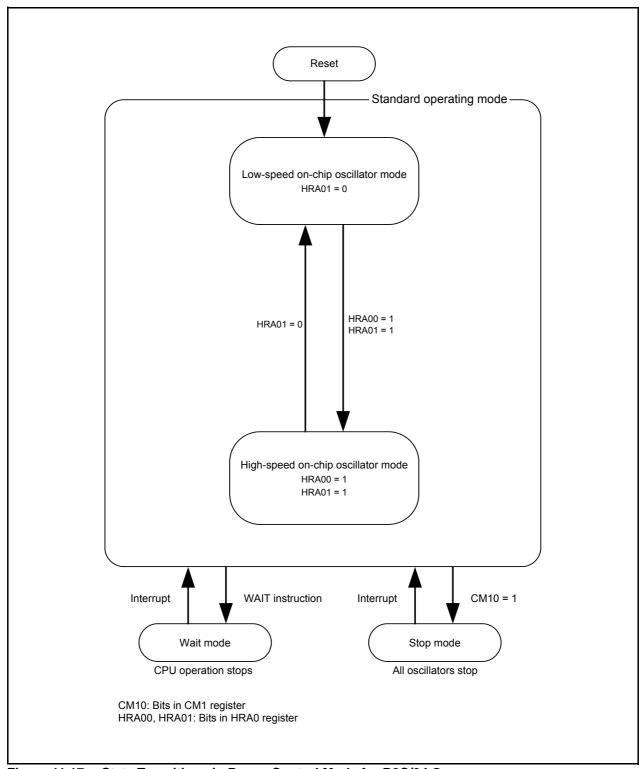

| 11. Cld      | ock Generation Circuit                                  | 03 |

| 11.1         | On-Chip Oscillator Clocks                               |    |

| 11.1.1       | •                                                       |    |

| 11.1.2       |                                                         |    |

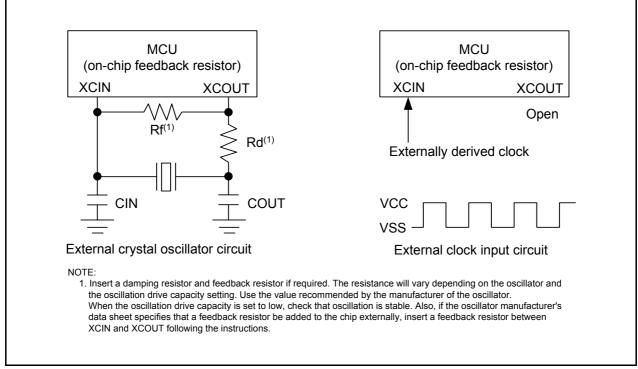

| 11.2         | XCIN Clock (for R8C/2H Group only)                      |    |

| 11.3         | CPU Clock and Peripheral Function Clock                 |    |

| 11.3.1       | •                                                       |    |

| 11.3.2       | •                                                       |    |

| 11.3.3       |                                                         |    |

| 11.3.4       | _                                                       |    |

| 11.3.5       |                                                         |    |

| 11.3.6       |                                                         |    |

| 11.3.7       |                                                         |    |

| 11.4         | Power Control                                           |    |

|              | Standard Operating Mode                                 |    |

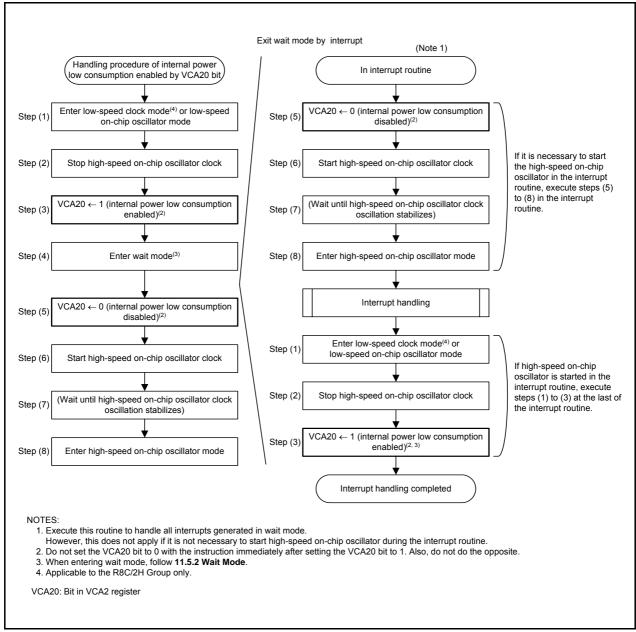

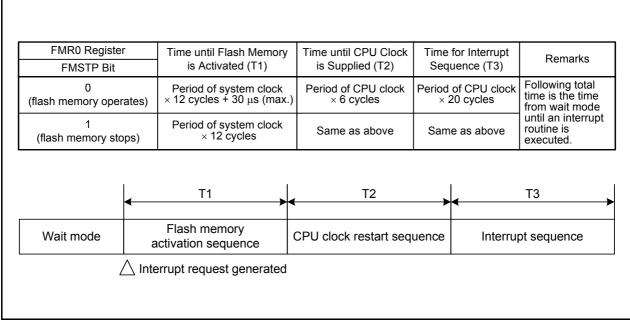

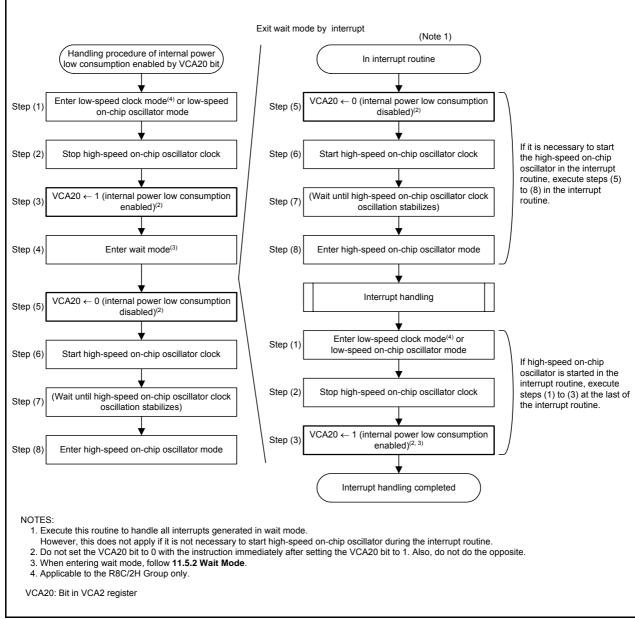

| 11.4.2         | Wait Mode                                            | 110 |

|----------------|------------------------------------------------------|-----|

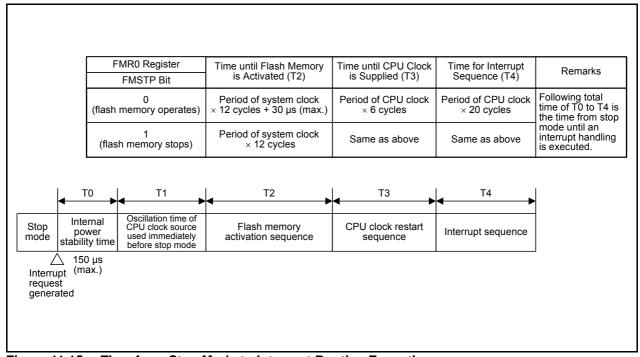

| 11.4.3         | Stop Mode                                            | 112 |

| 11.5           | Notes on Clock Generation Circuit                    | 116 |

| 11.5.1         | Stop Mode                                            | 116 |

| 11.5.2         | Wait Mode                                            | 116 |

| 11.5.3         | Oscillation Circuit Constants                        | 116 |

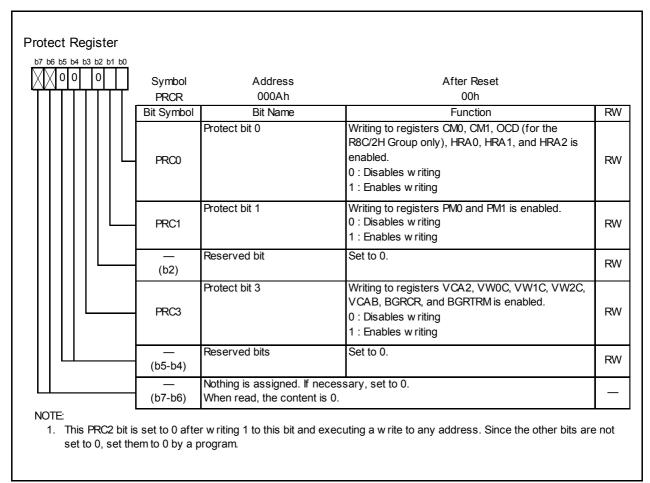

| 12. Pro        | tection                                              | 117 |

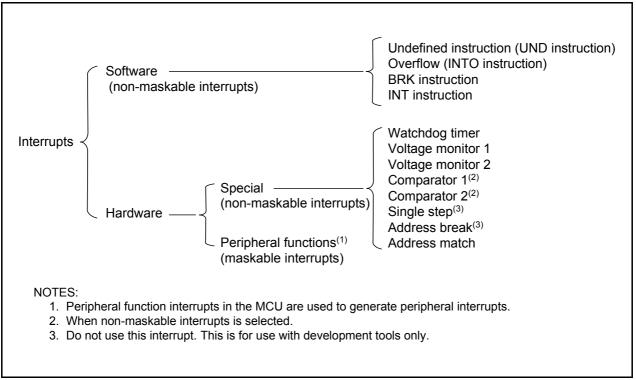

| 13. Inte       | rrupts                                               | 118 |

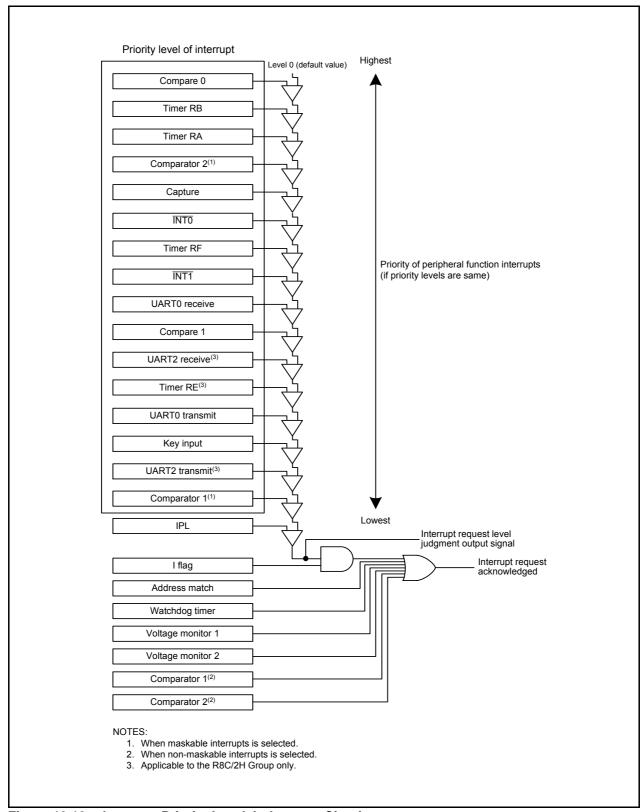

| 13.1           | Interrupt Overview                                   | 118 |

| 13.1.1         | Types of Interrupts                                  | 118 |

| 13.1.2         | Software Interrupts                                  | 119 |

| 13.1.3         | Special Interrupts                                   | 120 |

| 13.1.4         | Peripheral Function Interrupt                        |     |

| 13.1.5         | Interrupts and Interrupt Vectors                     | 121 |

| 13.1.6         | Interrupt Control                                    | 123 |

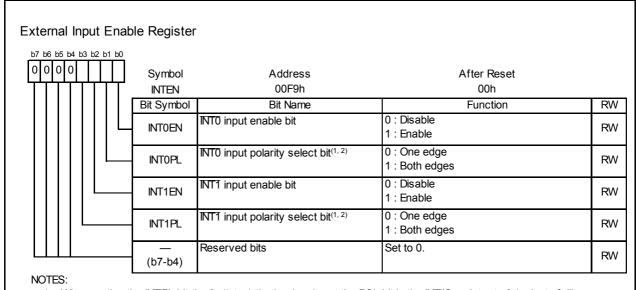

| 13.2           | INT Interrupt                                        | 131 |

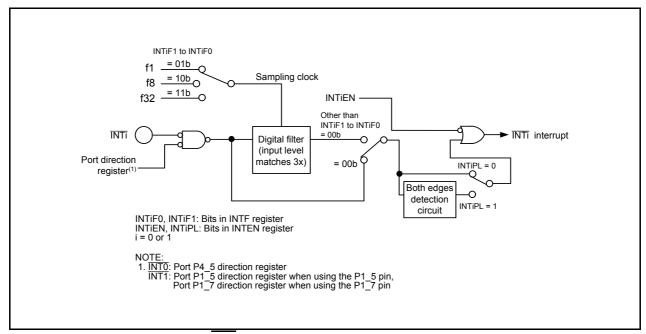

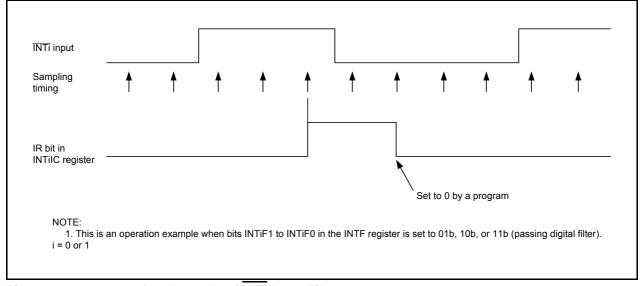

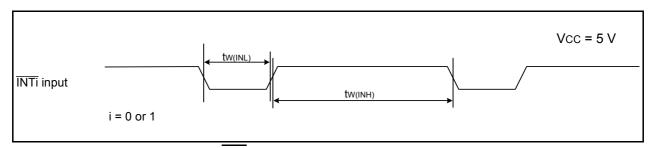

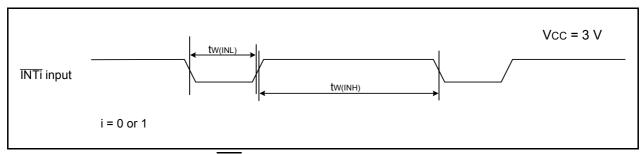

| 13.2.1         | $\overline{\text{INTi}}$ Interrupt (i = 0 or 1)      | 131 |

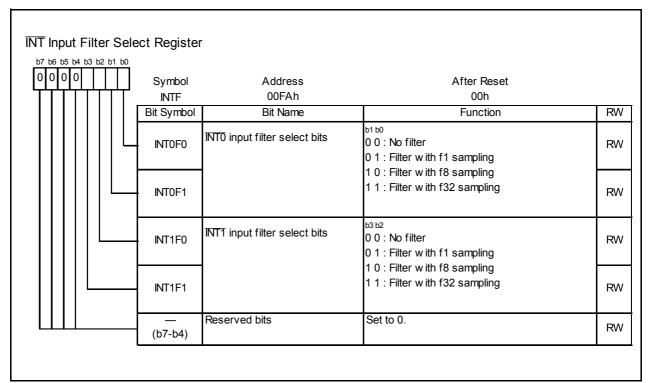

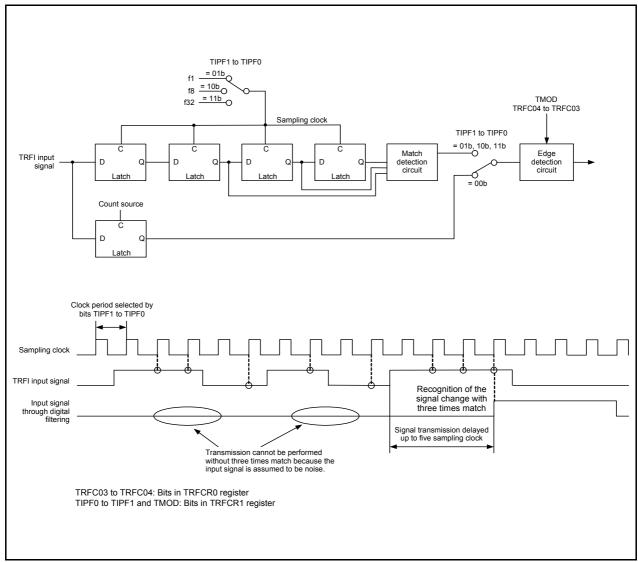

| 13.2.2         | $\overline{\text{INTi}}$ Input Filter (i = 0 or 1)   | 133 |

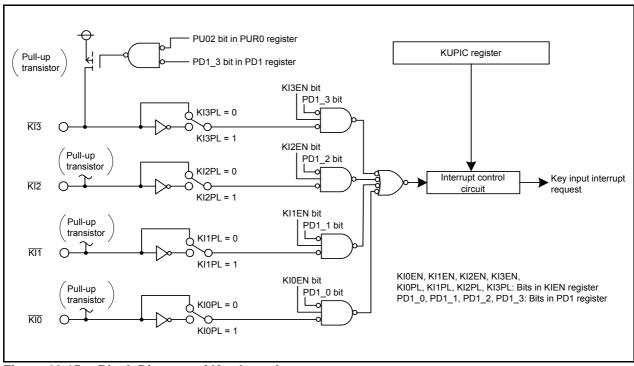

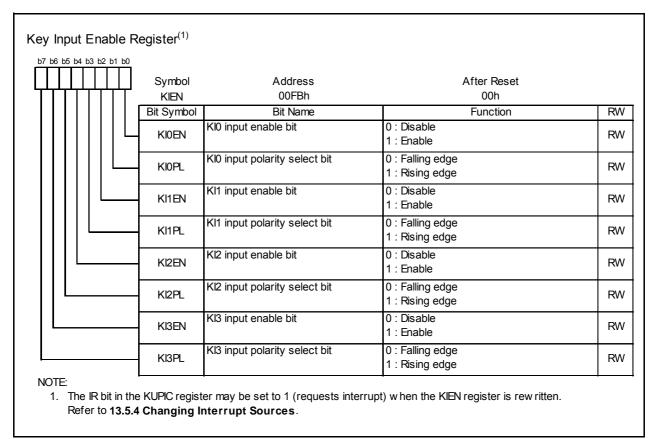

| 13.3           | Key Input Interrupt                                  | 134 |

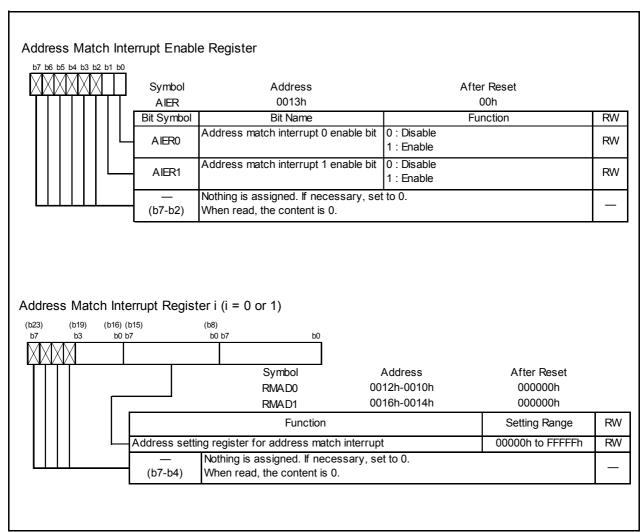

| 13.4           | Address Match Interrupt                              | 136 |

| 13.5           | Notes on Interrupts                                  | 138 |

| 13.5.1         | Reading Address 00000h                               | 138 |

| 13.5.2         | SP Setting                                           | 138 |

| 13.5.3         | External Interrupt and Key Input Interrupt           |     |

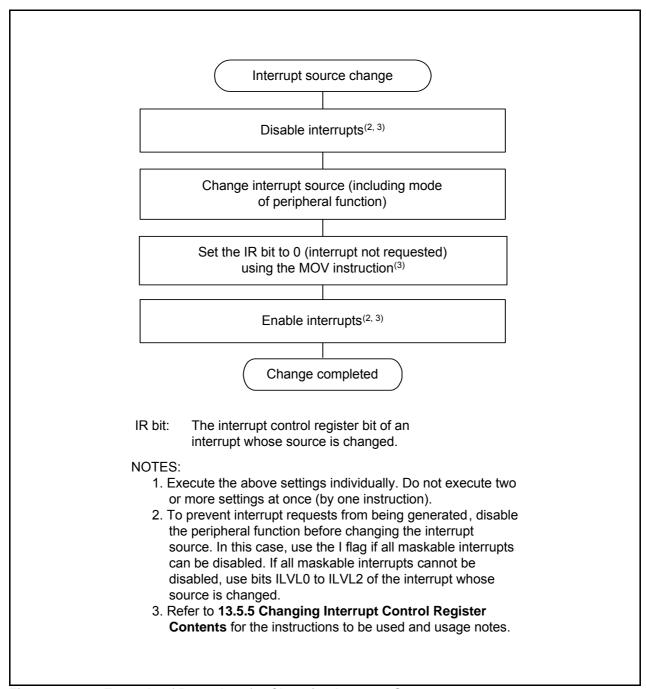

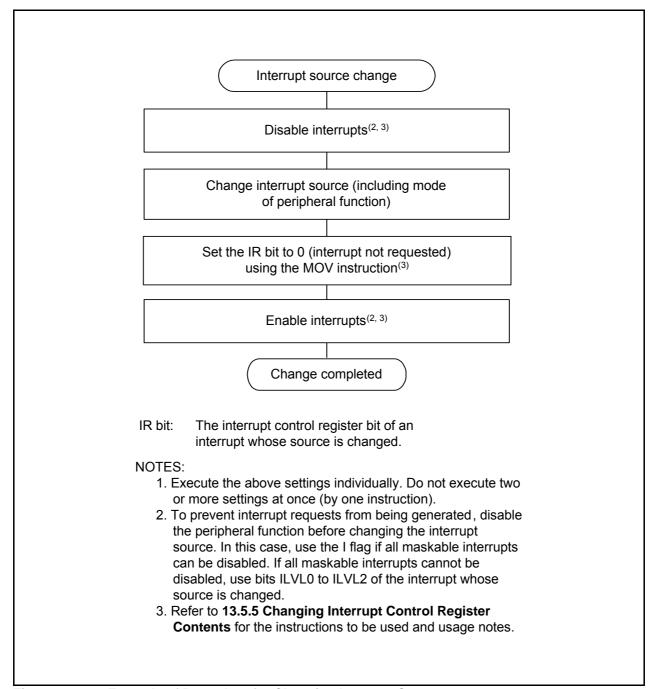

| 13.5.4         | Changing Interrupt Sources                           | 139 |

| 13.5.5         | Changing Interrupt Control Register Contents         | 140 |

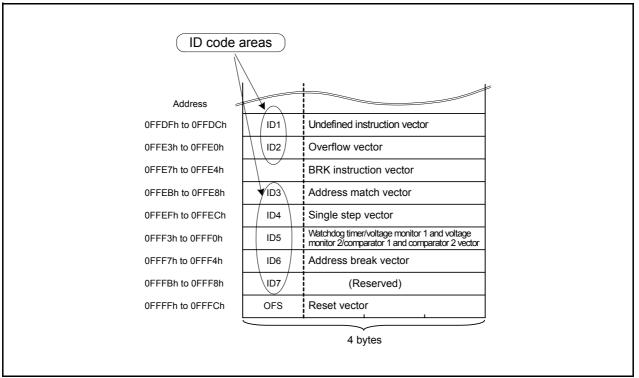

| 14. ID (       | Code Areas                                           | 141 |

| 14.1           | Overview                                             | 141 |

|                | Functions                                            |     |

|                | Notes on ID Code Areas                               |     |

| 14.3.1         | Setting Example of ID Code Areas                     |     |

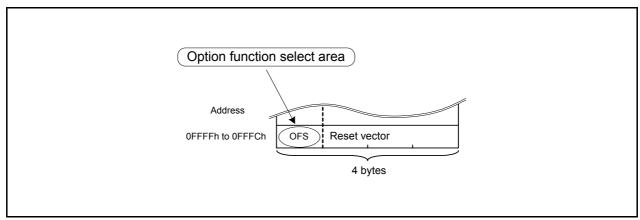

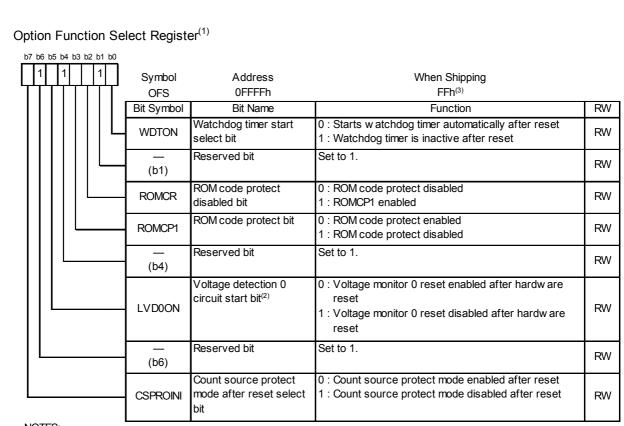

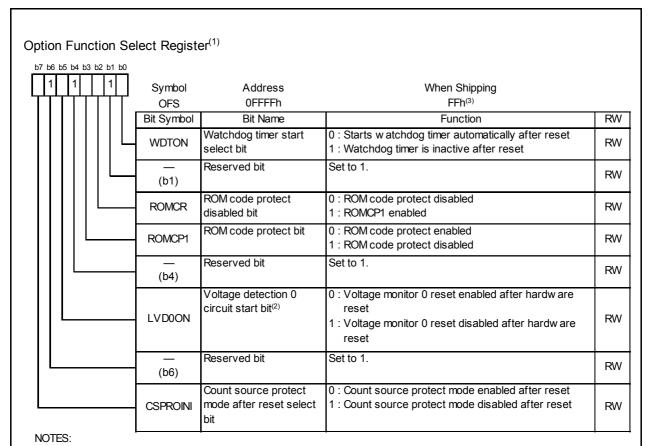

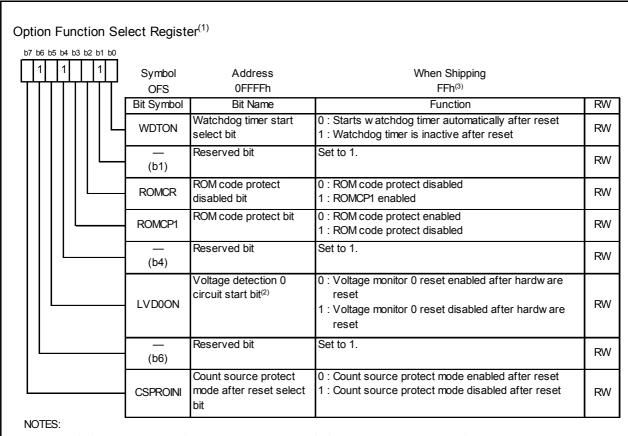

| 15. Opt        | ion Function Select Area                             | 143 |

| •              | Overview                                             |     |

|                | OVERVIEWOFS Register                                 |     |

|                |                                                      |     |

| 15.3<br>15.3.1 | Notes on Option Function Select Area                 |     |

|                |                                                      |     |

| 16. Wat        | chdog Timer                                          | 146 |

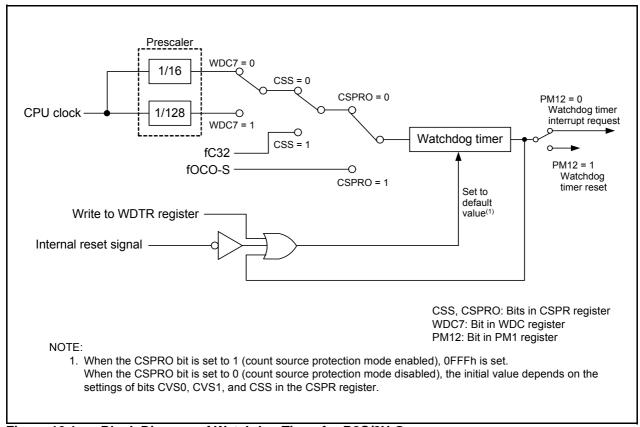

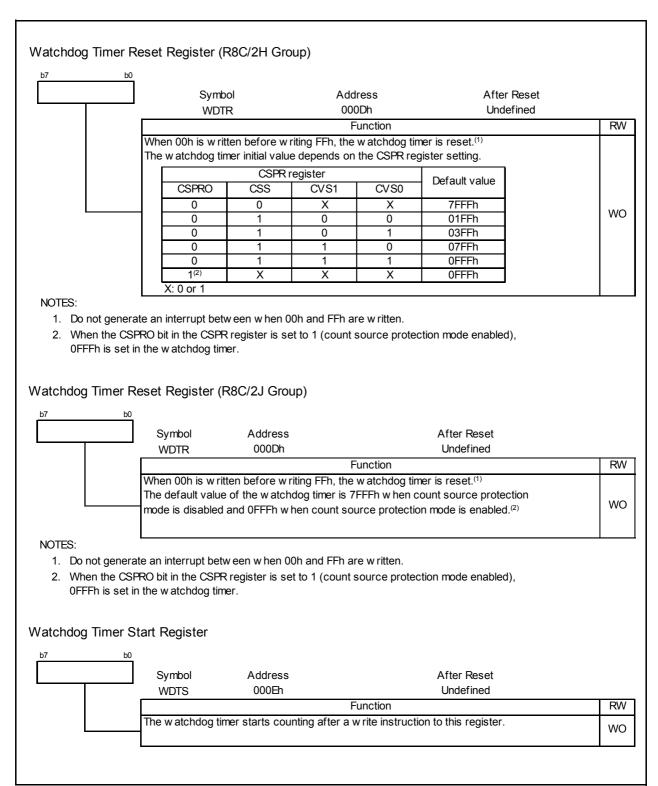

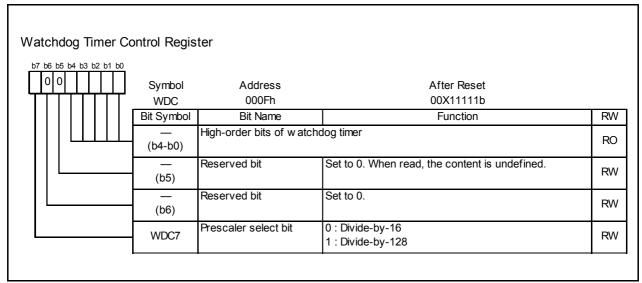

|                | Count Source Protection Mode Disabled (R8C/2H Group) |     |

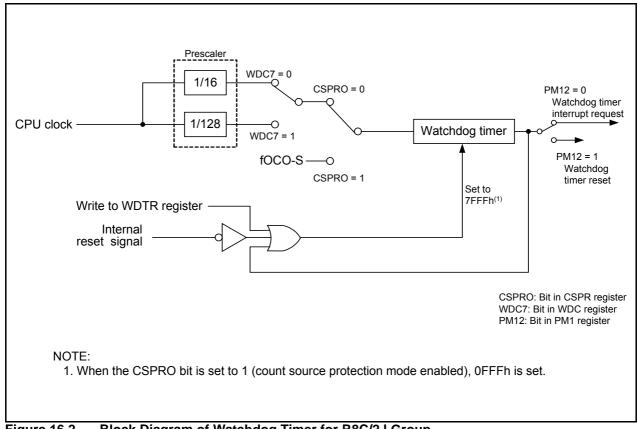

| 16.2           | Count Source Protection Mode Disabled (R8C/2J Group) | 154 |

| 16.3           | Count Source Protection Mode Enabled                 | 155 |

| 17. Tim        | ers                                                  | 156 |

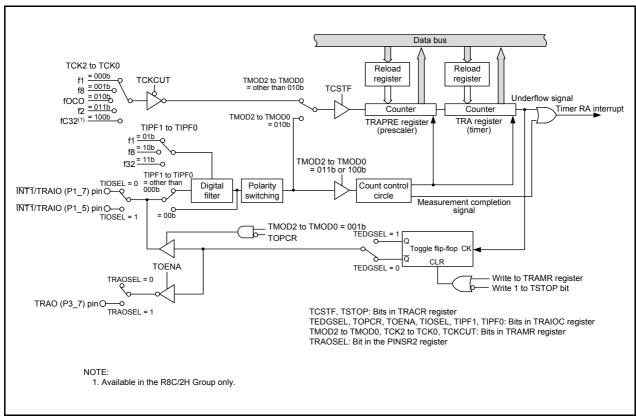

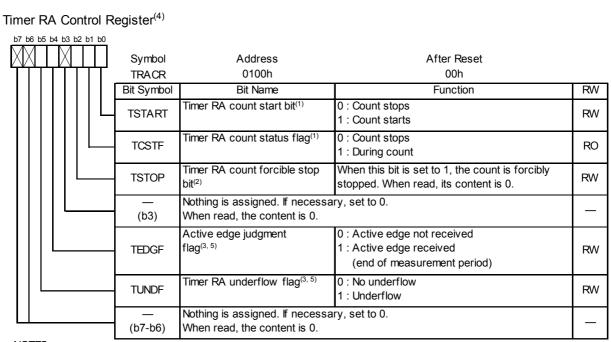

| 17.1           | Timer RA                                             | 158 |

| 17 1 1         |                                                      | 161 |

| 17.1.2    | Pulse Output Mode                              | 163 |

|-----------|------------------------------------------------|-----|

| 17.1.3    | Event Counter Mode                             | 165 |

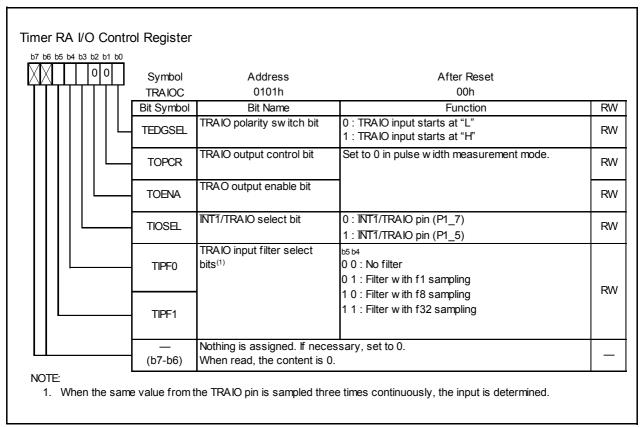

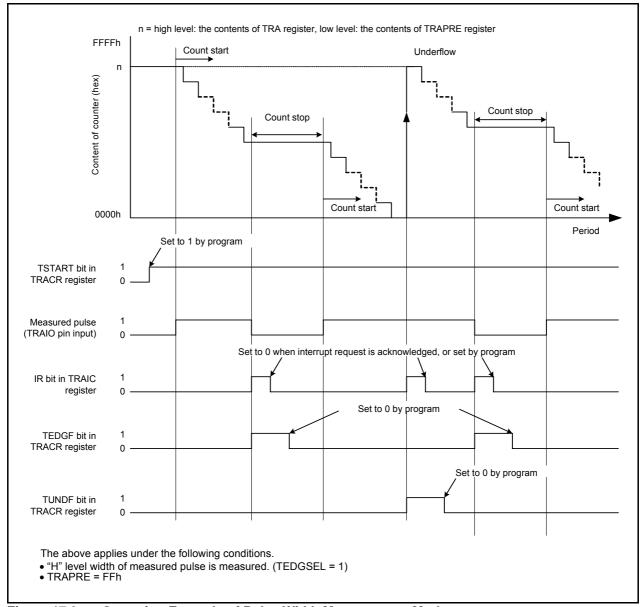

| 17.1.4    | Pulse Width Measurement Mode                   | 167 |

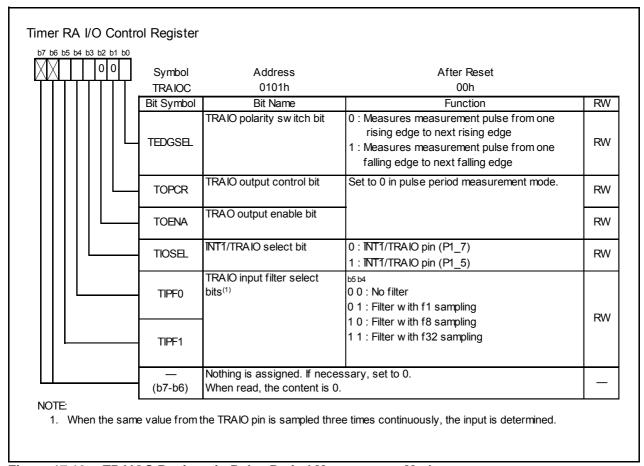

| 17.1.5    | Pulse Period Measurement Mode                  | 170 |

| 17.1.6    | Notes on Timer RA                              | 173 |

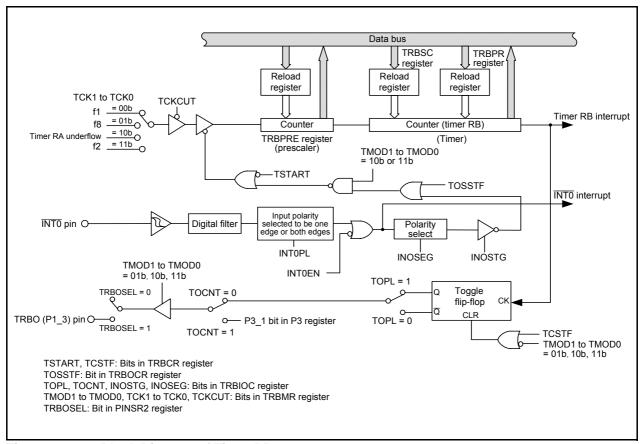

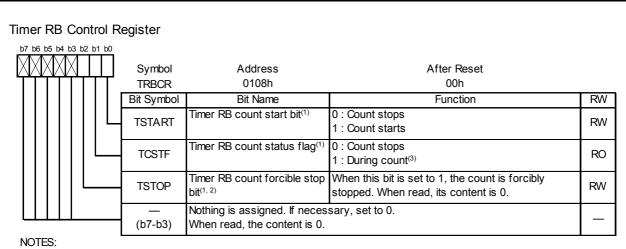

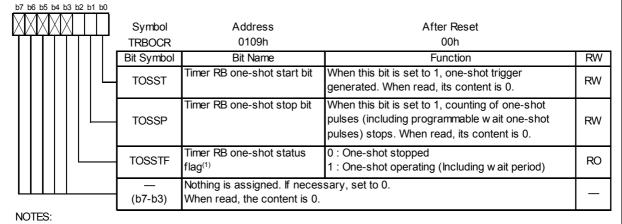

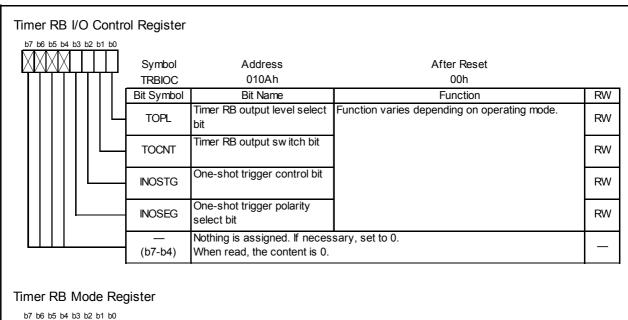

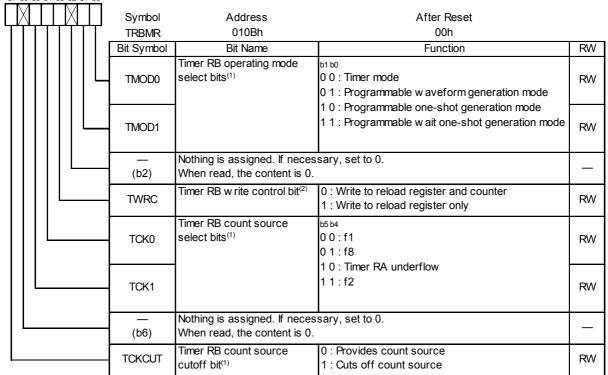

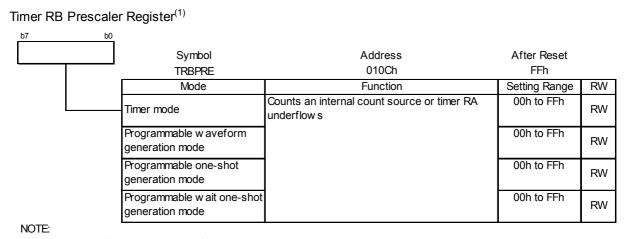

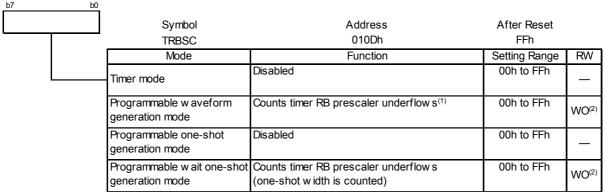

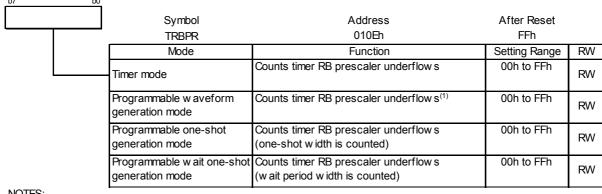

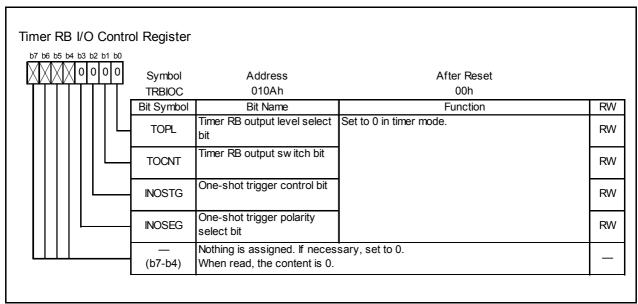

| 17.2      | Timer RB                                       | 174 |

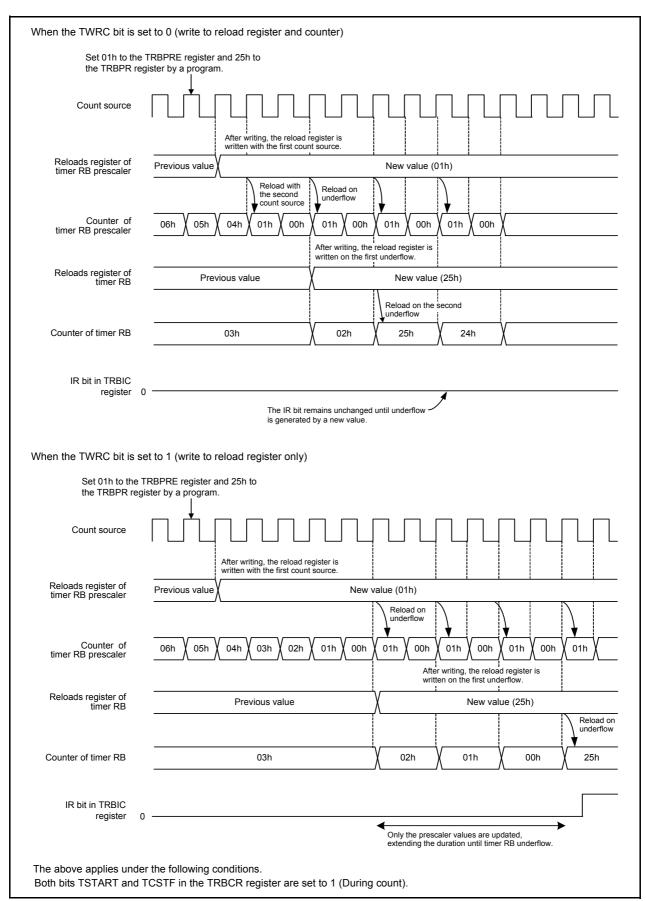

| 17.2.1    | Timer Mode                                     | 178 |

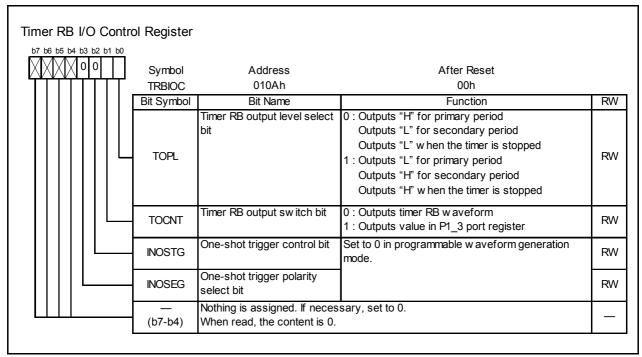

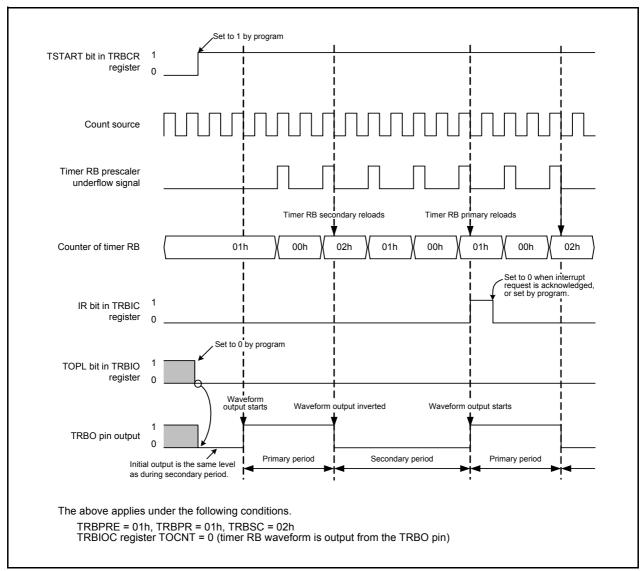

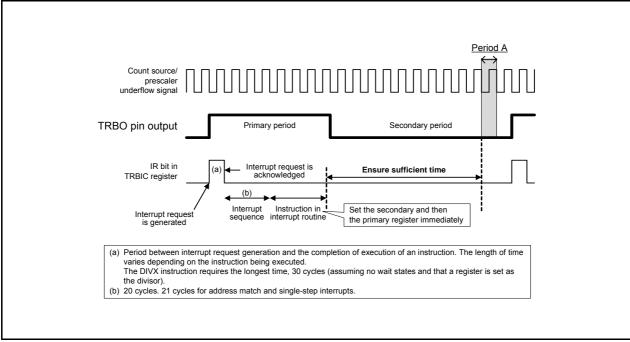

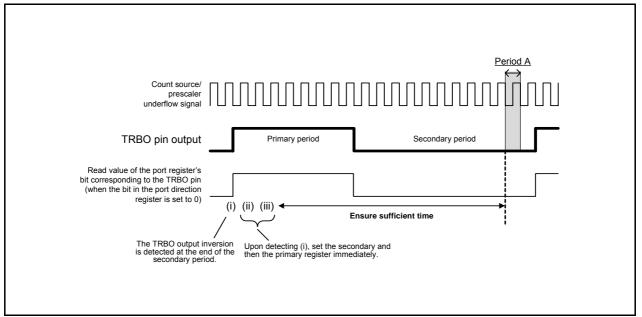

| 17.2.2    | Programmable Waveform Generation Mode          | 181 |

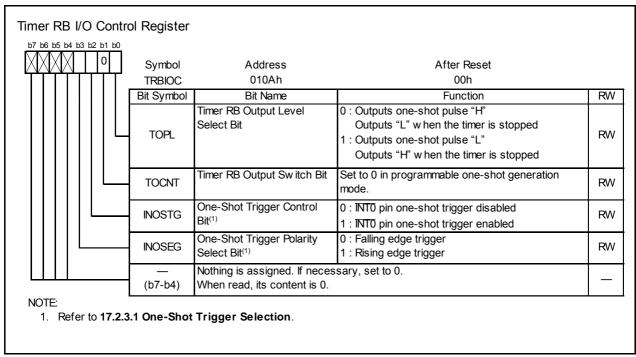

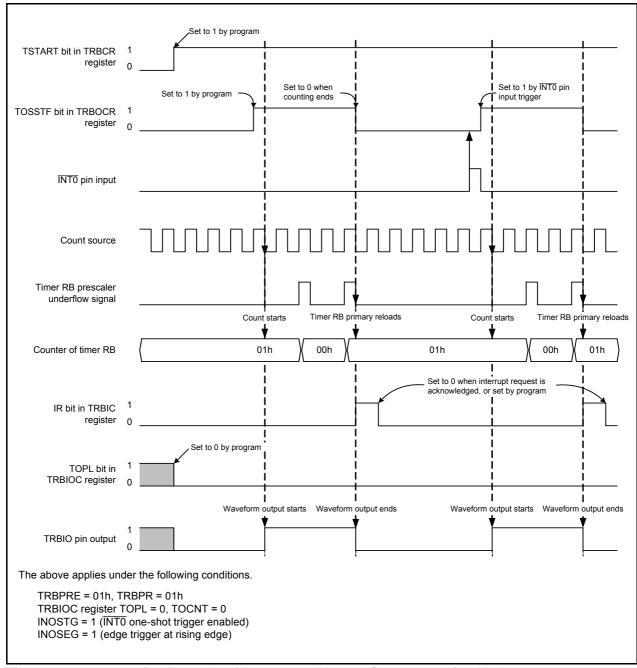

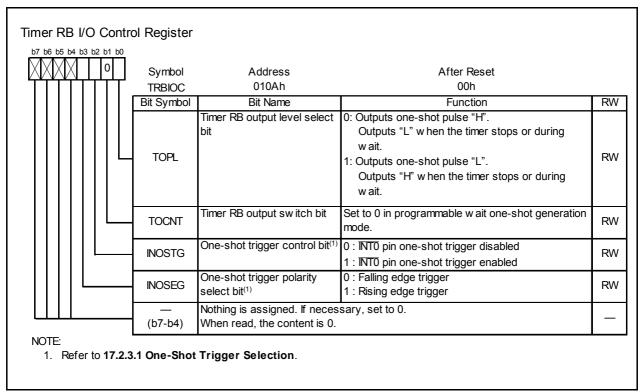

| 17.2.3    | Programmable One-shot Generation Mode          | 184 |

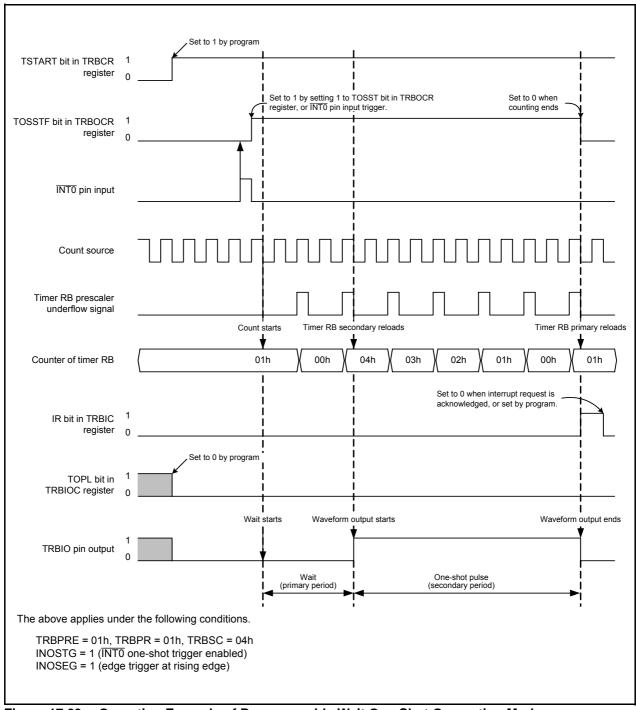

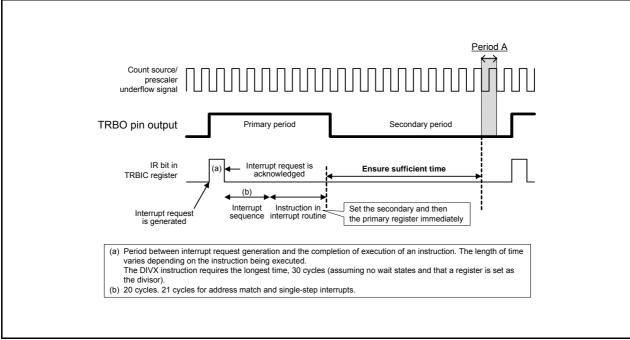

| 17.2.4    | Programmable Wait One-Shot Generation Mode     | 188 |

| 17.2.5    | Notes on Timer RB                              | 191 |

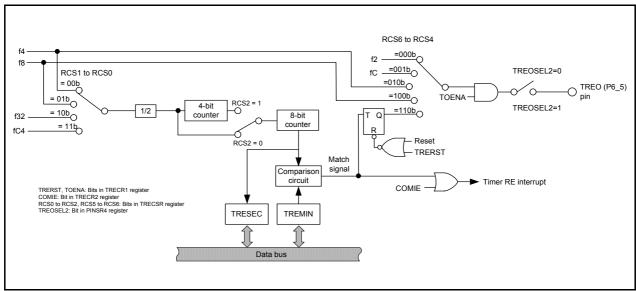

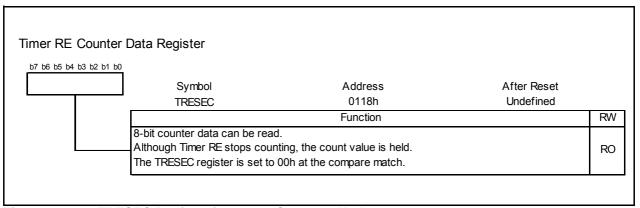

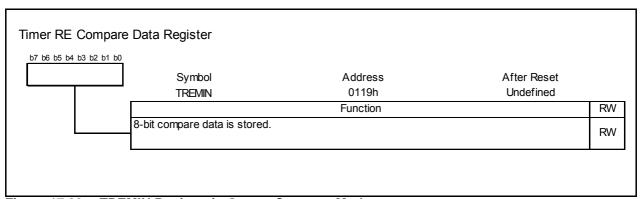

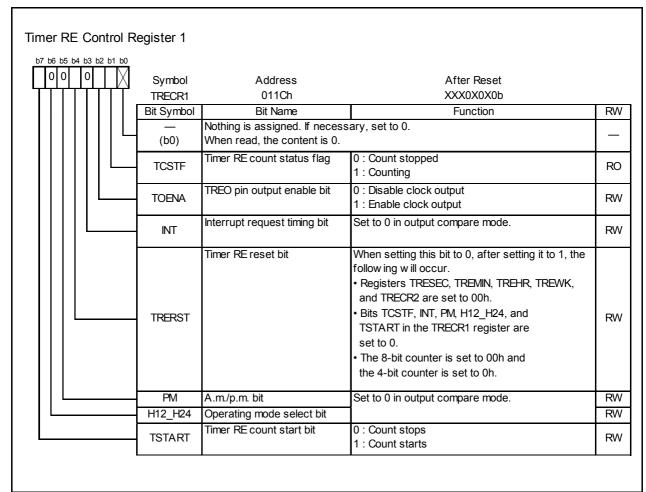

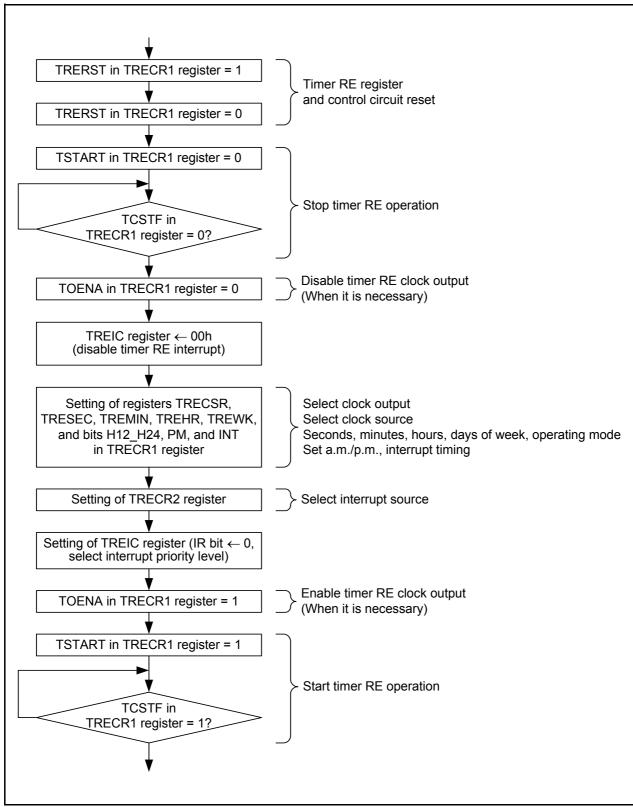

| 17.3      | Fimer RE (for R8C/2H Group only)               | 195 |

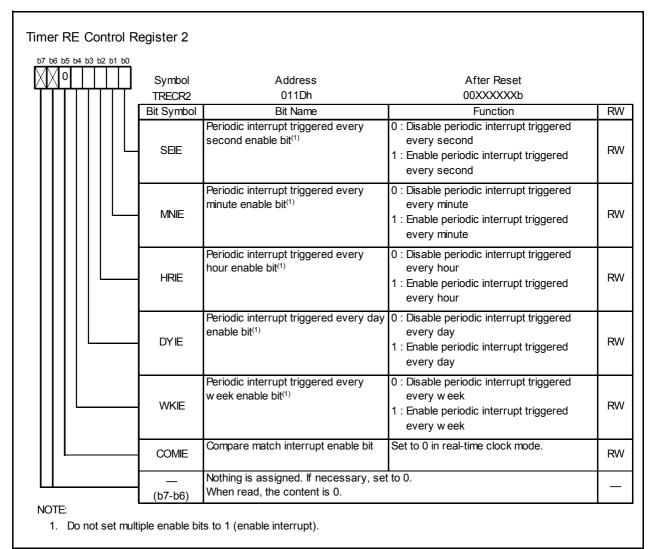

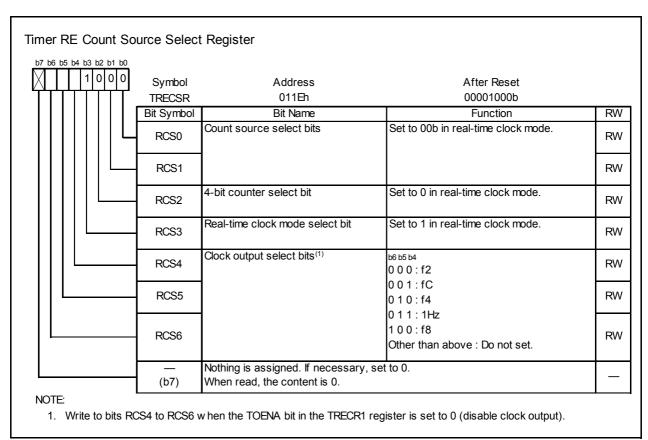

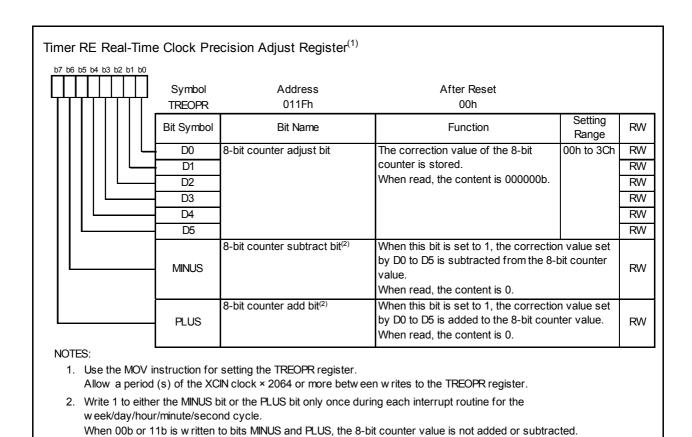

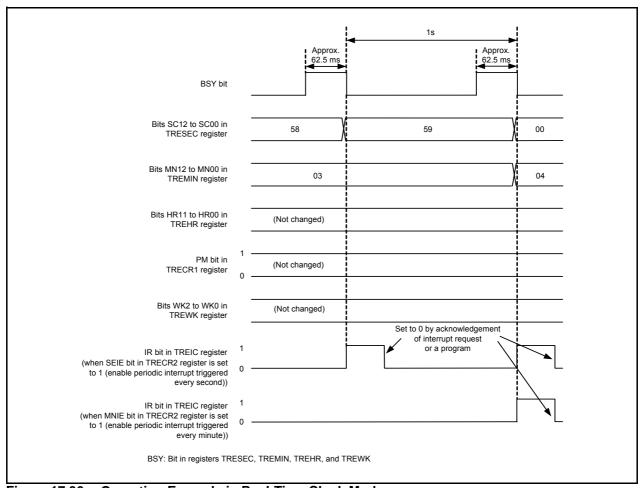

| 17.3.1    | Real-Time Clock Mode                           | 196 |

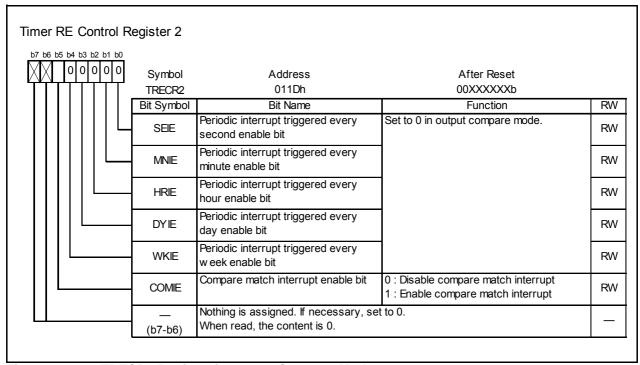

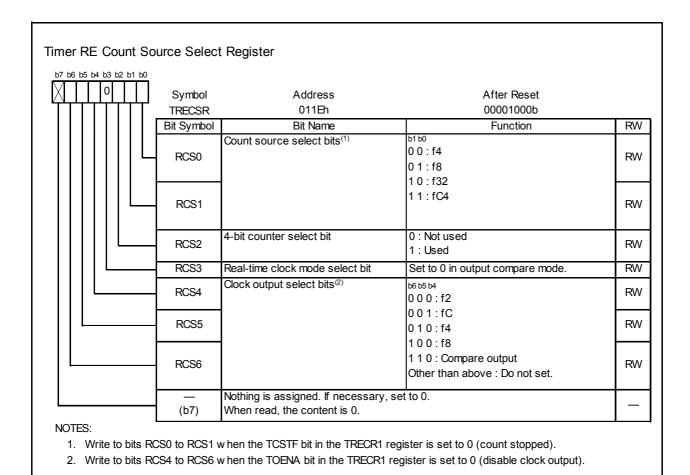

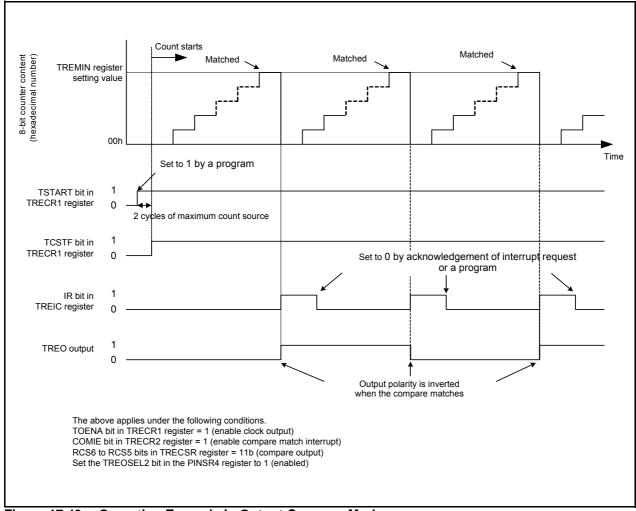

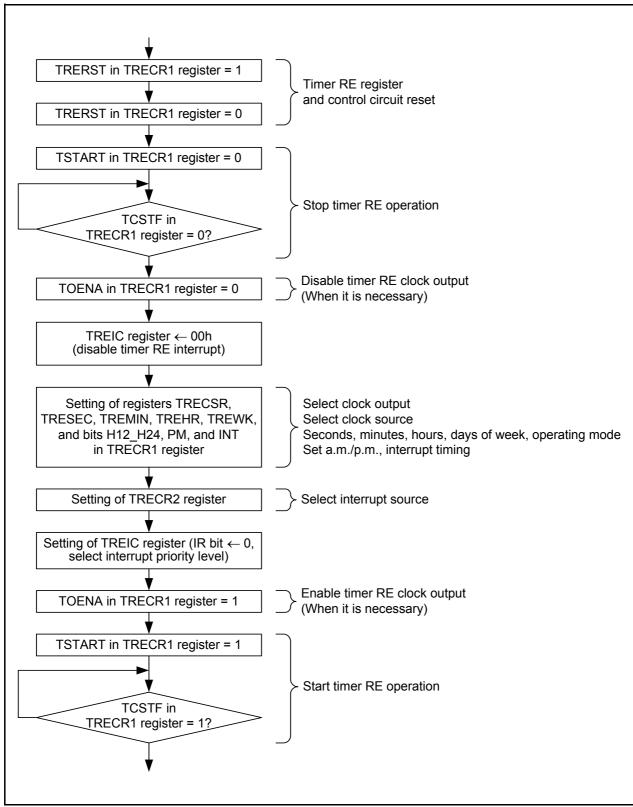

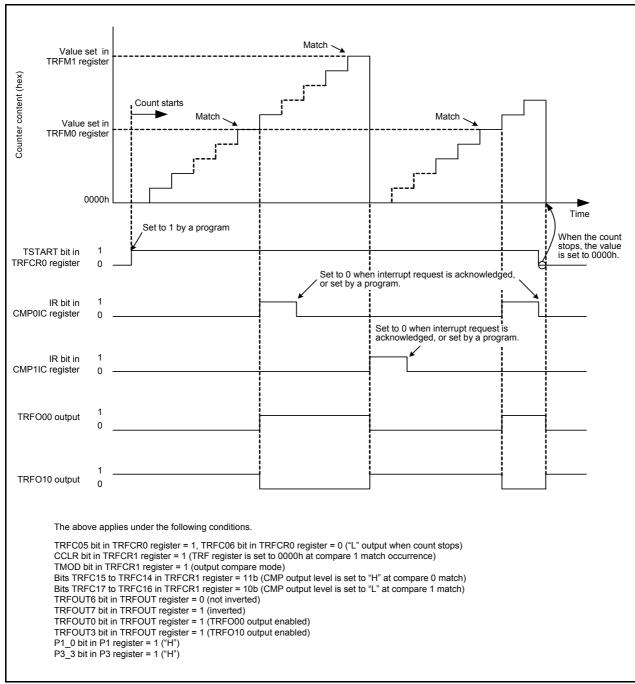

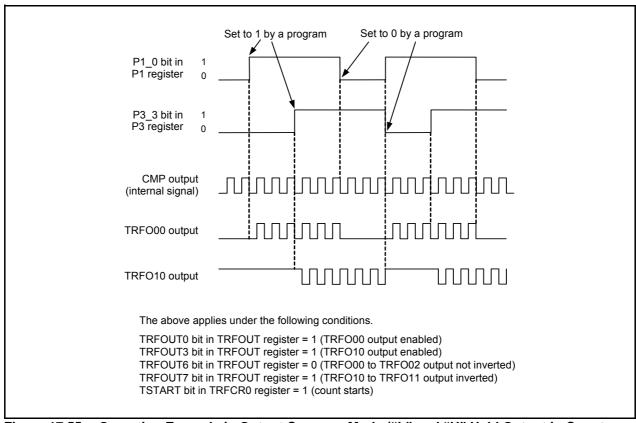

| 17.3.2    | Output Compare Mode                            | 204 |

| 17.3.3    | Notes on Timer RE (for R8C/2H Group only)      | 210 |

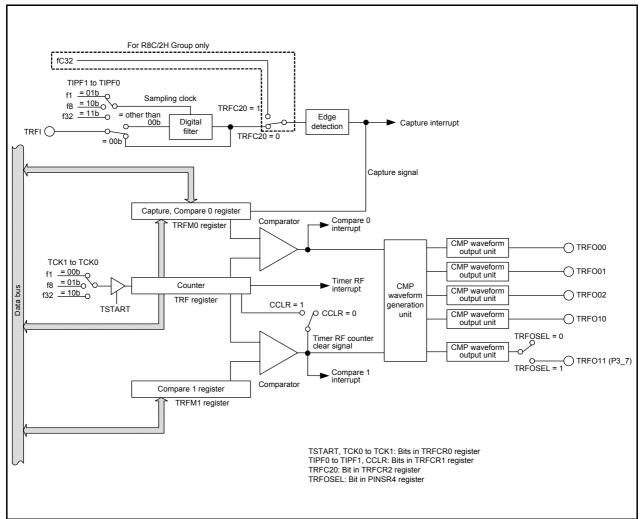

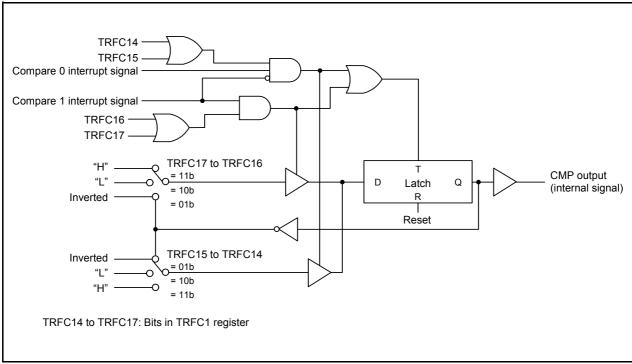

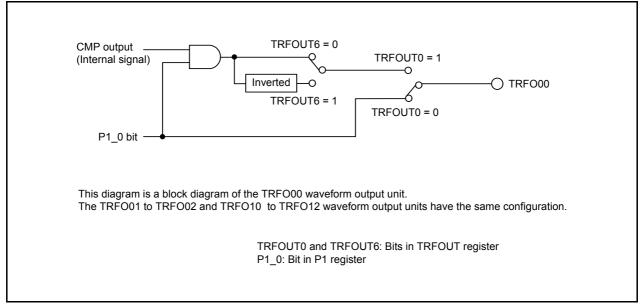

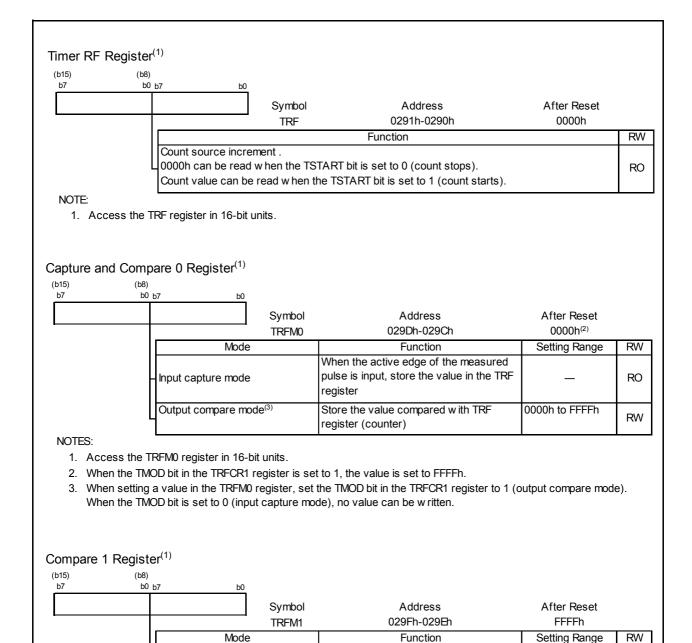

| 17.4      | Fimer RF                                       | 213 |

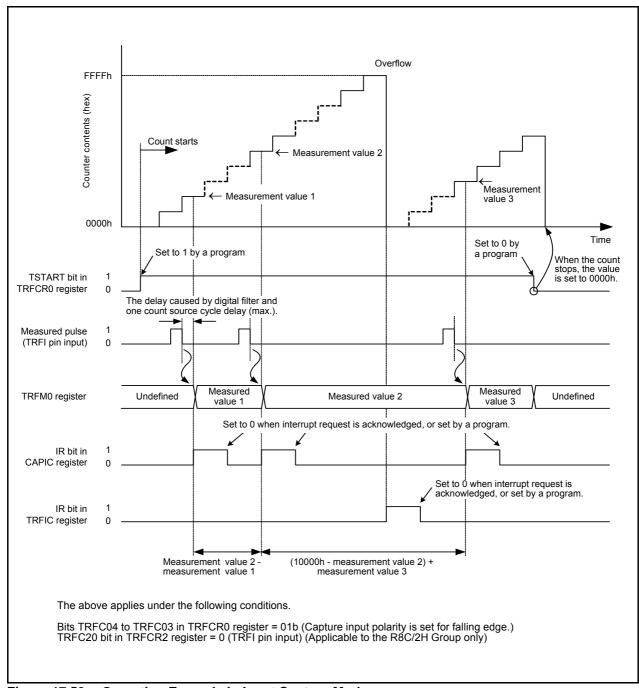

| 17.4.1    | Input Capture Mode                             | 218 |

| 17.4.2    | Output Compare Mode                            | 221 |

| 17.4.3    | Notes on Timer RF                              | 225 |

|           |                                                |     |

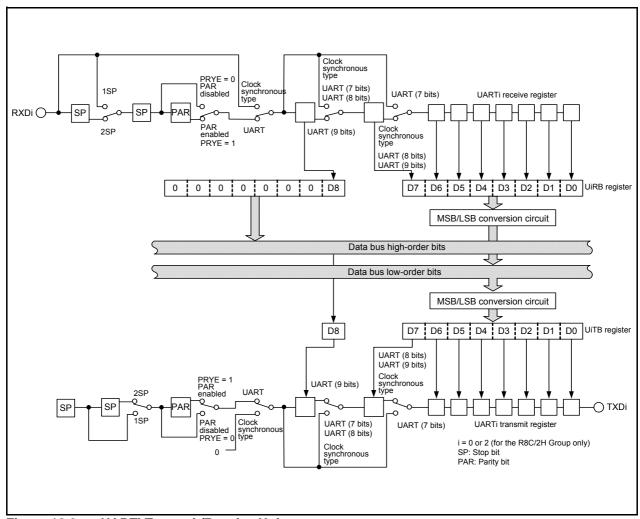

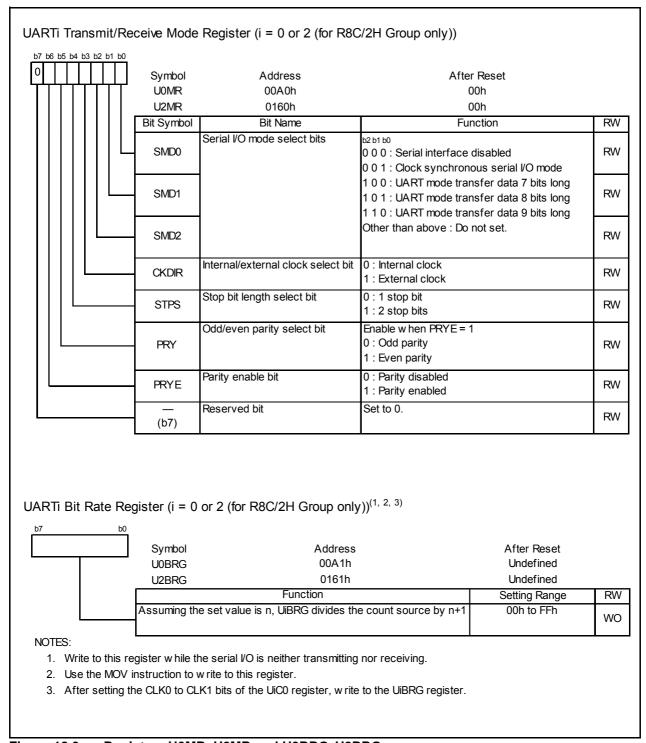

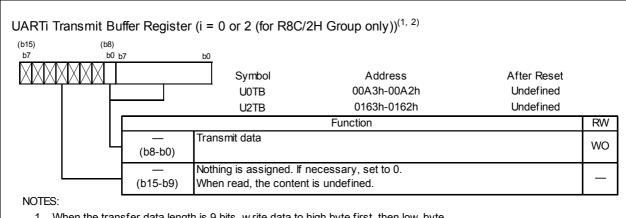

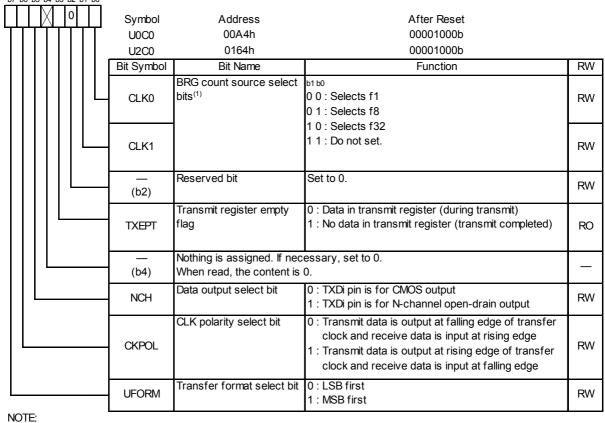

| 18. Seria | al Interface                                   | 226 |

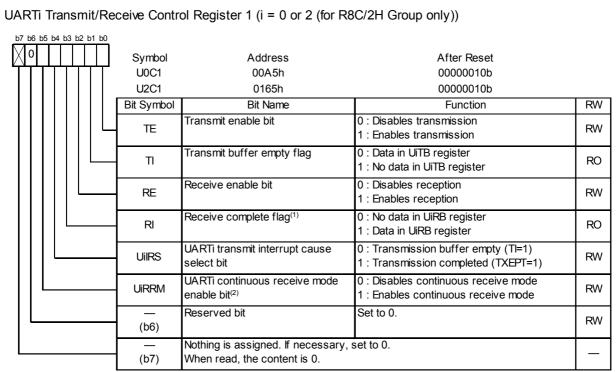

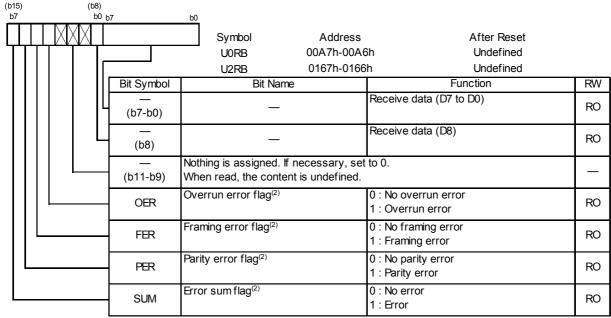

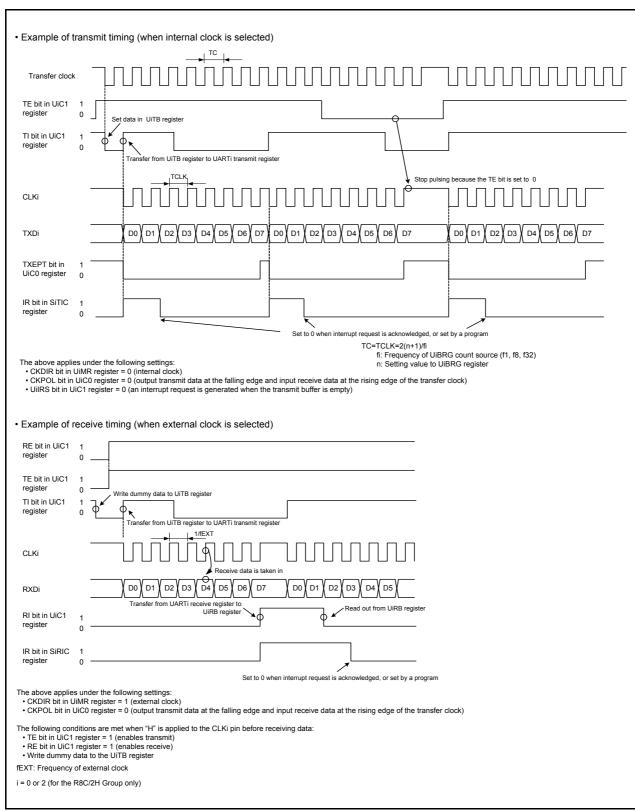

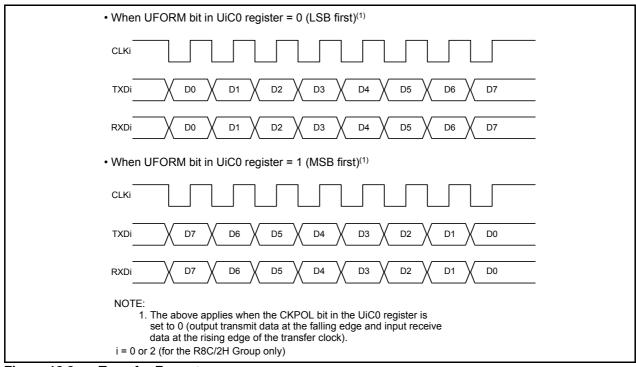

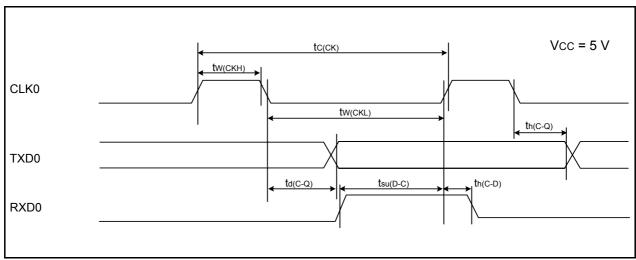

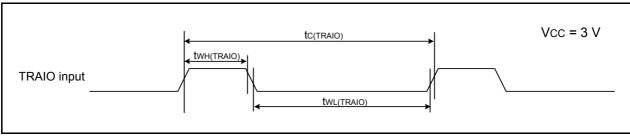

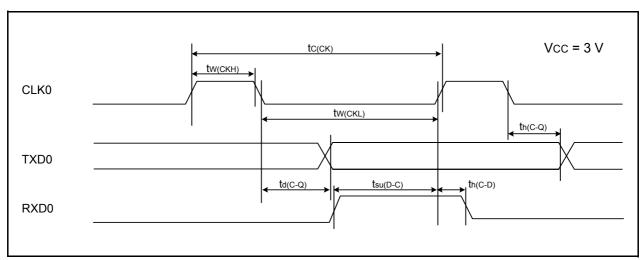

| 18.1      | Clock Synchronous Serial I/O Mode              | 231 |

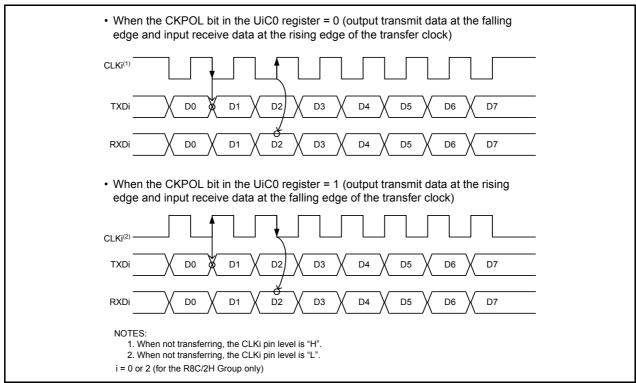

| 18.1.1    | Polarity Select Function                       | 234 |

| 18.1.2    | LSB First/MSB First Select Function            | 234 |

| 18.1.3    | Continuous Receive Mode                        | 235 |

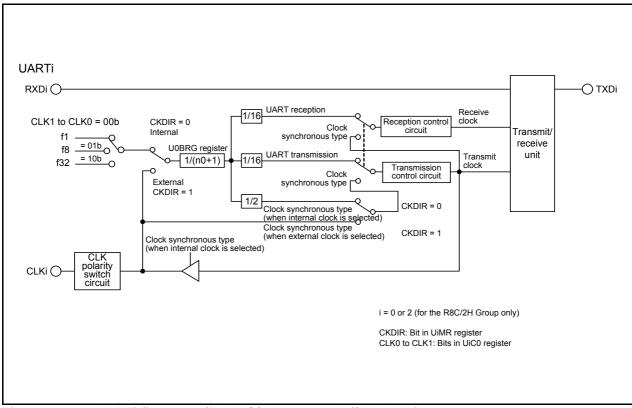

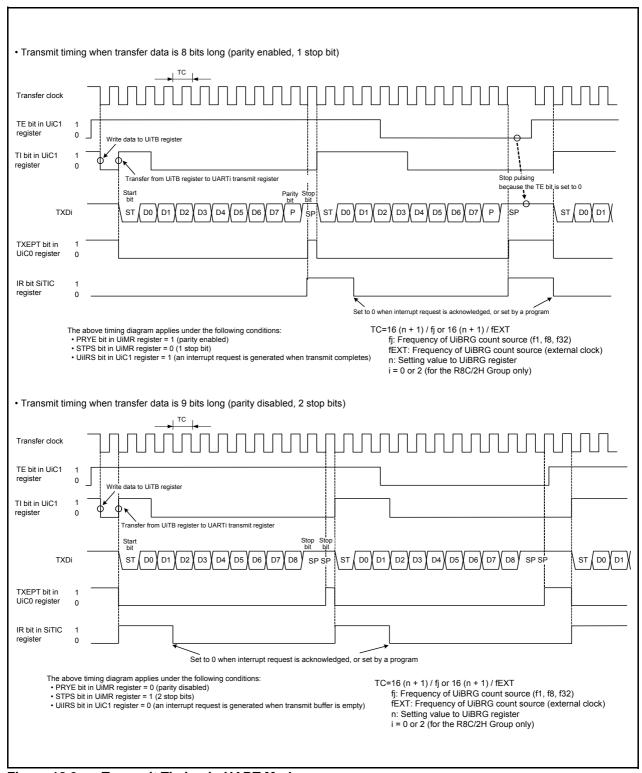

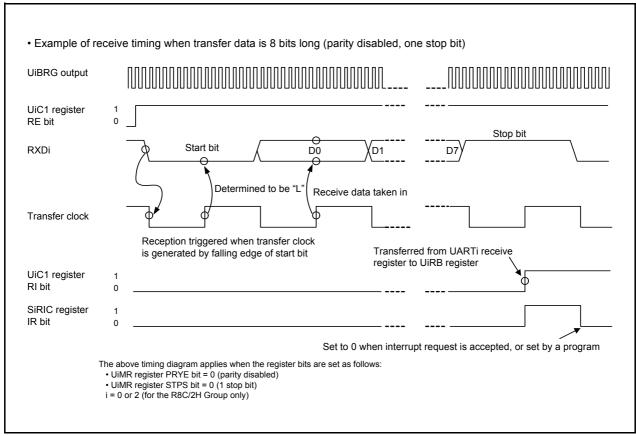

| 18.2      | Clock Asynchronous Serial I/O (UART) Mode      | 236 |

| 18.2.1    | Bit Rate                                       | 240 |

| 18.3      | Notes on Serial Interface                      | 241 |

|           |                                                |     |

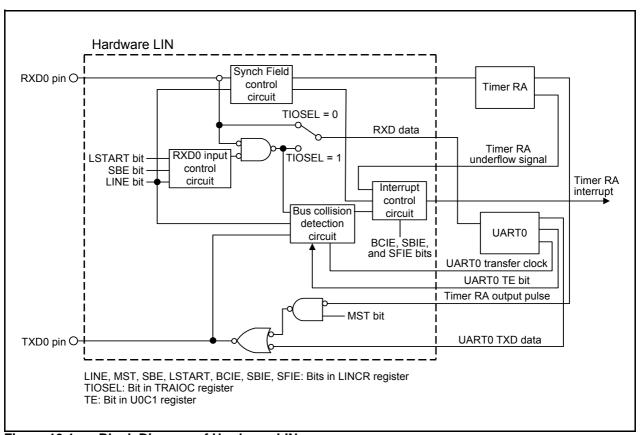

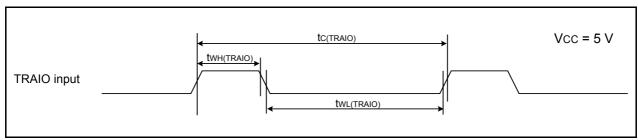

| 19. Hard  | lware LIN                                      | 242 |

| 19.1 l    | Features                                       | 242 |

| 19.2      | nput/Output Pins                               | 243 |

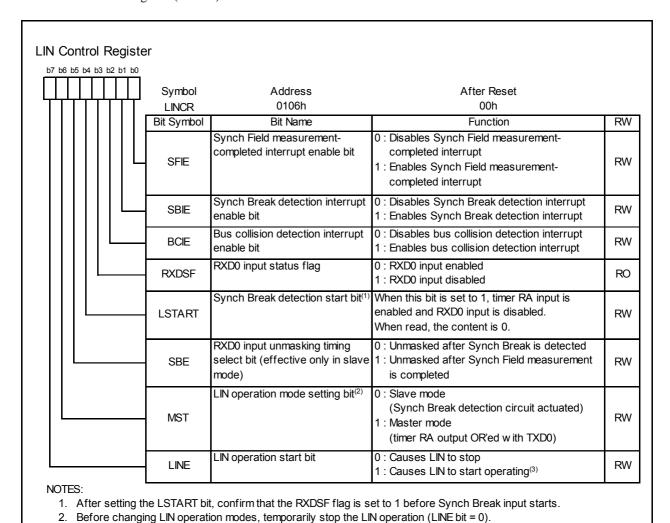

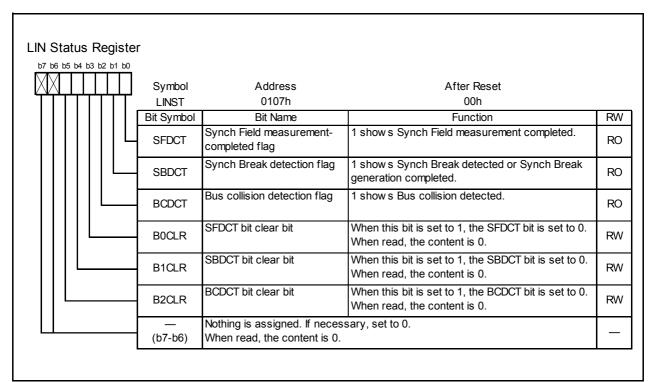

| 19.3 l    | Register Configuration                         | 244 |

| 19.4 l    | Functional Description                         | 246 |

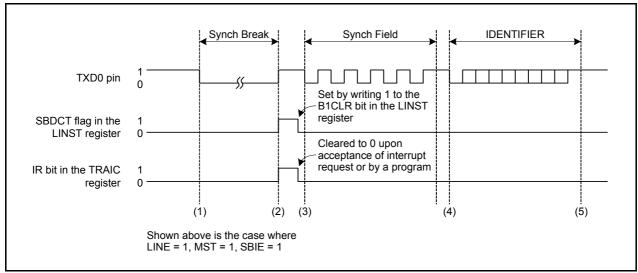

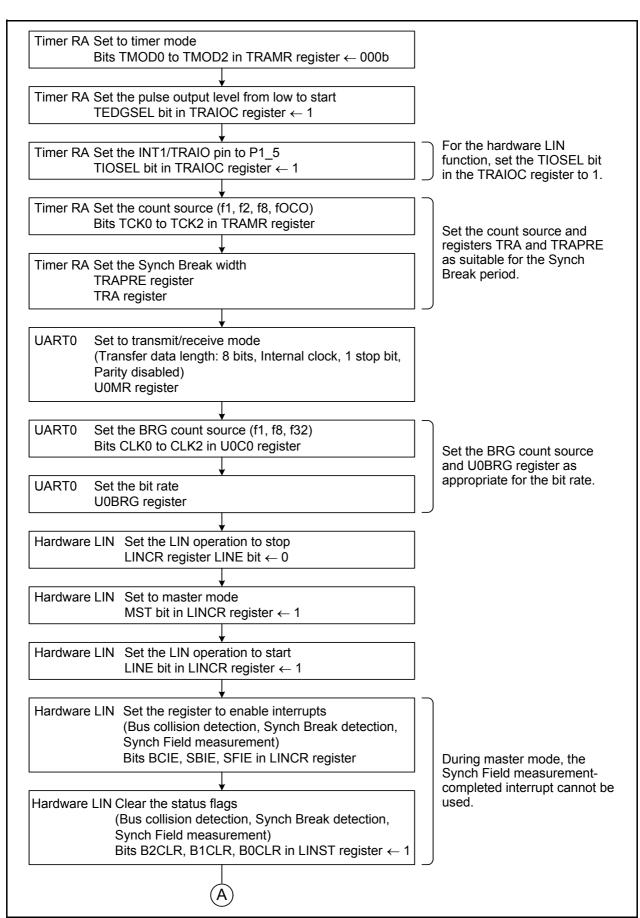

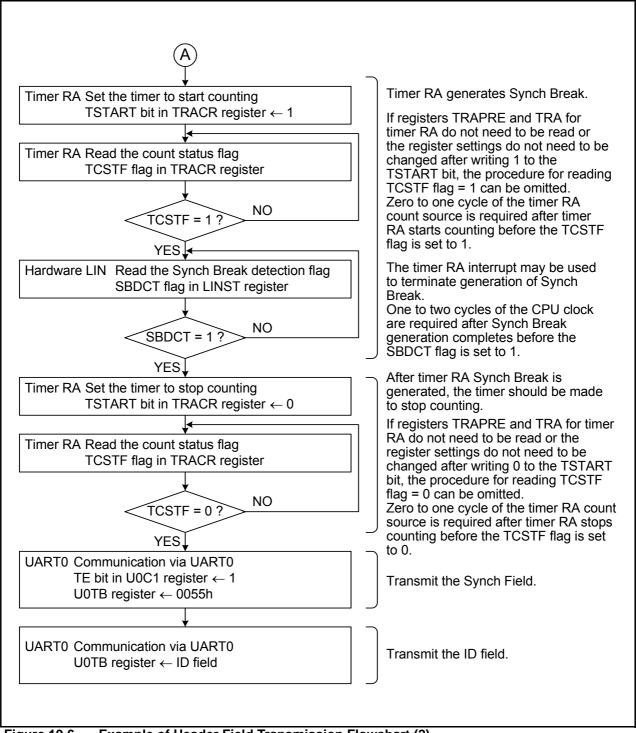

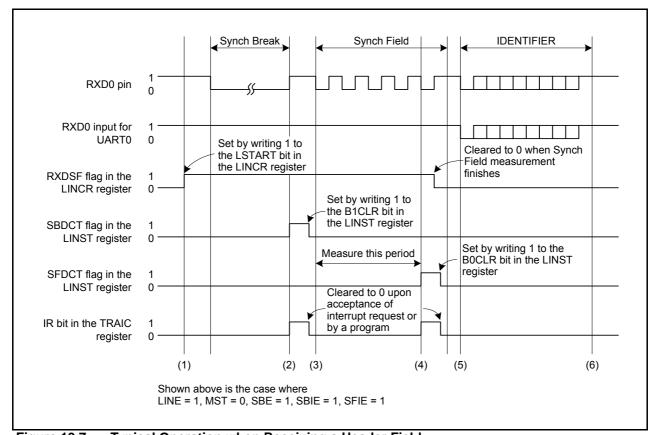

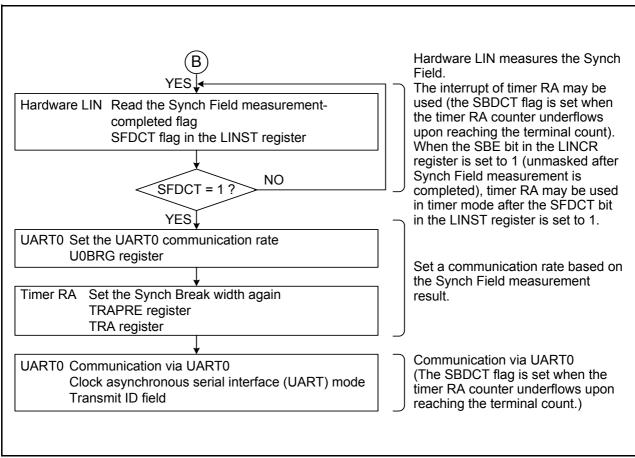

| 19.4.1    | Master Mode                                    | 246 |

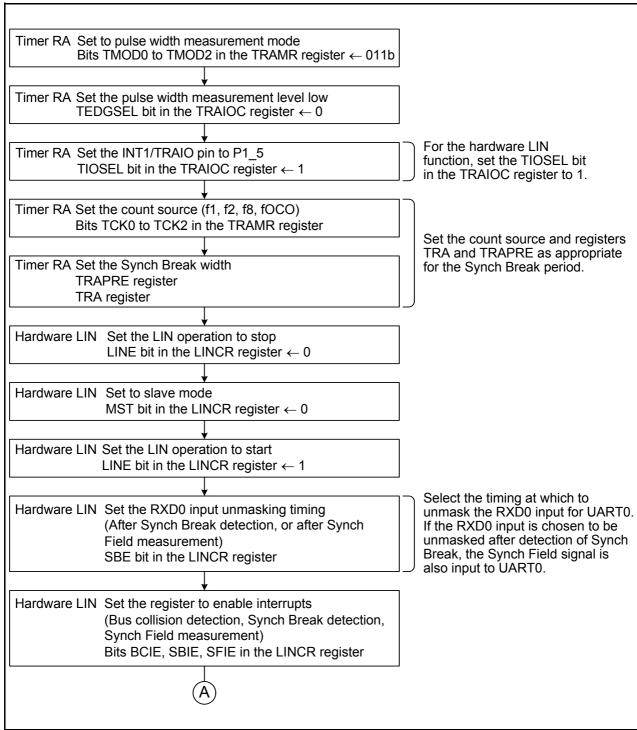

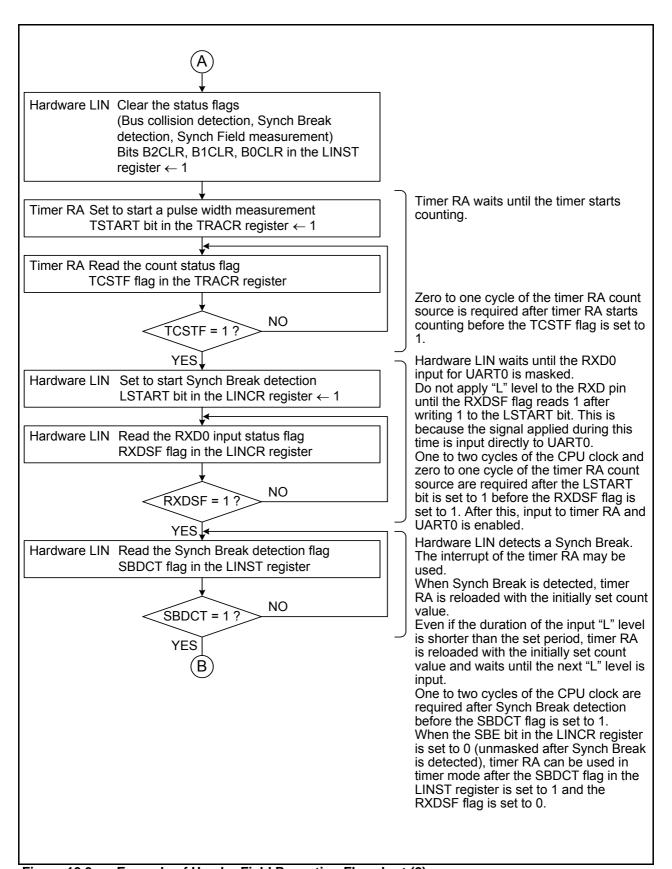

| 19.4.2    | Slave Mode                                     | 249 |

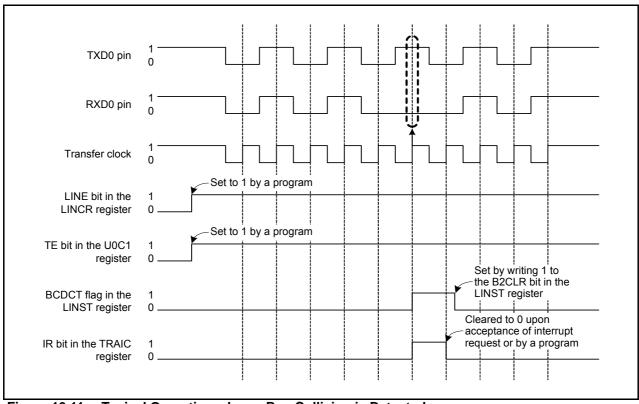

| 19.4.3    | Bus Collision Detection Function               | 253 |

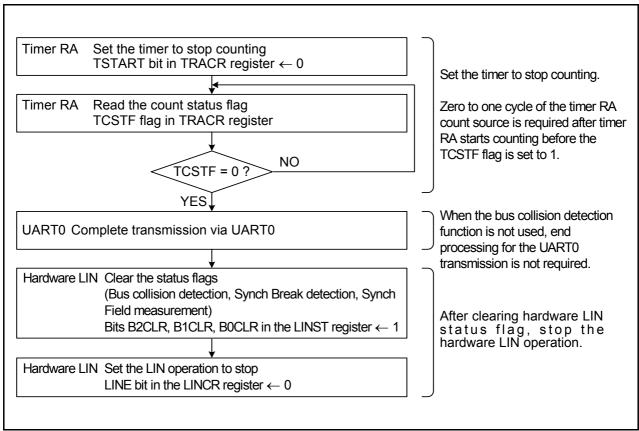

| 19.4.4    | Hardware LIN End Processing                    | 254 |

| 19.5      | nterrupt Requests                              | 255 |

| 19.6      | Notes on Hardware LIN                          | 256 |

| 00 Flac   | h Marsani.                                     | 257 |

|           | h Memory                                       |     |

|           | Overview                                       |     |

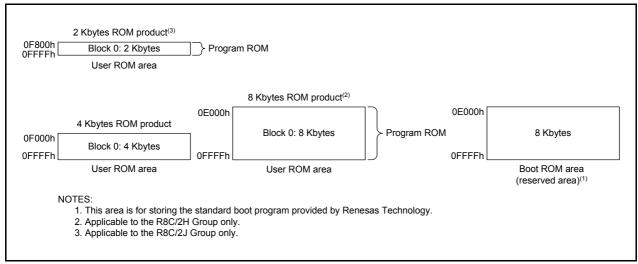

|           | Memory Map                                     |     |

|           | Functions to Prevent Rewriting of Flash Memory |     |

| 20.3.1    | ID Code Check Function                         |     |

| 20.3.2    | ROM Code Protect Function                      |     |

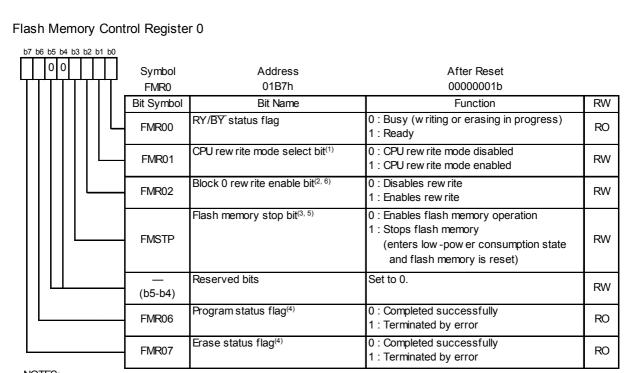

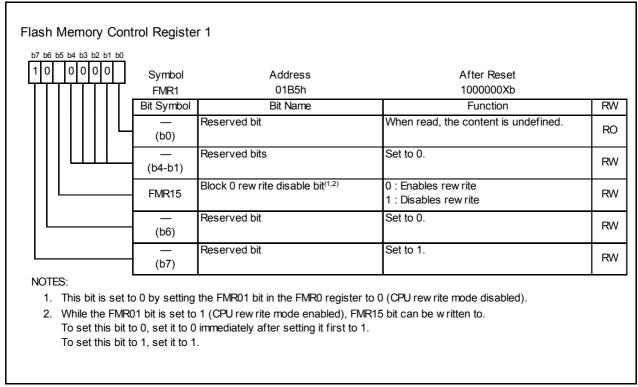

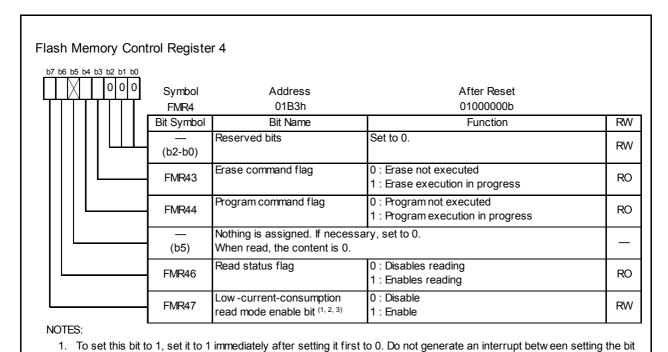

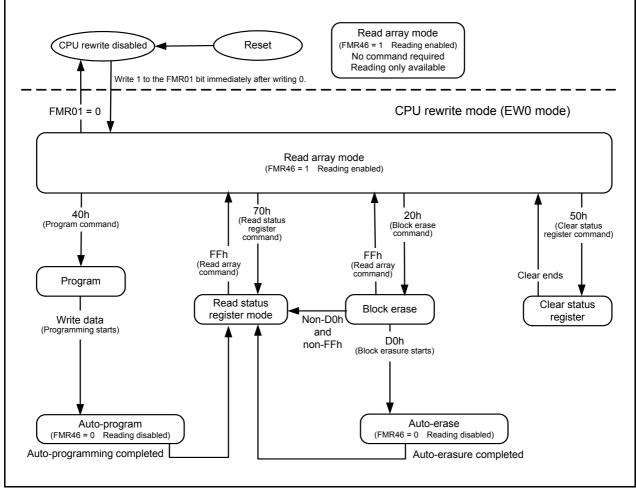

|           | CPU Rewrite Mode                               |     |

| 20.4.1    | Pagistar Description                           | 262 |

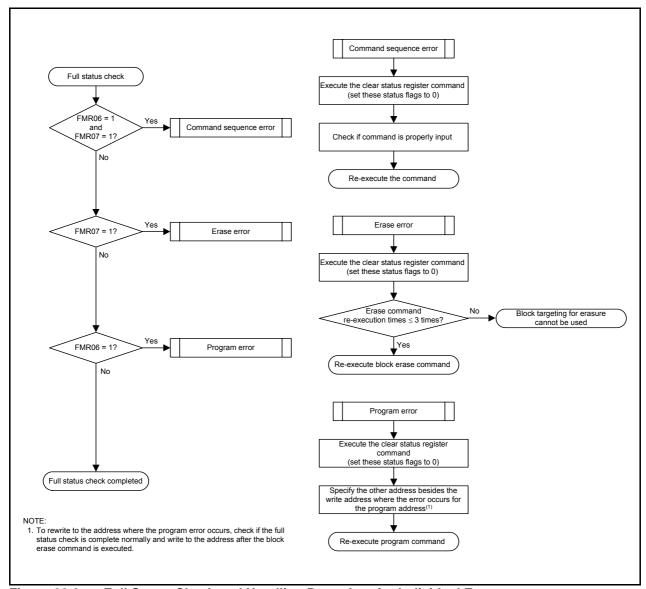

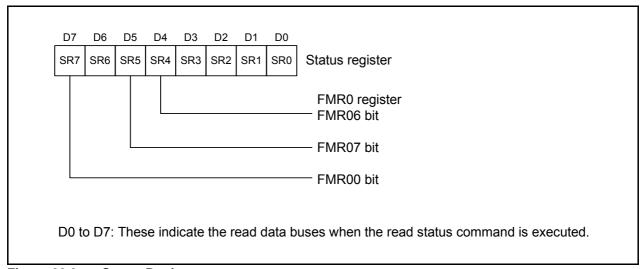

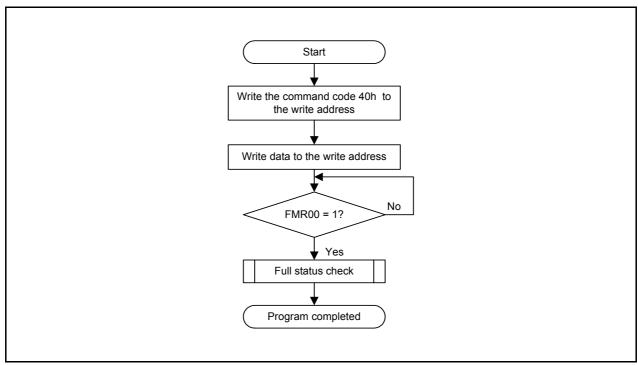

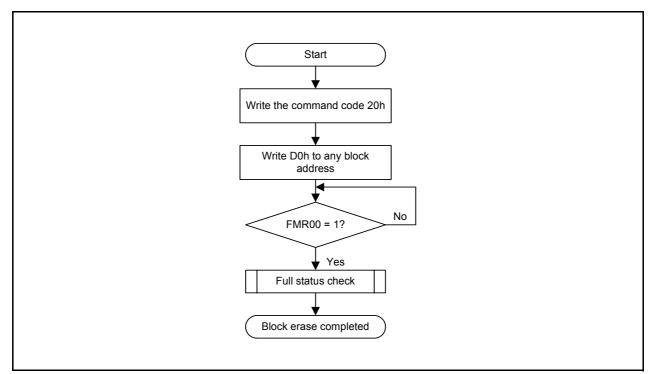

| 20.4.2  | Status Check Procedure                                           | 267 |

|---------|------------------------------------------------------------------|-----|

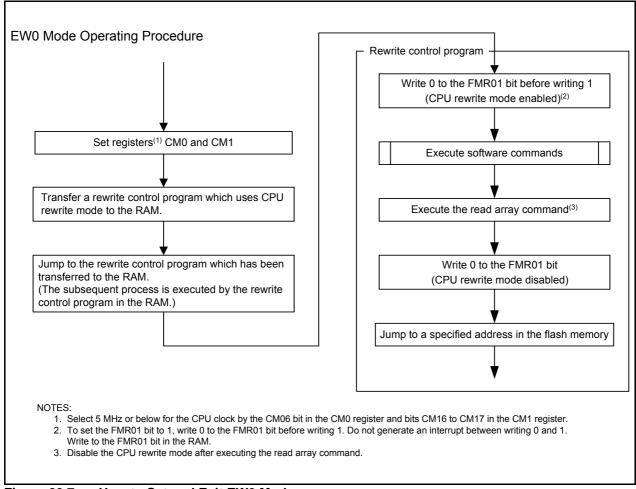

| 20.4.3  | EW0 Mode                                                         | 268 |

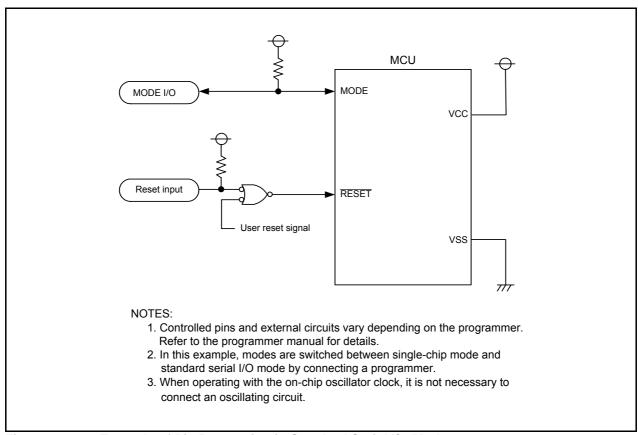

| 20.5    | Standard Serial I/O Mode                                         | 274 |

| 20.5.1  | ID Code Check Function                                           | 274 |

| 20.6    | Parallel I/O Mode                                                | 276 |

| 20.6.1  | ROM Code Protect Function                                        | 276 |

| 20.7    | Notes on Flash Memory                                            | 277 |

| 20.7.1  | CPU Rewrite Mode                                                 | 277 |

| 21. Red | ducing Power Consumption                                         | 278 |

| 21.1    | Overview                                                         | 278 |

| 21.2    | Key Points and Processing Methods for Reducing Power Consumption | 278 |

| 21.2.1  |                                                                  |     |

| 21.2.2  | Ports                                                            | 278 |

| 21.2.3  | Clocks                                                           | 278 |

| 21.2.4  | Selecting Oscillation Drive Capacity (for R8C/2H Group only)     | 278 |

| 21.2.5  |                                                                  |     |

| 21.2.6  | •                                                                |     |

| 21.2.7  |                                                                  |     |

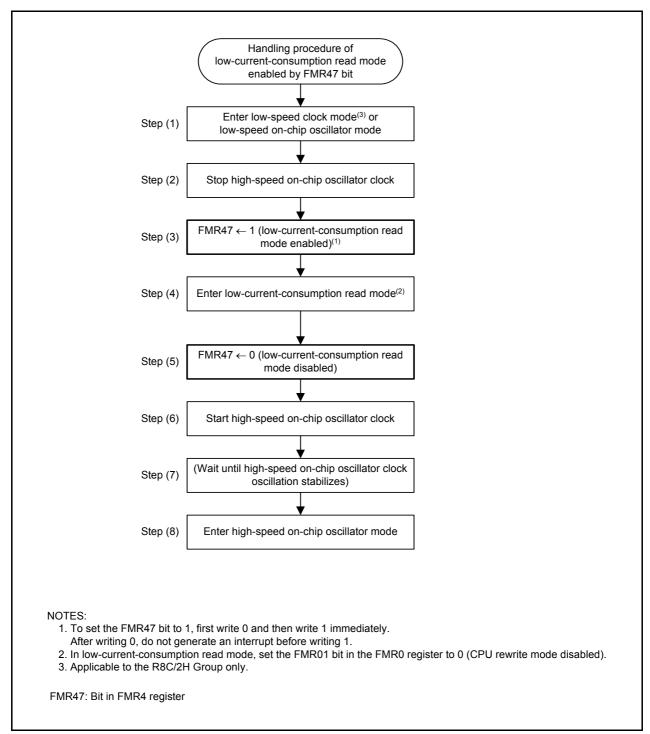

| 21.2.8  | Reducing Internal Power Consumption                              | 279 |

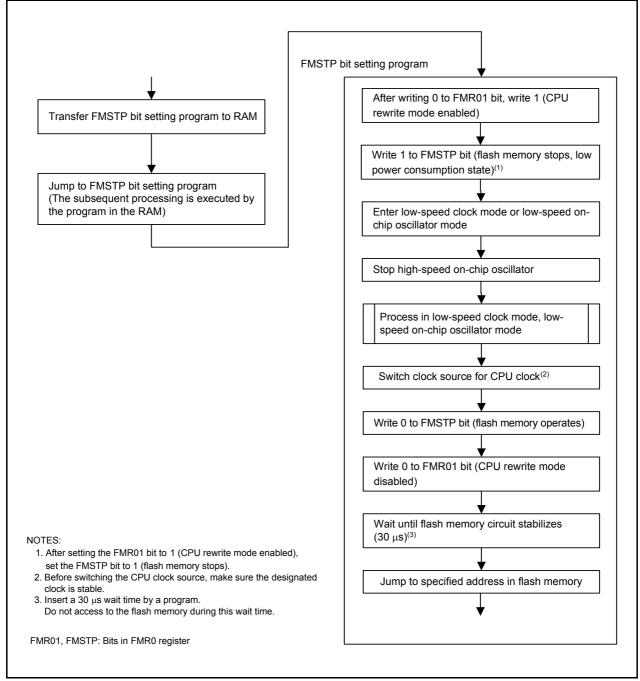

| 21.2.9  | Stopping Flash Memory                                            | 280 |

| 21.2.1  |                                                                  |     |

| 22. Ele | ctrical Characteristics                                          | 282 |

| 22.1    | R8C/2H Group                                                     |     |

| 22.2    | R8C/2J Group                                                     |     |

| 22.2    | 100/25 010up                                                     |     |

| 23. Usa | age Notes                                                        | 316 |

| 23.1    | Notes on I/O Ports                                               |     |

| 23.1.1  |                                                                  |     |

| 23.2    | Notes on Clock Generation Circuit                                |     |

| 23.2.1  |                                                                  |     |

| 23.2.2  | •                                                                |     |

| 23.2.3  |                                                                  |     |

| 23.3    | Notes on Interrupts                                              |     |

| 23.3.1  | •                                                                |     |

| 23.3.2  | e e e e e e e e e e e e e e e e e e e                            |     |

| 23.3.3  |                                                                  |     |

| 23.3.4  |                                                                  |     |

| 23.3.5  |                                                                  |     |

| 23.4    | Notes on ID Code Areas                                           |     |

| 23.4.1  |                                                                  |     |

| 23.5    | Notes on Option Function Select Area                             |     |

| 23.5.1  | Setting Example of Option Function Select Area                   |     |

| 23.6    | Notes on Timers                                                  |     |

| 23.6.1  | Notes on Timer RA                                                |     |

| 23.6.2  |                                                                  |     |

| 23.6.3  |                                                                  |     |

| 23.6.5  | • • •                                                            | 321 |

| 23.7     | Notes on Serial Interface                                                                              | 332 |

|----------|--------------------------------------------------------------------------------------------------------|-----|

| 23.8     | Notes on Hardware LIN                                                                                  | 333 |

| 23.9     | Notes on Flash Memory                                                                                  | 334 |

| 23.9.1   | CPU Rewrite Mode                                                                                       | 334 |

| 23.10    | Notes on Noise                                                                                         | 335 |

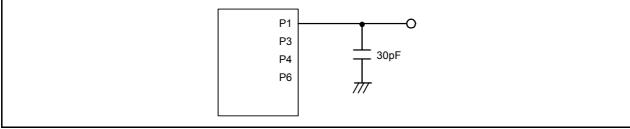

| 23.10.   | 1 Inserting a Bypass Capacitor between VCC and VSS Pins as a Countermeasure against Noise and Latch-up |     |

| 23.10.   | 2 Countermeasures against Noise Error of Port Control Registers                                        | 335 |

| 24. No   | tes for On-Chip Debugger                                                                               | 336 |

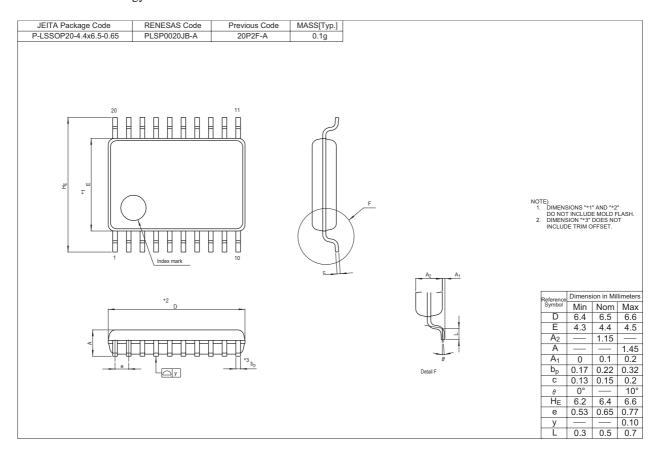

| Appendix | 1. Package Dimensions                                                                                  | 337 |

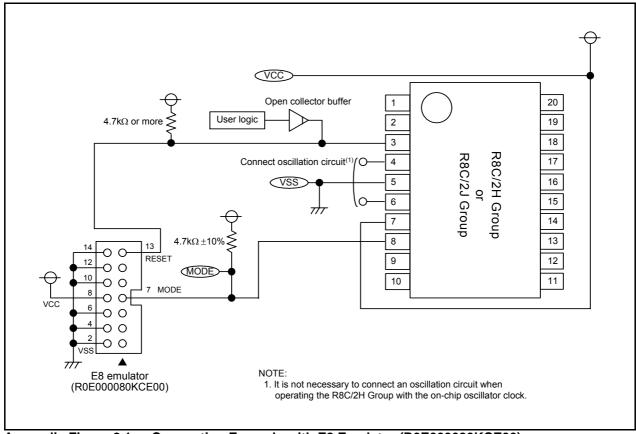

| Appendix | 2. Connection Examples with On-Chip Debugging Emulator                                                 | 338 |

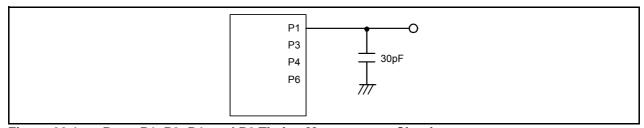

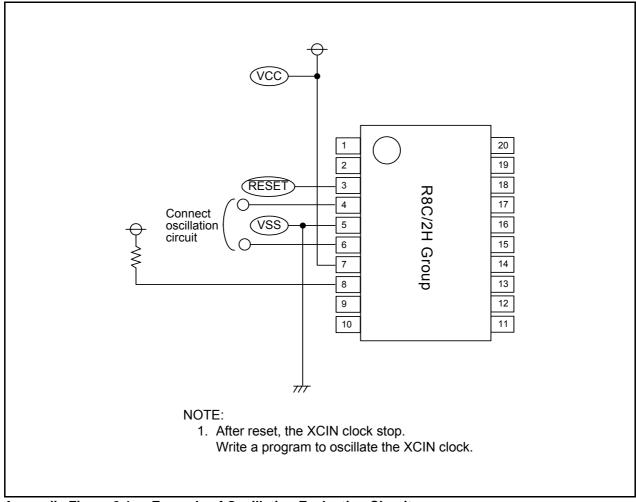

| Appendix | 3. Example of Oscillation Evaluation Circuit                                                           | 339 |

| Index    |                                                                                                        | 340 |

# **SFR Page Reference**

| 0000h   0001h   0002h   0002h   0002h   0002h   0002h   0002h   0002h   0006h   0006 | Address | Register                                          | Symbol    | Page   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------|-----------|--------|

| 0002h         Processor Mode Register 0         PM0         91           0005h         Processor Mode Register 1         PM1         91           0005h         Processor Mode Register 1         PM1         91           0007h         System Clock Control Register 1         CM0         96, 9           0008h         CM0         98, 9           0008h         CM1         98, 9           0009h         Protect Register         CM1           0009h         PRCR         117           0009h         Watchdog Timer Reset Register         WDTR         149           0000h         Watchdog Timer Reset Register         WDTS         149           000Ph         Watchdog Timer Start Register         WDC         150           000Ph         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0011h         Address Match Interrupt Register 1         RMAD1         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0015h         Gooth         RMAD1         137           0016h         Gooth         RMAD1         137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 1109.0101                                         | -,        | 1 3 -  |

| 0003h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0001h   |                                                   |           |        |

| 0004h         Processor Mode Register 0         PM0         91           0006h         System Clock Control Register 0         CM0         96, 9           0007h         System Clock Control Register 1         CM1         98, 9           0008h         System Clock Control Register 1         CM1         98, 9           0008h         DO009h         CM1         98, 9           0008h         DO000h         Protect Register         PRCR         117           0008h         DO000h         Walchdog Timer Reset Register         WDTS         149           0000h         Watchdog Timer Start Register         WDC         150           0007h         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0011h         Address Match Interrupt Register 1         RMAD1         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0015h         O016h         DO16h         DO16h         DO16h           0017h         O018h         DO16h         DO16h         DO16h           0018h         DO17h         DO16h         DO16h         DO16h         DO16h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0002h   |                                                   |           |        |

| 0005h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0003h   |                                                   |           |        |

| 0006h         System Clock Control Register 0         CM0         96, 9           0007h         System Clock Control Register 1         CM1         98, 9           0008h         0009h         CM1         98, 9           0000h         0000h         Protect Register         PRCR         117           0000h         System Clock Select Register(2)         OCD         100           0000h         Watchdog Timer Reset Register         WDTS         149           000FM         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0010h         Address Match Interrupt Register 1         RMAD1         137           0013h         Address Match Interrupt Register 1         RMAD1         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 1         RMAD1         137           0018h         Address Match Interrupt Register 1         RMAD1         137           0018h         Address Match Interrupt Register 1         RMAD1         137           0018h         Address Match Interrupt Register 2         CSPR         151           0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0004h   | · ·                                               |           | 91     |

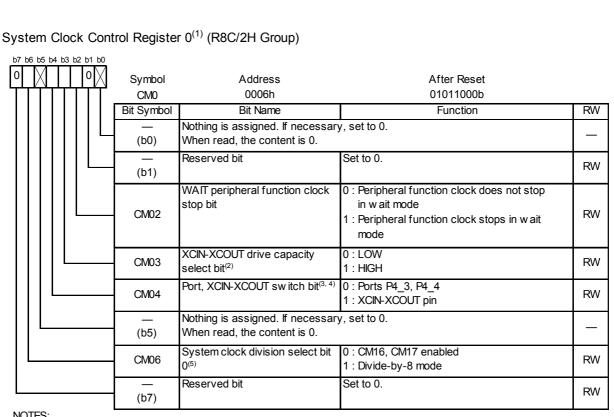

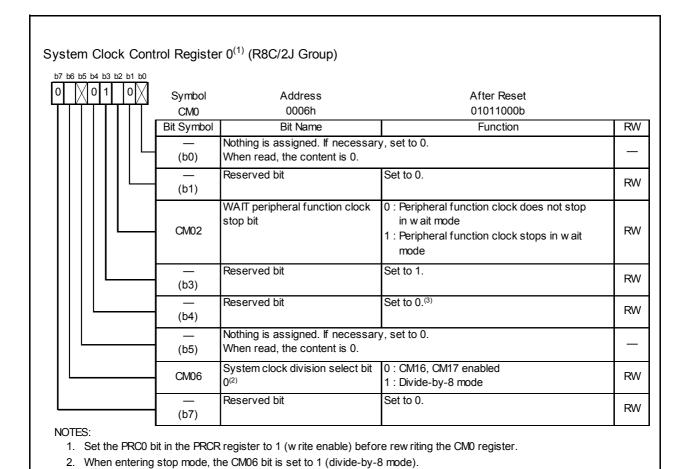

| 0007h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                   |           |        |

| 0008h         0009h           0000Ah         Protect Register         PRCR         117           000Bh         900Ch         System Clock Select Register         PCD         100           000Ch         Watchdog Timer Start Register         WDTS         149           000Eh         Watchdog Timer Start Register         WDC         150           0010h         Address Match Interrupt Register         WDC         150           0011h         Address Match Interrupt Register         AIER         137           0012h         Address Match Interrupt Register         AIER         137           0015h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 2         RMAD1         137           0015h         Address Match Interrupt Register 2         AIER         137           0015h         AIER         137         137           0015h         AIER         137         137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | <u> </u>                                          |           | 96, 97 |

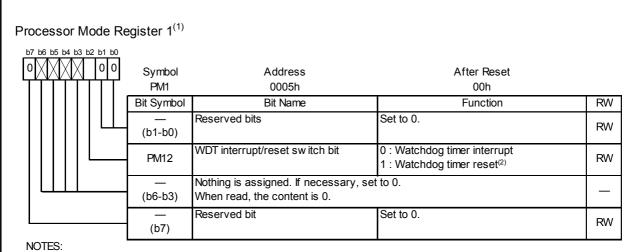

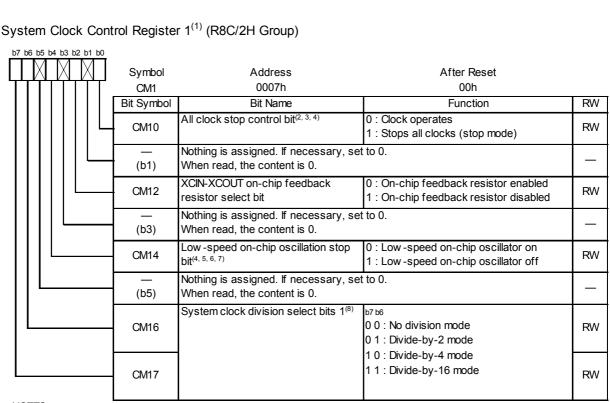

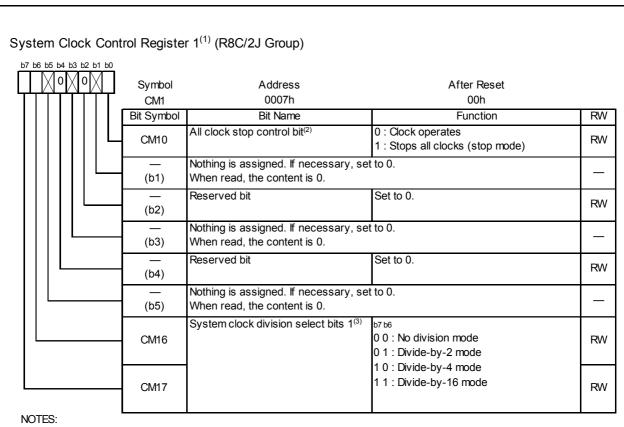

| 0009h   000Ah   000Ah   000Ah   000Ah   000Bh   000B |         | System Clock Control Register 1                   | CM1       | 98, 99 |

| 000Ah         Protect Register         PRCR         117           000Bh         900Ch         100           000Ch         System Clock Select Register         OCD         100           000Dh         Watchdog Timer Reset Register         WDTS         149           000Eh         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0013h         Address Match Interrupt Enable Register         AIER         137           0013h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 1         AIER         137           0015h         Address Match Interrupt Register Register Control Register 2         CSPR         151           0015h         O015h         AIER         137           0015h         O015h <td< td=""><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                                                   |           |        |

| 000Bh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | Destant Destintes                                 | DDOD      | 447    |

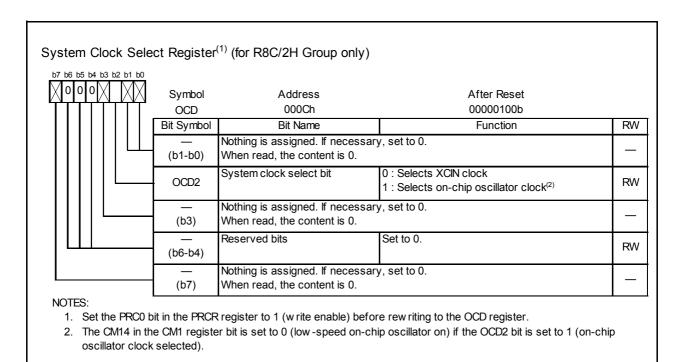

| 000Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | Protect Register                                  | PRCR      | 117    |

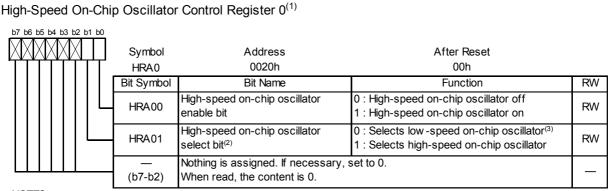

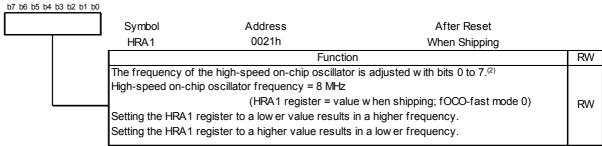

| 000Dh         Watchdog Timer Reset Register         WDTS         149           000Eh         Watchdog Timer Start Register         WDTS         149           000Fh         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0011h         Oddress Match Interrupt Register 1         AIER         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 1         AIER         137           0015h         AIER         AIER         137           0015h         AIER         AIER         137           0015h         AIER         AIER         137           0015h         High-Speed On-Chip Oscillator Control Registe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | System Cleak Salast Desister(2)                   | OCD       | 100    |

| 000Eh         Watchdog Timer Start Register         WDTS         149           000Fh         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0012h         Address Match Interrupt Register 1         AIER         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0015h         Address Match Interrupt Register 1         RMAD1         137           0016h         A017h         Address Match Interrupt Register 1         RMAD1         137           0018h         Address Match Interrupt Register 1         RMAD1         137           0018h         A019h         Address Match Interrupt Register 2         AIER         137           0018h         A019h         Address Match Interrupt Register 2         CSPR         151           0018h         A019h         Address Match Interrupt Register 2         CSPR         151           0018h         A019h         Address Match Interrupt Register 2         CSPR         151           0018h         A011h         Address Match Interrupt Register A Register 1         CSPR         151           0011ch         High-Speed On-Chip Oscillator Control Register 4         HRA0 <td></td> <td>-</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | -                                                 |           |        |

| 000Fh         Watchdog Timer Control Register         WDC         150           0010h         Address Match Interrupt Register 0         RMAD0         137           0011h         O012h         Address Match Interrupt Enable Register         AIER         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0014h         Address Match Interrupt Register 1         RMAD1         137           0015h         0016h         0017h         0018h         0018h           0014h         0018h         0014h         0018h         0014h           0014h         0014h         0014h         0014h         0014h           0015h         0016h         0016h         0016h         0016h           0016h         0016h         0016h         0016h         0016h           0017h         0016h         0016h         0016h         0016h           0016h         0017h         0020h         High-Speed On-Chip Oscillator Control Register 1         HRA0         101           0022h         High-Speed On-Chip Oscillator Control Register 4         102         102           0022h         O028h         0028h         102         102           0022h         High-Sp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                   |           |        |

| O010h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                   |           |        |

| 0011h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                   | _         |        |

| 0012h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                   |           |        |

| O014h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                   |           |        |

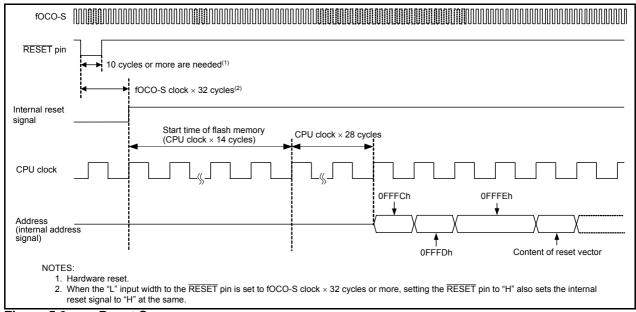

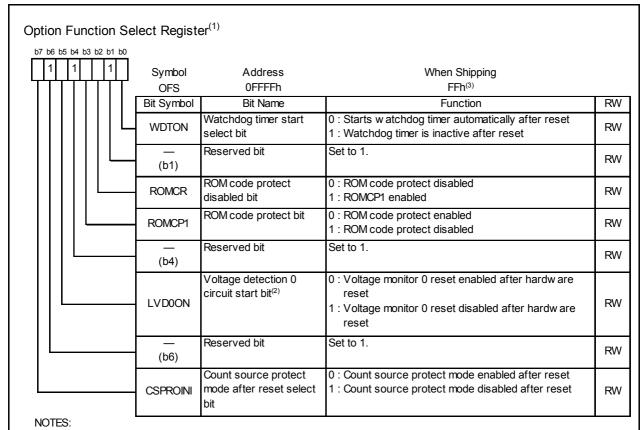

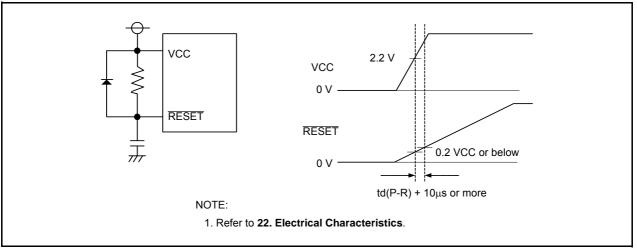

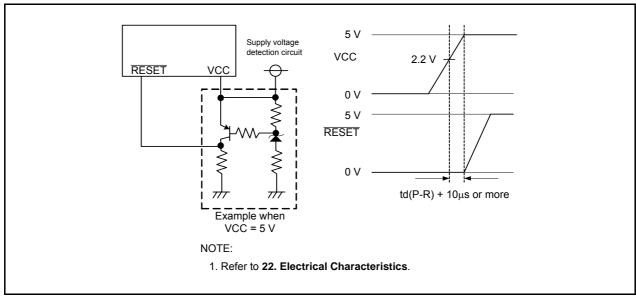

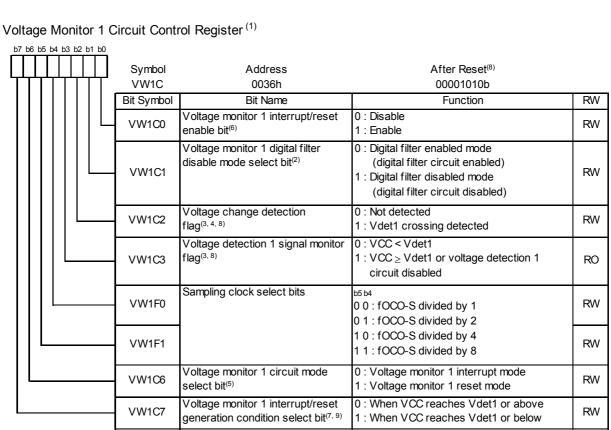

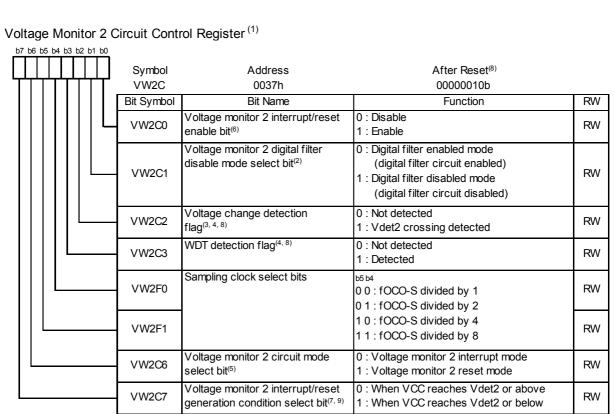

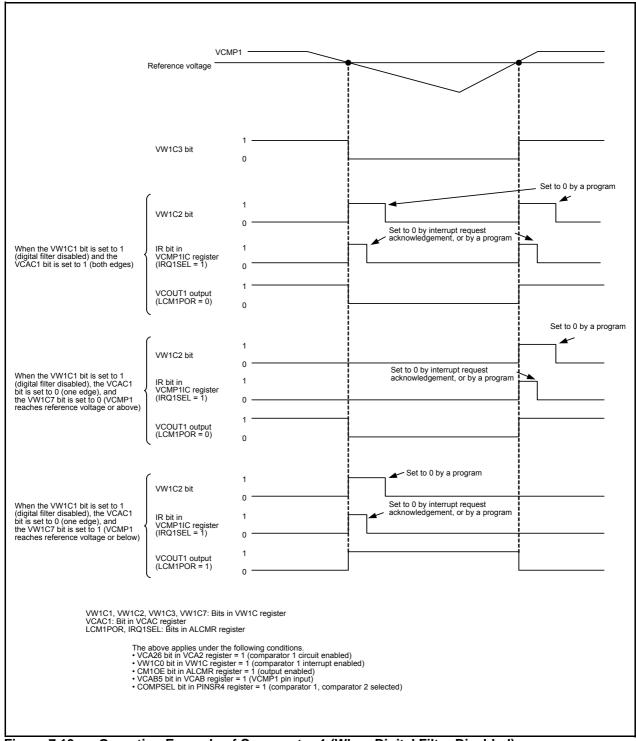

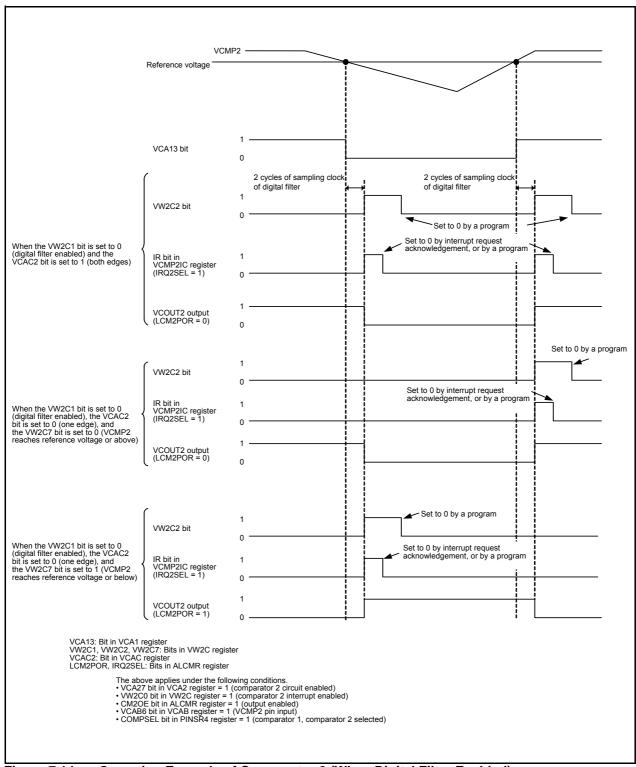

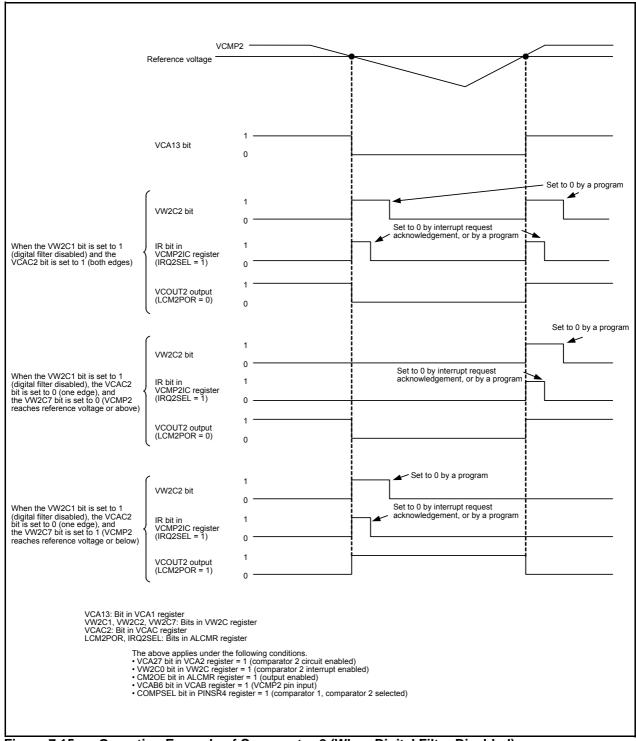

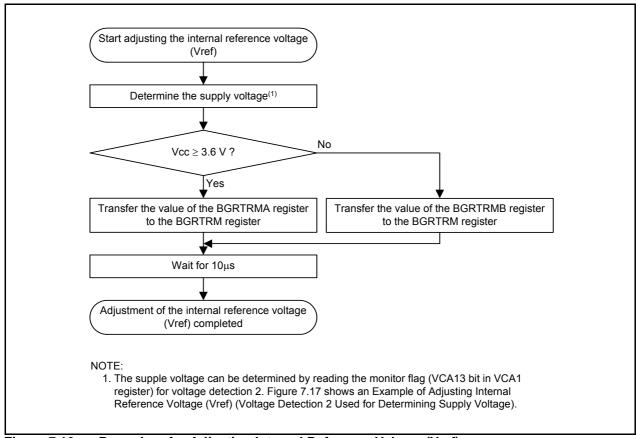

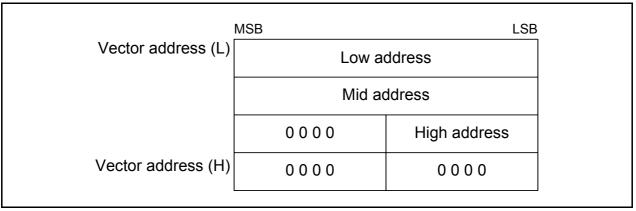

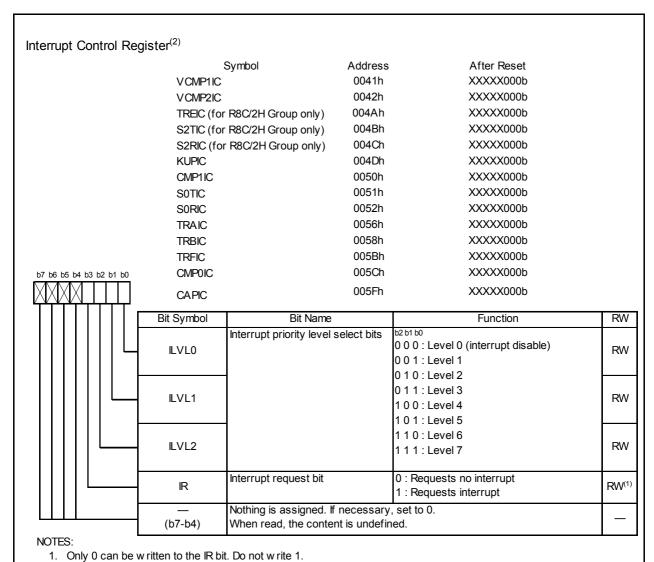

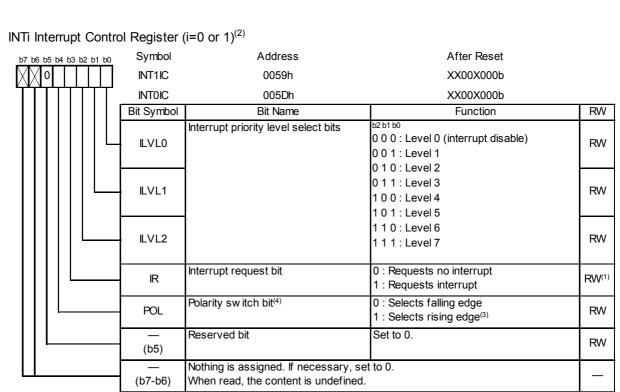

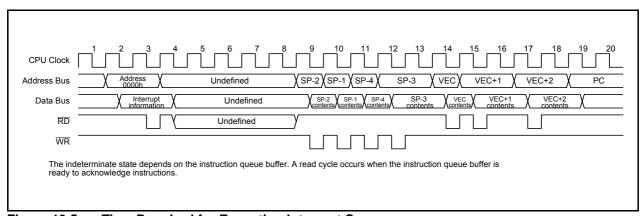

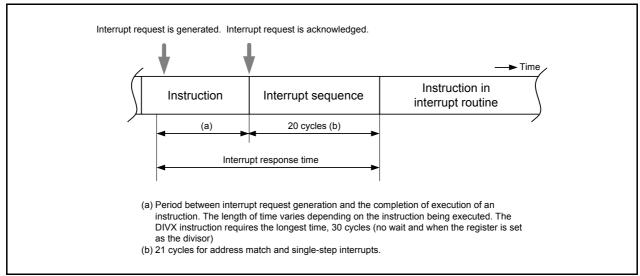

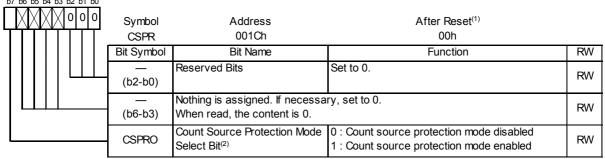

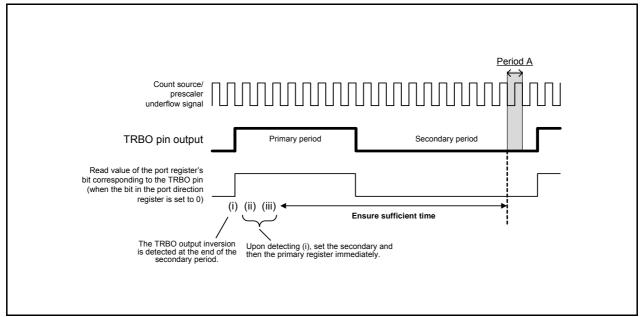

| 0014h         Address Match Interrupt Register 1         RMAD1         137           0016h         0016h         0017h         0018h         0019h           0019h         0014h         0019h         0016h         0016h         0016h           001Ch         Count Source Protection Mode Register         CSPR         151           001Dh         001Ch         Count Source Protection Mode Register         CSPR         151           001Dh         001Ch         Count Source Protection Mode Register         CSPR         151           001Dh         001Ch         Count Source Protection Mode Register         CSPR         151           001Dh         001Ch         001Ch         001Ch         001Ch         001Ch         001Ch         001Ch         001Ch         002Ch         002Ch <td< td=""><td>0013h</td><td>Address Match Interrupt Enable Register</td><td>AIER</td><td>137</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0013h   | Address Match Interrupt Enable Register           | AIER      | 137    |