# 18Mb Pipelined QDR™II SRAM Burst of 2

# *Advance Information IDT71P72204 IDT71P72104 IDT71P72804 IDT71P72604*

### Features

- 18Mb Density (2Mx8, 2Mx9, 1Mx18, 512kx36)

- Separate, Independent Read and Write Data Ports

Supports concurrent transactions

- Dual Echo Clock Output

- 2-Word Burst on all SRAM accesses

- DDR (Double Data Rate) Multiplexed Address Bus

- One Read and One Write request per clock cycle

- DDR (Double Data Rate) Data Buses

- Two word burst data per clock on each port

- Four word transfers per clock cycle (2 word bursts on 2 ports)

- Depth expansion through Control Logic

- HSTL (1.5V) inputs that can be scaled to receive signals from 1.4V to 1.9V.

- Scalable output drivers

- Can drive HSTL, 1.8V TTL or any voltage level from 1.4V to 1.9V.

- Output Impedance adjustable from 35 ohms to 70 ohms

- 1.8V Core Voltage (VDD)

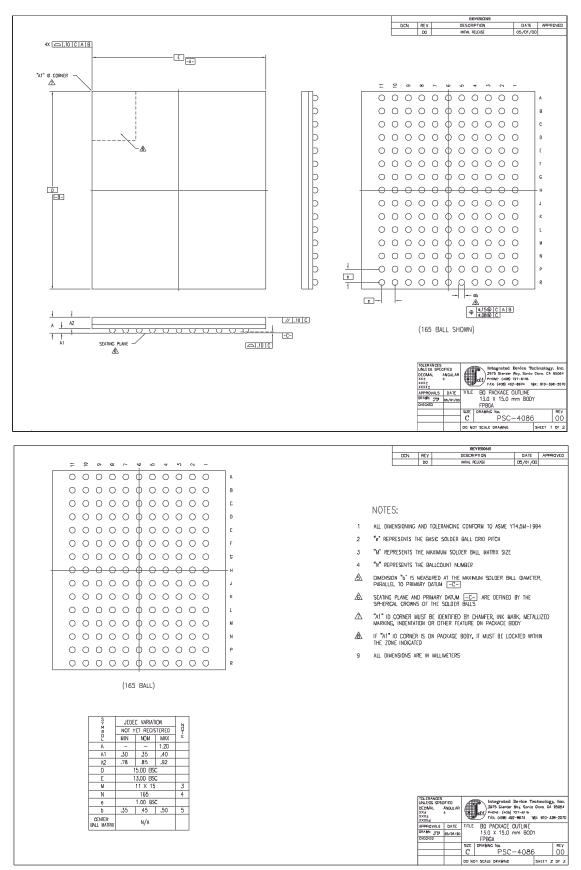

- 165-ball, 1.0mm pitch, 13mm x 15mm fBGA Package

- ♦ JTAG Interface

### Description

The IDT QDRII<sup>™</sup> Burst of two SRAMs are high-speed synchronous memories with independent, double-data-rate (DDR), read and write data ports. This scheme allows simultaneous read and write access for the maximum device throughput, with two data items passed with each read or write. Four data word transfers occur per clock cycle, providing quad-data-rate (QDR) performance. Comparing this with standard SRAM common I/O (CIO), single data rate (SDR) devices, a four to one increase in data access is achieved at equivalent clock speeds. Considering that QDRII allows clock speeds in excess of standard SRAM devices, the throughput can be increased well beyond four to one in most applications.

Using independent ports for read and write data access, simplifies system design by eliminating the need for bi-directional buses. All buses associated with the QDRII are unidirectional and can be optimized for signal integrity at very high bus speeds. The QDRII has scalable output impedance on its data output bus and echo clocks, allowing the user to tune the bus for low noise and high performance.

The QDRII has a single DDR address bus with multiplexed read and write addresses. All read addresses are received on the first half of the clock cycle and all write addresses are received on the second half of the clock cycle. The read and write enables are received on the first half of the clock cycle. The byte and nibble write signals are received on both halves of the clock cycle simultaneously with the data they are controlling on the data input bus.

The QDRII has echo clocks, which provide the user with a clock

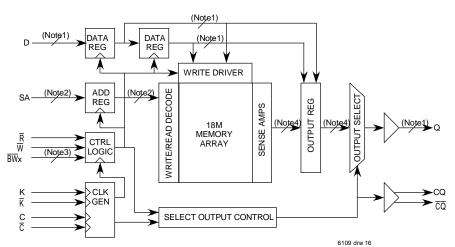

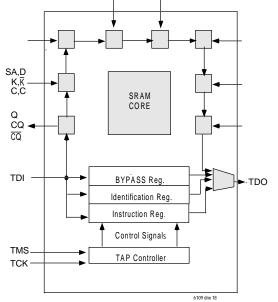

# **Functional Block Diagram**

Notes

- 1) Represents 8 data signal lines for x8, 9 signal lines for x9, 18 signal lines for x18, and 36 signal lines for x36

- 2) Represents 20 address signal lines for x8 and x9, 19 address signal lines for x18, and 18 address signal lines for x36.

- 3) Represents 1 signal line for x9, 2 signal lines for x18, and four signal lines for x36. On x8 parts, the BW is a "nibble write" and there are 2 signal lines.

- 4) Represents 16 data signal lines for x8, 18 signal lines for x9, 36 signal lines for x18, and 72 signal lines for x36.

**MAY 2004**

that is precisely timed to the data output, and tuned with matching impedance and signal quality. The user can use the echo clock for downstream clocking of the data. Echo clocks eliminate the need for the user to produce alternate clocks with precise timing, positioning, and signal qualities to guarantee data capture. Since the echo clocks are generated by the same source that drives the data output, the relationship to the data is not significantly affected by voltage, temperature and process, as would be the case if the clock were generated by an outside source.

All interfaces of the QDRII SRAM are HSTL, allowing speeds beyond SRAM devices that use any form of TTL interface. The interface can be scaled to higher voltages (up to 1.9V) to interface with 1.8V systems if necessary. The device has a  $V_{DD0}$  and a separate Vref, allowing the user to designate the interface operational voltage, independent of the device core voltage of 1.8V  $V_{DD}$ . The output impedance control allows the user to adjust the drive strength to adapt to a wide range of loads and transmission lines.

The device is capable of sustaining full bandwidth on both the input and output ports simultaneously. All data is in two word bursts, with addressing capability to the burst level.

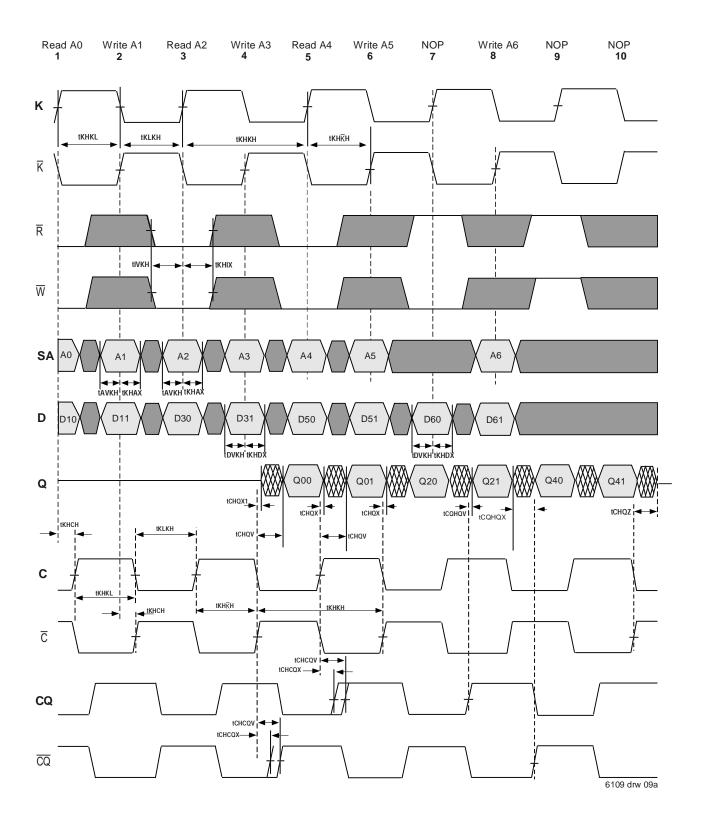

#### Clocking

The QDRII SRAM has two sets of input clocks, namely the K,  $\overline{K}$  clocks and the C,  $\overline{C}$  clocks. In addition, the QDRII has an output "echo" clock, CQ,  $\overline{CQ}$ .

The K and  $\overline{K}$  clocks are the primary device input clocks. The K clock is, used to clock in the control signals ( $\overline{R}$ ,  $\overline{W}$  and  $\overline{BWx}$  or  $\overline{NWx}$ ), the read address, and the first word of the data burst during a write operation. The  $\overline{K}$  clock is used to clock in the control signals ( $\overline{BWx}$  or  $\overline{NWx}$ ), write address and the second word of the data burst during a write operation. The K and  $\overline{K}$  clocks are also used internally by the SRAM. In the event that the user disables the C and  $\overline{C}$  clocks, the K and  $\overline{K}$  clocks will also be used to clock the data out of the output register and generate the echo clocks.

The C and  $\overline{C}$  clocks may be used to clock the data out of the output register during read operations and to generate the echo clocks. C and  $\overline{C}$  must be presented to the SRAM within the timing tolerances. The output data from the QDRII will be closely aligned to the C and  $\overline{C}$  input, through the use of an internal DLL. When C is presented to the QDRII SRAM, the DLL will have already internally clocked the first data word to arrive at the device output simultaneously with the arrival of the C clock.

The  $\overline{C}$  and second data word of the burst will also correspond.

### Single Clock Mode

The QDRII SRAM may be operated with a single clock pair. C and  $\overline{C}$  may be disabled by tying both signals high, forcing the outputs and echo clocks to be controlled instead by the K and  $\overline{K}$  clocks.

### **DLL Operation**

The DLL in the output structure of the QDRII SRAM can be used to closely align the incoming clocks C and  $\overline{C}$  with the output of the data, generating very tight tolerances between the two. The user may disable the DLL by holding  $\overline{\text{Doff}}$  low. With the DLL off, the C and  $\overline{C}$  (or K and  $\overline{K}$  if C and  $\overline{C}$  are not used) will directly clock the output register of the SRAM. With the DLL off, there will be a propagation delay from the time the clock enters the device until the data appears at the output.

### Echo Clock

The echo clocks, CQ and  $\overline{CQ}$ , are generated by the C and  $\overline{C}$  clocks (or K,  $\overline{K}$  if C,  $\overline{C}$  are disabled). The rising edge of C generates the rising edge of CQ, and the falling edge of  $\overline{CQ}$ . The rising edge of  $\overline{C}$  generates the rising edge of  $\overline{CQ}$  and the falling edge of CQ. This scheme improves the correlation of the rising and falling edges of the echo clock and will improve the duty cycle of the individual signals.

The echo clock is very closely aligned with the data, guaranteeing that the echo clock will remain closely correlated with the data, within the tolerances designated.

### **Read and Write Operations**

QDRII devices internally store the two words of the burst as a single, wide word and will retain their order in the burst. There is no ability to address to the single word level or reverse the burst order; however, the byte and nibble write signals can be used to prevent writing any individual bytes, or combined to prevent writing one word of the burst.

Read operations are initiated by holding the read port select ( $\overline{R}$ ) low, and presenting the read address to the address port during the rising edge of K which will latch the address. The data will then be read and will appear at the device output at the designated time in correspondence with the C and  $\overline{C}$  clocks.

Write operations are initiated by holding the write port select ( $\overline{W}$ ) low and designating with the Byte Write inputs ( $\overline{BWx}$ ) which bytes are to be written (or  $\overline{NWx}$  on x8 devices). The first word of the data must also be present on the data input bus D[X:0]. Upon the rising edge of K the first word of the burst will be latched into the input register. After K has risen, and the designated hold times observed, the second half of the clock cycle is initiated by presenting the write address to the address bus SA[X:0], the  $\overline{BWx}$  (or  $\overline{NWx}$ ) inputs for the second data word of the burst, and the second data item of the burst to the data bus D[X:0]. Upon the rising edge of  $\overline{K}$ , the second word of the burst will be latched, along with the designated address. Both the first and second words of the burst will then be written into memory as designated by the address and byte write enables.

### **Output Enables**

The QDRII SRAM automatically enables and disables the Q[X:0] outputs. When a valid read is in progress, and data is present at the output, the output will be enabled. If no valid data is present at the output (read not active), the output will be disabled (high impedance). The echo clocks will remain valid at all times and cannot be disabled or turned off. During power-up the Q outputs will come up in a high impedance state.

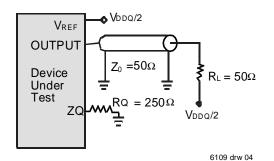

### Programmable Impedance

An external resistor, RQ, must be connected between the ZQ pin on the SRAM and Vss to allow the SRAM to adjust its output drive impedance. The value of RQ must be 5X the value of the intended drive impedance of the SRAM. The allowable range of RQ to guarantee impedance matching with a tolerance of +/- 10% is between 175 ohms and 350 ohms, with V<sub>DDQ</sub> = 1.5V. The output impedance is adjusted every 1024 clock cycles to correct for drifts in supply voltage and temperature. If the user wishes to drive the output impedance of the SRAM to it's lowest value, the ZQ pin may be tied to V<sub>DDQ</sub>.

# **Pin Definitions**

| Symbol                                       | Pin Function          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[X:0]                                       | Input<br>Synchronous  | Data input signals, sampled on the rising edge of K and $\overline{K}$ clocks during valid write operations 2M x 8 D[7:0]<br>2M x 9 D[8:0]<br>1M x 18 D[17:0]<br>512K x 36 D[35:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <u>₿₩</u> 0, <u>₿₩</u> 1<br><u>₿₩2, ₿₩</u> 3 | Input<br>Synchronous  | Byte Write Select 0, 1, 2, and 3 are active LOW. Sampled on the rising edge of the K and again on the rising edge of $\overline{K}$ clocks during write operations. Used to select which byte is written into the device during the current portion of the write operations. Bytes not written remain unaltered. All the byte writes are sampled on the same edge as the data. Deselecting a Byte Write Select will cause the corresponding byte of data to be ignored and not written in to the device.<br>$2M \times 9 - \overline{BW0}$ controls D[8:0]<br>$1M \times 18 - \overline{BW0}$ controls D[8:0] and $\overline{BW1}$ controls D[17:9]<br>$512K \times 36 - \overline{BW0}$ controls D[8:0], $\overline{BW1}$ controls D[17:9], $\overline{BW2}$ controls D[26:18] and $\overline{BW3}$ controls D[35:27] |

| <u>NW</u> 0, <u>NW</u> 1                     | Input<br>Synchronous  | Nibble Write Select 0 and 1 are active LOW. Available only on x8 bit parts instead of Byte Write Selects. Sampled on the rising edge of the K and $\bar{K}$ clocks during write operations. Used to select which nibble is written into the device during the current portion of the write operations. Nibbles not written remain unaltered. All the nibble writes are sampled on the same edge as the data. Deselecting a Nibble Write Select will cause the corresponding nibble of data to be ignored and not written in to the device.                                                                                                                                                                                                                                                                             |

| SA                                           | Input<br>Synchronous  | Address Inputs. Read addresses are sampled on the rising edge of K clock during active read operations. Write addresses are sampled on the rising edge of $\overline{K}$ clock during active write operations. These address inputs are multiplxed, so that both a read and write operation can occur on the same clock cycle. These inputs are ignored when the appropriate port is deselected.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Q[X:0]                                       | Output<br>Synchronous | Data Output signals. These pins drive out the requested data during a Read operation. Valid data is driven out on the rising edge of both the C and $\overline{C}$ clocks during Read operations or K and $\overline{K}$ when operating in single clock mode. When the Read port is deselected, Q[X:0] are automatically three-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| W                                            | Input<br>Synchronous  | Write Control Logic active Low. Sampled on the rising edge of the positive input clock (K). When asserted active, a write operation in initiated. Deasserting will deselect the Write port. Deselecting the Write port will cause D[X:0] to be ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| R                                            | Input<br>Synchronous  | Read Control Logic, active LOW. Sampled on the rising edge of Positive Input Clock (K). When active, a Read operation is initiated. Deasserting will cause the Read port to be deselected. When deselected, the pending access is allowed to complete and the output drivers are automatically three-stated following the next rising edge of the C clock. Each read access consists of a burst of two sequential transfer.                                                                                                                                                                                                                                                                                                                                                                                            |

| С                                            | Input Clock           | Positive Output Clock Input. C is used in conjunction with $\overline{C}$ to clock out the Read data from the device. C and $\overline{C}$ can be used together to deskew the flight times of various devices on the board back to the controller. See application example for further details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ē                                            | Input Clock           | Negative Output Clock Input. $\overline{C}$ is used in conjunction with C to clock out the Read data from the device. C and $\overline{C}$ can be used together to deskew the flight times of various devices on the board back to the controller. See application example for further details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| К                                            | Input Clock           | Positive Input Clock Input. The rising edge of K is used to capture synchronous inputs to the device and to drive out data through Q[X:0] when in single clock mode. All accesses are initiated on the rising edge of K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ĸ                                            | Input Clock           | Negative Input Clock Input. $\overline{K}$ is used to capture synchronous inputs being presented to the device and to drive out data through Q[X:0] when in single clock mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CQ, <u>CQ</u>                                | Output Clock          | Synchronous Echo clock outputs. The rising edges of these outputs are tightly matched to the synchronous data outputs and can be used as a data valid indication. These signals are free running and do not stop when the output data is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ZQ                                           | Input                 | Output Impedance Matching Input. This input is used to tune the device outputs to the system data bus impedance. Q[X:0] output impedance is set to 0.2 x RQ, where RQ is a resistor connected between ZQ and ground. Alternately, this pin can be connected directly to VDDQ, which enables the minimum impedance mode. This pin cannot be connected directly to GND or left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Pin Definitions continued**

| Symbol | Pin Function       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Doff   | Input              | DLL Turn Off. When low this input will turn off the DLL inside the device. The AC timings with the DLL turned off will be different from those listed in this data sheet. There will be an increased propagation delay from the incidence of C and $\overline{C}$ to Q, or K and $\overline{K}$ to Q as configured. The propagation delay is not a tested parameter, but will be similar to the propagation delay of other SRAM devices in this speed grade. |

| TDO    | Output             | TDO pin for JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ТСК    | Input              | TCK pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TDI    | Input              | TDI pin for JTAG. An internal resistor will pull TDI to $V_{DD}$ when the pin is unconnected.                                                                                                                                                                                                                                                                                                                                                                |

| ™S     | Input              | TMS pin for JTAG. An internal resistor will pull TMS to VDD when the pin is unconnected.                                                                                                                                                                                                                                                                                                                                                                     |

| NC     | No Connect         | No connects inside the package. Can be tied to any voltage level                                                                                                                                                                                                                                                                                                                                                                                             |

| Vref   | Input<br>Reference | Reference Voltage input. Static input used to set the reference level for HSTL inputs and<br>Outputs as well as AC measurement points.                                                                                                                                                                                                                                                                                                                       |

| Vdd    | Power<br>Supply    | Power supply inputs to the core of the device. Should be connected to a 1.8V power supply.                                                                                                                                                                                                                                                                                                                                                                   |

| Vss    | Ground             | Ground for the device. Should be connected to ground of the system.                                                                                                                                                                                                                                                                                                                                                                                          |

| VDDQ   | Power<br>Supply    | Power supply for the outputs of the device. Should be connected to a 1.5V power supply for HSTL or scaled to the desired output voltage.                                                                                                                                                                                                                                                                                                                     |

6109 tbl 02b

# **Pin Configuration 2M x 8**

|   | 1    | 2                         | 3    | 4    | 5               | 6   | 7               | 8    | 9    | 10                        | 11  |

|---|------|---------------------------|------|------|-----------------|-----|-----------------|------|------|---------------------------|-----|

| A | CQ   | Vss/<br>SA <sup>(2)</sup> | SA   | W    | NW1             | K   | NC              | R    | SA   | Vss/<br>SA <sup>(1)</sup> | CQ  |

| В | NC   | NC                        | NC   | SA   | NC              | К   | ₩0              | SA   | NC   | NC                        | Q3  |

| с | NC   | NC                        | NC   | Vss  | SA              | SA  | SA              | Vss  | NC   | NC                        | D3  |

| D | NC   | D4                        | NC   | Vss  | Vss             | Vss | Vss             | Vss  | NC   | NC                        | NC  |

| E | NC   | NC                        | Q4   | VDDQ | Vss             | Vss | Vss             | VDDQ | NC   | D2                        | Q2  |

| F | NC   | NC                        | NC   | VDDQ | Vdd             | Vss | Vdd             | VDDQ | NC   | NC                        | NC  |

| G | NC   | D5                        | Q5   | VDDQ | Vdd             | Vss | Vdd             | Vddq | NC   | NC                        | NC  |

| н | Doff | Vref                      | VDDQ | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | VDDQ | Vref                      | ZQ  |

| J | NC   | NC                        | NC   | VDDQ | Vdd             | Vss | Vdd             | Vddq | NC   | Q1                        | D1  |

| к | NC   | NC                        | NC   | VDDQ | Vdd             | Vss | Vdd             | VDDQ | NC   | NC                        | NC  |

| L | NC   | Q6                        | D6   | VDDQ | Vss             | Vss | Vss             | Vddq | NC   | NC                        | Q0  |

| м | NC   | NC                        | NC   | Vss  | Vss             | Vss | Vss             | Vss  | NC   | NC                        | Do  |

| N | NC   | D7                        | NC   | Vss  | SA              | SA  | SA              | Vss  | NC   | NC                        | NC  |

| Р | NC   | NC                        | Q7   | SA   | SA              | С   | SA              | SA   | NC   | NC                        | NC  |

| R | TDO  | TCK                       | SA   | SA   | SA              | Ē   | SA              | SA   | SA   | TMS                       | TDI |

6109 tbl 12

# 165-ball FBGA Pinout TOP VIEW

#### NOTES:

1. A10 is reserved for the 36Mb expansion address.

2. A2 is reserved for the 72Mb expansion address.

# Pin Configuration 2M x 9

|   | 1    | 2                         | 3    | 4    | 5   | 6   | 7   | 8    | 9    | 10                        | 11             |

|---|------|---------------------------|------|------|-----|-----|-----|------|------|---------------------------|----------------|

| A | CQ   | Vss/<br>SA <sup>(2)</sup> | SA   | W    | NC  | K   | NC  | R    | SA   | Vss/<br>SA <sup>(1)</sup> | CQ             |

| в | NC   | NC                        | NC   | SA   | NC  | К   | ₿W  | SA   | NC   | NC                        | Q3             |

| С | NC   | NC                        | NC   | Vss  | SA  | SA  | SA  | Vss  | NC   | NC                        | D3             |

| D | NC   | D4                        | NC   | Vss  | Vss | Vss | Vss | Vss  | NC   | NC                        | NC             |

| E | NC   | NC                        | Q4   | VDDQ | Vss | Vss | Vss | VDDQ | NC   | D2                        | Q2             |

| F | NC   | NC                        | NC   | VDDQ | Vdd | Vss | Vdd | VDDQ | NC   | NC                        | NC             |

| G | NC   | D5                        | Q5   | VDDQ | Vdd | Vss | Vdd | VDDQ | NC   | NC                        | NC             |

| н | Doff | Vref                      | VDDQ | VDDQ | Vdd | Vss | Vdd | VDDQ | VDDQ | Vref                      | ZQ             |

| J | NC   | NC                        | NC   | VDDQ | Vdd | Vss | Vdd | VDDQ | NC   | Q1                        | D1             |

| к | NC   | NC                        | NC   | VDDQ | Vdd | Vss | Vdd | VDDQ | NC   | NC                        | NC             |

| L | NC   | Q6                        | D6   | VDDQ | Vss | Vss | Vss | VDDQ | NC   | NC                        | Q <sub>0</sub> |

| м | NC   | NC                        | NC   | Vss  | Vss | Vss | Vss | Vss  | NC   | NC                        | D0             |

| N | NC   | D7                        | NC   | Vss  | SA  | SA  | SA  | Vss  | NC   | NC                        | NC             |

| Р | NC   | NC                        | Q7   | SA   | SA  | С   | SA  | SA   | NC   | D8                        | Q8             |

| R | TDO  | TCK                       | SA   | SA   | SA  | Ē   | SA  | SA   | SA   | TMS                       | TDI            |

|   |      |                           |      |      |     |     |     |      |      | (100)                     |                |

6109 tb I 12a

# 165-ball FBGA Pinout TOP VIEW

#### NOTES:

1. A10 is reserved for the 36Mb expansion address.

2. A2 is reserved for the 72Mb expansion address.

## **Pin Configuration 1M x 18**

|   | 1    | 2                         | 3                        | 4    | 5           | 6   | 7           | 8    | 9    | 10                        | 11  |

|---|------|---------------------------|--------------------------|------|-------------|-----|-------------|------|------|---------------------------|-----|

| A | CQ   | Vss/<br>SA <sup>(3)</sup> | NC/<br>SA <sup>(1)</sup> | W    | <b>B</b> ₩1 | ĸ   | NC          | R    | SA   | Vss/<br>SA <sup>(2)</sup> | CQ  |

| в | NC   | Q9                        | D9                       | SA   | NC          | К   | <b>B</b> ₩₀ | SA   | NC   | NC                        | Q8  |

| С | NC   | NC                        | D10                      | Vss  | SA          | SA  | SA          | Vss  | NC   | Q7                        | D8  |

| D | NC   | D11                       | Q10                      | Vss  | Vss         | Vss | Vss         | Vss  | NC   | NC                        | D7  |

| E | NC   | NC                        | Q11                      | VDDQ | Vss         | Vss | Vss         | Vddq | NC   | D6                        | Q6  |

| F | NC   | Q12                       | D12                      | VDDQ | Vdd         | Vss | Vdd         | Vddq | NC   | NC                        | Q5  |

| G | NC   | D13                       | Q13                      | VDDQ | Vdd         | Vss | Vdd         | VDDQ | NC   | NC                        | D5  |

| н | Doff | Vref                      | VDDQ                     | VDDQ | Vdd         | Vss | Vdd         | VDDQ | VDDQ | Vref                      | ZQ  |

| J | NC   | NC                        | D14                      | VDDQ | Vdd         | Vss | Vdd         | VDDQ | NC   | Q4                        | D4  |

| K | NC   | NC                        | Q14                      | Vddq | Vdd         | Vss | Vdd         | Vddq | NC   | D3                        | Q3  |

| L | NC   | Q15                       | D15                      | VDDQ | Vss         | Vss | Vss         | VDDQ | NC   | NC                        | Q2  |

| М | NC   | NC                        | D16                      | Vss  | Vss         | Vss | Vss         | Vss  | NC   | Q1                        | D2  |

| N | NC   | D17                       | Q16                      | Vss  | SA          | SA  | SA          | Vss  | NC   | NC                        | D1  |

| Р | NC   | NC                        | Q17                      | SA   | SA          | С   | SA          | SA   | NC   | Do                        | Q0  |

| R | TDO  | ТСК                       | SA                       | SA   | SA          | C   | SA          | SA   | SA   | TMS                       | TDI |

6109 tbl 12b

## 165-ball FBGA Pinout TOP VIEW

#### NOTES:

1. A3 is reserved for the 36Mb expansion address.

2. A10 is reserved for the 72Mb expansion address. This must be tied or driven to VSS on the 1M x 18 QDRII Burst of 2 (71P72804) devices.

3. A2 is reserved for the 144Mb expansion address. This must be tied or driven to VSS on the 1M x 18 QDRII Burst of 2 (71P72804) devices.

# Pin Configuration 512K x 36

|   | 1    | 2                         | 3                        | 4    | 5           | 6   | 7           | 8    | 9                        | 10                        | 11  |

|---|------|---------------------------|--------------------------|------|-------------|-----|-------------|------|--------------------------|---------------------------|-----|

| A | CQ   | Vss/<br>SA <sup>(4)</sup> | NC/<br>SA <sup>(2)</sup> | W    | <b>B</b> ₩₂ | ĸ   | <b>B</b> ₩1 | R    | NC/<br>SA <sup>(1)</sup> | Vss/<br>SA <sup>(3)</sup> | CQ  |

| В | Q27  | Q18                       | D18                      | SA   | <b>B</b> ₩₃ | К   | B₩o         | SA   | D17                      | Q17                       | Q8  |

| C | D27  | Q28                       | D19                      | Vss  | SA          | SA  | SA          | Vss  | D16                      | Q7                        | D8  |

| D | D28  | D20                       | Q19                      | Vss  | Vss         | Vss | Vss         | Vss  | Q16                      | D15                       | D7  |

| E | Q29  | D29                       | Q20                      | VDDQ | Vss         | Vss | Vss         | VDDQ | Q15                      | D6                        | Q6  |

| F | Q30  | Q21                       | D21                      | VDDQ | Vdd         | Vss | Vdd         | Vddq | D14                      | Q14                       | Q5  |

| G | D30  | D22                       | Q22                      | VDDQ | Vdd         | Vss | Vdd         | VDDQ | Q13                      | D13                       | D5  |

| н | Doff | Vref                      | Vddq                     | VDDQ | Vdd         | Vss | Vdd         | VDDQ | VDDQ                     | Vref                      | ZQ  |

| J | D31  | Q31                       | D23                      | VDDQ | Vdd         | Vss | Vdd         | VDDQ | D12                      | Q4                        | D4  |

| к | Q32  | D32                       | Q23                      | Vddq | Vdd         | Vss | Vdd         | VDDQ | Q12                      | D3                        | Q3  |

| L | Q33  | Q24                       | D24                      | Vddq | Vss         | Vss | Vss         | VDDQ | D11                      | Q11                       | Q2  |

| м | D33  | Q34                       | D25                      | Vss  | Vss         | Vss | Vss         | Vss  | D10                      | Q1                        | D2  |

| N | D34  | D26                       | Q25                      | Vss  | SA          | SA  | SA          | Vss  | Q10                      | D9                        | D1  |

| Р | Q35  | D35                       | Q26                      | SA   | SA          | С   | SA          | SA   | Q9                       | Do                        | Qo  |

| R | TDO  | TCK                       | SA                       | SA   | SA          | C   | SA          | SA   | SA                       | TMS                       | TDI |

6109 tb1 12c

### 165-ball FBGA Pinout TOP VIEW

#### NOTES:

1. A9 is reserved for the 36Mb expansion address.

2. A3 is reserved for the 72Mb expansion address.

3. A10 is reserved for the 144Mb expansion address. This must be tied or driven to VSS on the 512K x 36 QDRII Burst of 2 (71P72604) devices.

4. A2 is reserved for the 288Mb expansion address. This must be tied or driven to VSS on the 512K x 36 QDRII Burst of 2 (71P72604) devices.

# Absolute Maximum Ratings<sup>(1) (2)</sup>

| Symbol              | Rating                                                      | Value                        | Unit       |

|---------------------|-------------------------------------------------------------|------------------------------|------------|

| VTERM               | Supply Voltage on VDD with Respect to GND                   | -0.5 to +2.9                 | V          |

| VTERM               | Supply Voltage on Voda with Respect to GND                  | -0.5 to VDD +0.3             | V          |

| VTERM               | Voltage on Input terminals with respect to GND.             | -0.5 to V <sub>DD</sub> +0.3 | V          |

| VTERM               | Voltage on Output and I/O<br>terminals with respect to GND. | -0.5 to VDDQ +0.3            | V          |

| T <sub>B IA S</sub> | Temperature Under Bias                                      | -55 to +125                  | °C         |

| Tstg                | Storage Temperature                                         | -65 to +150                  | °C         |

| louт                | Continuous Current into Outputs                             | <u>+</u> 20                  | m A        |

|                     |                                                             | 6                            | 109 tbl 05 |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VDDQ must not exceed VDD during normal operation.

Write Descriptions<sup>(1,2)</sup>

| Signal         | ₿₩o | $\overline{B}\overline{W}_1$ | $\overline{B}\overline{W}_2$ | $\overline{B}\overline{W}_3$ | <b>N</b> ₩₀ | <b>N</b> ₩1 |

|----------------|-----|------------------------------|------------------------------|------------------------------|-------------|-------------|

| Write Byte 0   | L   | Х                            | Х                            | Х                            | Х           | Х           |

| Write Byte 1   | Х   | L                            | Х                            | Х                            | Х           | Х           |

| Write Byte 2   | Х   | Х                            | L                            | Х                            | Х           | Х           |

| Write Byte 3   | Х   | Х                            | Х                            | L                            | Х           | Х           |

| Write Nibble 0 | Х   | Х                            | Х                            | Х                            | L           | Х           |

| Write Nibble 1 | Х   | Х                            | Х                            | Х                            | Х           | L           |

#### NOTES:

1) All byte write  $(\overline{BW}x)$  and nibble write  $(\overline{NW}x)$  signals are sampled on the rising edge of K and again on  $\overline{K}$ . The data that is present on the data bus in the designated byte/nibble will be latched into the input if the corresponding BWx or NWx is held low. The rising edge of K will sample the first byte/nibble of the two word burst and the rising edge of  $\overline{K}$  will sample the second byte/nibble of the two word burst.

2) The availability of the  $\overline{BW}\!x$  or  $\overline{NW}\!x$  on designated devices is described in the pin description table.

3) The QDRII Burst of two SRAM has data forwarding. A read request that is initiated on the same cycle as a write request to the same address will produce the newly written data in response to the read request.

### **Capacitance** (TA = +25°C, f = 1.0MHz)<sup>(1)</sup>

| Symbol | Parameter               | Conditions                          | Max. | Unit |

|--------|-------------------------|-------------------------------------|------|------|

| Cin    | Input Capacitance       |                                     | 5    | pF   |

| Ссік   | Clock Input Capacitance | $V_{DD} = 1.8V$<br>$V_{DDO} = 1.5V$ | 6    | pF   |

| Со     | Output Capacitance      |                                     | 7    | pF   |

NOTE:

1. Tested at characterization and retested after any design or process change that may affect these parameters.

6109 tbl 06

# **Recommended DC Operating and Temperature Conditions**

| Symbol | Parameter                             | Min. | Тур.   | Max. | Unit        |

|--------|---------------------------------------|------|--------|------|-------------|

| Vdd    | Power Supply<br>Voltage               | 1.7  | 1.8    | 1.9  | V           |

| VDDQ   | I/O Supply Voltage                    | 1.4  | 1.5    | 1.9  | V           |

| Vss    | Ground                                | 0    | 0      | 0    | V           |

| Vref   | Input Reference<br>Voltage            | 0.68 | VDDQ/2 | 0.95 | V           |

| Та     | Ambient<br>Temperature <sup>(1)</sup> | 0    | 25     | +70  | °C          |

| NOTE:  |                                       |      |        | (    | 5109 tbl 04 |

NOTE:

1. During production testing, the case temperature equals the ambient temperature.

6109 tbl 09

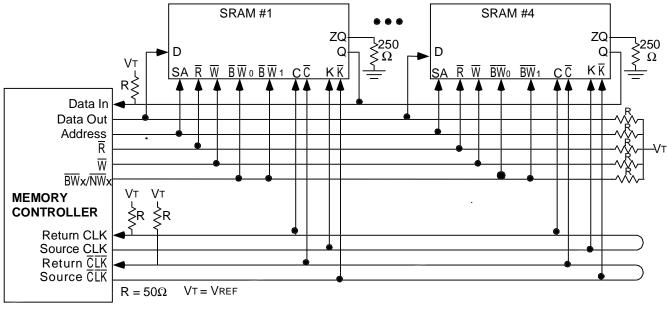

# **Application Example**

•.

6109 drw 20

10

6109 tbl 10c

### **DC Electrical Characteristics Over the Operating Temperature and** Supply Voltage Range (VDD = 1.8 ± 100mV, VDDQ = 1.4V to 1.9V)

| Parameter                                 | Symbol | Test Conditions                            |        | Min         | Мах         | Unit | Note |

|-------------------------------------------|--------|--------------------------------------------|--------|-------------|-------------|------|------|

| Input Leakage Current                     | liL.   | VDD = Max VIN = VSS to VDDQ                |        | -10         | +10         | μΑ   |      |

| Output Leakage Current                    | IOL    | Output Disabled                            |        | -10         | +10         | μΑ   |      |

|                                           |        | VDD = Max,                                 | 250MHz | -           | TBD         | mA   | 1    |

| Operating Current<br>(x36,x18,x9,x8): DDR | DD     | IOUT = 0mA (outputs open),                 | 200MHz | -           | TBD         |      |      |

|                                           |        | Cycle Time ≥ tKHKH Min                     | 167MHz | -           | TBD         |      |      |

|                                           |        | Device Deselected (in NOP state), 250      |        | -           | TBD         |      |      |

| Standby Current: NOP                      | ISB1   | lout = 0mA (outputs open),<br>f=Max,       | 200MHz | -           | TBD         | mA   | 2    |

|                                           |        | All Inputs $\leq$ 0.2V or $\geq$ VDD -0.2V | 167MHz | -           | TBD         |      |      |

| Output High Voltage                       | VOH1   | RQ = $250\Omega$ , IOH = $-15$ mA          |        | VDDQ/2-0.12 | VDDQ/2+0.12 | V    | 3,7  |

| Output Low Voltage                        | VOL1   | $RQ = 250\Omega$ , IOL = 15mA              |        | VDDQ/2-0.12 | VDDQ/2+0.12 | V    | 4,7  |

| Output High Voltage                       | VOH2   | IOH = -0.1mA                               |        | VDDQ-0.2    | VDDQ        | V    | 5    |

| Output Low Voltage                        | VOL2   | IOL = 0.1mA                                |        | Vss         | 0.2         | V    | 6    |

NOTES:

1. Operating Current is measured at 100% bus utilization.

2. Standby Current is only after all pending read and write burst operations are completed.

3. Outputs are impedance-controlled. IoH = -(VDD0/2)/(RQ/5) and is guaranteed by device characterization for  $175\Omega \leq RQ < 350\Omega$ . This parameter is tested at RQ =  $250\Omega$ , which gives a nominal  $50\Omega$  output impedance.

4. Outputs are impedance-controlled. IoL = (VDD0/2)/(RQ/5) and is guaranteed by device characterization for  $175\Omega \le RQ < 350\Omega$ . This parameter is tested at RQ =  $250\Omega$ , which gives a nominal  $50\Omega$  output impedance.

5. This measurement is taken to ensure that the output has the capability of pulling to the VDDO rail, and is not intended to be used as an impedance measurement point.

6. This measurement is taken to ensure that the output has the capability of pulling to Vss, and is not intended to be used as an impedance measurement point.

7. Programmable Impedance Mode.

### **Input Electrical Characteristics Over the Operating Temperature and** Supply Voltage Range (VDD = 1.8 ± 100mV, VDDQ = 1.4V to 1.9V)

| PARAMETER              | SYMBOL   | MIN       | MAX       | UNIT | NOTES |

|------------------------|----------|-----------|-----------|------|-------|

| Input High Voltage, DC | V⊮(DC)   | VREF +0.1 | VDDQ +0.3 | V    | 1,2   |

| Input Low Voltage, DC  | VIL (DC) | -0.3      | Vref -0.1 | V    | 1,3   |

| Input High Voltage, AC | VIH (AC) | VREF +0.2 | -         | V    | 4,5   |

| Input Low Voltage, AC  | VIL (AC) | -         | Vref -0.2 | V    | 4,5   |

#### NOTES:

1. These are DC test criteria. DC design criteria is VREF ± 50mV. The AC VIH/VIL levels are defined separately for measuring timing parameters.

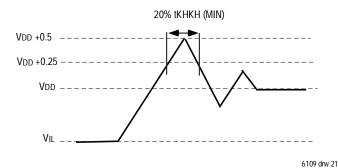

2. VIH (Max) DC = VDDQ+0.3, VIH (Max)  $\overrightarrow{AC}$  = VDD +0.5V (pulse width  $\leq$ 20% tKHKH (min))

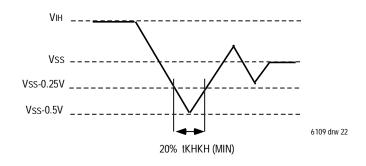

3. VIL (Min) DC = -0.3V, VIL (Min) AC = -0.5V (pulse width  $\leq$ 20% tKHKH (min))

4. This conditon is for AC function test only, not for AC parameter test.

5. To maintain a valid level, the transitioning edge of the input must:

a) Sustain a constant slew rate from the current AC level through the target AC level, VIL(AC) or VIH(AC)

b) Reach at least the target AC level.

c) After the AC target level is reached, continue to maintain at least the target DC level, VIL(DC) or VIH(DC)

# **Overshoot Timing**

# **Undershoot Timing**

6109 tbl 10d

# **AC Test Load**

# **AC Test Conditions**

| Parameter                     | Symbol  | Value     | Unit |

|-------------------------------|---------|-----------|------|

| Core Power Supply Voltage     | VDD     | 1.7-1.9   | V    |

| Output Power Supply Voltage   | VDDQ    | 1.4-1.9   | V    |

| Input High/Low Level          | VIH/VIL | 1.25/0.25 | V    |

| Input Reference Level         | VREF    | VDDQ/2    | V    |

| Input Rise/Fall Time          | TR/TF   | 0.6/0.6   | ns   |

| Output Timing Reference Level |         | VDDQ/2    | V    |

NOTE:

1. Parameters are tested with RQ=250 $\Omega$

1.25V -0.75V 0.25V -

6109tbl 11a

6109 drw 06

#### AC Electrical Characteristics (VDD = 1.8 ± 100mV, VDDQ = 1.4V to 1.9V, TA = 0 to 70°C) (3,8)

|            |                                                                                                        | 250   | MHz  | 200   | 200MHz |       | 167MHz |        |       |

|------------|--------------------------------------------------------------------------------------------------------|-------|------|-------|--------|-------|--------|--------|-------|

| Symbol     | Parameter                                                                                              | Min.  | Max  | Min.  | Мах    | Min.  | Мах    | Unit   | Notes |

| Clock Par  | ameters                                                                                                |       |      |       |        |       |        |        |       |

| tкнкн      | Average clock cycle time (K, $\overline{K}$ ,C,C)                                                      | 4.00  | 6.30 | 5.00  | 7.88   | 6.00  | 8.40   | ns     |       |

| tKC var    | Cycle to Cycle Period Jitter (K, $\overline{K}$ , C, $\overline{C}$ )                                  | -     | 0.20 | -     | 0.20   | -     | 0.20   | ns     | 1,5   |

| tk hkl     | Clock High Time (K, $\overline{K}$ ,C, $\overline{C}$ )                                                | 1.60  |      | 2.00  | -      | 2.40  | -      | ns     | 9     |

| tk l k h   | Clock LOW Time (K, $\overline{K}$ ,C, $\overline{C}$ )                                                 | 1.60  | -    | 2.00  | -      | 2.40  | -      | ns     | 9     |

| tĸн₩       | Clock to $\overline{\operatorname{clock}}$ (K $\rightarrow \overline{K}, C \rightarrow \overline{C}$ ) | 1.80  | -    | 2.20  | -      | 2.70  | -      | ns     | 10    |

| t₩HKH      | $\overline{\text{Clock}}$ to clock ( $\overline{K} \rightarrow K, \overline{C} \rightarrow C$ )        | 1.80  | -    | 2.20  | -      | 2.70  | -      | ns     | 10    |

| tкнсн      | Clock to data clock (K $\rightarrow$ C, $\overline{K}\rightarrow\overline{C}$ )                        | 0.00  | 1.80 | 0.00  | 2.30   | 0.00  | 2.80   | ns     |       |

| tKC lock   | DLL lock time (K, C)                                                                                   | 1024  | -    | 1024  | -      | 1024  | -      | cycles | 2     |

| tKC reset  | K static to DLL reset                                                                                  | 30    |      | 30    | -      | 30    | -      | ns     |       |

| Output Pa  | irameters                                                                                              |       |      |       |        |       |        |        |       |

| tc hq v    | $C, \overline{C}$ HIGH to output valid                                                                 | -     | 0.45 | -     | 0.45   | -     | 0.50   | ns     | 3     |

| tснох      | C, CHIGH to output hold                                                                                | -0.45 | -    | -0.45 | -      | -0.50 | -      | ns     | 3     |

| tc h c o v | $C,\overline{C}$ HIGH to echo clock valid                                                              |       | 0.45 | -     | 0.45   | -     | 0.50   | ns     | 3     |

| tc hc q x  | $C,\overline{C}$ HIGH to echo clock hold                                                               | -0.45 | -    | -0.45 | -      | -0.50 | -      | ns     | 3     |

| tco hov    | $CQ, \overline{CQ}$ HIGH to output valid                                                               | -     | 0.30 | -     | 0.35   | -     | 0.40   | ns     |       |

| tсонох     | $CQ, \overline{CQ}$ HIGH to output hold                                                                | -0.30 |      | -0.35 | -      | -0.40 | -      | ns     |       |

| tchqz      | $\overline{C}$ HIGH to output High-Z                                                                   | -     | 0.45 | -     | 0.45   | -     | 0.50   | ns     | 3,4,5 |

| tc HQ X 1  | $\overline{C}$ HIGH to output Low-Z                                                                    | -0.45 | -    | -0.45 | -      | -0.50 | -      | ns     | 3,4,5 |

| Set-Up Tir | mes                                                                                                    |       |      |       |        | -     |        |        |       |

| tav k h    | Address valid to K, $\overline{K}$ rising edge                                                         | 0.35  | -    | 0.40  | -      | 0.50  | -      | ns     | 6     |

| tiv KH     | Control inputs valid to K, $\overline{K}$ rising edge                                                  | 0.35  | -    | 0.40  | -      | 0.50  | -      | ns     | 7     |

| tdvкн      | Date-in valid to K, $\overline{K}$ rising edge                                                         | 0.35  | -    | 0.40  | -      | 0.50  | -      | ns     |       |

| Hold Time  | es                                                                                                     | -     |      |       |        |       |        |        |       |

| tk hax     | $K,\overline{K} rising$ edge to address hold                                                           | 0.35  | -    | 0.40  | -      | 0.50  | -      | ns     | 6     |

| tкнix      | $K,\overline{K}\xspace$ rising edge to control inputs hold                                             | 0.35  | -    | 0.40  | -      | 0.50  | -      | ns     | 7     |

| tкнdх      | K, $\overline{K}$ rising edge to data-in hold                                                          | 0.35  | -    | 0.40  | -      | 0.50  | -      | ns     |       |

NOTES:

1. Cycle to cycle period jitter is the variance from clock rising edge to the next expected clock rising edge, as defined per JEDEC Standard No.65 (EIA/JESD65) pg.10

2. Vid slew rate must be less than 0.1V DC per 50 ns for DLL lock retention. DLL lock time begins once Vdd and input clock are stable.

3. If  $C,\overline{C}$  are tied High,  $K,\overline{K}$  become the references for  $C,\overline{C}$  timing parameters.

4. To avoid bus contention, at a given voltage and temperature tCHQX1 is bigger than tCHQZ.

The specs as shown do not imply bus contention because tCHQX1 is a MIN parameter that is worse case at totally different test conditions (0°C, 1.9V) than tCHQZ, which is a MAX parameter (worst case at 70°C, 1.7V) It is not possible for two SRAMs on the same board to be at such different voltage and temperature.

5. This parameter is guaranteed by device characterization, but not production tested.

All address inputs must meet the specified setup and hold times for all latching clock edges.

7. Control signals are  $\overline{R}$ ,  $\overline{W}$ ,  $\overline{BW}_0$ ,  $\overline{BW}_1$  and  $(\overline{NW}_0$ ,  $\overline{NW}_1$ , for x8) and  $(\overline{BW}_2$ ,  $\overline{BW}_3$  also for x36)

8. During production testing, the case temperature equals TA.

9. Clock High Time (tKHKL) and Clock Low Time (tKLKH) should be within 40% to 60% of the cycle time (tKHKH).

10. Clock to Clock time (tKHKH) and Clock to Clock time (tKHKH) should be within 45% to 55% of the cycle time (tKHKH).

# **Timing Waveform of Combined Read and Write Cycles**

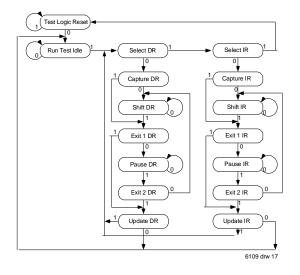

# **IEEE 1149.1 TEST ACCESS PORT AND BOUNDARY SCAN-JTAG**

This part contains an IEEE standard 1149.1 Compatible Test Access Port (TAP). The package pads are monitored by the Serial Scan circuitry when in test mode. This is to support connectivity testing during manufacturing and system diagnostics. In conformance with IEEE 1149.1, the SRAM contains a TAP controller, Instruction register, Bypass Register and ID register. The TAP controller has a standard 16-state machine that resets internally upon power-up; therefore, the TRST signal is not required. It is possible to use this device without utilizing the TAP. To disable the TAP controller without interfacing with normal operation of the SRAM, TCK must be tied to Vss to preclude a mid level input. TMS and TDI are designed so an undriven input will produce a response identical to the application of a logic 1, and may be left unconnected, but they may also be tied to VDD through a resistor. TDO should be left unconnected.

# JTAG Block Diagram

# **TAP Controller State Diagram**

# **JTAG Instruction Coding**

| IR2 | IR1 | IR0 | Instruction    | TDO Output              | Notes |

|-----|-----|-----|----------------|-------------------------|-------|

| 0   | 0   | 0   | EXTEST         | Boundary Scan Register  |       |

| 0   | 0   | 1   | IDCODE         | Identification register | 2     |

| 0   | 1   | 0   | SAMPLE-Z       | Boundary Scan Register  | 1     |

| 0   | 1   | 1   | RESERVED       | Do Not Use              | 5     |

| 1   | 0   | 0   | SAMPLE/PRELOAD | Boundary Scan register  | 4     |

| 1   | 0   | 1   | RESERVED       | Do Not Use              | 5     |

| 1   | 1   | 0   | RESERVED       | Do Not Use              | 5     |

| 1   | 1   | 1   | BYPASS         | Bypass Register         | 3     |

NOTES:

1. Places Qs in Hi-Z in order to sample all input data regardless of other SRAM inputs.

2. TDI is sampled as an input to the first ID register to allow for the serial shift of the external TDI data.

6109tbl 13

3. Bypass register is initialized to Vss when BYPASS instruction is invoked. The Bypass Register also holds serially loaded TDI when exiting the Shift DR states.

4. SAMPLE instruction does not place output pins in Hi-Z.

5. This instruction is reserved for future use.

| Scan | Register | Definition |

|------|----------|------------|

|      |          |            |

| Part    | Instruction Register | Bypass Register | ID Register | Boundary Scan |

|---------|----------------------|-----------------|-------------|---------------|

| 512Kx36 | 3 bits               | 1 bit           | 32 bits     | 107 bits      |

| 1Mx18   | 3 bits               | 1 bit           | 32 bits     | 107 bits      |

| 2Mx8/x9 | 3 bits               | 1 bit           | 32 bits     | 107 bits      |

6109 tbl 14

# **Identification Register Definitions**

| INSTRUCTION FIELD                     | ALL DEVICES                                                                                      | DESCRIPTION                                       | PART NUMBER                                      |

|---------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------|

| Revision Number (31:29)               | 000                                                                                              | Revision Number                                   |                                                  |

| Device ID (28:12)                     | 0 0000 0010 0100 0100<br>0 0000 0010 0100 0101<br>0 0000 0010 0100 0110<br>0 0000 0010 0100 0111 | 512Kx36 QDRII Burst of 2<br>1Mx18<br>2Mx9<br>2Mx8 | 71P72604S<br>71P72804S<br>71P72104S<br>71P72204S |

| IDT JEDEC ID CODE (11:1)              | 000 0011 0011                                                                                    | Allows unique identification of SRAM vendor.      |                                                  |

| ID Register Presence<br>Indicator (0) | 1                                                                                                | Indicates the presence of an ID register.         |                                                  |

6109 tbl 15

# Boundary Scan Exit Order (2M x 8-Bit, 2M x 9-Bit)

| ORDER | PIN ID |

|-------|--------|

| 1     | 6R     |

| 2     | 6P     |

| 3     | 6N     |

| 4     | 7P     |

| 5     | 7N     |

| 6     | 7R     |

| 7     | 8R     |

| 8     | 8P     |

| 9     | 9R     |

| 10    | 11P    |

| 11    | 10P    |

| 12    | 10N    |

| 13    | 9P     |

| 14    | 10M    |

| 15    | 11N    |

| 16    | 9M     |

| 17    | 9N     |

| 18    | 11L    |

| 19    | 11M    |

| 20    | 9L     |

| 21    | 10L    |

| 22    | 11K    |

| 23    | 10K    |

| 24    | 9J     |

| 25    | 9К     |

| 26    | 10J    |

| 27    | 11J    |

| 28    | 11H    |

| 29    | 10G    |

| 30    | 9G     |

| 31    | 11F    |

| 32    | 11G    |

| 33    | 9F     |

| 34    | 10F    |

| 35    | 11E    |

| 36    | 10E    |

| ORDER | PIN ID       |

|-------|--------------|

| 37    | 10D          |

| 38    | 9E           |

| 39    | 10C          |

| 40    | 11D          |

| 41    | 9C           |

| 42    | 9D           |

| 43    | 11B          |

| 44    | 11C          |

| 45    | 9B           |

| 46    | 10B          |

| 47    | 11A          |

| 48    | Internal     |

| 49    | 9A           |

| 50    | 8B           |

| 51    | 7C           |

| 52    | 6C           |

| 53    | 8A           |

| 54    | 7A           |

| 55    | 7B           |

| 56    | 6B           |

| 57    | 6A           |

| 58    | 5B           |

| 59    | 5A           |

| 60    | 4A           |

| 61    | 5C           |

| 62    | 4B           |

| 63    | 3A           |

| 64    | 2A           |

| 65    | 1A           |

| 66    | 2B           |

| 67    | 3B           |

| 68    | 1C           |

| 69    | 1B           |

| 70    | 3D           |

| 71    | 3C           |

| 72    | 2D           |

|       | 6100 tbl 173 |

| 73  | PIN ID |

|-----|--------|

| 15  | 3E     |

| 74  | 2C     |

| 75  | 1D     |

| 76  | 2E     |

| 77  | 1E     |

| 78  | 2F     |

| 79  | 3F     |

| 80  | 2G     |

| 81  | 3G     |

| 82  | 1F     |

| 83  | 1G     |

| 84  | 1J     |

| 85  | 2ا     |

| 86  | ЗК     |

| 87  | 31     |

| 88  | 3L     |

| 89  | 2L     |

| 90  | 1K     |

| 91  | 2К     |

| 92  | 1M     |

| 93  | 1L     |

| 94  | 3N     |

| 95  | 3M     |

| 96  | 2N     |

| 97  | 3P     |

| 98  | 2M     |

| 99  | 1N     |

| 100 | 2P     |

| 101 | 1P     |

| 102 | 3R     |

| 103 | 4R     |

| 104 | 4P     |

| 105 | 5P     |

| 106 | 5N     |

| 107 | 5R     |

6109 tbl 16a

6109 tbl 17a

6109 tbl 18a

# Boundary Scan Exit Order (1M x 18-Bit, 512K x 36 -Bit)

| ORDER | PIN ID |

|-------|--------|

| 1     | 6R     |

| 2     | 6P     |

| 3     | 6N     |

| 4     | 7P     |

| 5     | 7N     |

| 6     | 7R     |

| 7     | 8R     |

| 8     | 8P     |

| 9     | 9R     |

| 10    | 11P    |

| 11    | 10P    |

| 12    | 10N    |

| 13    | 9P     |

| 14    | 10M    |

| 15    | 11N    |

| 16    | 9M     |

| 17    | 9N     |

| 18    | 11L    |

| 19    | 11M    |

| 20    | 9L     |

| 21    | 10L    |

| 22    | 11K    |

| 23    | 10K    |

| 24    | 9J     |

| 25    | 9К     |

| 26    | 10J    |

| 27    | 11J    |

| 28    | 11H    |

| 29    | 10G    |

| 30    | 9G     |

| 31    | 11F    |

| 32    | 11G    |

| 33    | 9F     |

| 34    | 10F    |

| 35    | 11E    |

| 36    | 10E    |

| ORDER | PIN ID   |

|-------|----------|

| 37    | 10D      |

| 38    | 9E       |

| 39    | 10C      |

| 40    | 11D      |

| 41    | 9C       |

| 42    | 9D       |

| 43    | 11B      |

| 44    | 11C      |

| 45    | 9B       |

| 46    | 10B      |

| 47    | 11A      |

| 48    | Internal |

| 49    | 9A       |

| 50    | 8B       |

| 51    | 7C       |

| 52    | 6C       |

| 53    | 8A       |

| 54    | 7A       |

| 55    | 7B       |

| 56    | 6B       |

| 57    | 6A       |

| 58    | 5B       |

| 59    | 5A       |

| 60    | 4A       |

| 61    | 5C       |

| 62    | 4B       |

| 63    | 3A       |

| 64    | 1H       |

| 65    | 1A       |

| 66    | 2B       |

| 67    | 3B       |

| 68    | 1C       |

| 69    | 1B       |

| 70    | 3D       |

| 71    | 3C       |

| 72    | 1D       |

| ORDER | PIN ID      |

|-------|-------------|

| 73    | 2C          |

| 73    | 3E          |

| 74    | 2D          |

| 75    | 2D<br>2E    |

|       | 1E          |

| 77    | 2F          |

| 78    |             |

| 79    | 3F          |

| 80    | 1G          |

| 81    | 1F          |

| 82    | 3G          |

| 83    | 2G          |

| 84    | 1J          |

| 85    | 2J          |

| 86    | ЗК          |

| 87    | 31          |

| 88    | 2K          |

| 89    | 1K          |

| 90    | 2L          |

| 91    | 3L          |

| 92    | 1M          |

| 93    | 1L          |

| 94    | 3N          |

| 95    | 3M          |

| 96    | 1N          |

| 97    | 2M          |

| 98    | 3P          |

| 99    | 2N          |

| 100   | 2P          |

| 101   | 1P          |

| 102   | 3R          |

| 103   | 4R          |

| 104   | 4P          |

| 105   | 5P          |

| 106   | 5N          |

| 107   | 5R          |

|       | 6109 tbl 18 |

6109 tbl 16

6109 tbl 18

6109 tbl 17

## **JTAG DC Operating Conditions**

| Parameter                       | Symbol | Min        | Тур | Max     | Unit | Note        |

|---------------------------------|--------|------------|-----|---------|------|-------------|

| Output Power Supply             | VDDQ   | 1.4        | -   | 1.9     | V    |             |

| Power Supply Voltage            | VDD    | 1.7        | 1.8 | 1.9     | V    |             |

| Input High Level                | Vін    | 1.3        | -   | VDD+0.3 | V    |             |

| Input Low Level                 | VIL    | -0.3       |     | 0.5     | V    |             |

| Output High Voltage (Юн = -1mA) | Vон    | VDDQ - 0.2 |     | VDDQ    | V    | 1           |

| Output Low Voltage (IOL = 1mA)  | Vol    | Vss        | -   | 0.2     | V    | 1           |

| NOTE:                           |        |            |     |         |      | 6109 tbl 19 |

NOTE:

1. The output impedance of TDO is set to 50 ohms (nominal process) and does not vary with the external resistor connected to ZQ.

#### **JTAG AC Test Conditions**

| Parameter                               | Symbol  | Min     | Unit | Note        |

|-----------------------------------------|---------|---------|------|-------------|

| Input High/Low Level                    | VIH/VIL | 1.3/0.5 | V    |             |

| Input Rise/Fall Time                    | TR/TF   | 1.0/1.0 | ns   |             |

| Input and Output Timing Reference Level |         | VDDQ/2  | V    | 1           |

| NOTE: 6109 tbl 20                       |         |         |      | 6109 tbl 20 |

1. See AC test load on page 12.

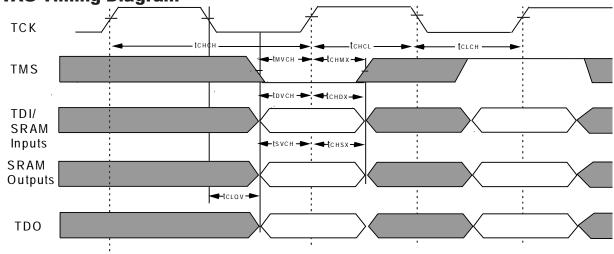

# **JTAG AC Characteristics**

| Parameter                 | Symbol        | Min | Max | Unit | Note |

|---------------------------|---------------|-----|-----|------|------|

| TCK Cycle Time            | tснсн         | 50  | -   | ns   |      |

| TCK High Pulse Width      | IC HCL        | 20  | -   | ns   |      |

| TCK Low Pulse Width       | <b>t</b> CLCH | 20  | -   | ns   |      |

| TMS Input Setup Time      | tмvсн         | 5   | -   | ns   |      |

| TMS Input Hold Time       | tснмх         | 5   | -   | ns   |      |

| TDI Input Setup Time      | tdvcн         | 5   | -   | ns   |      |

| TDI Input Hold Time       | <b>t</b> CHDX | 5   | -   | ns   |      |

| SRAM Input Setup Time     | tsvcн         | 5   | -   | ns   |      |

| SRAM Input Hold Time      | <b>t</b> CHSX | 5   | -   | ns   |      |

| Clock Low to Output Valid | tCLQV         | 0   | 10  | ns   |      |

**JTAG Timing Diagram**

6109 tbl.21

# Package Diagram Outline for 165-Ball Fine Pitch Grid Array

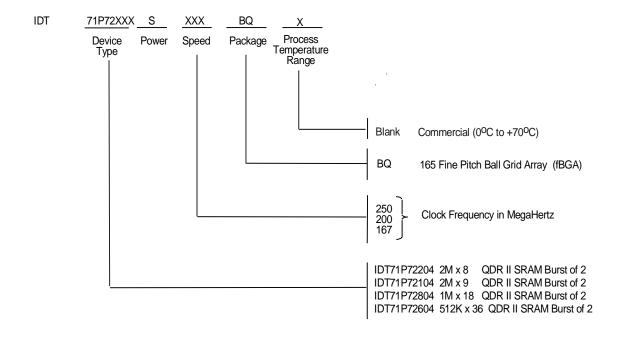

# **Ordering Information**

6109 drw 15

for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com for Tech Support: sramhelp@idt.com 800-544-7726

"QDR SRAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress Semiconductor, IDT, and Micron Technology, Inc. "

# **Revision History**

| <b>REVISION</b> | DATE     | PAGES         | DESCRIPTION                                                                                                         |

|-----------------|----------|---------------|---------------------------------------------------------------------------------------------------------------------|

| 0               | 8/01/03  | 1-21          | Initial Advance Information Data Sheet Release                                                                      |

| А               | 11/14/03 | 11,12,19      | Updated tкнкн (max) for 167-250 MHz and set-up & hold times for                                                     |

|                 |          |               | 250MHz. Incorporated 133 MHz speed grade in S167 speed bin.                                                         |

|                 |          | 15            | Changed number of Boundary Scan bits from 109 to 107. Specified ID bits [28:24] and                                 |

|                 |          |               | IDT JEDEC ID bits [11:1] in binary.                                                                                 |

|                 |          | 16            | Updated Boundary Scan Pin IDs for order #48, #64 and #84 through 107.                                               |

| В               | 3/30/04  | 1,3,5-8,14-15 | Renamed address inputs from A to SA.                                                                                |

|                 |          | 5-8           | Identified 36Mb to 288Mb address expansion pins and requirements.                                                   |

|                 |          | 9             | Updated absolute maximum VTERM on input terminals, added VDDQ requirement note 2 and VREF min/max specifications    |

|                 |          | 9,11,12       | Consolidated DC and AC input specifications by add ing new pg.12, including new Input                               |

|                 |          |               | Electrical Characteristics table, notes 1-5 and overshoot/undershoot timing diagrams.                               |

|                 |          | 10            | Updated application example showing HSTL terminations (R and VT) on control inputs.                                 |

|                 |          | 11            | Clarified VOH, VOL, IDD and ISB1 test conditions and notes.                                                         |

|                 |          | 13            | Clarified tKHKL,tKLKH,tKH $\overline{K}$ H, t $\overline{K}$ HKH as a percentage of the cycle time; updated tkc var |

|                 |          |               | cycle to cycle period jitter and notes for AC Electrical Characteristics.                                           |

|                 |          | 14            | Added tCQHQX to timing diagram.                                                                                     |

|                 |          | 17,18         | Modified Boundary Scan order for x8 and x9 options, adding new page 17 with new pin                                 |

|                 |          |               | IDs for order#64, #72-75, #80-83, #88-91 and #96-99; changed order #48 from 10A to                                  |

|                 |          |               | Internal for x8/9 and x18/36 options.                                                                               |

|                 |          | 19            | Updated JTAG DC Operating Conditions note 1 and VOH (max) specification from VDD to                                 |

|                 |          |               | VDDQ. Added tCLQV to JTAG Timing Diagram.                                                                           |

| С               | 5/18/04  | 1             | Corrected package size to 13mm x 17mm fBGA.                                                                         |

|                 |          | 2             | Clarified data word order.                                                                                          |

|                 |          | 12            | Updated AC Test Load and Test Conditions to VREF = VDDQ/2.                                                          |

|                 |          | 15            | Clarified pull up resistor to VDD for the unused JTAG inputs.                                                       |