#### **Freescale Semiconductor**

#### **Technical Data Advance Information**

## **DSP56L307**

### 24-Bit Digital Signal Processor

The DSP56L307 is intended for applications requiring a large amount of internal memory, such as networking and wireless infrastructure applications. The EFCOP can accelerate general filtering applications, such as echo-cancellation applications, correlation, and general-purpose convolution-based algorithms.

#### What's New?

Rev. 6 includes the following changes:

Adds lead-free packaging and part numbers.

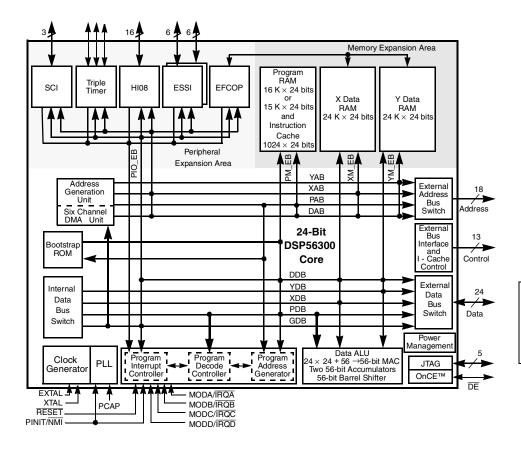

Figure 1. DSP56L307 Block Diagram

The Freescale DSP56L307, a member of the DSP56300 DSP family, supports network applications with general filtering operations. The Enhanced Filter Coprocessor (EFCOP) executes filter algorithms in parallel with core operations, enhancing signal quality with no impact on channel throughput or total channels supported. The result is increased overall performance. Like the other DSP56300 family members, the DSP56L307 uses a high-performance, single-clock-cycle-per- instruction engine (DSP56000 code-compatible), a barrel shifter, 24-bit addressing, an instruction cache, and a direct memory access (DMA) controller (see **Figure 1**). The DSP56L307 performs at up to 160 million multiply-accumulates per second (MMACS), attaining up to 320 MMACS when the EFCOP is in use. It operates with an internal 160 MHz clock with a 1.8 volt core and independent 3.3 volt input/output (I/O) power.

Note: This document contains information on a new product. Specifications and information herein are subject to change without notice.

### **Table of Contents**

|           |       | Data Sheet Conventions                          | i   |

|-----------|-------|-------------------------------------------------|-----|

|           |       | Features                                        | ii  |

|           |       | Target Applications                             | iv  |

|           |       | Product Documentation                           | iv  |

| Chapter 1 | Signa | als/Connections                                 |     |

| •         | 1.1   | Power                                           | 1-3 |

|           | 1.2   | Ground                                          |     |

|           | 1.3   | Clock                                           |     |

|           | 1.5   | External Memory Expansion Port (Port A)         | 1-4 |

|           | 1.6   | Interrupt and Mode Control                      |     |

|           | 1.7   | Host Interface (HI08)                           |     |

|           | 1.8   | Enhanced Synchronous Serial Interface 0 (ESSI0) |     |

|           | 1.9   | Enhanced Synchronous Serial Interface 1 (ESSI1) |     |

|           | 1.10  | Serial Communication Interface (SCI)            |     |

|           | 1.11  | Timers                                          |     |

|           | 1.12  | JTAG and OnCE Interface                         |     |

| Chapter 2 | Speci | eifications                                     |     |

| •         | 2.1   | Maximum Ratings                                 | 2-1 |

|           | 2.2   | Thermal Characteristics                         |     |

|           | 2.3   | DC Electrical Characteristics                   |     |

|           | 2.4   | AC Electrical Characteristics                   | 2-4 |

| Chapter 3 | Packa | aging                                           |     |

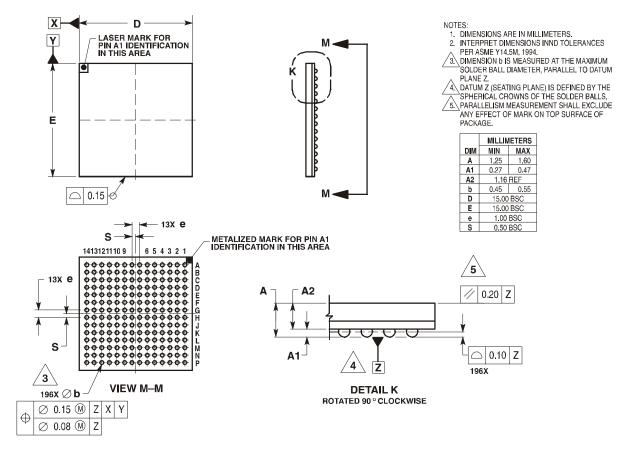

| •         | 3.1   | Package Description                             | 3-2 |

|           | 3.2   | MAP-BGA Package Mechanical Drawing              |     |

| Chapter 4 | Desid | gn Considerations                               |     |

| •         | 4.1   | Thermal Design Considerations                   | 4-1 |

|           | 4.2   | Electrical Design Considerations                |     |

|           | 4.3   | Power Consumption Considerations                |     |

|           | 4.4   | PLL Performance Issues                          |     |

|           | 4.5   | Input (EXTAL) Jitter Requirements               |     |

|           |       | r (                                             |     |

#### Appendix A Power Consumption Benchmark

### **Data Sheet Conventions**

ii

Indicates a signal that is active when pulled low (For example, the RESET pin is active when low.)

"asserted"

Means that a high true (active high) signal is high or that a low true (active low) signal is low "deasserted"

Means that a high true (active high) signal is low or that a low true (active low) signal is high

| Examples: | Signal/Symbol | Logic State | Signal State | Voltage         |

|-----------|---------------|-------------|--------------|-----------------|

|           | PIN           | True        | Asserted     | $V_{IL}/V_{OL}$ |

|           | PIN           | False       | Deasserted   | $V_{IH}/V_{OH}$ |

|           | PIN           | True        | Asserted     | $V_{IH}/V_{OH}$ |

|           | PIN           | False       | Deasserted   | $V_{IL}/V_{OL}$ |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

## **Features**

Table 1 lists the features of the DSP56L307 device.

Table 1. DSP56L307 Features

| Feature                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                                |                                |                      |                    |           |      |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------|--------------------------------|----------------------|--------------------|-----------|------|

| High-Performance<br>DSP56300 Core      | <ul> <li>160 million multiply-accumulates per second (MMACS) (320 MMACS using the EFCOP in filtering applications) with a 160 MHz clock at 1.8 V core and 3.3 V I/O</li> <li>Object code compatible with the DSP56000 core with highly parallel instruction set</li> <li>Data arithmetic logic unit (Data ALU) with fully pipelined 24 × 24-bit parallel multiplier-accumulator (MAC), 56-bit parallel barrel shifter (fast shift and normalization; bit stream generation and parsing), conditional ALU instructions, and 24-bit or 16-bit arithmetic support under software control</li> <li>Program control unit (PCU) with position-independent code (PIC) support, addressing modes optimized for DSP applications (including immediate offsets), internal instruction cache controller, internal memory-expandable hardware stack, nested hardware DO loops, and fast auto-return interrupts</li> <li>Direct memory access (DMA) with six DMA channels supporting internal and external accesses; one-, two-and three-dimensional transfers (including circular buffering); end-of-block-transfer interrupts; and triggering from interrupt lines and all peripherals</li> <li>Phase-lock loop (PLL) allows change of low-power divide factor (DF) without loss of lock and output clock with skew elimination</li> <li>Hardware debugging support including on-chip emulation (OnCE) module, Joint Test Action Group (JTAG) test access port (TAP)</li> </ul> |                           |                                |                                |                      |                    |           |      |

| Enhanced Filter<br>Coprocessor (EFCOP) | Internal 24 × 24-bit filtering and echo-cancellation coprocessor that runs in parallel to the DSP core Operation at the same frequency as the core (up to 160 MHz) Support for a variety of filter modes, some of which are optimized for cellular base station applications: Real finite impulse response (FIR) with real taps Complex FIR with complex taps Complex FIR generating pure real or pure imaginary outputs alternately A 4-bit decimation factor in FIR filters, thus providing a decimation ratio up to 16 Direct form 1 (DFI) Infinite Impulse Response (IIR) filter Direct form 2 (DFII) IIR filter Four scaling factors (1, 4, 8, 16) for IIR output Adaptive FIR filter with true least mean square (LMS) coefficient updates Adaptive FIR filter with delayed LMS coefficient updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |                                |                                |                      |                    |           |      |

| Internal Peripherals                   | Enhanced 8-bit parallel host interface (HI08) supports a variety of buses (for example, ISA) and provides glueless connection to a number of industry-standard microcomputers, microprocessors, and DSPs     Two enhanced synchronous serial interfaces (ESSI), each with one receiver and three transmitters (allows example, home theorer).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |                                |                                |                      |                    | s (allows |      |

|                                        | <ul> <li>192 × 24-bit b</li> <li>192 K × 24-bit</li> <li>Program RAM</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RAM total                 | e, X data RAM, a               | and Y data RAM s               | sizes are prog       | rammable           | :         |      |

|                                        | Program RAM<br>Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Instruction<br>Cache Size | X Data RAM<br>Size*            | Y Data RAM<br>Size*            | Instruction<br>Cache | Switch<br>Mode     | MSW1      | MSW0 |

|                                        | 16 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                         | 24 K × 24-bit                  | 24 K × 24-bit                  | disabled             | disabled           | 0/1       | 0/1  |

|                                        | 15 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1024 × 24-bit             | 24 K × 24-bit                  | 24 K × 24-bit                  | enabled              | disabled           | 0/1       | 0/1  |

|                                        | 48 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                         | 8 K × 24-bit                   | 8 K × 24-bit                   | disabled             | enabled            | 0         | 0    |

| Internal Memories                      | 47 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1024 × 24-bit             | 8 K × 24-bit                   | 8 K × 24-bit                   | enabled              | enabled            | 0         | 0    |

|                                        | 40 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                         | 12 K × 24-bit                  | 12 K × 24-bit                  | disabled             | enabled            | 0         | 1    |

|                                        | 39 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1024 × 24-bit             | 12 K × 24-bit                  | 12 K × 24-bit                  | enabled              | enabled            | 0         | 1    |

| İ                                      | 32 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0<br>1024 × 24-bit        | 16 K × 24-bit                  | 16 K × 24-bit                  | disabled             | enabled            | 1         | 0    |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1001 v 01 hit             | 16 K × 24-bit                  | 1 16 K V 7/1 hit               | enabled              | enabled            | 1         | (1)  |

|                                        | 31 K × 24-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |                                | 16 K × 24-bit                  |                      |                    |           | 0    |

|                                        | $ \begin{array}{c} 31 \text{ K} \times 24\text{-bit} \\ 24 \text{ K} \times 24\text{-bit} \\ 23 \text{ K} \times 24\text{-bit} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>1024 × 24-bit        | 20 K × 24-bit<br>20 K × 24-bit | 20 K × 24-bit<br>20 K × 24-bit | disabled<br>enabled  | enabled<br>enabled | 1         | 1    |

Freescale Semiconductor iii

Table 1. DSP56L307 Features (Continued)

| Feature                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

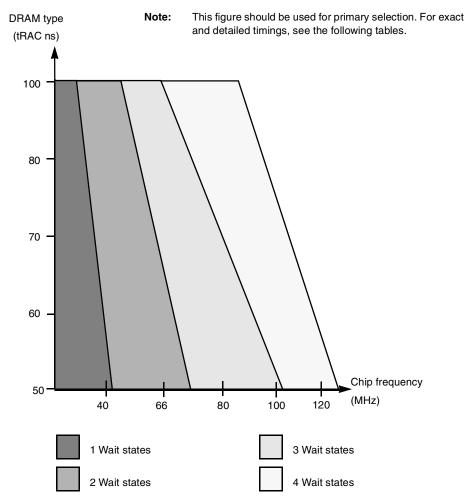

| External Memory<br>Expansion | <ul> <li>Data memory expansion to two 256 K × 24-bit word memory spaces using the standard external address lines</li> <li>Program memory expansion to one 256 K × 24-bit words memory space using the standard external address lines</li> <li>External memory expansion port</li> <li>Chip select logic for glueless interface to static random access memory (SRAMs)</li> <li>Internal DRAM Controller for glueless interface to dynamic random access memory (DRAMs) up to 100 MHz operating frequency</li> </ul> |  |  |  |  |

| Power Dissipation            | Very low-power CMOS design  Wait and Stop low-power standby modes  Fully static design specified to operate down to 0 Hz (dc)  Optimized power management circuitry (instruction-dependent, peripheral-dependent, and mode-dependent)                                                                                                                                                                                                                                                                                 |  |  |  |  |

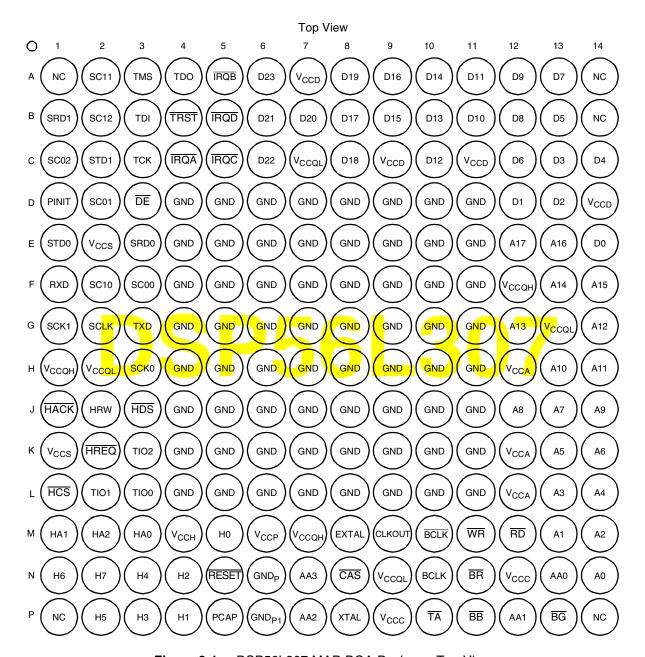

| Packaging                    | Molded array plastic-ball grid array (MAP-BGA) package in lead-free or lead-bearing versions.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

### **Target Applications**

- Wireless and wireline infrastructure applications

- Multi-channel wireless local loop systems

- DSP resource boards

- High-speed modem banks

- Packet telephony

#### **Product Documentation**

The documents listed in **Table 2** are required for a complete description of the DSP56L307 device and are necessary to design properly with the part. Documentation is available from a local Freescale distributor, a Freescale semiconductor sales office, or a Freescale Semiconductor Literature Distribution Center. For documentation updates, visit the Freescale DSP website. See the contact information on the back cover of this document.

Table 2. DSP56L307 Documentation

| Name                       | Description                                                                                                | Order Number                      |

|----------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------|

| DSP56L307<br>User's Manual | Detailed functional description of the DSP56L307 memory configuration, operation, and register programming | DSP56L307UM                       |

| DSP56300 Family<br>Manual  | Detailed description of the DSP56300 family processor core and instruction set                             | DSP56300FM                        |

| Application Notes          | Documents describing specific applications or optimized device operation including code examples           | See the DSP56L307 product website |

# Signals/Connections

1

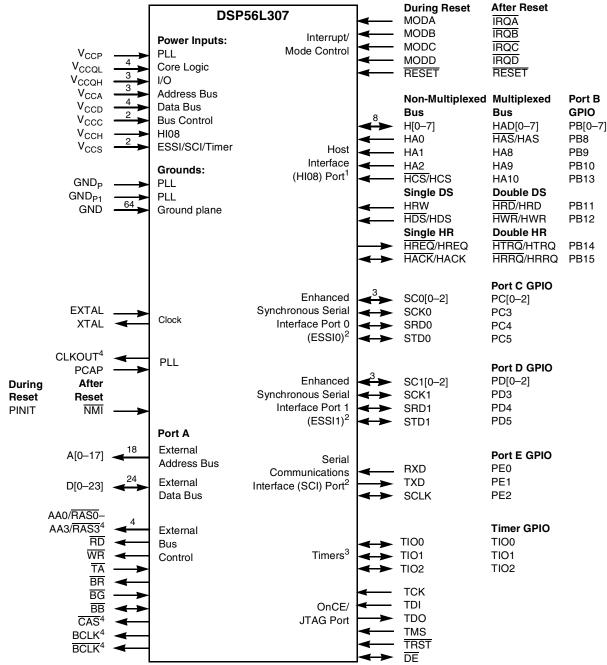

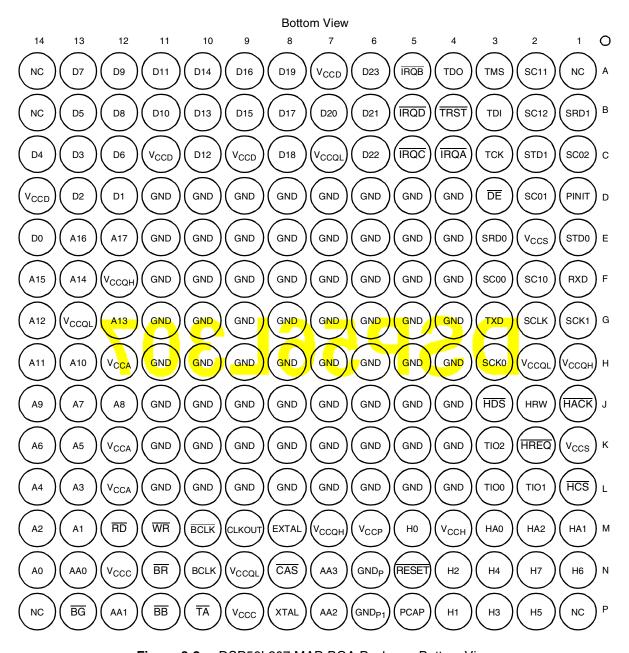

The DSP56L307 input and output signals are organized into functional groups as shown in **Table 1-1**. **Figure 1-1** diagrams the DSP56L307 signals by functional group. The remainder of this chapter describes the signal pins in each functional group.

**Table 1-1.** DSP56L307 Functional Signal Groupings

| Functional Group                                                         |                     |    |  |  |  |

|--------------------------------------------------------------------------|---------------------|----|--|--|--|

| Power (V <sub>CC</sub> )                                                 |                     | 20 |  |  |  |

| Ground (GND)                                                             |                     | 66 |  |  |  |

| Clock                                                                    |                     | 2  |  |  |  |

| PLL                                                                      |                     | 3  |  |  |  |

| Address bus                                                              | 18                  |    |  |  |  |

| Data bus Port A <sup>1</sup>                                             |                     |    |  |  |  |

| Bus control                                                              |                     |    |  |  |  |

| Interrupt and mode control                                               | ·                   | 5  |  |  |  |

| Host interface (HI08)                                                    | Port B <sup>2</sup> | 16 |  |  |  |

| Enhanced synchronous serial interface (ESSI)  Ports C and D <sup>3</sup> |                     |    |  |  |  |

| Serial communication interface (SCI)  Port E <sup>4</sup>                |                     |    |  |  |  |

| Timer                                                                    |                     |    |  |  |  |

| OnCE/JTAG Port                                                           |                     |    |  |  |  |

#### Notes:

- Port A signals define the external memory interface port, including the external address bus, data bus, and control signals. The Clock Output (CLKOUT), BCLK, BCLK, CAS, and RAS[0-3] signals used by other DSP56300 family members are supported by the DSP56L307 at operating frequencies up to 100 MHz. DRAM access is not supported above 100 MHz.

- 2. Port B signals are the HI08 port signals multiplexed with the GPIO signals.

- 3. Port C and D signals are the two ESSI port signals multiplexed with the GPIO signals.

- 4. Port E signals are the SCI port signals multiplexed with the GPIO signals.

- 5. There are 5 signal connections that are not used. These are designated as no connect (NC) in the package description (see Chapter 3).

**Note:** This chapter refers to a number of configuration registers used to select individual multiplexed signal functionality. Refer to the *DSP56L307 User's Manual* for details on these configuration registers.

Notes:

- 1. The HI08 port supports a non-multiplexed or a multiplexed bus, single or double Data Strobe (DS), and single or double Host Request (HR) configurations. Since each of these modes is configured independently, any combination of these modes is possible. These HI08 signals can also be configured alternatively as GPIO signals (PB[0–15]). Signals with dual designations (for example, HAS/HAS) have configurable polarity.

- 2. The ESSI0, ESSI1, and SCI signals are multiplexed with the Port C GPIO signals (PC[0–5]), Port D GPIO signals (PD[0–5]), and Port E GPIO signals (PE[0–2]), respectively.

- 3. TIO[0-2] can be configured as GPIO signals.

- 4. CLKOUT, BCLK, BCLK, CAS, and RAS[0–3] are valid only for operating frequencies ≤100 MHz.

Figure 1-1. Signals Identified by Functional Group

1-2 Freescale Semiconductor

## 1.1 Power

Table 1-2. Power Inputs

| Power Name        | Description                                                                                                                                                                                         |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>CCP</sub>  | <b>PLL Power</b> — $V_{CC}$ dedicated for PLL use. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the $V_{CC}$ power rail.           |  |  |  |  |

| V <sub>CCQL</sub> | Quiet Core (Low) Power—An isolated power for the core processing logic. This input must be isolated externally from all other chip power inputs.                                                    |  |  |  |  |

| V <sub>CCQH</sub> | Quiet External (High) Power—A quiet power source for I/O lines. This input must be tied externally to all other chip power inputs, except V <sub>CCQL</sub> .                                       |  |  |  |  |

| V <sub>CCA</sub>  | Address Bus Power—An isolated power for sections of the address bus I/O drivers. This input must be tied externally to all other chip power inputs, except V <sub>CCQL</sub> .                      |  |  |  |  |

| V <sub>CCD</sub>  | <b>Data Bus Power</b> —An isolated power for sections of the data bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .             |  |  |  |  |

| V <sub>CCC</sub>  | <b>Bus Control Power</b> —An isolated power for the bus control I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                   |  |  |  |  |

| V <sub>CCH</sub>  | <b>Host Power</b> —An isolated power for the HI08 I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                                 |  |  |  |  |

| V <sub>CCS</sub>  | <b>ESSI, SCI, and Timer Power</b> —An isolated power for the ESSI, SCI, and timer I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> . |  |  |  |  |

| Note: The user m  | ust provide adequate external decoupling capacitors for all power connections.                                                                                                                      |  |  |  |  |

### 1.2 Ground

Table 1-3. Grounds

| Name              | Description                                                                                                                                                                                                                                              |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| GND <sub>P</sub>  | <b>PLL Ground</b> —Ground-dedicated for PLL use. The connection should be provided with an extremely low-impedance path to ground. $V_{CCP}$ should be bypassed to $GND_P$ by a 0.47 $\mu F$ capacitor located as close as possible to the chip package. |  |  |  |  |  |

| GND <sub>P1</sub> | PLL Ground 1—Ground-dedicated for PLL use. The connection should be provided with an extremely low-impedance path to ground.                                                                                                                             |  |  |  |  |  |

| GND               |                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Note: The user    | must provide adequate external decoupling capacitors for all GND connections.                                                                                                                                                                            |  |  |  |  |  |

## 1.3 Clock

Table 1-4. Clock Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                   |

|-------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

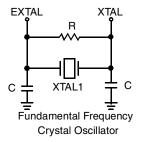

| EXTAL       | Input  | Input                 | <b>External Clock/Crystal Input</b> —Interfaces the internal crystal oscillator input to an external crystal or an external clock.                   |

| XTAL        | Output | Chip-driven           | <b>Crystal Output</b> —Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

DSP56L307 Technical Data, Rev. 6

Freescale Semiconductor 1-3

### 1.4 PLL

Table 0-1. Phase-Locked Loop Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                                                               |

|-------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

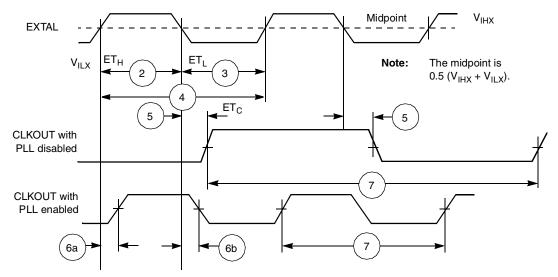

| CLKOUT      | Output | Chip-driven           | Clock Output—Provides an output clock synchronized to the internal core clock phase.                                                                                                             |

|             |        |                       | If the PLL is enabled and both the multiplication and division factors equal one, then CLKOUT is also synchronized to EXTAL.                                                                     |

|             |        |                       | If the PLL is disabled, the CLKOUT frequency is half the frequency of EXTAL.                                                                                                                     |

|             |        |                       | <b>Note:</b> At operating frequencies above 100 MHz, this signal produces a low-amplitude waveform that is not usable externally by other devices.                                               |

| PCAP        | Input  | Input                 | <b>PLL Capacitor</b> —An input connecting an off-chip capacitor to the PLL filter. Connect one capacitor terminal to PCAP and the other terminal to V <sub>CCP</sub> .                           |

|             |        |                       | If the PLL is not used, PCAP can be tied to V <sub>CC</sub> , GND, or left floating.                                                                                                             |

| PINIT       | Input  | Input                 | PLL Initial—During assertion of RESET, the value of PINIT is written into the PLL enable (PEN) bit of the PLL control (PCTL) register, determining whether the PLL is enabled or disabled.       |

| NMI         | Input  |                       | Nonmaskable Interrupt—After RESET deassertion and during normal instruction processing, this Schmitt-trigger input is the negative-edge-triggered NMI request internally synchronized to CLKOUT. |

### 1.5 External Memory Expansion Port (Port A)

**Note:** When the DSP56L307 enters a low-power standby mode (stop or wait), it releases bus mastership and tristates the relevant Port A signals: A[0–17], D[0–23], AA0/RAS0–AA3/RAS3, RD, WR, BB, CAS.

### 1.5.1 External Address Bus

Table 1-5. External Address Bus Signals

| Signal Name | Туре   | State During<br>Reset, Stop,<br>or Wait | Signal Description                                                                                                                                                                                                                                                                                        |

|-------------|--------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

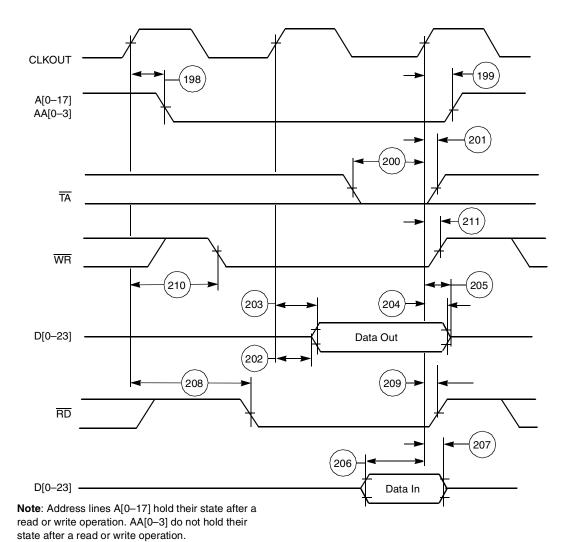

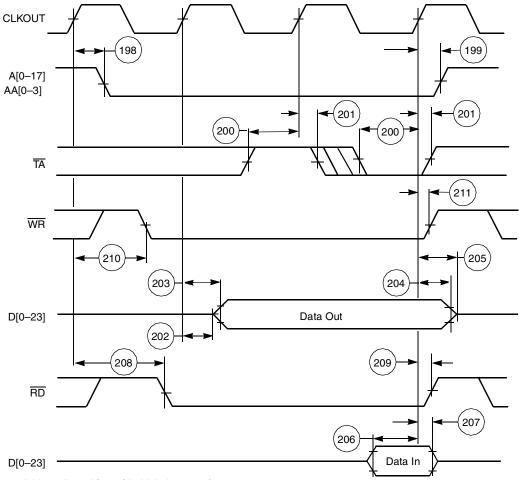

| A[0-17]     | Output | Tri-stated                              | Address Bus—When the DSP is the bus master, A[0–17] are active-high outputs that specify the address for external program and data memory accesses. Otherwise, the signals are tri-stated. To minimize power dissipation, A[0–17] do not change state when external memory spaces are not being accessed. |

### 1.5.2 External Data Bus

Table 1-6. External Data Bus Signals

| Signal Name | Туре          | State During<br>Reset | State During<br>Stop or Wait                           | Signal Description                                                                                                                                                                                                                                                                                                                                                          |

|-------------|---------------|-----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0-23]     | Input/ Output | Ignored Input         | Last state:<br>Input: Ignored<br>Output:<br>Last value | <b>Data Bus</b> —When the DSP is the bus master, D[0–23] are active-high, bidirectional input/outputs that provide the bidirectional data bus for external program and data memory accesses. Otherwise, D[0–23] drivers are tristated. If the last state is output, these lines have weak keepers that maintain the last output state even when all drivers are tri-stated. |

### 1.5.3 External Bus Control

Table 1-7. External Bus Control Signals

| Signal Name | Туре   | State During<br>Reset, Stop, or<br>Wait | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|--------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

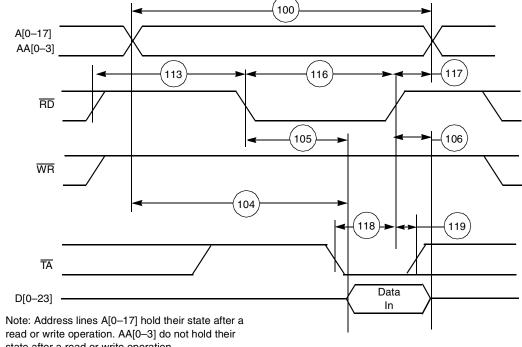

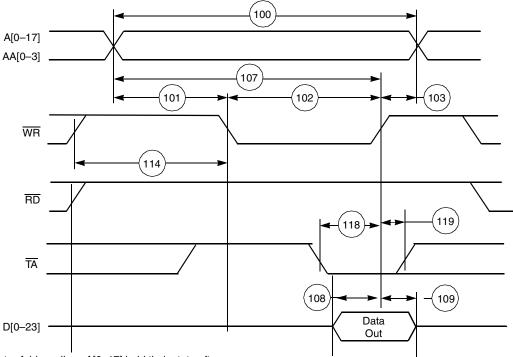

| AA[0-3]     | Output | Tri-stated                              | Address Attribute—When defined as AA, these signals can be used as chip selects or additional address lines. The default use defines a priority scheme under which only one AA signal can be asserted at a time. Setting the AA priority disable (APD) bit (Bit 14) of the Operating Mode Register, the priority mechanism is disabled and the lines can be used together as four external lines that can be decoded externally into 16 chip select signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RD          | Output | Tri-stated                              | <b>Read Enable</b> —When the DSP is the bus master, $\overline{RD}$ is an active-low output that is asserted to read external memory on the data bus (D[0–23]). Otherwise, $\overline{RD}$ is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WR          | Output | Tri-stated                              | <b>Write Enable</b> —When the DSP is the bus master, $\overline{WR}$ is an active-low output that is asserted to write external memory on the data bus (D[0–23]). Otherwise, the signals are tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TA          | Input  | Ignored Input                           | <b>Transfer Acknowledge</b> —If the DSP56L307 is the bus master and there is no external bus activity, or the DSP56L307 is not the bus master, the $\overline{\text{TA}}$ input is ignored. The $\overline{\text{TA}}$ input is a data transfer acknowledge (DTACK) function that can extend an external bus cycle indefinitely. Any number of wait states (1, 2infinity) can be added to the wait states inserted by the bus control register (BCR) by keeping $\overline{\text{TA}}$ deasserted. In typical operation, $\overline{\text{TA}}$ is deasserted at the start of a bus cycle, is asserted to enable completion of the bus cycle, and is deasserted before the next bus cycle. The current bus cycle completes one clock period after $\overline{\text{TA}}$ is asserted synchronous to CLKOUT. The number of wait states is determined by the $\overline{\text{TA}}$ input or by the BCR, whichever is longer. The BCR can be used to set the minimum number of wait states in external bus cycles.  To use the $\overline{\text{TA}}$ functionality, the BCR must be programmed to at least one wait state. A zero wait state access cannot be extended by $\overline{\text{TA}}$ deassertion; otherwise, improper operation may result. |

Freescale Semiconductor 1-5

Table 1-7.

External Bus Control Signals (Continued)

| Signal Name | Туре          | State During<br>Reset, Stop, or<br>Wait                                                                                                                                                                          | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

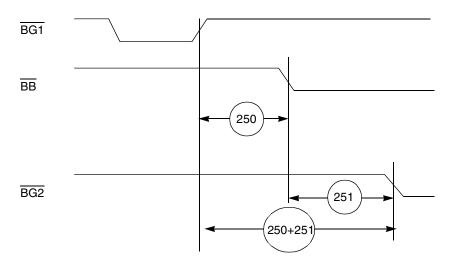

| BR          | Output        | Reset: Output<br>(deasserted)  State during<br>Stop/Wait<br>depends on BRH<br>bit setting: • BRH = 0: Output,<br>deasserted • BRH = 1:<br>Maintains last<br>state (that is, if<br>asserted, remains<br>asserted) | Bus Request—Asserted when the DSP requests bus mastership. $\overline{BR}$ is deasserted when the DSP no longer needs the bus. $\overline{BR}$ may be asserted or deasserted independently of whether the DSP56L307 is a bus master or a bus slave. Bus "parking" allows $\overline{BR}$ to be deasserted even though the DSP56L307 is the bus master. (See the description of bus "parking" in the $\overline{BB}$ signal description.) The bus request hold (BRH) bit in the BCR allows $\overline{BR}$ to be asserted under software control even though the DSP does not need the bus. $\overline{BR}$ is typically sent to an external bus arbitrator that controls the priority, parking, and tenure of each master on the same external bus. $\overline{BR}$ is affected only by DSP requests for the external bus, never for the internal bus. During hardware reset, $\overline{BR}$ is deasserted and the arbitration is reset to the bus slave state. |

| BG          | Input         | Ignored Input                                                                                                                                                                                                    | Bus Grant—Asserted by an external bus arbitration circuit when the DSP56L307 becomes the next bus master. When $\overline{BG}$ is asserted, the DSP56L307 must wait until $\overline{BB}$ is deasserted before taking bus mastership. When $\overline{BG}$ is deasserted, bus mastership is typically given up at the end of the current bus cycle. This may occur in the middle of an instruction that requires more than one external bus cycle for execution.  To ensure proper operation, the user must set the asynchronous bus arbitration enable (ABE) bit (Bit 13) in the Operating Mode Register. When this bit is set, $\overline{BG}$ and $\overline{BB}$ are synchronized internally. This adds a required delay between the deassertion of an initial $\overline{BG}$ input and the assertion of a subsequent $\overline{BG}$ input.                                                                                                                |

| BB          | Input/ Output | Ignored Input                                                                                                                                                                                                    | Bus Busy—Indicates that the bus is active. Only after \$\overline{BB}\$ is deasserted can the pending bus master become the bus master (and then assert the signal again). The bus master may keep \$\overline{BB}\$ asserted after ceasing bus activity regardless of whether \$\overline{BR}\$ is asserted or deasserted. Called "bus parking," this allows the current bus master to reuse the bus without rearbitration until another device requires the bus. \$\overline{BB}\$ is deasserted by an "active pull-up" method (that is, \$\overline{BB}\$ is driven high and then released and held high by an external pull-up resistor).  Notes:  1. See \$\overline{BG}\$ for additional information.  2. \$\overline{BB}\$ requires an external pull-up resistor.                                                                                                                                                                                         |

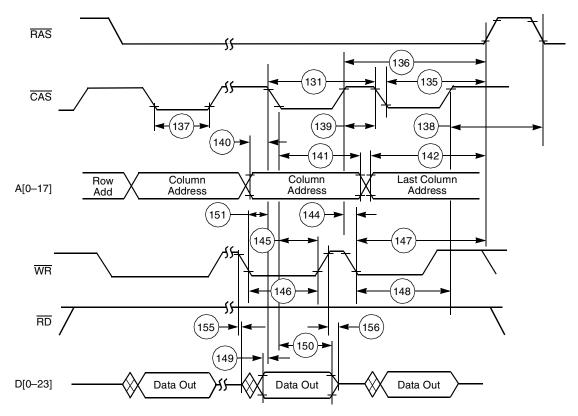

| CAS         | Output        | Tri-stated                                                                                                                                                                                                       | Column Address Strobe—When the DSP is the bus master, $\overline{CAS}$ is an active-low output used by DRAM to strobe the column address. Otherwise, if the Bus Mastership Enable (BME) bit in the DRAM control register is cleared, the signal is tri-stated.  Note: DRAM access is not supported above 100 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BCLK        | Output        | Tri-stated                                                                                                                                                                                                       | Bus Clock When the DSP is the bus master, BCLK is active when the address trace enable (ATE) bit in the Operating Mode Register is set. When BCLK is active and synchronized to CLKOUT by the internal PLL, BCLK precedes CLKOUT by one-fourth of a clock cycle.  Note: At operating frequencies above 100 MHz, this signal produces a low-amplitude waveform that is not usable externally by other devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BCLK        | Output        | Tri-stated                                                                                                                                                                                                       | Bus Clock Not When the DSP is the bus master, BCLK is the inverse of the BCLK signal. Otherwise, the signal is tri-stated.  Note: At operating frequencies above 100 MHz, this signal produces a low-amplitude waveform that is not usable externally by other devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

DSP56L307 Technical Data, Rev. 6

1-6 Freescale Semiconductor

## 1.6 Interrupt and Mode Control

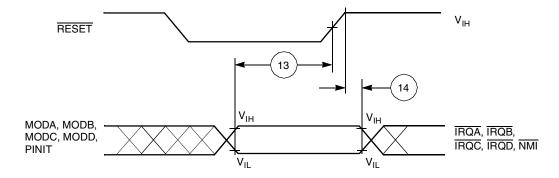

The interrupt and mode control signals select the chip operating mode as it comes out of hardware reset. After RESET is deasserted, these inputs are hardware interrupt request lines.

Table 1-8. Interrupt and Mode Control

| Signal Name | Туре  | State During<br>Reset    | Signal Description                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA        | Input | Schmitt-trigger<br>Input | Mode Select A—MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQĀ        | Input |                          | <b>External Interrupt Request A</b> —After reset, this input becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. If the processor is in the STOP or WAIT standby state and IRQA is asserted, the processor exits the STOP or WAIT state.                                                                |

| MODB        | Input | Schmitt-trigger<br>Input | Mode Select B—MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQB        | Input |                          | <b>External Interrupt Request B</b> —After reset, this input becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. If the processor is in the WAIT standby state and IRQB is asserted, the processor exits the WAIT state.                                                                                |

| MODC        | Input | Schmitt-trigger<br>Input | Mode Select C—MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQC        | Input |                          | <b>External Interrupt Request C</b> —After reset, this input becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. If the processor is in the WAIT standby state and IRQC is asserted, the processor exits the WAIT state.                                                                                |

| MODD        | Input | Schmitt-trigger<br>Input | Mode Select D—MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQD        | Input |                          | <b>External Interrupt Request D</b> —After reset, this input becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. If the processor is in the WAIT standby state and IRQD is asserted, the processor exits the WAIT state.                                                                                |

| RESET       | Input | Schmitt-trigger<br>Input | Reset—Places the chip in the Reset state and resets the internal phase generator. The Schmitt-trigger input allows a slowly rising input (such as a capacitor charging) to reset the chip reliably. When the RESET signal is deasserted, the initial chip operating mode is latched from the MODA, MODB, MODC, and MODD inputs. The RESET signal must be asserted after powerup. |

Freescale Semiconductor 1-7

### 1.7 Host Interface (HI08)

The HI08 provides a fast, 8-bit, parallel data port that connects directly to the host bus. The HI08 supports a variety of standard buses and connects directly to a number of industry-standard microcomputers, microprocessors, DSPs, and DMA hardware.

### 1.7.1 Host Port Usage Considerations

Careful synchronization is required when the system reads multiple-bit registers that are written by another asynchronous system. This is a common problem when two asynchronous systems are connected (as they are in the Host port). The considerations for proper operation are discussed in **Table 1-9**.

Table 1-9.

Host Port Usage Considerations

| Action                                        | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asynchronous read of receive byte registers   | When reading the receive byte registers, Receive register High (RXH), Receive register Middle (RXM), or Receive register Low (RXL), the host interface programmer should use interrupts or poll the Receive register Data Full (RXDF) flag that indicates data is available. This assures that the data in the receive byte registers is valid.                                                        |

| Asynchronous write to transmit byte registers | The host interface programmer should not write to the transmit byte registers, Transmit register High (TXH), Transmit register Middle (TXM), or Transmit register Low (TXL), unless the Transmit register Data Empty (TXDE) bit is set indicating that the transmit byte registers are empty. This guarantees that the transmit byte registers transfer valid data to the Host Receive (HRX) register. |

| Asynchronous write to host vector             | The host interface programmer must change the Host Vector (HV) register only when the Host Command bit (HC) is clear. This practice guarantees that the DSP interrupt control logic receives a stable vector.                                                                                                                                                                                          |

### 1.7.2 Host Port Configuration

HI08 signal functions vary according to the programmed configuration of the interface as determined by the 16 bits in the HI08 Port Control Register.

Table 1-10. Host Interface

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                        |

|-------------|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

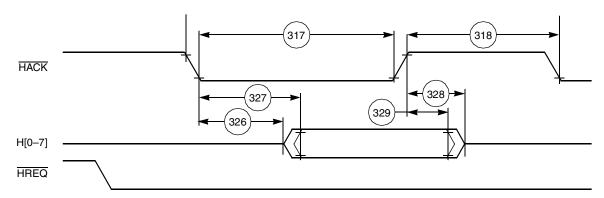

| H[0-7]      | Input/Output    | Ignored Input                        | <b>Host Data</b> —When the HI08 is programmed to interface with a non-multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional Data bus.                    |

| HAD[0-7]    | Input/Output    |                                      | <b>Host Address</b> —When the HI08 is programmed to interface with a multiplexed host bus and the HI function is selected, these signals are lines 0–7 of the bidirectional multiplexed Address/Data bus. |

| PB[0-7]     | Input or Output |                                      | Port B 0–7—When the HI08 is configured as GPIO through the HI08 Port Control Register, these signals are individually programmed as inputs or outputs through the HI08 Data Direction Register.           |

1-8 Freescale Semiconductor

Table 1-10. Host Interface (Continued)

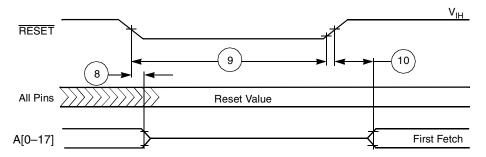

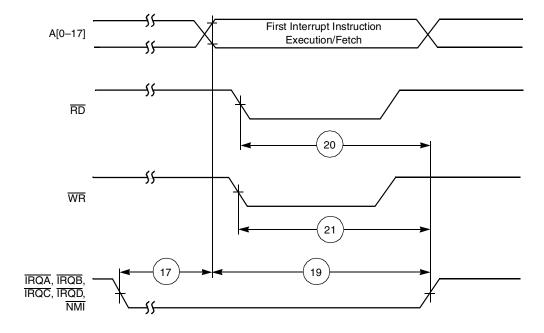

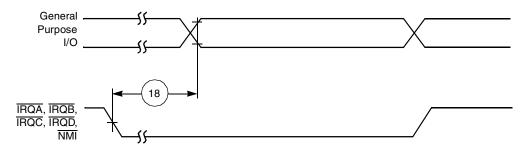

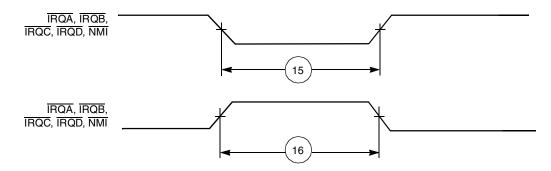

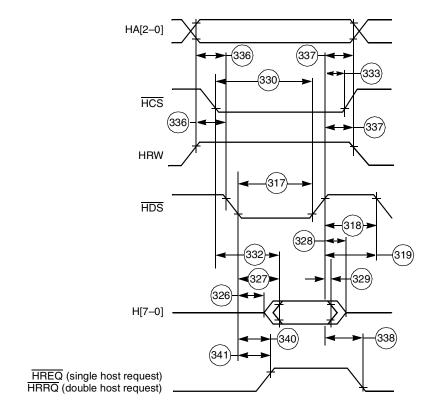

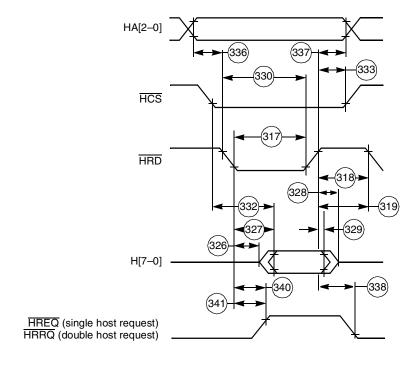

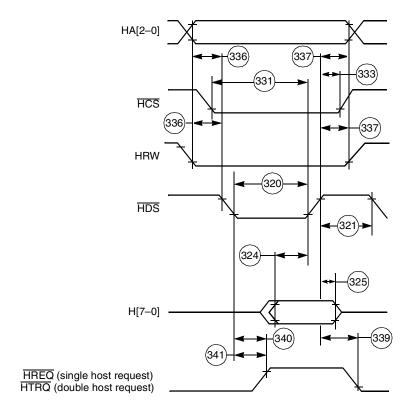

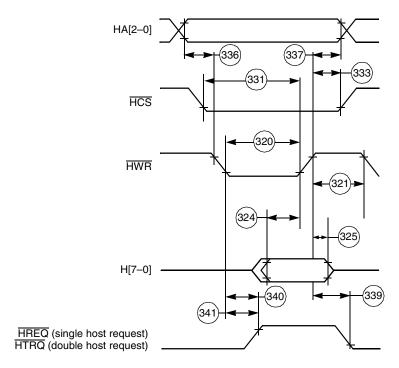

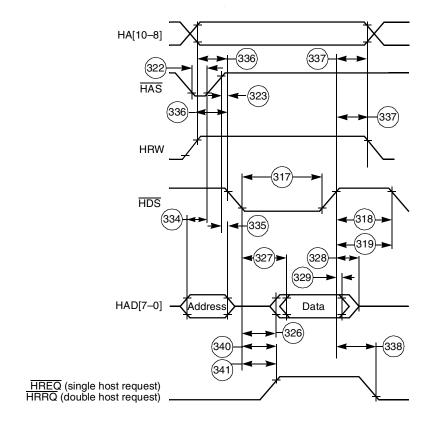

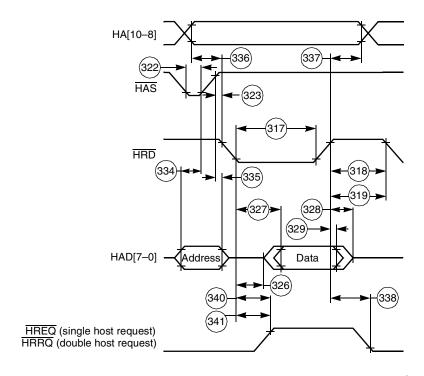

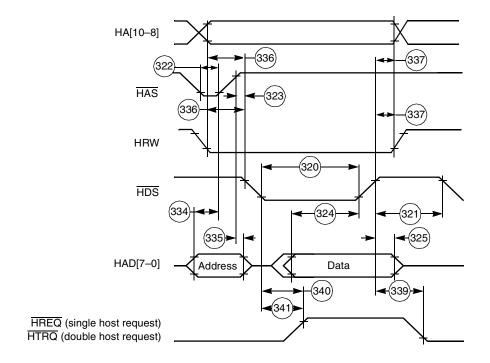

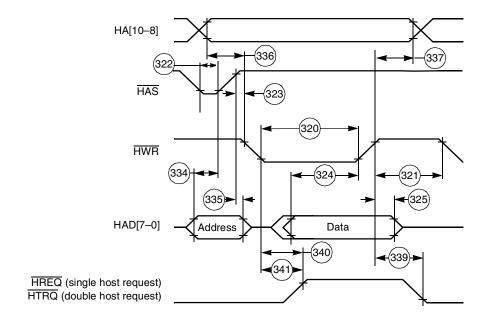

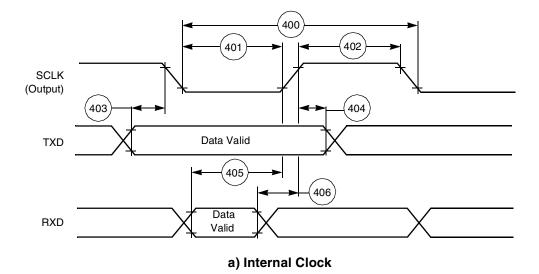

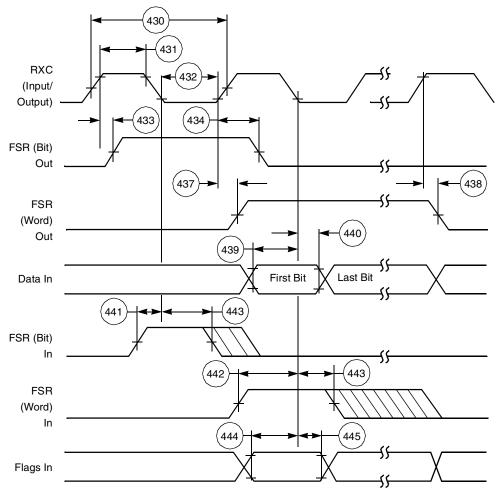

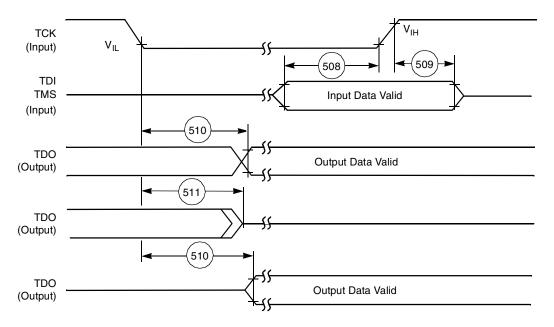

| Signal Name | Туре            | State During<br>Reset <sup>1,2</sup> | Signal Description                                                                                                                                                                                                                                                                                   |