5 V mixer/oscillator and low noise PLL synthesizer for hybrid terrestrial tuner (digital and analog)

Rev. 05 — 10 January 2007

**Product data sheet**

### 1. General description

The TDA6650TT; TDA6651TT is a programmable 3-band mixer/oscillator and low phase noise PLL synthesizer intended for pure 3-band tuner concepts applied to hybrid (digital and analog) or digital only terrestrial and cable TV reception.

Table 1. Different versions are available depending on the target application[1]

| Application                 | Type version    |

|-----------------------------|-----------------|

| hybrid (analog and digital) | TDA6650TT/C3    |

|                             | TDA6651TT/C3    |

| digital only                | TDA6650TT/C3/S2 |

|                             | TDA6651TT/C3/S2 |

|                             | TDA6651TT/C3/S3 |

[1] See Table 22 "Characteristics" for differences between TDA6651TT/C3/S2 and TDA6651TT/C3/S3.

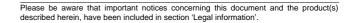

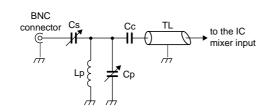

The device includes three double balanced mixers for low, mid and high bands, three oscillators for the corresponding bands, a switchable IF amplifier, a wideband AGC detector and a low noise PLL synthesizer. The frequencies of the three bands are shown in <a href="Table 2">Table 2</a>. Two pins are available between the mixer output and the IF amplifier input to enable IF filtering for improved signal handling and to improve the adjacent channel rejection.

Table 2. Recommended band limits in MHz

| Band                    | RF input             |                            | Oscillator |        |

|-------------------------|----------------------|----------------------------|------------|--------|

|                         | Min                  | Max                        | Min        | Max    |

| PAL and DVB-T tu        | ners for hybrid app  | olication <sup>[1]</sup>   |            |        |

| Low                     | 44.25                | 157.25                     | 83.15      | 196.15 |

| Mid                     | 157.25               | 443.25                     | 196.15     | 482.15 |

| High                    | 443.25               | 863.25                     | 482.15     | 902.15 |

| <b>DVB-T</b> tuners for | digital only applica | tion <u><sup>[2]</sup></u> |            |        |

| Low                     | 47.00                | 160.00                     | 83.15      | 196.15 |

| Mid                     | 160.00               | 446.00                     | 196.15     | 482.15 |

| High                    | 446.00               | 866.00                     | 482.15     | 902.15 |

<sup>[1]</sup> RF input frequency is the frequency of the corresponding picture carrier for analog standard.

The IF amplifier is switchable in order to drive both symmetrical and asymmetrical outputs. When it is used as an asymmetrical amplifier, the IFOUTB pin needs to be connected to the supply voltage  $V_{\text{CCA}}$ .

<sup>[2]</sup> RF input frequency is the frequency of the center of DVB-T channel.

5 V mixer/oscillator and low noise PLL synthesizer

Five open-drain PMOS ports are included on the IC. Two of them, BS1 and BS2, are also dedicated to the selection of the low, mid and high bands. PMOS port BS5 pin is shared with the ADC.

The AGC detector provides a control that can be used in a tuner to set the gain of the RF stage. Six AGC take-over points are available by software. Two programmable AGC time constants are available for search tuning and normal tuner operation.

The local oscillator signal is fed to the fractional-N divider. The divided frequency is compared to the comparison frequency into the fast phase detector which drives the charge pump. The loop amplifier is also on-chip, including the high-voltage transistor to drive directly the 33 V tuning voltage without the need to add an external transistor.

The comparison frequency is obtained from an on-chip crystal oscillator. The crystal frequency can be output to the XTOUT pin to drive the clock input of a digital demodulation IC.

Control data is entered via the I<sup>2</sup>C-bus; six serial bytes are required to address the device, select the Local Oscillator (LO) frequency, select the step frequency, program the output ports and set the charge pump current or select the ALBC mode, enable or disable the crystal output buffer, select the AGC take-over point and time constant and/or select a specific test mode. A status byte concerning the AGC level detector and the ADC voltage can be read out on the SDA line during a read operation. During a read operation, the loop 'in-lock' flag, the power-on reset flag and the automatic loop bandwidth control flag are read.

The device has 4 programmable addresses. Each address can be selected by applying a specific voltage to pin AS, enabling the use of multiple devices in the same system.

The I<sup>2</sup>C-bus is fast mode compatible, except for the timing as described in the functional description and is compatible with 5 V, 3.3 V and 2.5 V microcontrollers depending on the voltage applied to pin BVS.

### 2. Features

- Single-chip 5 V mixer/oscillator and low phase noise PLL synthesizer for TV and VCR tuners, dedicated to hybrid (digital and analog) as well as pure digital applications (DVB-T)

- Five possible step frequencies to cope with different digital terrestrial TV and analog TV standards

- **E**ight charge pump currents between 40  $\mu$ A and 600  $\mu$ A to reach the optimum phase noise performance over the bands

- Automatic Loop Bandwidth Control (ALBC) sets the optimum phase noise performance for DVB-T channels

- I<sup>2</sup>C-bus protocol compatible with 2.5 V, 3.3 V and 5 V microcontrollers:

- ◆ Address + 5 data bytes transmission (I<sup>2</sup>C-bus write mode)

- ◆ Address + 1 status byte (I<sup>2</sup>C-bus read mode)

- Four independent I<sup>2</sup>C-bus addresses.

- Five PMOS open-drain ports with 15 mA source capability for band switching and general purpose; one of these ports is combined with a 5-step ADC

- Wideband AGC detector for internal tuner AGC:

2 of 54

- Six programmable take-over points

- ◆ Two programmable time constants

- AGC flag.

- In-lock flag

- Crystal frequency output buffer

- 33 V tuning voltage output

- Fractional-N programmable divider

- Balanced mixers with a common emitter input for the low band and for the mid band (each single input)

- Balanced mixer with a common base input for the high band (balanced input)

- 2-pin asymmetrical oscillator for the low band

- 2-pin symmetrical oscillator for the mid band

- 4-pin symmetrical oscillator for the high band

- Switched concept IF amplifier with both asymmetrical and symmetrical outputs to drive low impedance or SAW filters i.e.  $500 \Omega / 40 pF$ .

## 3. Applications

For all applications, the recommendations given in the latest application note *AN10544* must be used.

### 3.1 Application summary

- Digital and analog terrestrial tuners (OFDM, PAL, etc.)

- Cable tuners (QAM)

- Digital TV sets

- Digital set-top boxes.

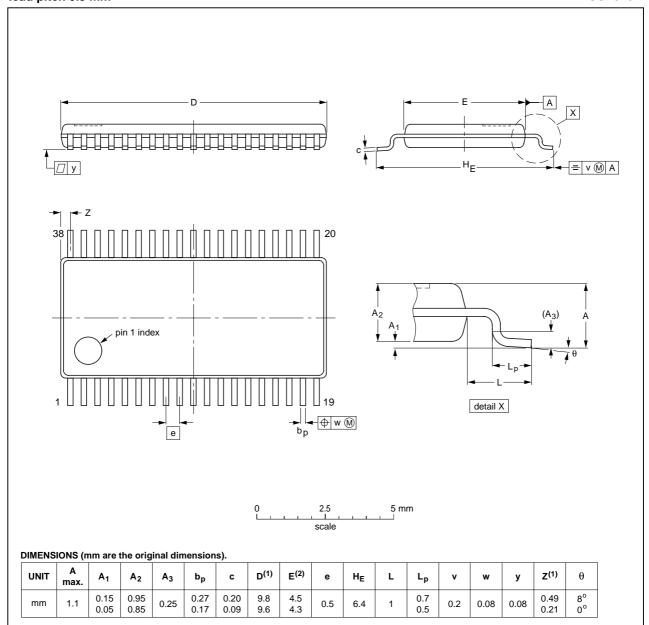

## 4. Ordering information

Table 3. Ordering information

| Type number     | Package |                                                                         |          |  |  |  |  |

|-----------------|---------|-------------------------------------------------------------------------|----------|--|--|--|--|

|                 | Name    | Description                                                             | Version  |  |  |  |  |

| TDA6650TT/C3    | TSSOP38 | plastic thin shrink small outline package; 38 leads; body width 4.4 mm; | SOT510-1 |  |  |  |  |

| TDA6650TT/C3/S2 |         | lead pitch 0.5 mm                                                       |          |  |  |  |  |

| TDA6651TT/C3    |         |                                                                         |          |  |  |  |  |

| TDA6651TT/C3/S2 |         |                                                                         |          |  |  |  |  |

| TDA6651TT/C3/S3 |         |                                                                         |          |  |  |  |  |

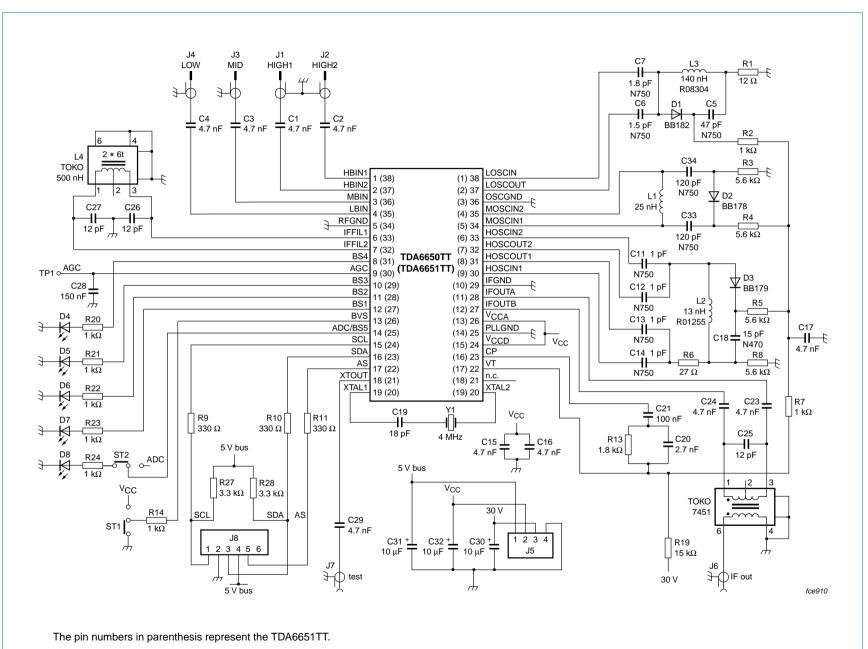

## 5. Block diagram

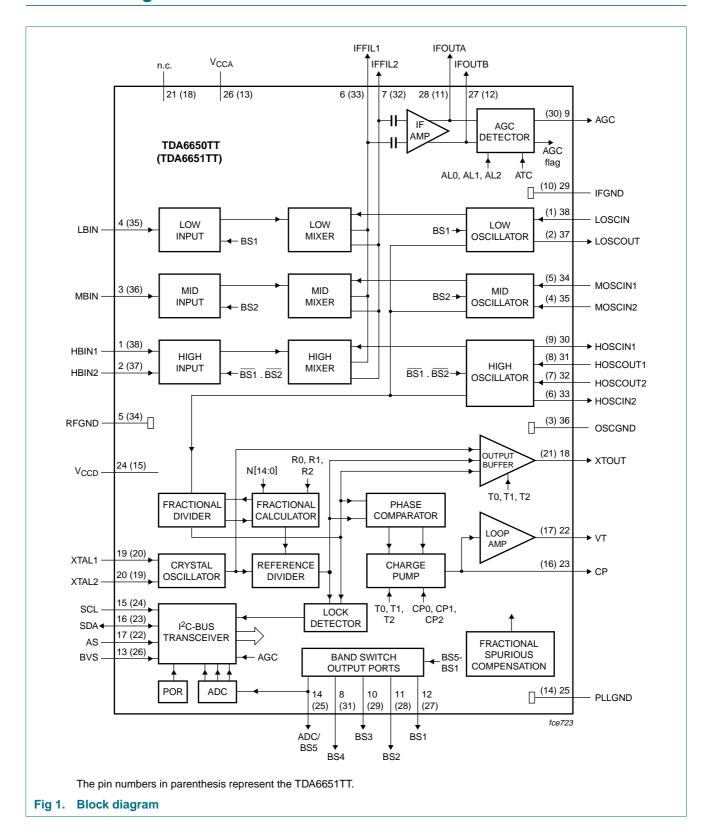

# 6. Pinning information

### 6.1 Pin description

Table 4. Pin description

| Symbol    | Pin                 |    | Description                                                                      |

|-----------|---------------------|----|----------------------------------------------------------------------------------|

| - j       | TDA6650TT TDA6651TT |    |                                                                                  |

| HBIN1     | 1                   | 38 | high band RF input 1                                                             |

| HBIN2     | 2                   | 37 | high band RF input 2                                                             |

| MBIN      | 3                   | 36 | mid band RF input                                                                |

| LBIN      | 4                   | 35 | low band RF input                                                                |

| RFGND     | 5                   | 34 | RF ground                                                                        |

| IFFIL1    | 6                   | 33 | IF filter output 1                                                               |

| IFFIL2    | 7                   | 32 | IF filter output 2                                                               |

| BS4       | 8                   | 31 | PMOS open-drain output port 4 for general purpose                                |

| AGC       | 9                   | 30 | AGC output                                                                       |

| BS3       | 10                  | 29 | PMOS open-drain output port 3 for general purpose                                |

| BS2       | 11                  | 28 | PMOS open-drain output port 2 to select the mid band                             |

| BS1       | 12                  | 27 | PMOS open-drain output port 1 to select the low band                             |

| BVS       | 13                  | 26 | bus voltage selection input                                                      |

| ADC/BS5   | 14                  | 25 | ADC input or PMOS open-drain output port 5 for general purpose                   |

| SCL       | 15                  | 24 | I <sup>2</sup> C-bus serial clock input                                          |

| SDA       | 16                  | 23 | I <sup>2</sup> C-bus serial data input and output                                |

| AS        | 17                  | 22 | I <sup>2</sup> C-bus address selection input                                     |

| XTOUT     | 18                  | 21 | crystal frequency buffer output                                                  |

| XTAL1     | 19                  | 20 | crystal oscillator input 1                                                       |

| XTAL2     | 20                  | 19 | crystal oscillator input 2                                                       |

| n.c       | 21                  | 18 | not connected                                                                    |

| VT        | 22                  | 17 | tuning voltage output                                                            |

| СР        | 23                  | 16 | charge pump output                                                               |

| $V_{CCD}$ | 24                  | 15 | supply voltage for the PLL part                                                  |

| PLLGND    | 25                  | 14 | PLL ground                                                                       |

| $V_{CCA}$ | 26                  | 13 | supply voltage for the analog part                                               |

| IFOUTB    | 27                  | 12 | IF output B for symmetrical amplifier and asymmetrical IF amplifier switch input |

| IFOUTA    | 28                  | 11 | IF output A                                                                      |

| IFGND     | 29                  | 10 | IF ground                                                                        |

| HOSCIN1   | 30                  | 9  | high band oscillator input 1                                                     |

| HOSCOUT1  | 31                  | 8  | high band oscillator output 1                                                    |

| HOSCOUT2  | 32                  | 7  | high band oscillator output 2                                                    |

| HOSCIN2   | 33                  | 6  | high band oscillator input 2                                                     |

5 of 54

Table 4. Pin description...continued

| Symbol  | Pin       |           | Description                 |

|---------|-----------|-----------|-----------------------------|

|         | TDA6650TT | TDA6651TT |                             |

| MOSCIN1 | 34        | 5         | mid band oscillator input 1 |

| MOSCIN2 | 35        | 4         | mid band oscillator input 2 |

| OSCGND  | 36        | 3         | oscillators ground          |

| LOSCOUT | 37        | 2         | low band oscillator output  |

| LOSCIN  | 38        | 1         | low band oscillator input   |

### 6.2 Pinning

## 7. Functional description

### 7.1 Mixer, Oscillator and PLL (MOPLL) functions

Bit BS1 enables the BS1 port, the low band mixer and the low band oscillator. Bit BS2 enables the BS2 port, the mid band mixer and the mid band oscillator. When both BS1 and BS2 bits are logic 0, the high band mixer and the high band oscillator are enabled.

The oscillator signal is applied to the fractional-N programmable divider. The divided signal  $f_{\text{div}}$  is fed to the phase comparator where it is compared in both phase and frequency with the comparison frequency  $f_{\text{comp}}$ . This frequency is derived from the signal present on the crystal oscillator  $f_{\text{xtal}}$  and divided in the reference divider. There is a fractional calculator on the chip that generates the data for the fractional divider as well as

the reference divider ratio, depending on the step frequency selected. The crystal oscillator requires a 4 MHz crystal in series with an 18 pF capacitor between pins XTAL1 and XTAL2.

The output of the phase comparator drives the charge pump and the loop amplifier section. This amplifier has an on-chip high voltage drive transistor. Pin CP is the output of the charge pump, and pin VT is the pin to drive the tuning voltage to the varicap diodes of the oscillators and the tracking filters. The loop filter has to be connected between pins CP and VT. The spurious signals introduced by the fractional divider are automatically compensated by the spurious compensation block.

It is possible to drive the clock input of a digital demodulation IC from pin XTOUT with the 4 MHz signal from the crystal oscillator. This output is also used to output  $\frac{1}{2}f_{div}$  and  $f_{comp}$  signals in a specific test mode (see <u>Table 9</u>). It is possible to switch off this output, which is recommended when it is not used.

For test and alignment purposes, it is also possible to release the tuning voltage output by selecting the sinking mode (see Table 9), and by applying an external voltage on pin VT.

In addition to the BS1 and BS2 output ports that are used for the band selection, there are three general purpose ports BS3, BS4 and BS5. All five ports are PMOS open-drain type, each with 15 mA drive capability. The connection for port BS5 and the ADC input is combined on one pin. It is not possible to use the ADC if port BS5 is used.

The AGC detector compares the level at the IF amplifier output to a reference level which is selected from 6 different levels via the I<sup>2</sup>C-bus. The time constant of the AGC can be selected via the I<sup>2</sup>C-bus to cope with normal operation as well as with search operation.

When the output level on pin AGC is higher than the threshold  $V_{RMH}$ , then bit AGC = 1. When the output level on pin AGC is lower than the threshold  $V_{RML}$ , then bit AGC = 0. Between these two thresholds, bit AGC is not defined. The status of the AGC bit can be read via the  $I^2$ C-bus according to the read mode as described in Table 15.

### 7.2 I<sup>2</sup>C-bus voltage

The  $I^2C$ -bus lines SCL and SDA can be connected to an  $I^2C$ -bus system tied to 2.5 V, 3.3 V or 5 V. The choice of the bus input threshold voltages is made with pin BVS that can be left open-circuit, connected to the supply voltage or to ground (see <u>Table 5</u>).

Table 5. I<sup>2</sup>C-bus voltage selection

| Pin BVS connection | Bus voltage | Logic level   | Logic level     |  |  |

|--------------------|-------------|---------------|-----------------|--|--|

|                    |             | LOW           | HIGH            |  |  |

| To ground          | 2.5 V       | 0 V to 0.75 V | 1.75 V to 5.5 V |  |  |

| Open-circuit       | 3.3 V       | 0 V to 1.0 V  | 2.3 V to 5.5 V  |  |  |

| To V <sub>CC</sub> | 5 V         | 0 V to 1.5 V  | 3.0 V to 5.5 V  |  |  |

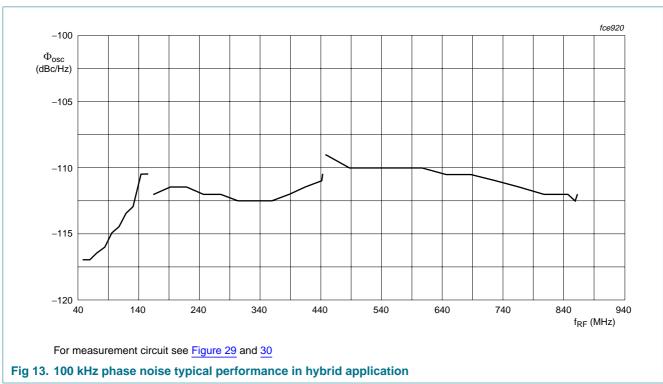

### 7.3 Phase noise, I<sup>2</sup>C-bus traffic and crosstalk

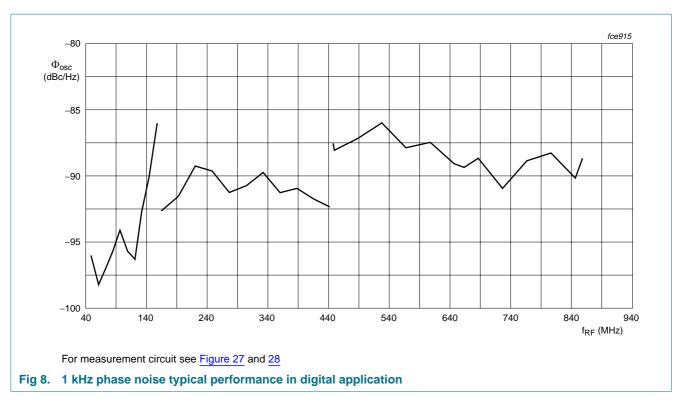

While the TDA6650TT; TDA6651TT is dedicated for hybrid terrestrial applications, the low noise PLL will clean up the noise spectrum of the VCOs close to the carrier to reach noise levels at 1 kHz offset from the carrier compatible with e.g. DVB-T reception.

5 V mixer/oscillator and low noise PLL synthesizer

Linked to this noise improvement, some disturbances may become visible while they were not visible because they were hidden into the noise in analog dedicated applications and circuits.

This is especially true for disturbances coming from the I<sup>2</sup>C-bus traffic, whatever this traffic is intended for the MOPLL or for another slave on the bus.

To avoid this I<sup>2</sup>C-bus crosstalk and be able to have a clean noise spectrum, it is necessary to use a bus gate that enables the signal on the bus to drive the MOPLL only when the communication is intended for the tuner part (such a kind of I<sup>2</sup>C-bus gate is included into the NXP terrestrial channel decoders), and to avoid unnecessary repeated sending of the same information.

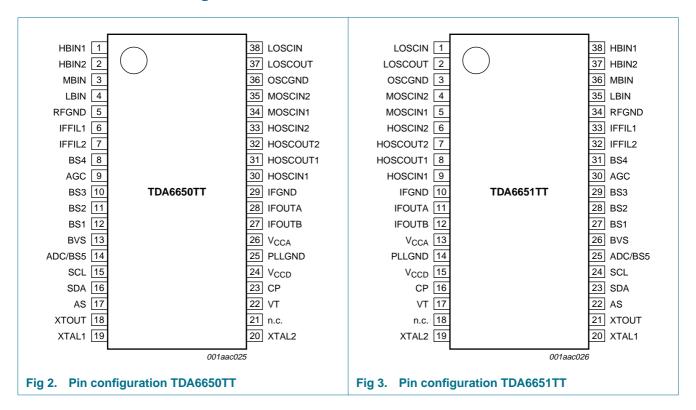

### 8. I<sup>2</sup>C-bus protocol

The TDA6650TT; TDA6651TT is controlled via the two-wire  $I^2C$ -bus. For programming, there is one device address (7 bits) and the  $R/\overline{W}$  bit for selecting read or write mode. To be able to have more than one MOPLL in an  $I^2C$ -bus system, one of four possible addresses is selected depending on the voltage applied to address selection pin AS (see Table 8).

The TDA6650TT; TDA6651TT fulfils the fast mode  $I^2C$ -bus, according to the NXP  $I^2C$ -bus specification, except for the timing as described in <u>Figure 4</u>. The  $I^2C$ -bus interface is designed in such a way that the pins SCL and SDA can be connected to 5 V, 3.3 V or to 2.5 V pulled-up  $I^2C$ -bus lines, depending on the voltage applied to pin BVS (see <u>Table 5</u>).

### 8.1 Write mode; $R/\overline{W} = 0$

After the address transmission (first byte), data bytes can be sent to the device (see Table 6). Five data bytes are needed to fully program the TDA6650TT; TDA6651TT. The I<sup>2</sup>C-bus transceiver has an auto-increment facility that permits programming the device within one single transmission (address + 5 data bytes).

The TDA6650TT; TDA6651TT can also be partly programmed on the condition that the first data byte following the address is byte 2 (divider byte 1) or byte 4 (control byte 1). The first bit of the first data byte transmitted indicates whether byte 2 (first bit = 0) or byte 4 (first bit = 1) will follow. Until an I $^2$ C-bus STOP condition is sent by the controller, additional data bytes can be entered without the need to re-address the device. The fractional calculator is updated only at the end of the transmission (STOP condition). Each control byte is loaded after the 8th clock pulse of the corresponding control byte. Main divider data are valid only if no new I $^2$ C-bus transmission is started (START condition) during the computation period of 50  $\mu s$ .

Both DB1 and DB2 need to be sent to change the main divider ratio. If the value of the ratio selection bits R2, R1 and R0 are changed, the bytes DB1 and DB2 have to be sent in the same transmission.

Table 6. I<sup>2</sup>C-bus write data format

| Name                  | Byte | Bit    | Bit     |     |     |     |     |     |                      | Ack |

|-----------------------|------|--------|---------|-----|-----|-----|-----|-----|----------------------|-----|

|                       |      | MSB[1] |         |     |     |     |     |     | LSB                  |     |

| Address byte          | 1    | 1      | 1       | 0   | 0   | 0   | MA1 | MA0 | $R/\overline{W} = 0$ | Α   |

| Divider byte 1 (DB1)  | 2    | 0      | N14     | N13 | N12 | N11 | N10 | N9  | N8                   | Α   |

| Divider byte 2 (DB2)  | 3    | N7     | N6      | N5  | N4  | N3  | N2  | N1  | N0                   | Α   |

| Control byte 1 (CB1); | 4    | 1      | T/A = 1 | T2  | T1  | T0  | R2  | R1  | R0                   | Α   |

| see Table 7           |      | 1      | T/A = 0 | 0   | 0   | ATC | AL2 | AL1 | AL0                  | Α   |

| Control byte 2 (CB2)  | 5    | CP2    | CP1     | CP0 | BS5 | BS4 | BS3 | BS2 | BS1                  | Α   |

<sup>[1]</sup> MSB is transmitted first.

Table 7. Description of write data format bits

| Description                                                                                                         |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                     |  |  |  |  |  |

| acknowledge                                                                                                         |  |  |  |  |  |

| programmable address bits; see Table 8                                                                              |  |  |  |  |  |

| logic 0 for write mode                                                                                              |  |  |  |  |  |

| programmable LO frequency; $N = N14 \times 2^{14} + N13 \times 2^{13} + N12 \times 2^{12} + + N1 \times 2^{1} + N0$ |  |  |  |  |  |

| test/AGC bit                                                                                                        |  |  |  |  |  |

| T/A = 0: the next 6 bits sent are AGC settings                                                                      |  |  |  |  |  |

| T/A = 1: the next 6 bits sent are test and reference divider ratio settings                                         |  |  |  |  |  |

| test bits; see Table 9                                                                                              |  |  |  |  |  |

| reference divider ratio and programmable frequency step; see Table 10                                               |  |  |  |  |  |

| AGC current setting and time constant; capacitor on pin AGC = 150 nF                                                |  |  |  |  |  |

| ATC = 0: AGC current = 220 nA; AGC time constant = 2 s                                                              |  |  |  |  |  |

| ATC = 1: AGC current = 9 $\mu$ A; AGC time constant = 50 ms                                                         |  |  |  |  |  |

| AGC take-over point bits; see <u>Table 11</u>                                                                       |  |  |  |  |  |

| charge pump current; see <u>Table 12</u>                                                                            |  |  |  |  |  |

| PMOS ports control bits                                                                                             |  |  |  |  |  |

| BSn = 0: corresponding port is off, high-impedance state (status at power-on reset)                                 |  |  |  |  |  |

| BSn = 1: corresponding port is on; $V_O = V_{CC} - V_{DS(sat)}$                                                     |  |  |  |  |  |

|                                                                                                                     |  |  |  |  |  |

### 8.1.1 I<sup>2</sup>C-bus address selection

The device address contains programmable address bits MA1 and MA0, which offer the possibility of having up to four MOPLL ICs in one system. <u>Table 8</u> gives the relationship between the voltage applied to the AS input and the MA1 and MA0 bits.

Table 8. Address selection

| Voltage applied to pin AS                                | MA1 | MA0 |

|----------------------------------------------------------|-----|-----|

| 0 V to 0.1V <sub>CC</sub>                                | 0   | 0   |

| 0.2V <sub>CC</sub> to 0.3V <sub>CC</sub> or open-circuit | 0   | 1   |

| 0.4V <sub>CC</sub> to 0.6V <sub>CC</sub>                 | 1   | 0   |

| 0.9V <sub>CC</sub> to V <sub>CC</sub>                    | 1   | 1   |

### 8.1.2 XTOUT output buffer and mode setting

The crystal frequency can be sent to pin XTOUT and used in the application, for example to drive the clock input of a digital demodulator, saving a quartz crystal in the bill of material. To output  $f_{xtal}$ , it is necessary to set T[2:0] to 001. If the output signal on this pin is not used, it is recommended to disable it, by setting T[2:0] to 000. This pin is also used to output  $\frac{1}{2}f_{div}$  and  $f_{comp}$  in a test mode. At power-on, the XTOUT output buffer is set to on, supplying the  $f_{xtal}$  signal. The relation between the signal on pin XTOUT and the setting of the T[2:0] bits is given in Table 9.

Table 9. XTOUT buffer status and test modes

| T2 | T1 | T0 | Pin XTOUT                   | Mode                              |

|----|----|----|-----------------------------|-----------------------------------|

| 0  | 0  | 0  | disabled                    | normal mode with XTOUT buffer off |

| 0  | 0  | 1  | f <sub>xtal</sub> (4 MHz)   | normal mode with XTOUT buffer on  |

| 0  | 1  | 0  | $\frac{1}{2}f_{\text{div}}$ | charge pump off                   |

| 0  | 1  | 1  | f <sub>xtal</sub> (4 MHz)   | switch ALBC on or off[1]          |

| 1  | 0  | 0  | $f_{comp}$                  | test mode                         |

| 1  | 0  | 1  | $\frac{1}{2}f_{\text{div}}$ | test mode                         |

| 1  | 1  | 0  | f <sub>xtal</sub> (4 MHz)   | charge pump sinking current[2]    |

| 1  | 1  | 1  | disabled                    | charge pump sourcing current      |

<sup>[1]</sup> Automatic Loop Bandwidth Control (ALBC) is disabled at power-on reset. After power-on reset this feature is enabled by setting T[2:0] = 011. To disable again the ALBC, set T[2:0] = 011 again. This test mode acts like a toggle switch, which means each time it is set the status of the ALBC changes. To toggle the ALBC, two consecutive Control byte 1s (CB1), should be sent: one byte with T[2:0] = 011 indicating that ALBC will be switched on or off and one byte programming the test mode to be selected (see Table 30, example of I<sup>2</sup>C-bus sequence).

### 8.1.3 Step frequency setting

The step frequency is set by three bits, giving five steps to cope with different application requirements.

The reference divider ratio is automatically set depending on bits R2, R1 and R0. The phase detector works at either 4 MHz, 2 MHz or 1 MHz.

<u>Table 10</u> shows the step frequencies and corresponding reference divider ratios. When the value of bits R2, R1 and R0 are changed, it is necessary to re-send the data bytes DB1 and DB2.

<sup>[2]</sup> This is the default mode at power-on reset. This mode disables the tuning voltage.

Table 10. Reference divider ratio select bits

| R2 | R1 | R0 | Reference divider ratio | Frequency comparison | Frequency step |

|----|----|----|-------------------------|----------------------|----------------|

| 0  | 0  | 0  | 2                       | 2 MHz                | 62.5 kHz       |

| 0  | 0  | 1  | 1                       | 4 MHz                | 142.86 kHz     |

| 0  | 1  | 0  | 1                       | 4 MHz                | 166.67 kHz     |

| 0  | 1  | 1  | 4                       | 1 MHz                | 50 kHz         |

| 1  | 0  | 0  | 1                       | 4 MHz                | 125 kHz        |

| 1  | 0  | 1  | -                       | -                    | reserved       |

| 1  | 1  | 0  | -                       | -                    | reserved       |

| 1  | 1  | 1  | -                       | -                    | reserved       |

### 8.1.4 AGC detector setting

The AGC take-over point can be selected out of 6 levels according to Table 11.

Table 11. AGC programming

| AL2 | AL1 | AL0 | Typical take-over point level |

|-----|-----|-----|-------------------------------|

| 0   | 0   | 0   | 124 dBμV (p-p)                |

| 0   | 0   | 1   | <u>11</u> 121 dBμV (p-p)      |

| 0   | 1   | 0   | <u>11</u> 118 dBμV (p-p)      |

| 0   | 1   | 1   | [2] 115 dBμV (p-p)            |

| 1   | 0   | 0   | 112 dBμV (p-p)                |

| 1   | 0   | 1   | [2] 109 dBμV (p-p)            |

| 1   | 1   | 0   | [3] I <sub>AGC</sub> = 0 A    |

| 1   | 1   | 1   | [4] V <sub>AGC</sub> = 3.5 V  |

<sup>[1]</sup> This take-over point is available for both symmetrical and asymmetrical modes.

### 8.1.5 Charge pump current setting

The charge pump current can be chosen from 8 values depending on the value of bits CP2, CP1 and CP0 bits; see <u>Table 12</u>. The programming of the CP bits are not taken into account when ALBC mode is in use.

Table 12. Charge pump current

| CP2 | CP1 | CP0 | Charge pump current number | Typical current (absolute value in $\mu$ A) |

|-----|-----|-----|----------------------------|---------------------------------------------|

| 0   | 0   | 0   | 1                          | 38                                          |

| 0   | 0   | 1   | 2                          | 54                                          |

| 0   | 1   | 0   | 3                          | 83                                          |

| 0   | 1   | 1   | 4                          | 122                                         |

| 1   | 0   | 0   | 5                          | 163                                         |

<sup>[2]</sup> This take-over point is available for asymmetrical mode only.

<sup>[3]</sup> The AGC current sources are disabled. The AGC output goes into a high-impedance state and an external AGC source can be connected in parallel and will not be influenced.

<sup>[4]</sup> The AGC detector is disabled and  $I_{AGC} = 9 \mu A$ .

Table 12. Charge pump current...continued

| CP2 | CP1 | CP0 | Charge pump current number | Typical current (absolute value in μA) |

|-----|-----|-----|----------------------------|----------------------------------------|

| 1   | 0   | 1   | 6                          | 254                                    |

| 1   | 1   | 0   | 7                          | 400                                    |

| 1   | 1   | 1   | 8                          | 580                                    |

### 8.1.6 Automatic Loop Bandwidth Control (ALBC)

In a PLL controlled VCO in which the PLL reduces phase noise close to the carrier, there is an optimum loop bandwidth corresponding to the minimum integrated phase jitter. This loop bandwidth depends on different parameters like the VCO slope, the loop filter components, the dividing ratio and the gain of the phase detector and charge pump.

In order to reach the best phase noise performance it is necessary, especially in a wideband system like a digital tuner, to set the charge pump current to different values depending on the band and frequency used. This is to cope with the variations of the different parameters that set the bandwidth. The selection can be done in the application and requires for each frequency to program not only the divider ratios, but also the band and the best charge pump current.

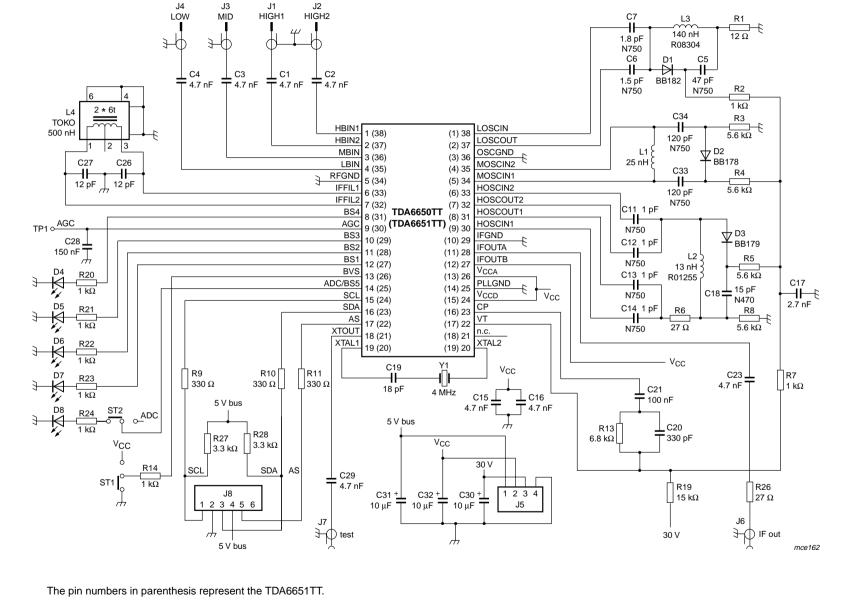

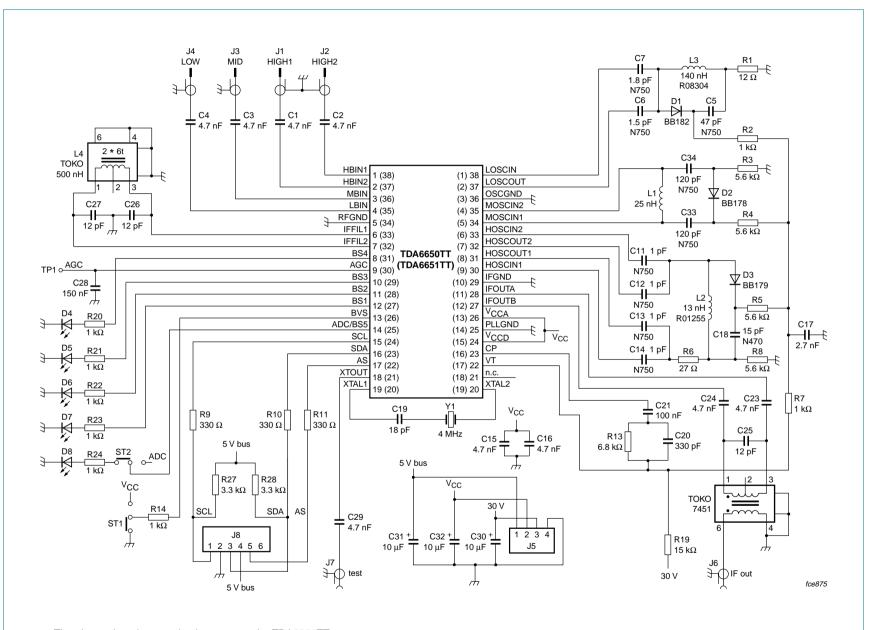

The TDA6650TT; TDA6651TT includes the ALBC feature that automatically sets the band and the charge pump current, provided the IC is used in the DVB-T standard application shown in Figure 27 and 28. This feature is activated by setting bits T[2:0] = 011 after power-on reset. This feature is disabled when the same bits are set again. When ALBC is activated, the output ports BS1, BS2 and BS3 are not programmed by the corresponding BS bits, but are set according to Table 13 and 14. When ALBC is active, bit ALBC = 1. Table 14 summarizes the programming of the band selection and the charge pump current when ALBC is active.

Table 13. ALBC settings

| Bit  |     |     |     | Band      | Charge pump      | Port               | Port   |     |  |  |

|------|-----|-----|-----|-----------|------------------|--------------------|--------|-----|--|--|

| ALBC | BS3 | BS2 | BS1 | selected  | current          | BS3                | BS2    | BS1 |  |  |

| 0    | X   | 0   | 0   | high      | see Table 14     | follows<br>bit BS3 | off    | off |  |  |

| 0    | X   | 0   | 1   | low       | see Table 14     | follows<br>bit BS3 | off    | on  |  |  |

| 0    | Χ   | 1   | 0   | mid       | see Table 14     | follows<br>bit BS3 | on     | off |  |  |

| 0    | Χ   | 1   | 1   | forbidden |                  |                    |        |     |  |  |

| 1    | Χ   | Χ   | Χ   | depends o | n LO program, sh | nown in <u>Ta</u>  | ble 14 |     |  |  |

Table 14. ALBC band selection and charge current setting

| LO frequency       | Band | Charge pump current number |

|--------------------|------|----------------------------|

| 80 MHz to 92 MHz   | low  | 2                          |

| 92 MHz to 144 MHz  | low  | 3                          |

| 144 MHz to 156 MHz | low  | 4                          |

| 156 MHz to 176 MHz | low  | 5                          |

| 176 MHz to 184 MHz | low  | 6                          |

TDA6650TT\_6651TT\_5 © NXP B.V. 2007. All rights reserved.

Table 14. ALBC band selection and charge current setting...continued

| LO frequency       | Band | Charge pump current number |

|--------------------|------|----------------------------|

| 184 MHz to 196 MHz | low  | 7                          |

| 196 MHz to 224 MHz | mid  | 2                          |

| 224 MHz to 296 MHz | mid  | 3                          |

| 296 MHz to 380 MHz | mid  | 4                          |

| 380 MHz to 404 MHz | mid  | 5                          |

| 404 MHz to 448 MHz | mid  | 6                          |

| 448 MHz to 472 MHz | mid  | 7                          |

| 472 MHz to 484 MHz | mid  | 8                          |

| 484 MHz to 604 MHz | high | 4                          |

| 604 MHz to 676 MHz | high | 5                          |

| 676 MHz to 752 MHz | high | 6                          |

| 752 MHz to 868 MHz | high | 7                          |

| 868 MHz to 904 MHz | high | 8                          |

### 8.2 Read mode; $R/\overline{W} = 1$

Data can be read from the device by setting the R/W bit to 1 (see <u>Table 15</u>). After the device address has been recognized, the device generates an acknowledge pulse and the first data byte (status byte) is transferred on the SDA line (MSB first). Data is valid on the SDA line during a HIGH level of the SCL clock signal.

A second data byte can be read from the device if the microcontroller generates an acknowledge on the SDA line (master acknowledge). End of transmission will occur if no master acknowledge occurs. The device will then release the data line to allow the microcontroller to generate a STOP condition.

Table 15. I<sup>2</sup>C-bus read data format

| Name         | Byte | Bit    | Bit |      |   |     |     |     |                      | ACK |

|--------------|------|--------|-----|------|---|-----|-----|-----|----------------------|-----|

|              |      | MSB[1] |     |      |   |     |     |     | LSB                  |     |

| Address byte | 1    | 1      | 1   | 0    | 0 | 0   | MA1 | MA0 | $R/\overline{W} = 1$ | Α   |

| Status byte  | 2    | POR    | FL  | ALBC | 1 | AGC | A2  | A1  | A0                   | -   |

<sup>[1]</sup> MSB is transmitted first.

Table 16. Description of read data format bits

| Bit | Description               |  |  |  |  |  |  |

|-----|---------------------------|--|--|--|--|--|--|

| A   | acknowledge bit           |  |  |  |  |  |  |

| POR | power-on reset flag       |  |  |  |  |  |  |

|     | POR = 0, normal operation |  |  |  |  |  |  |

|     | POR = 1, power-on reset   |  |  |  |  |  |  |

| FL  | in-lock flag              |  |  |  |  |  |  |

|     | FL = 0, not locked        |  |  |  |  |  |  |

|     | FL = 1, the PLL is locked |  |  |  |  |  |  |

TDA6650TT\_6651TT\_5 © NXP B.V. 2007. All rights reserved.

Table 16. Description of read data format bits...continued

| Bit        | Description                                                   |  |  |  |  |  |

|------------|---------------------------------------------------------------|--|--|--|--|--|

| ALBC       | automatic loop bandwidth control flag                         |  |  |  |  |  |

|            | ALBC = 0, no automatic loop bandwidth control                 |  |  |  |  |  |

|            | ALBC = 1, automatic loop bandwidth control selected           |  |  |  |  |  |

| AGC        | internal AGC flag                                             |  |  |  |  |  |

|            | AGC = 0 when internal AGC is active $(V_{AGC} < V_{RML})$     |  |  |  |  |  |

|            | AGC = 1 when internal AGC is not active $(V_{AGC} > V_{RMH})$ |  |  |  |  |  |

| A2, A1, A0 | digital outputs of the 5-level ADC; see Table 17              |  |  |  |  |  |

Table 17. ADC levels

| Voltage applied to pin ADC[1]             | A2 | <b>A</b> 1 | A0 |

|-------------------------------------------|----|------------|----|

| 0.6V <sub>CC</sub> to V <sub>CC</sub>     | 1  | 0          | 0  |

| 0.45V <sub>CC</sub> to 0.6V <sub>CC</sub> | 0  | 1          | 1  |

| 0.3V <sub>CC</sub> to 0.45V <sub>CC</sub> | 0  | 1          | 0  |

| 0.15V <sub>CC</sub> to 0.3V <sub>CC</sub> | 0  | 0          | 1  |

| 0 V to 0.15V <sub>CC</sub>                | 0  | 0          | 0  |

<sup>[1]</sup> Accuracy is  $\pm 0.03 V_{CC}$ . Bit BS5 must be set to logic 0 to disable the BS5 output port. The BS5 output port uses the same pin as the ADC and can not be used when the ADC is in use.

### 8.3 Status at power-on reset

At power on or when the supply voltage drops below approximately 2.85 V (at  $T_{amb}$  = 25 °C), internal registers are set according to Table 18.

At power on, the charge pump current is set to 580  $\mu$ A, the test bits T[2:0] are set to 110 which means that the charge pump is sinking current, the tuning voltage output is disabled and the ALBC function is disabled. The XTOUT buffer is on, driving the 4 MHz signal from the crystal oscillator and all the ports are off. As a consequence, the high band is selected by default.

Table 18. Default setting at power-on reset

| Name                 | Byte | Bit[1]  |                 |         |         |         |         |         |         |

|----------------------|------|---------|-----------------|---------|---------|---------|---------|---------|---------|

|                      |      | MSB     |                 |         |         |         |         |         | LSB     |

| Address byte         | 1    | 1       | 1               | 0       | 0       | 0       | MA1     | MA0     | Χ       |

| Divider byte 1 (DB1) | 2    | 0       | N14 = X         | N13 = X | N12 = X | N11 = X | N10 = X | N9 = X  | N8 = X  |

| Divider byte 2 (DB2) | 3    | N7 = X  | N6 = X          | N5 = X  | N4 = X  | N3 = X  | N2 = X  | N1 = X  | N0 = X  |

| Control byte 1 (CB1) | 4    | 1       | $T/A = X^{[2]}$ | T2 = 1  | T1 = 1  | T0 = 0  | R2 = X  | R1 = X  | R0 = X  |

|                      |      | 1       | $T/A = X^{[3]}$ | 0       | 0       | ATC = 0 | AL2 = 0 | AL1 = 1 | AL0 = 0 |

| Control byte 2 (CB2) | 5    | CP2 = 1 | CP1 = 1         | CP0 = 1 | BS5 = 0 | BS4 = 0 | BS3 = 0 | BS2 = 0 | BS1 = 0 |

<sup>[1]</sup> X means that this bit is not set or reset at power-on reset.

<sup>[2]</sup> The next six bits are written, when bit T/A = 1 in a write sequence.

<sup>[3]</sup> The next six bits are written, when bit T/A = 0 in a write sequence.

## 9. Internal circuitry

Table 19. Internal pin configuration

| Symbol | Pin       |           | Average D selection                            | Average DC voltage versus band selection |                             | Description[1]                             |

|--------|-----------|-----------|------------------------------------------------|------------------------------------------|-----------------------------|--------------------------------------------|

|        | TDA6650TT | TDA6651TT | Low                                            | Mid                                      | High                        |                                            |

| HBIN1  | 1         | 38        | n.a.                                           | n.a                                      | 1.0 V                       |                                            |

| HBIN2  | 2         | 37        | n.a.                                           | n.a                                      | 1.0 V                       | (38) 1 ——————————————————————————————————— |

| MBIN   | 3         | 36        | n.a.                                           | 1.8 V                                    | n.a.                        | (36) 3 fce901                              |

| LBIN   | 4         | 35        | 1.8 V                                          | n.a.                                     | n.a                         | (35) 4 fce898                              |

| RFGND  | 5         | 34        | -                                              | -                                        | -                           | 5 (34)<br>fce897                           |

| IFFIL1 | 6         | 33        | 3.7 V                                          | 3.7 V                                    | 3.7 V                       |                                            |

| IFFIL2 | 7         | 32        | 3.7 V                                          | 3.7 V                                    | 3.7 V                       | (33) 6 7 (32)<br>fce896                    |

| BS4    | 8         | 31        | high-Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | high-Z or $V_{CC} - V_{DS}$              | high-Z or $V_{CC} - V_{DS}$ | 8 (31)<br>fce895                           |

5 V mixer/oscillator and low noise PLL synthesizer

Table 19. Internal pin configuration...continued

| Symbol  | Pin       |           | Average D selection                            | C voltage ve                      | ersus band                      | Description <sup>[1]</sup>                  |  |

|---------|-----------|-----------|------------------------------------------------|-----------------------------------|---------------------------------|---------------------------------------------|--|

|         | TDA6650TT | TDA6651TT | Low                                            | Mid                               | High                            | _                                           |  |

| AGC     | 9         | 30        | 0 V or<br>3.5 V                                | 0 V or<br>3.5 V                   | 0 V or<br>3.5 V                 | 9 (30)<br>fce907                            |  |

| BS3     | 10        | 29        | high-Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | high-Z or $V_{CC} - V_{DS}$       | high-Z or $V_{CC} - V_{DS}$     | 10 (29)<br>fce893                           |  |

| BS2     | 11        | 28        | high-Z                                         | V <sub>CC</sub> - V <sub>DS</sub> | high-Z                          | 11 (28)<br>fce892                           |  |

| BS1     | 12        | 27        | V <sub>CC</sub> – V <sub>DS</sub>              | high-Z                            | high-Z                          | 12 (27)<br>fce891                           |  |

| BVS     | 13        | 26        | 2.5 V                                          | 2.5 V                             | 2.5 V                           | (26) 13 — — — — — — — — — — — — — — — — — — |  |

| ADC/BS5 | 14        | 25        | V <sub>CEsat</sub> or<br>high-Z                | V <sub>CEsat</sub> or<br>high-Z   | V <sub>CEsat</sub> or<br>high-Z | (25) 14 fce887                              |  |

5 V mixer/oscillator and low noise PLL synthesizer

Table 19. Internal pin configuration...continued

| Symbol | Pin       |           | Average D selection | C voltage v | ersus band | Description[1]                              |

|--------|-----------|-----------|---------------------|-------------|------------|---------------------------------------------|

|        | TDA6650TT | TDA6651TT | Low                 | Mid         | High       |                                             |

| SCL    | 15        | 24        | high-Z              | high-Z      | high-Z     | (24) 15 ——————————————————————————————————— |

| SDA    | 16        | 23        | high-Z              | high-Z      | high-Z     | (23) 16 fce888                              |

| AS     | 17        | 22        | 1.25 V              | 1.25 V      | 1.25 V     | (22) 17 fce890                              |

| XTOUT  | 18        | 21        | 3.45 V              | 3.45 V      | 3.45 V     | 18 (21)<br>mce164                           |

| XTAL1  | 19        | 20        | 2.2 V               | 2.2 V       | 2.2 V      |                                             |

| XTAL2  | 20        | 19        | 2.2 V               | 2.2 V       | 2.2 V      | 19 (20) + 20 (19) fce883                    |

| n.c.   | 21        | 18        | n.a.                |             |            | not connected                               |

5 V mixer/oscillator and low noise PLL synthesizer

Table 19.

Internal pin configuration...continued

| Symbol           | Pin       |           | Average D selection | C voltage v     | ersus band      | Description[1]                           |

|------------------|-----------|-----------|---------------------|-----------------|-----------------|------------------------------------------|

|                  | TDA6650TT | TDA6651TT | Low                 | Mid             | High            |                                          |

| VT               | 22        | 17        | V <sub>VT</sub>     | V <sub>VT</sub> | V <sub>VT</sub> | 22 (17)<br>fce884                        |

| CP               | 23        | 16        | 1.8 V               | 1.8 V           | 1.8 V           | 23 (16)<br>fce885                        |

| V <sub>CCD</sub> | 24        | 15        | 5 V                 | 5 V             | 5 V             |                                          |

| PLLGND           | 25        | 14        | -                   | -               | -               | 25 (14)<br>fce882                        |

| V <sub>CCA</sub> | 26        | 13        | 5 V                 | 5 V             | 5 V             |                                          |

| IFOUTB           | 27        | 12        | 2.1 V               | 2.1 V           | 2.1 V           |                                          |

| IFOUTA           | 28        | 11        | 2.1 V               | 2.1 V           | 2.1 V           | 28 (11)<br>fce886                        |

| IFGND            | 29        | 10        | -                   | -               | -               | 29 (10)<br>fce880                        |

| HOSCIN1          | 30        | 9         | 2.2 V               | 2.2 V           | 1.8 V           |                                          |

| HOSCOUT1         | 31        | 8         | 5 V                 | 5 V             | 2.5 V           | -                                        |

| HOSCOUT2         | 32        | 7         | 5 V                 | 5 V             | 2.5 V           |                                          |

| HOSCIN2          | 33        | 6         | 2.2 V               | 2.2 V           | 1.8 V           | (8) 31 32 (7)<br>(6) 33 30 (9)<br>fce879 |

Table 19. Internal pin configuration...continued

| Symbol  | Pin       |           | Average selection | DC voltage<br>า | versus band | Description[1]                                       |

|---------|-----------|-----------|-------------------|-----------------|-------------|------------------------------------------------------|

|         | TDA6650TT | TDA6651TT | Low               | Mid             | High        |                                                      |

| MOSCIN1 | 34        | 5         | 2.3 V             | 1.3 V           | 2.3 V       |                                                      |

| MOSCIN2 | 35        | 4         | 2.3 V             | 1.3 V           | 2.3 V       | 34 (5)<br>35 (4)<br>fce878                           |

| OSCGND  | 36        | 3         | -                 | -               | -           | 36 (3)<br>fce908                                     |

| LOSCOUT | 37        | 2         | 1.7 V             | 1.4 V           | 1.4 V       |                                                      |

| LOSCIN  | 38        | 1         | 2.9 V             | 3.5 V           | 3.5 V       | 37 (2)<br>(1) 38 ——————————————————————————————————— |

[1] The pin numbers in parenthesis refer to the TDA6651TT.

## 10. Limiting values

### Table 20. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Positive currents are entering the IC and negative currents are going out of the IC; all voltages are referenced to ground [1].

| Symbol           | Parameter                            | Conditions            | Min  | Max | Unit |

|------------------|--------------------------------------|-----------------------|------|-----|------|

| $V_{CCA}$        | analog supply voltage                |                       | -0.3 | +6  | V    |

| $V_{CCD}$        | digital supply voltage               |                       | -0.3 | +6  | V    |

| $V_{VT}$         | tuning voltage output                |                       | -0.3 | +35 | V    |

| $V_{SDA}$        | serial data input and output voltage |                       | -0.3 | +6  | V    |

| I <sub>SDA</sub> | serial data output current           | during<br>acknowledge | 0    | 10  | mA   |

| $V_{SCL}$        | serial clock input voltage           |                       | -0.3 | +6  | V    |

| $V_{AS}$         | address selection input voltage      |                       | -0.3 | +6  | V    |

#### Table 20. Limiting values...continued

In accordance with the Absolute Maximum Rating System (IEC 60134). Positive currents are entering the IC and negative currents are going out of the IC; all voltages are referenced to ground [1].

| Symbol               | Parameter                                                                                     | Conditions                                      | Min        | Max                   | Unit |

|----------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|------------|-----------------------|------|

| V <sub>n</sub>       | voltage on all other inputs,<br>outputs and combined<br>inputs and outputs, except<br>grounds | $4.5 \text{ V} < \text{V}_{CC} < 5.5 \text{ V}$ | -0.3       | V <sub>CC</sub> + 0.3 | V    |

| I <sub>BSn</sub>     | PMOS port output current                                                                      | corresponding port on; open-drain               | -20        | 0                     | mA   |

| I <sub>BS(tot)</sub> | sum of all PMOS port output currents                                                          | open-drain                                      | <b>–50</b> | 0                     | mA   |

| t <sub>sc(max)</sub> | maximum short-circuit time                                                                    | each pin to V <sub>CC</sub> or to ground        | -          | 10                    | S    |

| T <sub>stg</sub>     | storage temperature                                                                           |                                                 | -40        | +150                  | °C   |

| T <sub>amb</sub>     | ambient temperature                                                                           |                                                 | [2] –20    | T <sub>amb(max)</sub> | °C   |

| Tj                   | junction temperature                                                                          |                                                 | -          | 150                   | °C   |

<sup>[1]</sup> Maximum ratings cannot be exceeded, not even momentarily without causing irreversible IC damage. Maximum ratings cannot be accumulated.

### 11. Thermal characteristics

Table 21. Thermal characteristics

| Symbol        | Parameter                                   | Conditions  | Тур       | Unit |

|---------------|---------------------------------------------|-------------|-----------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air | [1][2][3] |      |

|               | TDA6650TT                                   |             | 82        | K/W  |

|               | TDA6651TT                                   |             | 74        | K/W  |

<sup>[1]</sup> Measured in free air as defined by JEDEC standard JESD51-2.

- [2] These values are given for information only. The thermal resistance depends strongly on the nature and design of the printed-circuit board used in the application. The thermal resistance given corresponds to the value that can be measured on a multilayer printed-circuit board (4 layers) as defined by JEDEC standard.

- [3] The junction temperature influences strongly the reliability of an IC. The printed-circuit board used in the application contributes in a large part to the overall thermal characteristic. It must therefore be insured that the junction temperature of the IC never exceeds  $T_{i(max)} = 150$  °C at the maximum ambient temperature.

<sup>[2]</sup> The maximum allowed ambient temperature  $T_{amb(max)}$  depends on the assembly conditions of the package and especially on the design of the printed-circuit board. The application mounting must be done in such a way that the maximum junction temperature is never exceeded. An estimation of the junction temperature can be obtained through measurement of the temperature of the top center of the package ( $T_{package}$ ). The temperature difference junction to case ( $\Delta T_{j-c}$ ) is estimated at about 13 °C on the demo board (PCB 827-3). The junction temperature:  $T_j = T_{package} + \Delta T_{j-c}$ .

### 12. Characteristics

### Table 22. Characteristics

| Symbol               | Parameter                                                | Conditions                                                                                                | Min   | Тур  | Max  | Unit |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|------|------|

| Supply               |                                                          |                                                                                                           |       |      |      |      |

| $V_{CC}$             | supply voltage                                           |                                                                                                           | 4.5   | 5.0  | 5.5  | V    |

| I <sub>CC</sub>      | supply current                                           | PMOS ports off                                                                                            | 80    | 96   | 115  | mA   |

|                      |                                                          | one PMOS port on: sourcing 15 mA                                                                          | 96    | 112  | 131  | mA   |

|                      |                                                          | two PMOS ports on: one port sourcing 15 mA and one other port sourcing 5 mA                               | 101   | 117  | 136  | mA   |

| General fu           | ınctions                                                 |                                                                                                           |       |      |      |      |

| $V_{POR}$            | power-on reset supply voltage                            | power-on reset active if $V_{CC} < V_{POR}$                                                               | -     | 2.85 | 3.5  | V    |

| $\Delta f_{lock}$    | frequency range the PLL is able to synthesize            |                                                                                                           | 64    | -    | 1024 | MHz  |

| Crystal os           | cillator[1]                                              |                                                                                                           |       |      |      |      |

| f <sub>xtal</sub>    | crystal frequency                                        |                                                                                                           | -     | 4.0  | -    | MHz  |

| Z <sub>xtal</sub>    | input impedance<br>(absolute value)                      | $f_{xtal}$ = 4 MHz; $V_{CC}$ = 4.5 V to 5.5 V;<br>$T_{amb}$ = -20 °C to + $T_{amb(max)}$ , see Section 10 | 350   | 430  | -    | Ω    |

| P <sub>xtal</sub>    | crystal drive level                                      | $f_{xtal} = 4 \text{ MHz}$                                                                                | [2] _ | 70   | -    | μW   |

| PMOS por             | ts: pins BS1, BS2, BS3, BS                               | S4 and BS5                                                                                                |       |      |      |      |

| $I_{\text{LO(off)}}$ | output leakage current in off state                      | $V_{CC} = 5.5 \text{ V}; V_{BS} = 0 \text{ V}$                                                            | -10   | -    | -    | μΑ   |

| V <sub>DS(sat)</sub> | output saturation voltage                                | only corresponding buffer is on, sourcing 15 mA; $V_{DS(sat)} = V_{CC} - V_{BS}$                          | -     | 0.2  | 0.4  | V    |

| ADC input            | t: pin ADC                                               |                                                                                                           |       |      |      |      |

| Vi                   | ADC input voltage                                        | see Table 17                                                                                              | 0     | -    | 5.5  | V    |

| I <sub>IH</sub>      | HIGH-level input current                                 | $V_{ADC} = V_{CC}$                                                                                        | -     | -    | 10   | μΑ   |

| I <sub>IL</sub>      | LOW-level input current                                  | $V_{ADC} = 0 V$                                                                                           | -10   | -    | -    | μΑ   |

| Address s            | election input: pin AS                                   |                                                                                                           |       |      |      |      |

| I <sub>IH</sub>      | HIGH-level input current                                 | $V_{AS} = 5.5 \text{ V}$                                                                                  | -     | -    | 10   | μΑ   |

| $I_{IL}$             | LOW-level input current                                  | $V_{AS} = 0 V$                                                                                            | -10   | -    | -    | μΑ   |

| Bus voltaç           | ge selection input: pin BVS                              |                                                                                                           |       |      |      |      |

| I <sub>IH</sub>      | HIGH-level input current                                 |                                                                                                           | -     | -    | 100  | μΑ   |

| $I_{IL}$             | LOW-level input current                                  | $V_{BVS} = 0 V$                                                                                           | -100  | -    | -    | μΑ   |

| Buffered o           | output: pin XTOUT                                        |                                                                                                           |       |      |      |      |

| $V_{o(p-p)}$         | square wave AC output<br>voltage (peak-to peak<br>value) |                                                                                                           | [3] - | 400  | -    | mV   |

| Zo                   | output impedance                                         |                                                                                                           | -     | 175  | -    | Ω    |

### Table 22. Characteristics...continued

| Symbol               | Parameter                              | Conditions                                                                                            | Min              | Тур | Max    | Unit |

|----------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|------------------|-----|--------|------|

| I <sup>2</sup> C-bus | 001 100:                               |                                                                                                       |                  |     |        |      |

|                      | s SCL and SDA                          |                                                                                                       |                  |     |        |      |

| f <sub>clk</sub>     | clock frequency                        | frequency on SCL                                                                                      | -                | -   | 400    | kHz  |

| $V_{IL}$             | LOW-level input voltage                | $V_{BVS} = 0 V$                                                                                       | 0                | -   | 0.75   | V    |

|                      |                                        | V <sub>BVS</sub> = 2.5 V or open-circuit                                                              | 0                | -   | 1.0    | V    |

|                      |                                        | $V_{BVS} = 5 V$                                                                                       | 0                | -   | 1.5    | V    |

| $V_{IH}$             | HIGH-level input voltage               | $V_{BVS} = 0 V$                                                                                       | 1.75             | -   | 5.5    | V    |

|                      |                                        | V <sub>BVS</sub> = 2.5 V or open-circuit                                                              | 2.3              | -   | 5.5    | V    |

|                      |                                        | $V_{BVS} = 5 V$                                                                                       | 3.0              | -   | 5.5    | V    |

| I <sub>IH</sub>      | HIGH-level input current               | $V_{CC} = 0 \text{ V}; V_{BUS} = 5.5 \text{ V}$                                                       | -                | -   | 10     | μΑ   |

|                      |                                        | $V_{CC} = 5.5 \text{ V}; V_{BUS} = 5.5 \text{ V}$                                                     | -                | -   | 10     | μΑ   |

| I <sub>IL</sub>      | LOW-level input current                | $V_{CC} = 0 \text{ V}; V_{BUS} = 1.5 \text{ V}$                                                       | -                | -   | 10     | μΑ   |

|                      |                                        | V <sub>CC</sub> = 5.5 V; V <sub>BUS</sub> = 0 V                                                       | -10              | -   | -      | μΑ   |

| Output: pin          | SDA                                    |                                                                                                       |                  |     |        |      |

| I <sub>LH</sub>      | leakage current                        | V <sub>SDA</sub> = 5.5 V                                                                              | -                | -   | 10     | μΑ   |

| V <sub>O(ack)</sub>  | output voltage during acknowledge      | $I_{SDA} = 3 \text{ mA}$                                                                              | -                | -   | 0.4    | V    |

| Charge pu            | ımp output: pin CP                     |                                                                                                       |                  |     |        |      |

| I <sub>o</sub>       | output current (absolute value)        | see <u>Table 12</u>                                                                                   | -                | -   | -      | μΑ   |

| I <sub>L(off)</sub>  | off-state leakage current              | charge pump off (T[2:0] = 010)                                                                        | -15              | 0   | +15    | nΑ   |

| Tuning vo            | Itage output: pin VT                   |                                                                                                       |                  |     |        |      |

| $I_{L(off)}$         | leakage current when switched-off      | tuning supply voltage = 33 V                                                                          | -                | -   | 10     | μΑ   |

| V <sub>o(cl)</sub>   | output voltage when the loop is closed | tuning supply voltage = 33 V; $R_L$ = 15 $k\Omega$                                                    | 0.3              | -   | 32.7   | V    |

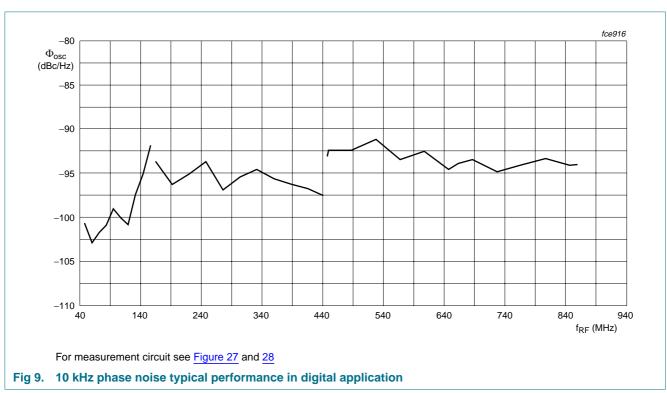

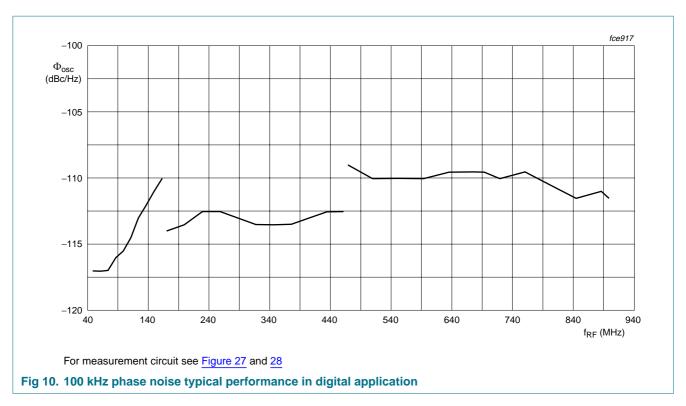

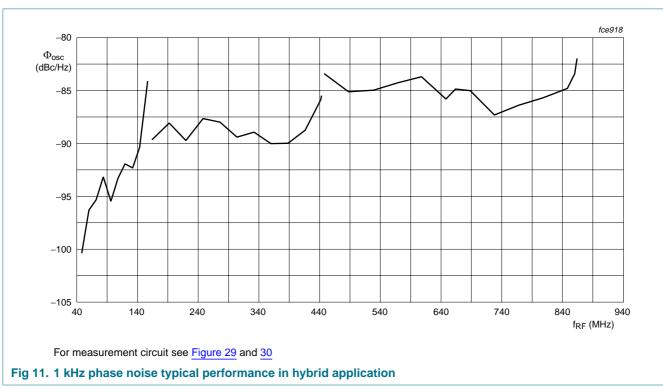

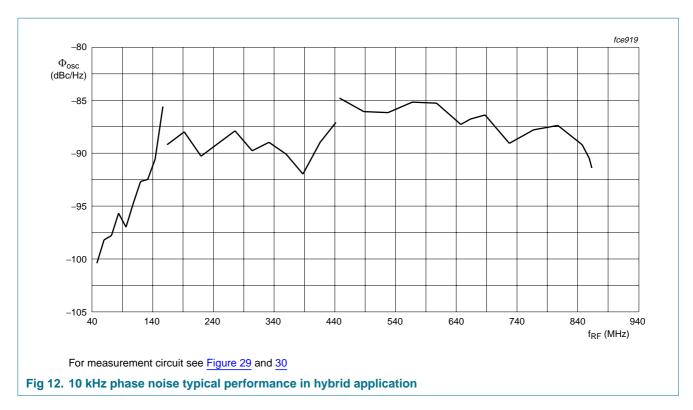

| Noise perf           | formance                               |                                                                                                       |                  |     |        |      |

| $J_{\phi(rms)}$      | phase jitter (RMS value)               | integrated between 1 kHz and 1 MHz offset from the carrier                                            |                  |     |        |      |

|                      |                                        | digital only application:<br>TDA6650TT/C3/S2; TDA6651TT/C3/S2;<br>TDA6651TT/C3/S3                     | -                | 0.5 | -      | deg  |

|                      |                                        | hybrid application: TDA6650TT/C3; TDA6651TT/C3                                                        | -                | 0.6 | -      | deg  |

| Low band             | mixer, including IF amplifi            | er                                                                                                    |                  |     |        |      |

| f <sub>RF</sub>      | RF frequency                           | picture carrier for digital only application:<br>TDA6650TT/C3/S2; TDA6651TT/C3/S2;<br>TDA6651TT/C3/S3 | <u>[4]</u> 47.00 | -   | 160.00 | MHz  |

|                      |                                        | picture carrier for hybrid application:<br>TDA6650TT/C3; TDA6651TT/C3                                 | [4] 43.25        | -   | 157.25 | MHz  |

### Table 22. Characteristics...continued

| Symbol             | Parameter                                                                    | Conditions                                                                                      |            | Min    | Тур  | Max    | Unit                   |

|--------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|--------|------|--------|------------------------|

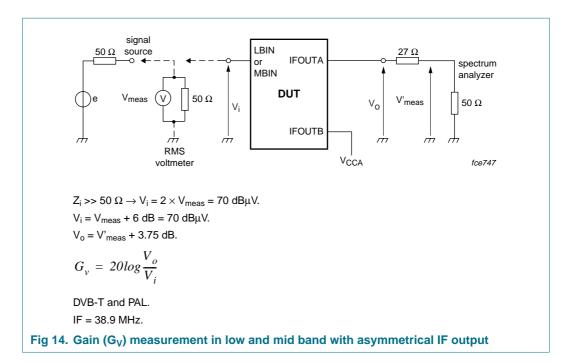

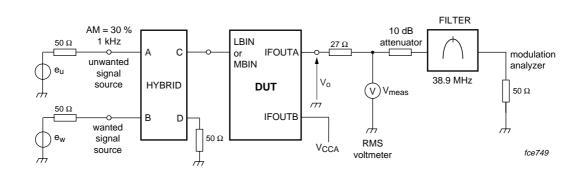

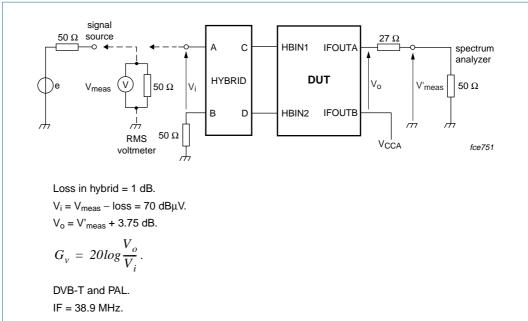

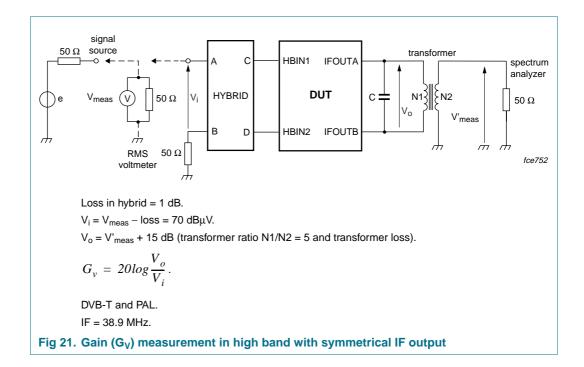

| G <sub>v</sub>     | voltage gain                                                                 | asymmetrical IF output; $R_L = 75 \Omega$ ; see Figure 14                                       |            |        |      |        |                        |

|                    |                                                                              | $f_{RF} = 44.25 \text{ MHz}$                                                                    |            | 21     | 24   | 27     | dB                     |

|                    |                                                                              | f <sub>RF</sub> = 157.25 MHz                                                                    |            | 21     | 24   | 27     | dB                     |

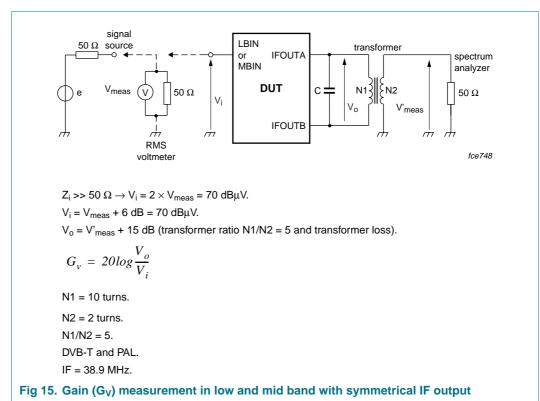

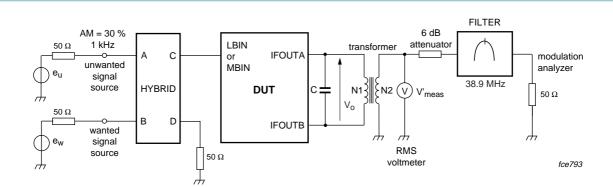

|                    |                                                                              | symmetrical IF output; $R_L = 1.25 \text{ k}\Omega$ ; see Figure 15                             |            |        |      |        |                        |

|                    |                                                                              | f <sub>RF</sub> = 44.25 MHz                                                                     |            | 25     | 28   | 31     | dB                     |

|                    |                                                                              | f <sub>RF</sub> = 157.25 MHz                                                                    |            | 25     | 28   | 31     | dB                     |

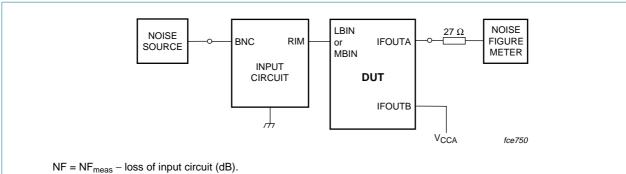

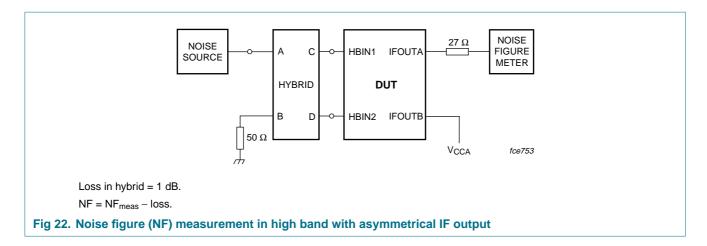

| NF                 | noise figure                                                                 | see Figure 16 and 17                                                                            |            |        |      |        |                        |

|                    |                                                                              | $f_{RF} = 50 \text{ MHz}$                                                                       |            | -      | 8.0  | 10.0   | dB                     |

|                    |                                                                              | $f_{RF} = 150 \text{ MHz}$                                                                      |            | -      | 8.0  | 10.0   | dB                     |

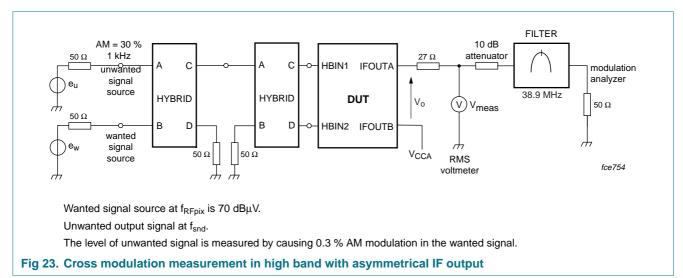

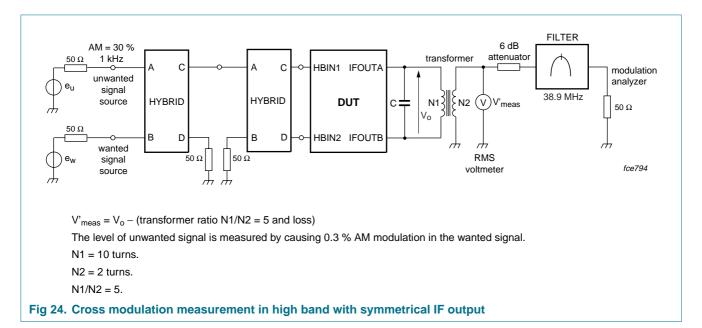

| Vo                 | output voltage causing                                                       | asymmetrical application; see Figure 18                                                         | <u>[5]</u> |        |      |        |                        |

|                    | 1 % cross modulation in<br>channel                                           | f <sub>RF</sub> = 44.25 MHz                                                                     |            | 107    | 110  | -      | $\text{dB}\mu\text{V}$ |

|                    | Channel                                                                      | f <sub>RF</sub> = 157.25 MHz                                                                    |            | 107    | 110  | -      | $\text{dB}\mu\text{V}$ |

|                    |                                                                              | symmetrical application; see Figure 19                                                          | <u>[5]</u> |        |      |        |                        |

|                    |                                                                              | f <sub>RF</sub> = 44.25 MHz                                                                     |            | 117    | 120  | -      | $dB\mu V$              |

|                    |                                                                              | f <sub>RF</sub> = 157.25 MHz                                                                    |            | 117    | 120  | -      | $dB\mu V$              |

| Vi                 | input voltage causing<br>750 Hz frequency<br>deviation pulling in<br>channel | asymmetrical IF output                                                                          |            | -      | 90   | -      | dBμV                   |

| INT <sub>SO2</sub> | channel SO2 beat                                                             | hybrid application: TDA6650TT/C3;<br>TDA6651TT/C3; V <sub>RFpix</sub> = 80 dBμV                 | [6]        | 57     | 60   | -      | dBc                    |

| $V_{i(lock)}$      | input level without lock-out                                                 | see Figure 25                                                                                   | <u>[7]</u> | -      | -    | 120    | dBμV                   |

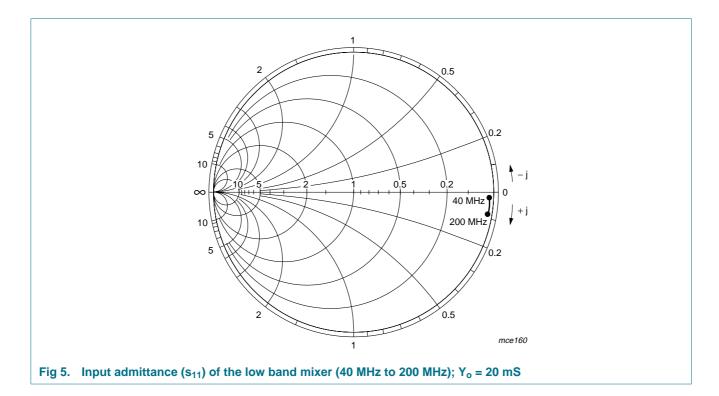

| Gi                 | input conductance                                                            | f <sub>RF</sub> = 44.25 MHz; see <u>Figure 5</u>                                                |            | -      | 0.13 | -      | mS                     |

|                    |                                                                              | f <sub>RF</sub> = 157.25 MHz; see <u>Figure 5</u>                                               |            | -      | 0.11 | -      | mS                     |

| Ci                 | input capacitance                                                            | f <sub>RF</sub> = 44.25 MHz to 157.25 MHz;<br>see <u>Figure 5</u>                               |            | -      | 1.36 | -      | pF                     |

| Mid band           | mixer, including IF amplific                                                 | er                                                                                              |            |        |      |        |                        |

| f <sub>RF</sub>    | RF frequency                                                                 | picture carrier for digital only application: TDA6650TT/C3/S2; TDA6651TT/C3/S2; TDA6651TT/C3/S3 | <u>[4]</u> | 160.00 | -    | 446.00 | MHz                    |

|                    |                                                                              | picture carrier for hybrid application: TDA6650TT/C3; TDA6651TT/C3                              | <u>[4]</u> | 157.25 | -    | 443.25 | MHz                    |

### Table 22. Characteristics...continued

| Symbol                | Parameter                                                                    | Conditions                                                                                            |            | Min    | Тур  | Max    | Unit |

|-----------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------|--------|------|--------|------|

| $G_v$                 | voltage gain                                                                 | asymmetrical IF output; load = 75 $\Omega$ ; see Figure 14                                            |            |        |      |        |      |

|                       |                                                                              | f <sub>RF</sub> = 157.25 MHz                                                                          |            | 21     | 24   | 27     | dB   |

|                       |                                                                              | f <sub>RF</sub> = 443.25 MHz                                                                          |            | 21     | 24   | 27     | dB   |

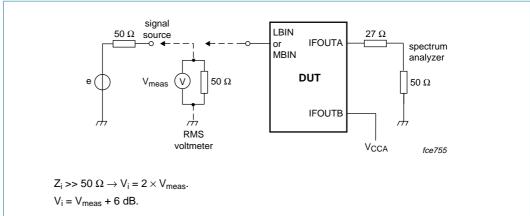

|                       |                                                                              | symmetrical IF output; load = 1.25 k $\Omega$ ; see Figure 15                                         |            |        |      |        |      |