## **Three/Four-cell Lithium-Ion Battery Protection IC**

## FEATURES

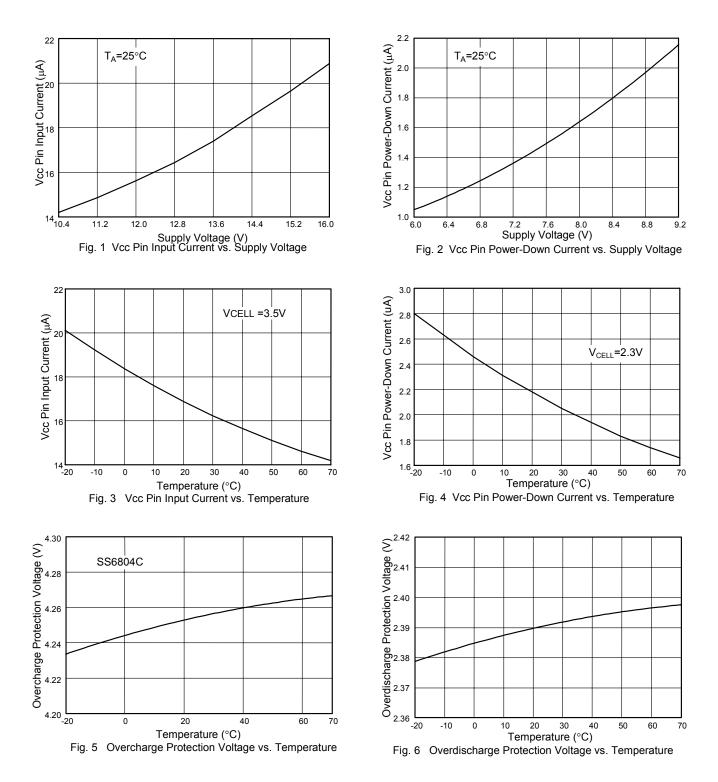

Ultra-low quiescent current,  $17\mu A$  (4-cell, V<sub>cell</sub> = 3.5V). Ultra-low power-down current, 2.2 $\mu A$  (4-cell, V<sub>cell</sub> = 2.3V). Wide supply voltage range: 2V to 18V.

Precision over-charge protection voltage:

4.35V±30mV for the SS6804A 4.30V±30mV for the SS6804B

4.25V±30mV for the SS6804C

4.20V±30mV for the SS6804D

Externally set over-charge, over-discharge and over-current delay time.

Built-in cell-balancing bleeding network under over-charge condition.

Three detection levels for over-current protection.

## **APPLICATIONS**

Protection IC for three/four-cell lithium-ion battery packs.

## DESCRIPTION

The SS6804 is designed to protect a lithium-ion battery from damage or degraded lifetime due to over-charging, over-discharging and over-current for three- or four-cell lithium-ion battery powered systems such as notebook PCs.

It provides the cell-balancing "bleeding" function to automatically discharge the over-charged cell until the over-charge condition is eliminated.

Safe charging with full utilization is ensured by the accurate ±30mV over-charge detection. Four different specification values for over-charge protection voltage are provided for various protection requirements. The very low standby current represents little drain from the cell while in storage.

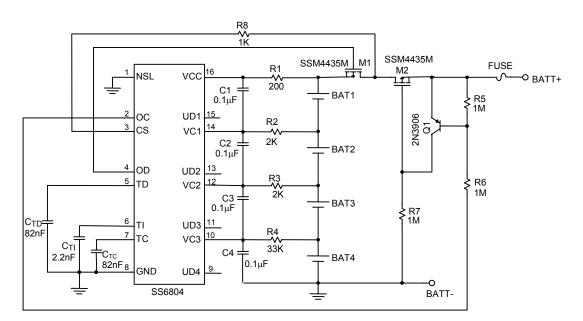

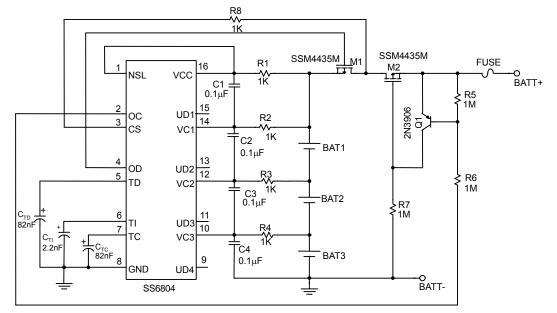

## TYPICAL APPLICATION CIRCUIT

#### Protection Circuit for Four-Cell Lithium-Ion Battery Pack

## ORDERING INFORMATION

## SS6804XCX<u>XX</u>

| Packing type<br>TR: Tape and reel<br>TB: Tube                                     |

|-----------------------------------------------------------------------------------|

| Package type<br>S: SO-16                                                          |

| Over-charge Protection<br>Voltage<br>A: 4.35V<br>B: 4.30V<br>C: 4.25V<br>D: 4.20V |

|       | TOP VIEW | _      |

|-------|----------|--------|

| NSL 1 |          | 16 VCC |

| OC [2 | -        | 15 UD1 |

| CS 3  | -        | 14 VC1 |

| OD 4  | -        | 13 UD2 |

| TD 5  |          | 12 VC2 |

| TI 6  |          | 11 UD3 |

| TC 7  | -        | 10 VC3 |

| GND 8 |          | 9 UD4  |

**PIN CONFIGURATION**

Example: SS6804ACSTR

$\rightarrow$  4.35V version, in SO-16, shipped on tape and reel

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                   | 18V           |

|----------------------------------|---------------|

| DC Voltage Applied on other Pins | 18V           |

| Operating Temperature Range      | 20°C~70°C     |

| Storage Temperature Range        | - 65°C ~125°C |

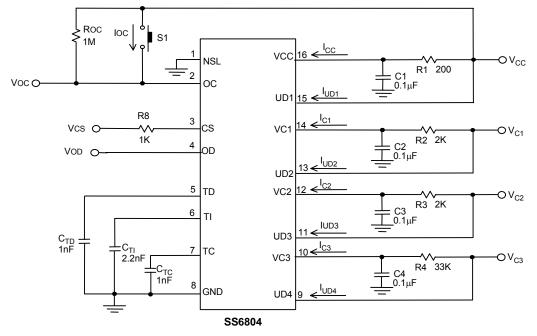

## **TEST CIRCUIT**

# ELECTRICAL CHARACTERISTICS (TA=25°C, unless otherwise specified.)

| PARAMETER                                       | TEST CONDITIONS                                                                                                    | SYMBOL              | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|------|------|------|------|

| VCC Pin Input Current in Normal<br>Mode         | V <sub>CELL</sub> =3.5V                                                                                            | I <sub>CC</sub>     |      | 17   | 26   | μA   |

| VC1 Pin Input Current in Normal Mode            | V <sub>CELL</sub> =3.5V                                                                                            | I <sub>C1</sub>     |      | 0.7  | 1.8  | μA   |

| VC2 Pin Input Current in Normal<br>Mode         | V <sub>CELL</sub> =3.5V                                                                                            | I <sub>C2</sub>     |      | 0.4  | 1.0  | μA   |

| VC3 Pin Input Current in Normal<br>Mode         | V <sub>CELL</sub> =3.5V                                                                                            | I <sub>C3</sub>     |      | 0.2  | 0.5  | μA   |

| Vcc Pin Input Current in Power-<br>Down Mode    | V <sub>CELL</sub> =2.3V                                                                                            | I <sub>CC(PD)</sub> |      | 2.2  | 4.0  | μA   |

| VC1,VC2,VC3 Input Current in<br>Power-Down Mode | V <sub>CELL</sub> =2.3V                                                                                            | I <sub>C(PD)</sub>  |      | 0.01 | 0.15 | μA   |

|                                                 | SS6804A                                                                                                            |                     | 4.32 | 4.35 | 4.38 | - V  |

| Overcharge Protection Voltage                   | SS6804B                                                                                                            | V <sub>OCP</sub>    | 4.27 | 4.30 | 4.33 |      |

| Overcharge Frotection voltage                   | SS6804C                                                                                                            |                     | 4.22 | 4.25 | 4.28 |      |

|                                                 | SS6804D                                                                                                            |                     | 4.17 | 4.20 | 4.23 |      |

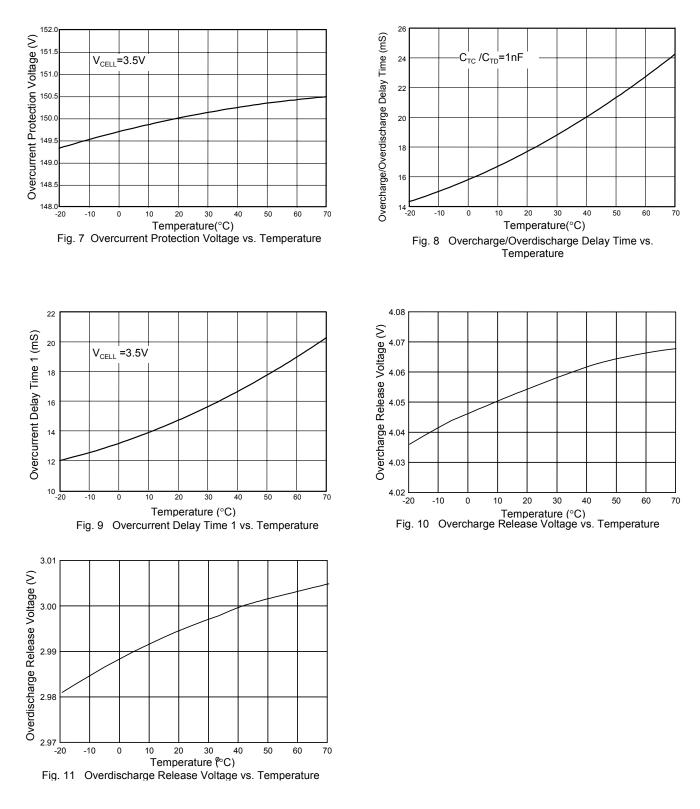

| Overcharge Hysteresis Voltage                   |                                                                                                                    | V <sub>HYS</sub>    | 150  | 200  | 250  | mV   |

| Overdischarge Protection Voltage                |                                                                                                                    | V <sub>ODP</sub>    | 2.27 | 2.40 | 2.53 | V    |

| Overdischarge Release Voltage                   |                                                                                                                    | V <sub>ODR</sub>    | 2.85 | 3.00 | 3.15 | V    |

| Overcurrent Protection Voltage                  | V <sub>CELL</sub> =3.5V                                                                                            | V <sub>OIP</sub>    | 135  | 150  | 165  | mV   |

| Overcharge Delay Time                           | $V_{CELL1}=V_{OCP} - 30mV$<br>$\rightarrow V_{OCP}+30mV$<br>$V_{CELL2}=V_{CELL3}=V_{CELL4}=$<br>$3.5V, C_{TC}=1nF$ | Тос                 | 10   | 21   | 32   | mS   |

| Overdischarge Delay Time                        | $V_{CELL1}$ = 2.5V→ 2.3V<br>$V_{CELL2}$ = $V_{CELL3}$ = $V_{CELL4}$ =<br>3.5V, $C_{TD}$ =1nF                       | T <sub>OD</sub>     | 10   | 21   | 32   | mS   |

| Overcurrent Delay Time (1)                      | V <sub>CELL</sub> = 3.5V,0.15V <v<sub>CC -<br/>V<sub>CS</sub> &lt;0.3V,C<sub>TI</sub>=2.2nF</v<sub>                | T <sub>OI1</sub>    | 7    | 15   | 23   | mS   |

## ELECTRICAL CHARACTERISTICS (Continued)

| PARAMETER                                  | TEST CONDITIONS                                                                                                                        | SYMBOL           | MIN.                                          | TYP.                 | MAX.                  | UNIT |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------|----------------------|-----------------------|------|

| Overcurrent Delay Time (2)                 | V <sub>CELL</sub> =3.5V,<br>0.3V <v<sub>CC-V<sub>CS</sub>&lt;1.0V</v<sub>                                                              | T <sub>OI2</sub> | 2                                             | 4                    | 6                     | mS   |

| Overcurrent Delay Time (3)                 | V <sub>CELL</sub> =3.5V, V <sub>CC</sub> -V <sub>CS</sub> >1.0V                                                                        | T <sub>OI3</sub> | 150                                           | 300                  | 450                   | μS   |

| OC Pin Sink Current                        | V <sub>CELL1</sub> =4.4V,<br>V <sub>CELL2</sub> = V <sub>CELL3</sub> =<br>V <sub>CELL4</sub> =3.5V,<br>OC Pin Short to V <sub>CC</sub> | l <sub>OC</sub>  | 2.2                                           | 3.2                  | 4.2                   | mA   |

| OD Pin Output "H" Voltage                  |                                                                                                                                        | V <sub>DH</sub>  | V <sub>cc</sub> -0.15V V <sub>cc</sub> -0.03V |                      | V                     |      |

| OD Pin Output "L" Voltage                  |                                                                                                                                        | V <sub>DL</sub>  |                                               | 0.01                 | 0.15                  | V    |

| Charge Detection Threshold Voltage         | V <sub>CELL</sub> =2.3V                                                                                                                | V <sub>CH</sub>  |                                               | V <sub>CC</sub> +0.4 | V <sub>CC</sub> +0.55 | V    |

| UD1 Pin Cell-Balancing<br>Bleeding Current | V <sub>CELL1</sub> =4.4V,<br>V <sub>CELL2</sub> = V <sub>CELL3</sub> =<br>V <sub>CELL4</sub> =3.5V                                     | I <sub>UD1</sub> | 6.5                                           | 9.3                  | 12.1                  | mA   |

| UD2 Pin Cell-Balancing<br>Bleeding Current | V <sub>CELL2</sub> =4.4V,<br>V <sub>CELL1</sub> = V <sub>CELL3</sub> =<br>V <sub>CELL4</sub> =3.5V                                     | I <sub>UD2</sub> | 6.3                                           | 9.0                  | 11.7                  | mA   |

| UD3 Pin Cell-Balancing<br>Bleeding Current | V <sub>CELL3</sub> =4.4V,<br>V <sub>CELL1</sub> = V <sub>CELL2</sub> =<br>V <sub>CELL4</sub> =3.5V                                     | I <sub>UD3</sub> | 6.2                                           | 8.8                  | 11.4                  | mA   |

| UD4 Pin Cell-Balancing<br>Bleeding Current | V <sub>CELL4</sub> =4.4V,<br>V <sub>CELL1</sub> = V <sub>CELL2</sub> =<br>V <sub>CELL3</sub> =3.5V                                     | I <sub>UD4</sub> | 6.4                                           | 9.2                  | 12.0                  | mA   |

Note: V<sub>CELL</sub> means the battery cell voltage. Therefore,

$V_{CELL1} = V_{CC} - V_{C1}$  $V_{CELL2} = V_{C1} - V_{C2}$  $V_{CELL3} = V_{C2} - V_{C3}$  $V_{CELL4} = V_{C3}$

## **TYPICAL PERFORMANCE CHARACTERISTICS**

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

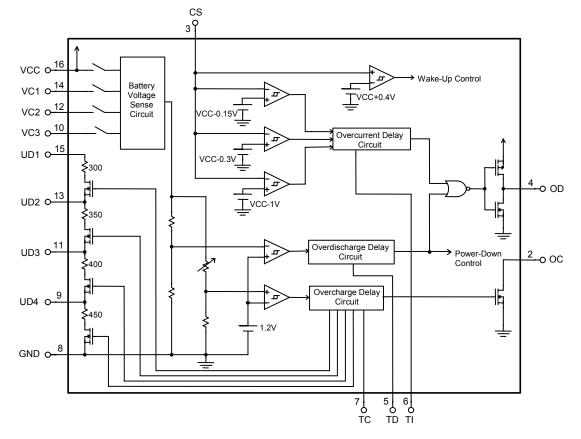

## **BLOCK DIAGRAM**

## PIN DESCRIPTIONS

- PIN 1: NSL- Input pin for cell number selection. Connect this pin to VCC for three-cell application and to GND for four-cell application.

- PIN 2: OC- NMOS open drain output for control of the charge control MOSFET M2. When overcharge occurs, this pin sinks current to switch the external PNP Q1 on, and charging is inhibited by turning off the charge control MOSFET M2.

- PIN 3: CS-Input pin for current sensing. Using the drain-source voltage of the discharge control MOSFET M1 (voltage between VCC and CS), it senses the discharge current during normal mode and detects whether charging current is present during power-down mode.

- PIN 4: OD Output pin for control of discharge control MOSFET M1. When overdischarge occurs, this pin goes high to turn off the discharge control MOSFET M1 and discharging is inhibited.

- PIN 5: TD- Overdischarge delay time setting pin.

- PIN 6: TI Overcurrent delay time setting pin.

- PIN 7: TC Overcharge delay time setting pin.

- PIN 8: GND Ground pin. This pin is to be connected to the negative terminal of the battery cell BAT4.

- PIN 9: UD4-This pin is to be connected to the positive terminal of the battery cell BAT4 for cell-balancing bleeding function under overcharge condition.

- PIN10: VC3- Input pin for battery BAT4 voltage sensing. This pin is to be connected to the positive terminal of the battery cell BAT4.

- PIN11: UD3 This pin is to be connected to the positive terminal of the battery cell BAT3 for cellbalancing bleeding function under overcharge condition.

- PIN12: VC2 Input pin for battery BAT3 voltage sensing. This pin is to be connected to the positive terminal of the battery cell BAT3.

- PIN13: UD2 This pin is to be connected to the positive terminal of the battery cell BAT2 for cell-balancing

bleeding function under overcharge condition.

PIN14: VC1 - Input pin for battery BAT2 voltage sensing. This pin is to be connected to the positive terminal of the battery cell BAT2.

- PIN15: UD1 positive terminal of the battery BAT1 for cell-balancing bleeding function under overcharge condition.

- PIN16: VCC Power supply pin and input for battery BAT1 voltage sensing. This pin is to be connected to the positive terminal of the battery cell BAT1.

## **APPLICATION INFORMATION**

#### THE OPERATION

#### Initialization

On initial power-up, such as connecting the battery pack for the first time to the SS6804, the SS6804 enters the power-down mode. A charger must be applied to the SS6804 circuit to enable the pack.

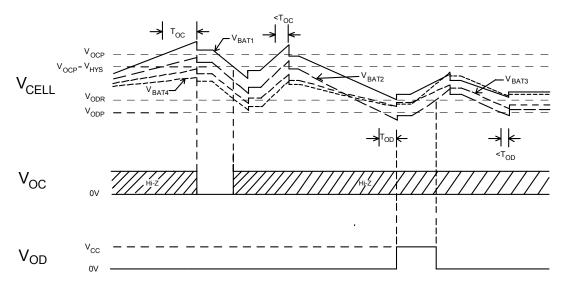

#### **Overcharge Protection**

When the voltage of either of the battery cells exceeds the overcharge protection voltage  $(V_{OCP})$  beyond the overcharge delay time  $(T_{OC})$ period, charging is inhibited by the turning-off of the charge control MOSFET M2. The overcharge delay time is set by the external capacitor C<sub>TC</sub>. Inhibition of charging is immediately released when the voltage of the overcharged cell becomes lower than overcharge release voltage (V<sub>OCR</sub> or V<sub>OCP</sub>-V<sub>HYS</sub>) through discharging.

#### **Overdischarge Protection**

When the voltage of either of the battery cells falls below the overdischarge protection voltage ( $V_{ODP}$ ) beyond the overdischarge delay time ( $T_{OD}$ ) period, discharging is inhibited by the

turning-off of the discharge control MOSFET M1. The overdischarge delay time is set by the external capacitor  $C_{TD}$ . Inhibition of discharging is immediately released when the voltage of the overdischarge cell becomes higher than the overdischarge release voltage (V<sub>ODR</sub>) through charging.

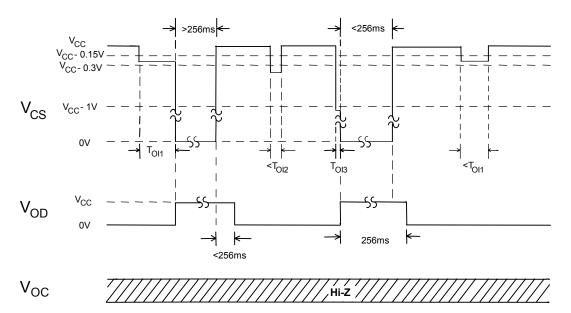

#### **Overcurrent Protection**

In normal mode, the SS6804 continuously monitors the discharge current by sensing the voltage of CS pin. If the voltage V<sub>CC</sub>-V<sub>CS</sub> exceeds the overcurrent protection voltage ( $V_{OIP}$ ) beyond the overcurrent delay time  $(T_{OI})$  period, the overcurrent protection circuit operates and discharging is inhibited by the turning-off of the discharge control MOSFET M1. Discharging must be inhibited for at least 256ms after overcurrent takes place to avoid damage to external control MOSFETs due to rapidly switching transient between BATT+ and BATTterminals. The overcurrent condition returns to normal mode when the load is released and the impedance between the BATT+ and BATTterminals is  $20M\Omega$  or higher.

The SS6804 is provided with the three

overcurrent detection levels (0.15V, 0.3V and 1.0V) and the three overcurrent delay time ( $_{TO|1}$ ,  $T_{O|2}$  and  $T_{O|3}$ ) corresponding to each overcurrent detection level.  $T_{O|1}$  is set by the external capacitor  $C_{TI}$ .  $T_{O|2}$  and  $T_{O|3}$  default to 4ms and 300 $\mu$ s respectively, and can not be adjusted due to protection of external MOSFETs

#### Cell-Balancing Bleeding after Overcharge

When either of the battery cells is overcharged, the SS6804 provides the cell-balancing bleeding function to discharge the overcharged cell at about 9mA until the voltage of the overcharged cell decreases to overcharge release voltage (Vocr or VOCP-VHYS). Connecting UD1, UD2, UD3 and UD4 pins to the positive terminals of battery cells BAT1, BAT2, BAT3 and BAT4 accomplish this function, respectively. Inserting resistors along UD2 pin to BAT2 positive terminal path and UD4 pin to BAT4 positive terminal path can decrease the bleeding current.

#### Power-Down after Overdischarge

When overdischarge occurs, the SS6804 will go into power-down mode, turning off all the timing generation and detection circuitry to reduce the quiescent current to about  $2.2\mu$ A (V<sub>CC</sub>=9.2V). In the unusual case where one battery cell is overdischarged while another one under overcharge condition, the SS6804 will turn off all the detection circuitry except the overcharge detection circuit for the cell under overcharge condition.

#### Charge Detection after Overdischarge

When overdischarge occurs, the discharge control MOSFET M1 turns off and discharging is inhibited. However, charging is still permitted through the parasitic diode of M1. Once the

charger is connected to the battery pack, the SS6804 immediately turns on all the timing generation and detection circuitry and goes into normal mode. Charging is determined to be in progress if the CS pin voltage is higher than VCC + 0.4V (charge detection threshold voltage V<sub>CH</sub>).

#### **DESIGN GUIDE**

#### **Cell Number Selection**

The user must configure the SS6804 for three or four series cells application. For three-cell application, NSL pin should be connected directly to VCC pin. For four-cell application, NSL pin should be connected directly to GND pin.

| No. of Series Cells | NSL Pin          |

|---------------------|------------------|

| 3-cell              | Connected to VCC |

| 4-cell              | Connected to GND |

The protection circuit for three-cell lithium-ion battery pack is shown in application examples Fig. 1.

# Setting the Overcharge and Overdischarge Delay Time

The overcharge delay time is set by the external capacitor  $C_{TC}$  and the overdischarge delay time is set by the external capacitor  $C_{TD}$ . The relationship between capacitance of the external capacitors and delay time is tabulated as below.

| C <sub>TC</sub> ,C <sub>TD</sub> (nF) | T <sub>OC</sub> ,T <sub>OD</sub> (ms) |

|---------------------------------------|---------------------------------------|

|                                       | 100,100(113)                          |

| 1                                     | 21                                    |

| 5                                     | 52                                    |

| 10                                    | 132                                   |

| 22                                    | 253                                   |

| 33                                    | 347                                   |

| 47                                    | 617                                   |

| 68                                    | 748                                   |

| 82                                    | 1004                                  |

| 100                                   | 1630                                  |

The delay time can also be approximately calculated by the following equations (if  $C_{TC}$ ,  $C_{TD} \le 82nF$ ): T<sub>OC</sub>(mS) = 11.8 x C<sub>TC</sub>(nF)

$T_{OD}(mS) = 11.8 \times C_{TD}(nF)$

#### Setting the Overcurrent Delay Time 1

The overcurrent delay time 1 ( $T_{OI1}$ ) at 0.15V < V<sub>CC</sub>-V<sub>CS</sub> < 0.3V is set by the external capacitor C<sub>TI</sub>, while the overcurrent delay time 2 and 3 ( $T_{OI2}$  and  $T_{OI3}$ ) is fixed by IC internal circuit.The relationship between capacitance of the external capacitor and delay time is tabulated as below.

| C <sub>TI</sub> (nF) | T <sub>OI</sub> (ms) |

|----------------------|----------------------|

| 1                    | 4.8                  |

| 2.2                  | 15.0                 |

| 3.3                  | 18.8                 |

| 5                    | 23.6                 |

| 6.8                  | 31.0                 |

| 10                   | 61.8                 |

# Selection of External Control MOSFETs

Because the overcurrent protection voltage is preset, the threshold current for overcurrent detection is determined by the turn-on resistance of the discharge control MOSFET M1. The turn-on resistance of the external control MOSFETs can be determined by the equation:  $R_{ON}=V_{OIP}/I_T$  ( $I_T$  is the overcurrent threshold current). For example, if the overcurrent threshold current  $I_T$  is designed to be 5A, the turn-on resistance of the external control MOSFETs must be  $30m\Omega$ . Users should be aware that turn-on resistance of the MOSFET changes with temperature variation due to heat dissipation. It changes with the voltage between gate and source as well. (Turn-on resistance of a MOSFET increases as the voltage between gate and source decreases). Once the turn-on resistance of the external MOSFET changes, the overcurrent threshold current will change accordingly.

# Suppressing the Ripple and Disturbance from Charger

To suppress the ripple and disturbance from charger, connecting R1 to R4 and C1 to C4 is recommended. Larger R1 will cause larger error of battery sense voltage.

# Controlling the Charge Control MOSFET

R5, R6, R7 and NPN transistor Q1 are used to switch the charge control MOSFET M2. If overcharge does not occur, no current flows into OC pin and Q1 is turned off, then M2 is turned on. When overcharge occurs, current flows into OC pin and Q1 is turned on, which turns off M2 in turn.

#### **Protection at CS Pin**

R8 is used for protection of IC when charger is connected in reverse. The charge detection function after overdischarge is possibly disabled by larger value of R8. Resistance of  $1K\Omega$  is recommended.

## **APPLICATION EXAMPLE**

Fig. 12 Protection Circuit for Three-Cell Lithium-Ion Battery Pack

### TIMING DIAGRAM

• Overcharge and Overdischarge Protection (V<sub>cs</sub>=V<sub>cc</sub>)

#### **Overcurrent Protection (V<sub>CELL</sub>=3.5V)**

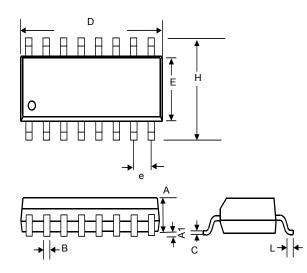

### PHYSICAL DIMENSIONS

#### 16 LEAD PLASTIC SO (150 mil) (unit: mm)

| SYMBOL | MIN        | MAX   |  |  |

|--------|------------|-------|--|--|

| А      | 1.35       | 1.75  |  |  |

| A1     | 0.10       | 0.25  |  |  |

| В      | 0.33       | 0.51  |  |  |

| С      | 0.19       | 0.25  |  |  |

| D      | 9.80       | 10.00 |  |  |

| E      | 3.80       | 4.00  |  |  |

| е      | 1.27 (TYP) |       |  |  |

| Н      | 5.80       | 6.20  |  |  |

| L      | 0.40       | 1.27  |  |  |

Information furnished by Silicon Standard Corporation is believed to be accurate and reliable. However, Silicon Standard Corporation makes no guarantee or warranty, express or implied, as to the reliability, accuracy, timeliness or completeness of such information and assumes no responsibility for its use, or for infringement of any patent or other intellectual property rights of third parties that may result from its use. Silicon Standard reserves the right to make changes as it deems necessary to any products described herein for any reason, including without limitation enhancement in reliability, functionality or design. No license is granted, whether expressly or by implication, in relation to the use of any products described herein or to the use of any information provided herein, under any patent or other intellectual property rights of Silicon Standard Corporation or any third parties.