# AUDIO PROCESSOR LSI WITH SD CARD INTERFACE FOR MOBILE PHONES

## DESCRIPTION

NEC

The  $\mu$ PD99911 is an audio processor LSI with CPU and SD memory card interface. This LSI can perform the functions of an SD audio player without host interactions during playback, which helps the system to achieve low power consumption. This LSI also performs audio streaming playback. It supports not only MP3 but also AAC decoding.

## **FEATURES**

High performance on-chip digital signal processor for the following functions.

Decoder: MP3, WMA, AAC, HE-AAC, Enhanced aacPlus

- AGC (Automatic Gain Controller)

- SRC (Sampling Rate Converter)

- 5-band PEQ (Parametric Equalizer)

- SD memory card interface with CPRM function

- 2 sets of audio serial I/O interface (16 bits stereo) provided. The serial data input frequency is variable from 32 fs to 128 fs in the slave mode. I2S is supported.

- 16-bit parallel host interface

- 8 general-purpose on-chip output ports •

- Programmable PLL on-chip for 32.768 kHz input clock, such as an RTC clock.

- Power management system on-chip

- Operation mode

- Sleep mode (resume data of memory and register)

- Transparency mode (direct connection between ASIO1 and ASIO2)

- Deep sleep mode

- Power supply voltages:

| 1.7 to 2.0 V   |

|----------------|

| 1.16 to 1.24 V |

| 1.16 to 1.24 V |

| 1.7 to 3.0 V   |

|                |

## ORDERING INFORMATION

Part number Package μPD99911F1-BAC-A 97-pin plastic FBGA (6 × 6)

Remark A lead-free product.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

<R>

© NEC Electronics Corporation 2006 The mark <R> shows major revised points.

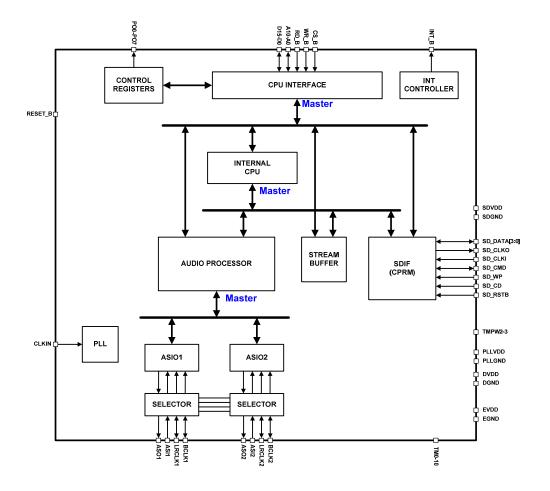

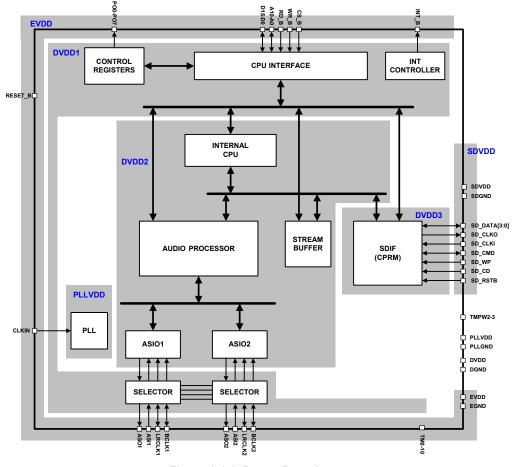

# **BLOCK DIAGRAM AND FUNCTIONS**

### (1) Audio processor

The LSI contains a high-performance digital signal processor for decoding and encoding audio. For operation, firmware needs to be downloaded in advance from external memory via a host CPU. The firmware provides the following different configurable functions:

- Audio decoder

MP3, WMA, AAC, HE-AAC, Enhanced aacPlus

- Sampling rate converter (SRC)

- Volume controller (including soft volume function)

- Automatic gain controller (AGC)

- 5-band parametric equalizer

- Channel controller

- Stereo/mono

(2) PLL

Clock input of 32.768 kHz is supported. When a clock with a frequency in this range is input, it is multiplied by the PLL to generate the fixed frequency clock that is required internally. After activation, normal operation begins after at least 2 ms have elapsed.

## (3) General-purpose output (PO0 to PO7)

The PO0 to PO7 ports can be controlled by the command register.

## (4) Host interface

16-bit parallel interface is supported for the host interface.

## (5) Audio serial interface (ASIO1 and ASIO2)

These are two I/O interface lines for external audio serial data communication. The serial data input frequency is variable. The frequency can be selected in 2-bit steps within a range from 32 to 128 bits. The I2S format is available.

It is possible to make a direct connection of ASIO1 and ASIO2 internally (transparency mode). Very low power consumption can be achieved during the transparency mode.

## (6) SD memory card interface

An SD memory card can be directly connected to the LSI.

## (7) Power management system

Power management system is included internally, which provides suitable operation modes for low power consumption.

# CONTENTS

| 1. PIN FUNCTIONS                                                                            | 6  |

|---------------------------------------------------------------------------------------------|----|

| 1.1 Pin Configuration                                                                       | 6  |

| 1.2 Pin Configuration                                                                       | 7  |

| 1.3 Pin Functions                                                                           | 8  |

| 1.4 Connection of Unused Pins                                                               | 11 |

| 1.5 Initial State of Pins                                                                   | 11 |

| 1.6 Pin Protection                                                                          | 12 |

| 1.7 Pin Outline Schematics                                                                  | 12 |

| 2. INTERNAL POWER AND CLOCK DOMAINS                                                         | 14 |

| 2.1 Power Domains                                                                           | 14 |

| 2.1.1 Hardware reset                                                                        | 15 |

| 2.1.2 Power/reset control of DVDD2 and DVDD3 domains                                        | 16 |

| 2.2 Clock Domains                                                                           | 17 |

| 2.2.1 CLKIN                                                                                 | 17 |

| 2.2.2 PLL                                                                                   | 17 |

| 2.2.3 Divider and domains                                                                   | 17 |

| 2.2.4 Standby                                                                               | 17 |

| 3. HOST CPU INTERFACE                                                                       | 18 |

|                                                                                             |    |

| 4. AUDIO SERIAL INTERFACE                                                                   | 19 |

| 4.1 Format                                                                                  | 19 |

| 4.2 Synchronous Operation                                                                   |    |

| 4.3 Transparency Mode                                                                       | 21 |

| 5. REGISTERS                                                                                |    |

| 5.1 Register Maps                                                                           |    |

| 5.1.1 Register map for chip control                                                         |    |

| 5.1.2 Register map for DSP control                                                          |    |

| 5.1.3 Register map for CPU control                                                          |    |

| 5.1.4 Register map for SD interface control                                                 |    |

| 5.2 Chip Control Registers                                                                  |    |

| 5.2.1 Power domain control register: PWSW (Address: 000H)                                   | 24 |

| 5.2.2 Async RESET for power domains register: RSTB (Address: 002H)                          | 24 |

| 5.2.3 Standby setting register: STNBY (Address: 004H)                                       | 25 |

| 5.2.4 Master clock setting register: MCLK (Address: 006H)                                   | 26 |

| 5.2.5 ASIO control register: ASIOCNT (Address: 00AH)                                        | 27 |

| 5.2.6 General-purpose output port setting register: POUT (Address: 020H)                    | 29 |

| 5.2.7 Interrupt source register: INTSRC (Address: 030H)                                     | 29 |

| 5.2.8 Timer interrupt clear register: ITIM (Address: 032H)                                  | 29 |

| 5.2.9 Interrupt mask register: INTM (Address: 034H)                                         | 29 |

| 5.2.10 PLL activation enable flag register: ENFLG (Address: 040H)                           | 30 |

| 5.2.11 Continuous data access control registers: CSTA (Address: 042H), CCLR (Address: 044H) | 30 |

| 5.3 DSP Registers                                                                           | 31 |

| 5.4 CPU Registers                                                                           | 31 |

| 5.5 SD Registers                                                                            | 31 |

| 6. POWER MANAGEMENT                                                                                                                                                                                                                                                                                                                                 | 32                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 6.1 Acceptable Power Supply Combinations                                                                                                                                                                                                                                                                                                            | 32                                                                                           |

| 6.2 Standby Modes                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| 6.2.1 Sleep mode                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| 6.2.2 Transparency mode                                                                                                                                                                                                                                                                                                                             |                                                                                              |

| 6.2.3 Deep sleep mode                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| 7. POWER STARTUP PROCEDURE                                                                                                                                                                                                                                                                                                                          | 34                                                                                           |

| 7.1 Wakeup Sequence                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 7.1.1 Basic sequence                                                                                                                                                                                                                                                                                                                                | 34                                                                                           |

| 7.1.2 Wakeup sequence of DVDD2                                                                                                                                                                                                                                                                                                                      | 35                                                                                           |

| 7.1.3 Wakeup sequence of DVDD3 and SDVDD                                                                                                                                                                                                                                                                                                            |                                                                                              |

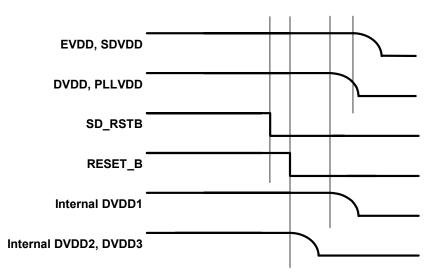

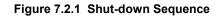

| 7.2 Shut-down Sequence                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 7.3 Power Control During Operation                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 7.3.1 DVDD2 control                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

| 7.3.2 DVDD3 and SDVDD control                                                                                                                                                                                                                                                                                                                       |                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| 8. ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 8. ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 8.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                        | 40                                                                                           |

| 8.1 Absolute Maximum Ratings<br>8.2 Recommended Operating Conditions                                                                                                                                                                                                                                                                                | 40<br>40                                                                                     |

| 8.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                        | 40<br>40<br>40                                                                               |

| 8.1 Absolute Maximum Ratings<br>8.2 Recommended Operating Conditions<br>8.3 Capacitance                                                                                                                                                                                                                                                             |                                                                                              |

| <ul> <li>8.1 Absolute Maximum Ratings</li> <li>8.2 Recommended Operating Conditions</li> <li>8.3 Capacitance</li> <li>8.4 DC Characteristics</li> </ul>                                                                                                                                                                                             | 40<br>40<br>40<br>41<br>42                                                                   |

| <ul> <li>8.1 Absolute Maximum Ratings</li></ul>                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>41<br>42<br>42                                                             |

| <ul> <li>8.1 Absolute Maximum Ratings</li> <li>8.2 Recommended Operating Conditions</li></ul>                                                                                                                                                                                                                                                       | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>42                                                 |

| <ul> <li>8.1 Absolute Maximum Ratings</li></ul>                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>42<br>42                                           |

| <ul> <li>8.1 Absolute Maximum Ratings</li></ul>                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>42<br>42<br>42                                     |

| <ul> <li>8.1 Absolute Maximum Ratings.</li> <li>8.2 Recommended Operating Conditions</li> <li>8.3 Capacitance</li> <li>8.4 DC Characteristics.</li> <li>8.5 AC Characteristics.</li> <li>8.5.1 Clock</li> <li>8.5.2 Reset (RESET_B and SD_RSTB).</li> <li>8.5.3 Wakeup wait time of internal power supply.</li> <li>8.5.4 Host interface</li> </ul> | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>42<br>42<br>42<br>42<br>42<br>42<br>43<br>43       |

| <ul> <li>8.1 Absolute Maximum Ratings</li></ul>                                                                                                                                                                                                                                                                                                     | 40<br>40<br>40<br>41<br>42<br>42<br>42<br>42<br>42<br>42<br>42<br>42<br>42<br>43<br>43<br>45 |

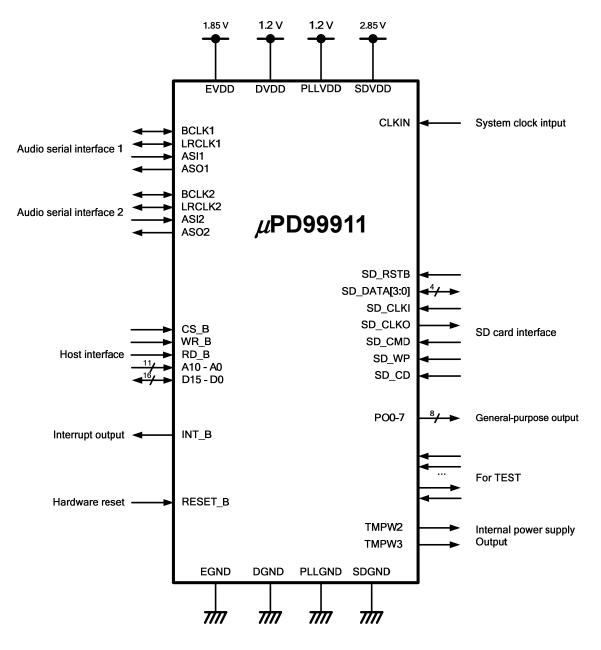

## 1. PIN FUNCTIONS

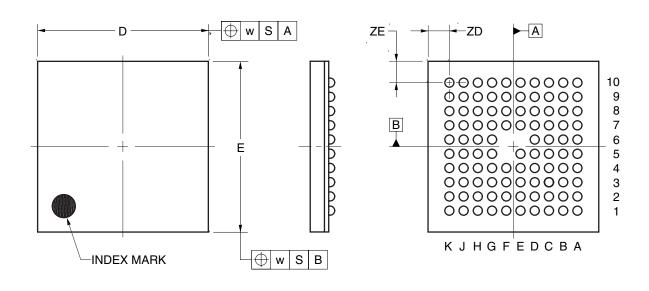

## 1.1 Pin Configuration

# 1.2 Pin Configuration

<R>

97-pin plastic FBGA (6 x 6) μ PD99911F1-BAC-A

| (Bottom View)                                    | _               |

|--------------------------------------------------|-----------------|

| 000000000<br>0000000000<br>0000000000<br>0000000 | 10<br>987654321 |

| Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|

| A1      | N.C.     | D4      | SD_CLKI  | K7      | EVDD     |

| B1      | EVDD     | E4      | SDGND    | A8      | EVDD     |

| C1      | BCLK1    | F4      | SD_DATA2 | B8      | EGND     |

| D1      | DGND     | G4      | DVDD     | C8      | TM5      |

| E1      | SDVDD    | H4      | EGND     | D8      | D11      |

| F1      | SD_DATA0 | J4      | PO2      | E8      | D14      |

| G1      | SD_WP    | K4      | PO3      | F8      | A9       |

| H1      | PLLVDD   | A5      | D0       | G8      | A8       |

| J1      | PLLGND   | B5      | ASI2     | H8      | A1       |

| K1      | N.C.     | C5      | D1       | J8      | A3       |

| A2      | TM10     | D5      | DGND     | K8      | A2       |

| B2      | EGND     | E5      | DVDD     | A9      | TM7      |

| C2      | LRCLK2   | G5      | DVDD     | B9      | TM8      |

| D2      | ASI1     | H5      | PO4      | C9      | D8       |

| E2      | TMPW3    | J5      | PO5      | D9      | D9       |

| F2      | SD_DATA1 | K5      | PO6      | E9      | D13      |

| G2      | SD_CMD   | A6      | BCLK2    | F9      | A10      |

| H2      | SD_CD    | B6      | D2       | G9      | A6       |

| J2      | TM4      | C6      | D3       | H9      | A5       |

| K2      | TM3      | D6      | DVDD     | J9      | TM2      |

| A3      | WR_B     | G6      | DGND     | K9      | TM1      |

| B3      | TM6      | H6      | PO7      | A10     | N.C.     |

| C3      | ASO1     | J6      | EGND     | B10     | TM9      |

| D3      | LRCLK1   | K6      | INT_B    | C10     | D7       |

| E3      | SD_RSTB  | A7      | D5       | D10     | D10      |

| F3      | SD_CLKO  | B7      | D4       | E10     | DGND     |

| G3      | SD_DATA3 | C7      | D6       | F10     | DVDD     |

| H3      | CLKIN    | D7      | D12      | G10     | A7       |

| J3      | PO0      | E7      | D15      | H10     | A4       |

| K3      | PO1      | F7      | TMPW2    | J10     | TM0      |

| A4      | RD_B     | G7      | A0       | K10     | N.C.     |

| B4      | ASO2     | H7      | EGND     |         |          |

| C4      | CS_B     | J7      | RESET_B  |         |          |

Caution: Leave the N.C. pins open.

# 1.3 Pin Functions

# (1) Power supply pins

| Pin Name | I/O | Function                                                                |

|----------|-----|-------------------------------------------------------------------------|

| DVDD     | _   | Power supply for digital core block                                     |

|          |     | Be sure to connect a 0.1 $\mu$ F capacitor between this pin and DGND.   |

| DGND     | _   | Ground for digital core block                                           |

| EVDD     | _   | Power supply for I/O                                                    |

|          |     | Be sure to connect a 0.1 $\mu$ F capacitor between this pin and EGND.   |

| EGND     | _   | Ground for I/O                                                          |

| PLLVDD   | _   | Power supply for PLL                                                    |

|          |     | Be sure to connect a 0.1 $\mu$ F capacitor between this pin and PLLGND. |

| PLLGND   | _   | Ground for PLL block                                                    |

| SDVDD    | _   | Power supply for SD I/O                                                 |

|          |     | Be sure to connect a 0.1 $\mu$ F capacitor between this pin and SDGND.  |

| SDGND    | _   | Ground for SD I/O block                                                 |

# (2) Clock and system control pins

| Pin Name | I/O   | Function                                                                                                             |

|----------|-------|----------------------------------------------------------------------------------------------------------------------|

| CLKIN    | Input | Clock input<br>This is the reference clock input that is used to generate the internal master<br>clock.              |

| RESET_B  | Input | Hardware reset input signal<br>This resets the LSI. Registers are initialized to their initial values after a reset. |

# (3) Host interface pins

| Pin Name  | I/O    | Function                                                                                                                                                                             |

|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 to A10 | Input  | Host interface address signal input                                                                                                                                                  |

| D0 to D15 | I/O    | Host data bus (D15 to D0).<br>Data I/O is performed when the host CPU accesses this LSI.<br>This bus is set to high impedance when the CS_B signal is inactive (high).               |

| CS_B      | Input  | Chip select strobe input<br>This is the input pin for the host interface select signal. This pin must be<br>active (low) while the host CPU accesses a host interface register.      |

| WR_B      | Input  | Host write strobe input<br>This pin must be active (low) while the host CPU writes to a host interface<br>register. Do not set this pin and the RD_B pin as active at the same time. |

| RD_B      | Input  | Host read strobe input<br>This pin must be active (low) while the host CPU reads a host interface<br>register. Do not set this pin and the WR_B pin as active at the same time.      |

| INT_B     | Output | Interrupt request (Level trigger)<br>This is used to request data transfer or to notify the internal status.                                                                         |

# (4) Audio serial interface 1 (option)

| Pin Name | I/O    | Function                                                                                       |  |  |

|----------|--------|------------------------------------------------------------------------------------------------|--|--|

| BCLK1    | I/O    | Bit synchronization clock I/O for audio serial interface                                       |  |  |

|          |        | This pin is used to input or output a bit synchronization clock for an audio serial interface. |  |  |

|          |        | Leave this pin open when not used.                                                             |  |  |

| LRCLK1   | I/O    | Audio serial frame synchronization clock I/O                                                   |  |  |

|          |        | This pin is used to input or output a frame sync signal for serial transfers.                  |  |  |

|          |        | Leave this pin open when not used.                                                             |  |  |

| ASO1     | Output | Audio serial data output                                                                       |  |  |

|          |        | Leave this pin open when not used.                                                             |  |  |

| ASI1     | Input  | Audio serial data input                                                                        |  |  |

|          |        | Connect this pin to GND when not used.                                                         |  |  |

# (5) Audio serial interface 2 (for DAC)

| Pin Name | I/O    | Function                                                                                                                                                      |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BCLK2    | I/O    | Bit synchronization clock I/O for audio serial interface<br>This pin is used to input or output a bit synchronization clock for an audio<br>serial interface. |

| LRCLK2   | I/O    | Audio serial frame synchronization clock I/O<br>This pin is used to input or output a frame sync signal for serial transfers.                                 |

| ASO2     | Output | Audio serial data output                                                                                                                                      |

| ASI2     | Input  | Audio serial data input                                                                                                                                       |

## (6) Internal power supply output pins

| Pin Name | I/O | Function                                                              |

|----------|-----|-----------------------------------------------------------------------|

| TMPW2    | -   | Internal DVDD2 output                                                 |

|          |     | Be sure to connect a 0.1 $\mu$ F capacitor between this pin and DGND. |

| TMPW3    | -   | Internal DVDD3 output                                                 |

|          |     | Be sure to connect a 0.1 $\mu$ F capacitor between this pin and DGND. |

# (7) SD card interface pins

| Pin Name      | I/O    | Function                                    |

|---------------|--------|---------------------------------------------|

| SD_RSTB       | Input  | Reset for SD card interface                 |

| SD_CLKI       | Input  | Clock input. Connect to SD_CLKO externally. |

| SD_CLKO       | Output | Clock output                                |

| SD_DATA0 to 3 | I/O    | Bi-directional SD data bus                  |

| SD_WP         | Input  | SD write protection                         |

| SD_CMD        | I/O    | SD command input                            |

| SD_CD         | Input  | SD card detection input                     |

## (8) General-purpose output pins

| Pin Name   | I/O    | Function                                                                |

|------------|--------|-------------------------------------------------------------------------|

| PO0 to PO7 | Output | General-purpose external output pins                                    |

|            |        | These pins can be used to output control signals to peripheral devices. |

# (9) Test pins

| Pin Name | I/O    | Function                                  |

|----------|--------|-------------------------------------------|

| ТМО      | Input  | Device test pin. Connect this pin to GND. |

| TM1      | Input  | Device test pin. Connect this pin to GND. |

| TM2      | Input  | Device test pin. Connect this pin to GND. |

| ТМЗ      | Input  | Device test pin. Connect this pin to GND. |

| TM4      | Input  | Device test pin. Connect this pin to GND. |

| TM5      | Input  | Device test pin. Connect this pin to GND. |

| TM6      | Input  | Device test pin. Connect this pin to GND. |

| TM7      | Input  | Device test pin. Connect this pin to GND. |

| ТМ8      | Output | Device test pin. Leave this pin open.     |

| ТМ9      | Input  | Device test pin. Connect this pin to GND. |

| TM10     | Input  | Device test pin. Connect this pin to GND. |

# (10) Others

| Pin Name | I/O | Function                                             |

|----------|-----|------------------------------------------------------|

| N.C.     | _   | Reserved pin for compatibility with future products. |

|          |     | Leave this pin open.                                 |

# 1.4 Connection of Unused Pins

It is recommended to connect the unused pins as shown in the table below.

| Pin Name      | I/O    | Recommended Connection |

|---------------|--------|------------------------|

| A0            | Input  | Connect to GND.        |

| ASO1          | Output | Leave open.            |

| ASI1          | Input  | Connect to GND.        |

| ASI2          | Input  | Connect to GND.        |

| BCLK1         | I/O    | Leave open.            |

| LRCLK1        | I/O    | Leave open.            |

| PO0 to PO7    | Output | Leave open.            |

| SD_CLKI       | Input  | Connect to GND.        |

| SD_CLKO       | Output | Leave open.            |

| SD_CD         | Input  | Connect to GND.        |

| SD_CMD        | I/O    | Connect to GND.        |

| SD_DATA0 to 3 | I/O    | Connect to GND.        |

| SD_WP         | Input  | Connect to GND.        |

| TM0 to TM7    | Input  | Connect to GND.        |

| TM8           | Output | Leave open.            |

| TM9, TM10     | Input  | Connect to GND.        |

Caution: Leave the N.C. pins open.

## 1.5 Initial State of Pins

| Pin Name      | I/O    | During Reset      | After Reset       |

|---------------|--------|-------------------|-------------------|

| INT_B         | Output | High-level output | High-level output |

| ASO1, ASO2    | Output | Hi-Z              | Output            |

| BCLK1         | I/O    | Hi-Z              | Output            |

| BCLK2         | I/O    | Hi-Z              | Input             |

| LRCLK1        | I/O    | Hi-Z              | Output            |

| LRCLK2        | I/O    | Hi-Z              | Input             |

| D0 to D15     | I/O    | Hi-Z              | Input             |

| PO0 to PO7    | Output | Low-level output  | Low-level output  |

| SD_CLKO       | Output | Low-level output  | Low-level output  |

| SD_CMD        | I/O    | Hi-Z              | Input             |

| SD_DATA0 to 3 | I/O    | Hi-Z              | Input             |

Notes 1. This LSI enters the transparency mode after reset.

- 2. The pin status in the deep sleep mode is the same as that during reset.

- **3.** The statuses of the ASO1/2, BCLK1/2, and LRCLK1/2 pins can be controlled by the ASMODE register after reset.

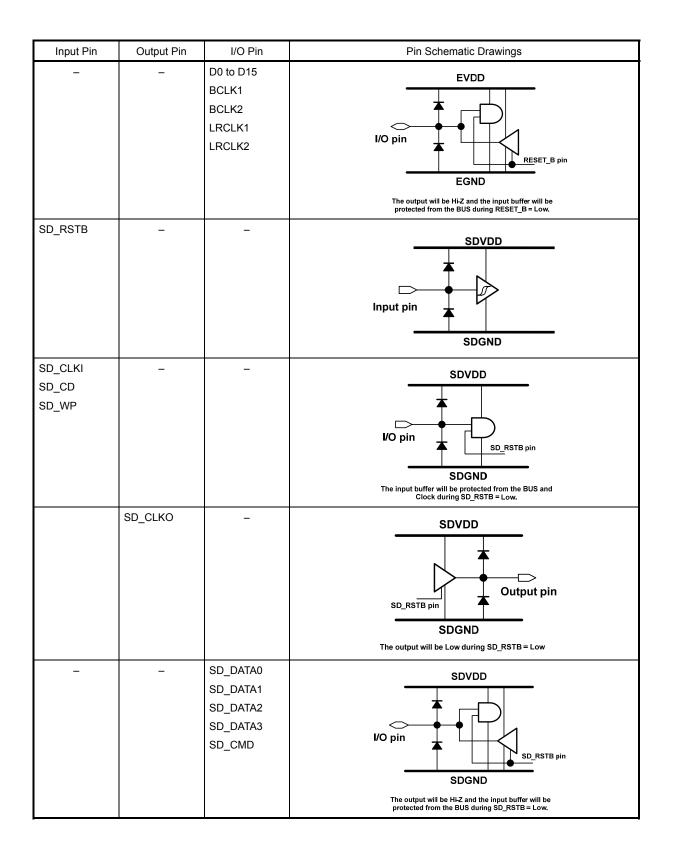

# 1.6 Pin Protection

By setting the RESET\_B pin to Low (during reset), pins are protected from the bus and no switching current flows into any of the functional pins even if the bus is activated.

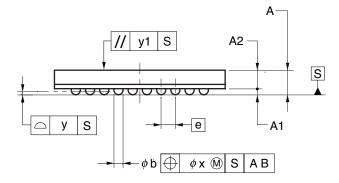

# 1.7 Pin Outline Schematics

| Input Pin                                                  | Output Pin   | I/O Pin | Pin Schematic Drawings                                                                                        |

|------------------------------------------------------------|--------------|---------|---------------------------------------------------------------------------------------------------------------|

| RESET_B                                                    | -            | _       | EVDD<br>Input pin<br>EGND                                                                                     |

| CLKIN<br>CS_B<br>WR_B<br>RD_B<br>A0 to A10<br>ASI1<br>ASI2 | _            | _       | EVDD<br>Input pin<br>EGND<br>The input buffer will be protected from the BUS and<br>Clock during RESET_B=Low. |

| -                                                          | ASO1<br>ASO2 | _       | EVDD<br>Output pin<br>EGND<br>The output will be Hi-Z during RESET_B = Low                                    |

| -                                                          | PO0 to PO7   | _       | EVDD<br>Output pin<br>EGND<br>The output will be Low state during RESET_B = Low                               |

| -                                                          | INT_B        | _       | EVDD<br>Output pin<br>EGND<br>The output will be High during RESET_B = Low                                    |

# 2. INTERNAL POWER AND CLOCK DOMAINS

## 2.1 Power Domains

This LSI needs four power supplies (EVDD, DVDD, PLLVDD and SDVDD) and there are six power domains internally on this LSI. Internal DVDD1 is supplied while DVDD is supplied. Internal DVDD2 and DVDD3 are generated from DVDD by power switch, so it can cut off its domain internally.

| Item         | A/D     | Voltage Range  | Syr              | mbol          | Blocks                                               |  |  |  |  |

|--------------|---------|----------------|------------------|---------------|------------------------------------------------------|--|--|--|--|

| item         | AD      | voltage Range  | Pin              | Internal      | DIUCKS                                               |  |  |  |  |

| I/O          | Digital | 1.7 to 2.0 V   | EVDD<br>EGND     |               | Digital I/O buffer                                   |  |  |  |  |

|              |         |                |                  | DVDD1<br>DGND | Host interface, pin control<br>Chip control register |  |  |  |  |

| Digital core | Digital | 1.16 to 1.24 V | DVDD<br>DGND     | DVDD2<br>DGND | CPU, audio processor, RAM                            |  |  |  |  |

|              |         |                |                  | DVDD3<br>DGND | SD interface block                                   |  |  |  |  |

| PLL          | Analog  | 1.16 to 1.24 V | PLLVDD<br>PLLGND |               | PLL                                                  |  |  |  |  |

| SD I/O       | Digital | 2.7 to 3.0 V   | SDVDD            |               | SD I/O                                               |  |  |  |  |

Table 2.1 Power Domains

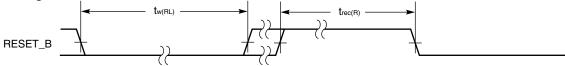

#### 2.1.1 Hardware reset

There are two types of hardware reset on this LSI. One is controlled by a pin and the other is controlled by a command register.

## (1) RESET\_B (pin)

RESET\_B is a hardware reset pin for all internal circuits of this LSI. The LSI enters the reset state when RESET\_B set to Low (EGND level). The functions of these pins are as follows.

- Initialization of all registers

All registers will be set to the default value immediately after RESET\_B is set to Low. DVDD2 and DVDD3 domains are OFF after RESET\_B is set to Low.

- Initialization of all circuits

- Initialization of I/O buffer functions (EVDD domain) for bus protection

- Protection of internal level shifter between internal EVDD and DVDD domains during power switching

#### (2) RSTBFNC (command register)

RSTBFNC is a hardware reset register for the DVDD2 domain. It can be controlled during RESET\_B = High.

- Initialization of internal CPU registers and audio processor registers (DVDD2 domain)

- Initialization of all circuits of DVDD2 domain

- Protection of input between internal DVDD1 and DVDD2 domains during power switching

#### (3) RSTBSD (command register)

RSTBSD is a hardware reset register for the DVDD3 domain. It can be controlled during RESET\_B = High. DVDD3 domain is initialized by RSTBSD after a clock is supplied for the DVDD3 domain.

- Initialization of SD interface registers (DVDD3 domain)

- Initialization of all circuits of DVDD3 domain

- Protection of input between internal DVDD1 and DVDD3 domains during power switching

## (4) SD\_RSTB (pin)

SD\_RSTB is a hardware reset pin exclusively for SD interface I/O (SDIO). SDIO enters the reset state when SD\_RSTB is set to Low (SDGND level). The circuits of the DVDD3 domain are not initialized by this pin. The functions of these pins are as follows.

- Initialization of I/O buffer functions (SDVDD domain) for SD Card bus protection

- Protection of internal level shifter between SDVDD and DVDD domains during power switching

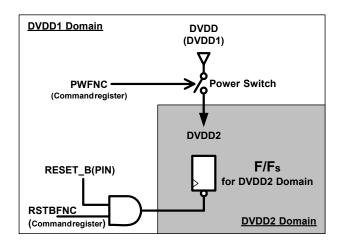

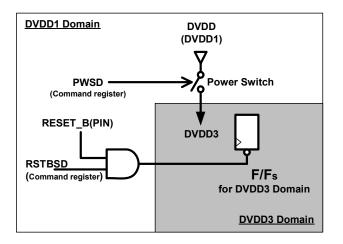

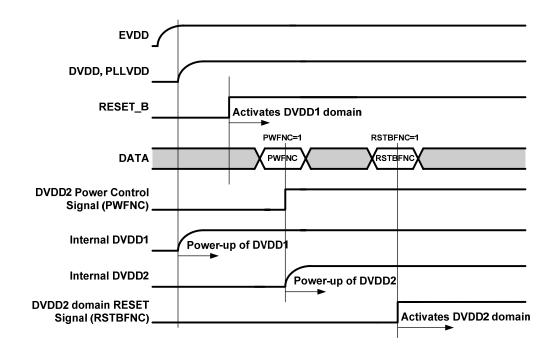

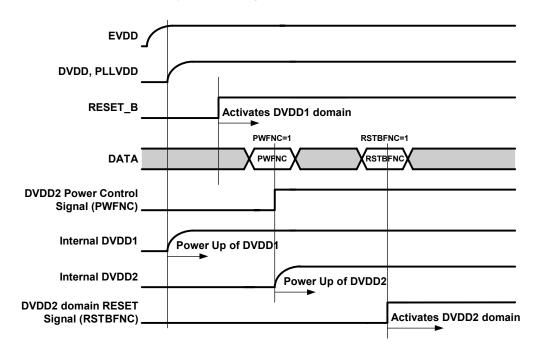

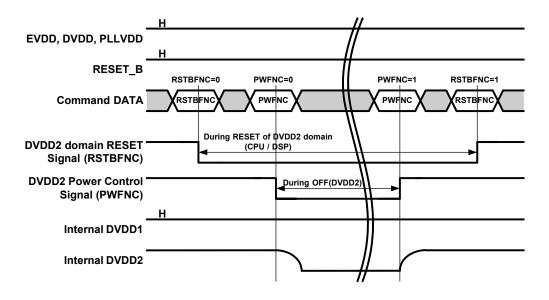

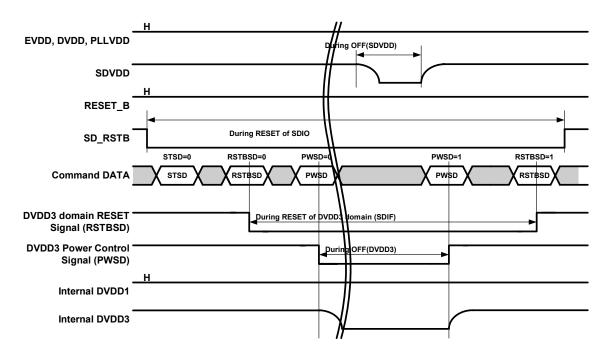

## 2.1.2 Power/reset control of DVDD2 and DVDD3 domains

It is possible to cut-off the internal DVDD2 and DVDD3 domains by command register control while DVDD is supplied, so it is also possible to reduce the standby current of each domain.

The PWFNC register is used for DVDD2 power control. PWFNC is OFF by default, which means the DVDD2 domain is OFF. Therefore, the DVDD2 domain circuits cannot be initialized by the RESET\_B pin. The RSTBFNC register is also used to protect the input gates of the DVDD2 domain for security reasons. The DVDD2 domain must therefore be reset by the RSTBFNC register before DVDD2 will be ON.

Figure 2.1.2 Power/Reset Control of DVDD2 Domain

The PWSD register is used for DVDD3 power control. PWSD is OFF by default, which means the DVDD3 domain is OFF. Therefore, the DVDD3 domain circuits cannot be initialized by the RESET\_B pin. They are initialized by the RSTBSD register after the DVDD3 domain is turned on. RSTBSD is also used to protect input gates of DVDD3 domain for security reasons. The DVDD3 domain must therefore be reset by the RSTBSD register before DVDD3 will be ON.

Figure 2.1.3 Power and Reset Control of DVDD3 Domain

The power control sequence is described in section 7.

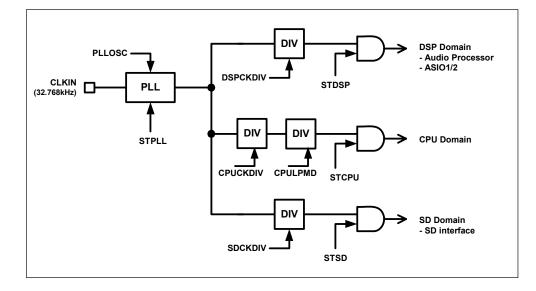

## 2.2 Clock Domains

## 2.2.1 CLKIN

CLKIN is a system clock input pin. It is necessary to supply a 32.768 kHz clock from the RTC.

## 2.2.2 PLL

The PLL circuit generates an internal master clock from the CLKIN input (32.768 kHz). It is controllable by a command register (PLLOSC).

## 2.2.3 Divider and domains

This LSI has three clock domains. Dividers make a clock of domain from the PLL output. They are controllable by command registers (DSPCKDIV, CPUCKDIV, and SDCKDIV).

## - DSP domain

Audio processor, ASIO1/2

- CPU domain

Internal CPU for stream control, stream buffer

- SD domain

SD interface core

## 2.2.4 Standby

Standby registers enable internal clocks to be supplied. The standby registers are also used for saving power.

- STPLL

Enables PLL block operation.

- STDSP

Enables clock supply to DSP domain.

- STCPU

Enables clock supply to CPU domain.

- STSD

Enables clock supply to SD domain.

Figure 2.2.1 Clock Domains

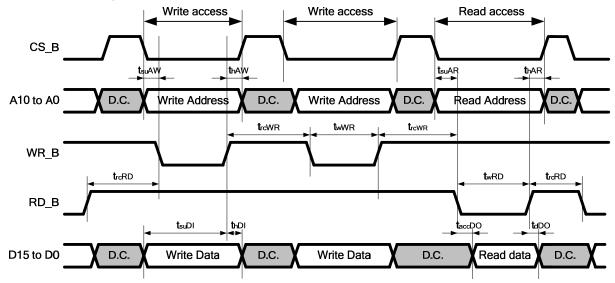

# 3. HOST CPU INTERFACE

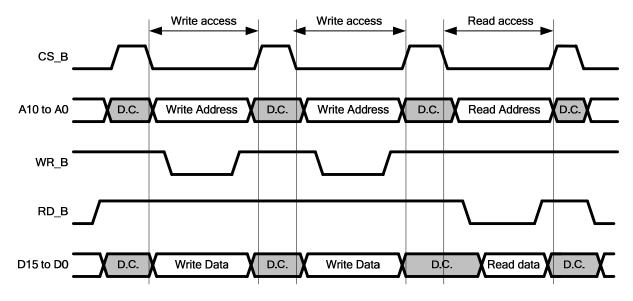

This LSI communicates as a slave device, with the host system by using a 16-bit parallel interface. This LSI detects the address and data at a low level period of the CS\_B pin and takes into the data at a low level width and a rising edge of the WR\_B pin.

Figure 3.1 Parallel Interface Format

- Caution: 1. Be sure to observe the timing requirements of the parallel interface.

- 2. Be sure to fix the RD\_B pin to high during the write cycle (WR\_B = Low). Be sure also to fix the WR\_B pin to high level during the read cycle (RD\_B = Low).

**Remark:** D.C.: Don't care.

# 4. AUDIO SERIAL INTERFACE

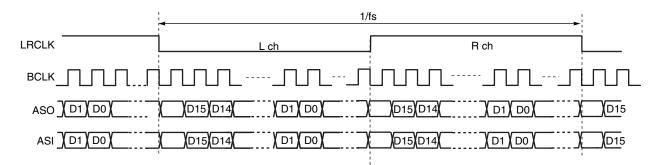

The audio serial interface (ASIO) is used for transmitting and receiving 16-bit PCM data serially. This LSI has two ASIOs, so it is easy to perform signal processing between the host and audio front-end device.

The available functions on each ASIO are as follows. These functions can be enabled by setting command registers.

- The I<sup>2</sup>S format is available.

- Master operation and slave operation are supported.

Master operation: The signal received as a slave is used for the master.

| ASIO1  | ASIO2  | Comments                                                                                                                          |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| Slave  | Slave  | Prohibited                                                                                                                        |

| Slave  | Master | Available. ASIO1 and ASIO2 must be used under the same conditions and operated synchronously.<br>ASIO2 can not be operated alone. |

| Master | Slave  | Available. ASIO1 and ASIO2 must be used under the same conditions and operated synchronously.<br>ASIO1 cannot be operated alone.  |

| Master | Master | Prohibited                                                                                                                        |

- Serial data clock (the number of data bits per sample) can be varied.

32 to 128 fs, by 2 fs steps

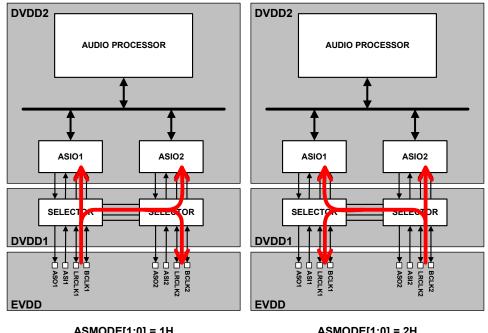

- Transparency mode (direct connection between ASIO1 and ASIO2) is supported. (This mode is set by default.)

## 4.1 Format

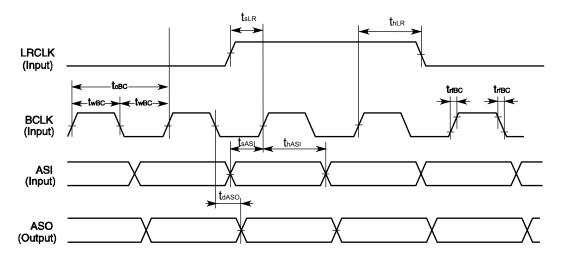

Figure 4.1 I<sup>2</sup>S Format

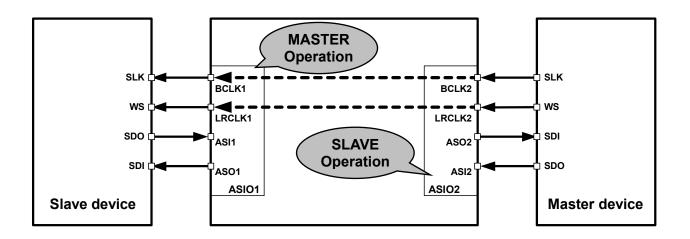

# 4.2 Synchronous Operation

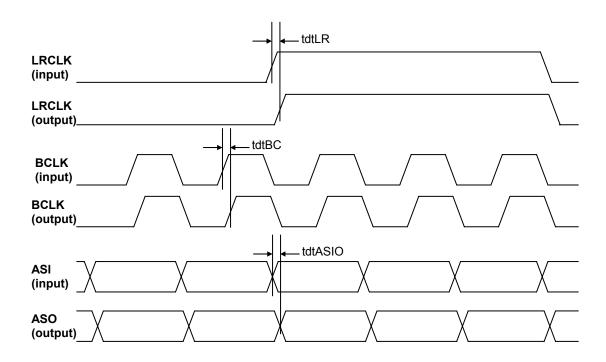

Synchronous operation is available when placing this LSI between a master device and a slave device on a serial PCM bus. This LSI outputs a serial clock (BCLK) and a word sync signal (LRCLK) to a slave device, as a master operation. These clocks are the same as those received from a master device. ASIO1 and ASIO2 therefore operate with the same format and setting.

Figure 4.2 Synchronous Operation

ASMODE[1:0] = 1H

ASMODE[1:0] = 2H

Figure 4.3 Relation Between Master and Slave

# 4.3 Transparency Mode

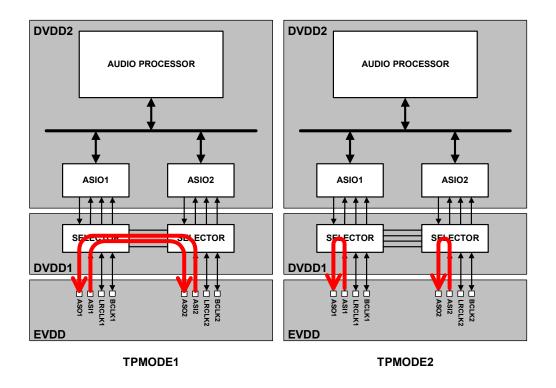

ASIO1 and ASIO2 can be directly connected internally (transparency mode). There are two types of the transparency modes.

- Connection of ASIO1 and ASIO2 ASI1  $\rightarrow$  ASO2, ASI2  $\rightarrow$  ASO1

- Connection inside ASIO1 or ASIO2) ASI1  $\rightarrow$  ASO1, ASI2  $\rightarrow$  ASO2

The connection type can be specified by using a control register. These pins are assigned in the DVDD1 domain. The other DVDD domains can be cut off during this mode, so the power consumption can be reduced.

Figure 4.4 Transparency Mode

# 5. REGISTERS

# 5.1 Register Maps

| ync/Async Power domain |

|------------------------|

| A DVDD1                |

| DVDD1                  |

| DVDD2                  |

| DVDD2                  |

| DVDD3                  |

| DVDD3                  |

| DVDD2                  |

| DVDD2                  |

|                        |

## 5.1.1 Register map for chip control

|         |     |     |     |       |          |       |          | 0.1   |          | ·       |         | ~p .v   |         | p       |         |         |         |         |                                        |                  |

|---------|-----|-----|-----|-------|----------|-------|----------|-------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------------------------------------|------------------|

| Address | W/R | D15 | D14 | D13   | D12      | D11   | D10      | D9    | D8       | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      | Default | Contents                               | Register<br>Name |

| 000H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | 0       | 0       | 0       | PWSD    | 0       | 0       | 0       | PWFNC   | 0000H   | Power domains                          | PWSW             |

| 002H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | 0       | 0       | 0       | RSTBS   | 0       | 0       | 0       | RSTBFNC | 0000H   | Async RESET for<br>Power domains       | RSTB             |

| 004H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | STSD     | 0       | 0       | STCPU   | STDSP   | 0       | 0       | 0       | STPLL   | 0000H   | Standby setting                        | STNBYB           |

| 006H    | W/R | 0   | 0   | SDCKD | 0IV[1:0] | CPUCK | DIV[1:0] | DSPCK | DIV[1:0] | CPULPI  | MD[1:0] |         |         | PLLOS   | SC[5:0] |         |         | 0827H   | Master clock setting                   | MCLK             |

| 00AH    | w   | 0   | 0   | 0     | 0        | 0     | 0        | TPMO  | DE[1:0]  | 0       | 0       | ASMO    | DE[1:0] | ASI1EN  | ASO1EN  | ASI2EN  | ASO2EN  | 012FH   | ASIO control                           | ASIOCNT          |

| 020H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | POUT7   | POUT6   | POUT5   | POUT4   | POUT3   | POUT2   | POUT1   | POUT0   | 0000H   | General purpose port<br>output setting | POUT             |

| 030H    | R   | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | INTSRC7 | INTSRC6 | INTSRC5 | INTSRC4 | INTSRC3 | INTSRC2 | INTSRC1 | INTSRC0 | 0000H   | Interrupt source<br>register           | INTSRC           |

| 032H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | 0       | 0       | 0       | 0       | 0       | ITIM2   | ITIM1   | ITIM0   | 0000H   | Interrupt clear for<br>Timer           | ITIM             |

| 034H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | INTM7   | INTM6   | INTM5   | INTM4   | INTM3   | INTM2   | INTM1   | INTM0   | 0000H   | Mask for INT<br>controllor input       | INTM             |

| 040H    | W/R | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | 0       | 0       | 0       | 0       | 0       | 0       | 0       | ENFLG   | 0000H   | Enable flag for device<br>access       | ENFLG            |

| 042H    | R   | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | 0       | 0       | 0       | 0       | 0       | 0       | CSTCPU  | CSTDSP  | 0000H   | Status of continuous<br>access         | CSTA             |

| 044H    | w   | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        | 0       | 0       | 0       | 0       | 0       | 0       | CCLRCPU | CCLRDSP | 0000H   | Release of continuous<br>access        | CCLR             |

| 070H    | R   | 0   | 0   | 0     | 0        | 0     | 0        | 0     | 0        |         | PVEF    | R[3:0]  |         |         | MVE     | R[3:0]  |         | 004*H   | Product discernment<br>and LSI Version | VER              |

## Table 5.1.1 Register Map for Chip Control

Note: Addresses 030H, 032H and 034H can be read or written after PLL is activated.

## Caution: Register accesses except for the above addresses are prohibited.

## 5.1.2 Register map for DSP control

#### Table 5.1.2 Register Map for DSP Control

| Address           | W/R | D15 | D14 | D13 | D12 | D11 | D10 | D9     | D8        | D7      | D6    | D5 | D4 | D3 | D2 | D1 | D0 | Default | Contents | Register<br>Name |

|-------------------|-----|-----|-----|-----|-----|-----|-----|--------|-----------|---------|-------|----|----|----|----|----|----|---------|----------|------------------|

| 200H<br>:<br>2FEH | W/R |     |     |     |     |     |     | Regist | ers for t | the DSF | block |    |    |    |    |    |    |         |          |                  |

Note: This register area can be accessed after PLL is activated and STDSP is set to 1.

## Caution: Register accesses except for the above addresses are prohibited.

## 5.1.3 Register map for CPU control

|                   | Table 5.1.3 Register Map for CPU Control |     |                                                                       |  |  |  |    |         |           |         |         |     |  |  |  |  |                  |  |  |  |

|-------------------|------------------------------------------|-----|-----------------------------------------------------------------------|--|--|--|----|---------|-----------|---------|---------|-----|--|--|--|--|------------------|--|--|--|

| Address           | W/R                                      | D15 | 15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Default Contents |  |  |  |    |         |           |         |         |     |  |  |  |  | Register<br>Name |  |  |  |

| 300H<br>:<br>3FEH | W/R                                      |     |                                                                       |  |  |  | Re | gisters | for the i | nternal | CPU blo | ock |  |  |  |  |                  |  |  |  |

**Note:** This register area can be accessed after PLL is activated and STCPU is set to 1.

#### Caution: Register accesses except for the above addresses are the prohibited.

## 5.1.4 Register map for SD interface control

|                   | Table 5.1.4 Register Map for SD Interface Control |     |                            |     |     |     |     |    |    |    |    |    |    |    |    |    |    |         |          |                  |

|-------------------|---------------------------------------------------|-----|----------------------------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------|----------|------------------|

| Address           | W/R                                               | D15 | D14                        | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Default | Contents | Register<br>Name |

| 400H<br>:<br>5FEH |                                                   |     | Registers for SD intreface |     |     |     |     |    |    |    |    |    |    |    |    |    |    |         |          |                  |

Note: This register area can be accessed after PLL is activated and STSD is set to 1.

#### Caution: Register accesses except for the above addresses are the prohibited.

# 5.2 Chip Control Registers

## 5.2.1 Power domain control register: PWSW (Address: 000H)

### (1) **PWFNC**

This is a bit that controls inside the DVDD2 domain.

PWFNC = 1 enables power supply to the DVDD2 domain.

The values of DSP registers, RAM and DSP will not be kept during PWFNC = 0. After setting PWFNC to 1, a hardware reset must be applied (RSTBFNC register) to DVDD2 domain.

#### PWFNC

| Data | Mode | Initial Value | Description                                       |

|------|------|---------------|---------------------------------------------------|

| 0    | OFF  | 0             | Internal power supply to DVDD2 domain is cut off. |

| 1    | ON   |               | Normal operation                                  |

#### (2) PWSD

This is a bit that controls inside the DVDD3 domain.

PWSD = 1 enables power supply to the DVDD3 domain.

The values of SD registers and SD interface core will not be kept during PWSD = 0. After setting PWSD to 1, a hardware reset must be applied (RSTBSD register) to the DVDD3 domain.

#### PWSD

| Data | Mode | Initial Value | Description                                       |

|------|------|---------------|---------------------------------------------------|

| 0    | OFF  | 0             | Internal power supply to DVDD3 domain is cut off. |

| 1    | ON   |               | Normal operation                                  |

## 5.2.2 Async RESET for power domains register: RSTB (Address: 002H)

The RSTB register initializes the internal states of the DVDD2 and DVDD3 domains. This register must be asserted after power-on for each domain.

## (1) RSTBFNC

This is a hardware reset bit for the DVDD2 domain. This bit must be set to 0, if PWFNC is changed.

#### RSTBFNC

| Data | Mode   | Initial Value | Description                           |

|------|--------|---------------|---------------------------------------|

| 0    | Reset  | 0             | Hardware async reset for DVDD2 domain |

| 1    | Active |               | Normal operation                      |

### (2) RSTBSD

This is a hardware reset bit for the DVDD3 domain. This bit must be set to 0, if PWSD is changed.

#### RSTBSD

| Data | Mode   | Initial Value | Description                           |

|------|--------|---------------|---------------------------------------|

| 0    | Reset  | 0             | Hardware async reset for DVDD3 domain |

| 1    | Active |               | Normal operation                      |

## 5.2.3 Standby setting register: STNBY (Address: 004H)

This is a register that controls internal functional blocks and controls clock supply to the specific block. The register does not initialize each block.

## (1) STPLL

This is a bit that controls PLL standby. This controls PLL on/off.

#### STPLL

| Data | Mode    | Initial Value | Description               |

|------|---------|---------------|---------------------------|

| 0    | Standby | 0             | Sets PLL block to standby |

| 1    | ON      |               | Normal operation          |

Remark: The PLL output clock is stopped during PLL standby mode (power down).

**Note:** Since the clock is not supplied to internal blocks during PLL standby, the block does not operate even if the STxx bit is set to 1.

#### (2) STDSP

This is a bit that controls an audio processor standby. The audio processor block enters the standby when this bit is set to 0. The DSP registers cannot be accessed because no clock is supplied. The DSP block is not initialized by setting this bit, but by hardware reset using RESET\_B, RSTBFNC, or a DSP command.

#### STDSP

| Data | Mode    | Initial Value | Description               |

|------|---------|---------------|---------------------------|

| 0    | Standby | 0             | Sets DSP block to standby |

| 1    | ON      |               | Normal operation          |

## (3) STCPU

This is a bit that controls internal CPU standby. The internal CPU block enters the standby when this bit is set to 0. The CPU registers cannot be accessed because no clock is supplied. The CPU block is not initialized by setting this bit, but by hardware reset using RESET B, RSTBFNC, or a CPU command.

#### STCPU

| Data | Mode    | Initial Value | Description               |

|------|---------|---------------|---------------------------|

| 0    | Standby | 0             | Sets CPU block to standby |

| 1    | ON      |               | Normal operation          |

#### (4) STSD

This is a bit that controls the SD interface core standby. The SD interface core block enters the standby when this bit is set to 0. The SD register cannot be accessed because no clock is supplied. The SD interface core block. The block is not initialized by setting this bit, but by hardware reset using RESET B or RSTBSD.

STSD

| Data | Mode    | Initial Value | Description              |

|------|---------|---------------|--------------------------|

| 0    | Standby | 0             | Sets SD block to standby |

| 1    | ON      |               | Normal operation         |

# 5.2.4 Master clock setting register: MCLK (Address: 006H)

The MCLK register controls the master clock on the LSI side.

## (1) PLLOSC

These are PLL output control register bits.

## PLLOSC[5:0]

| PLLOSC[5:0] | Initial Value | Oscillation Frequency [MHz] |

|-------------|---------------|-----------------------------|

| 1DH         | 27H           | 122.880                     |

| 1EH         |               | 126.976                     |

| 1FH         |               | 131.072                     |

| 20H         |               | 135.168                     |

| 21H         |               | 139.264                     |

| 22H         |               | 143.360                     |

| 23H         |               | 147.456                     |

| 24H         |               | 151.552                     |

| 25H         |               | 155.648                     |

| 26H         |               | 159.744                     |

| 27H         |               | 163.840                     |

Caution: 00 to 1C and 28H to 3F are invalid. These setting are prohibited.

### (2) DSPCKDIV

This is a register that sets the division ratio of the clock supplied to the DSP domain.

## DSPCKDIV[1:0]

| DSPCKDIV[1:0] | Initial Value | Division Ratio |

|---------------|---------------|----------------|

| ОН            | 0H            | 1/2            |

| 1H            |               | 1/3            |

| 2H            |               | 1/4            |

Caution: 3H is invalid and is prohibited.

# (3) CPUCKDIV

This is a register that sets the division ratio of the clock supplied to the CPU domain.

## CPUCKDIV[1:0]

| CPUCKDIV[1:0] | Initial Value | Division Ratio |

|---------------|---------------|----------------|

| ОH            | 2H            | 1/2            |

| 1H            |               | 1/3            |

| 2H            |               | 1/4            |

Caution: 3H is invalid and prohibited.

## (4) SDCKDIV

NEC

This is a register that sets the division ratio of the clock supplied to the SD domain.

## SDCKDIV[1:0]

| SDCKDIV[1:0] | Initial Value | Division Ratio |

|--------------|---------------|----------------|

| ОН           | ОH            | 1/2            |

| 1H           |               | 1/3            |

| 2H           |               | 1/4            |

Caution: 3H is invalid and prohibited.

### (5) CPULPMD

This is a register that sets the division ratio of the clock supplied to the CPU domain.

#### CPULPMD[1:0]

| CPULPMD[1:0] | Initial Value | Division Ratio |

|--------------|---------------|----------------|

| 0H           | 0H            | 1/1            |

| 1H           |               | 1/2            |

| 2H           |               | 1/4            |

Caution:

3H is invalid and prohibited.

These registers must be changed when STCPU = 0 or STPLL = 0.

#### 5.2.5 ASIO control register: ASIOCNT (Address: 00AH)

## (1) ASI1EN, ASI2EN, ASO1EN, ASO2EN

These bits control the ASI1, ASI2, ASO1 and ASO2 pin statuses.

## ASI1EN

| Data | Mode | Initial Value | Description   |

|------|------|---------------|---------------|

| 0    | OFF  | 1             | Disables ASI1 |

| 1    | ON   |               | Enables ASI1  |

## ASI2EN

| Data | Mode | Initial Value | Description   |

|------|------|---------------|---------------|

| 0    | OFF  | 1             | Disables ASI2 |

| 1    | ON   |               | Enables ASI2  |

#### ASO1EN

| Data | Mode | Initial Value | Description                                        |

|------|------|---------------|----------------------------------------------------|

| 0    | OFF  | 1             | Disables ASO1 (ASO1 will be Hi-Z when ASO1EN = 0.) |

| 1    | ON   |               | Enables ASO1                                       |

### ASO2EN

| Data | Mode | Initial Value | Description                                        |

|------|------|---------------|----------------------------------------------------|

| 0    | OFF  | 1             | Disables ASO2 (ASO2 will be Hi-Z when ASO2EN = 0.) |

| 1    | ON   |               | Enables ASO2                                       |

Note: 1. When ASI1EN = ASO1EN = 0, both LRCLK1 and BCLK1 pins become Hi-Z.

When ASI2EN = ASO2EN = 0, both LRCLK2 and BCLK2 pins become Hi-Z.

- ASO1 will be Hi-Z when ASO1EN = 0.

ASO2 will be Hi-Z when ASO2EN = 0.

- **3.** ASI1 and ASI2 must be low or high after reset regardless of ASI1EN/ASI2EN. Unexpected current may flow if ASI1 or ASI2 is in the Hi-Z state.

## (2) ASMODE

These bits control synchronous operation. They control the master/slave operation for the ASIO1 and ASIO2 blocks. The LRCLK and BCLK inputs of the slave mode ASIO will be output to ones of the master mode ASIO, so the LSI cannot be the original master.

## ASMODE[1:0]

| Data | Initial Value | ASIO1  | ASIO2  | Description                                                 |

|------|---------------|--------|--------|-------------------------------------------------------------|

| 0H   | 2H            | Slave  | Slave  | Setting prohibited                                          |

| 1H   |               | Slave  | Master | The LRCLK and BCLK of ASIO2 are the same as those of ASIO1. |

| 2H   |               | Master | Slave  | The LRCLK and BCLK of ASIO1 are the same as those of ASIO2. |

| 3H   |               | Master | Master | Setting prohibited                                          |

## **Pin directions**

| Data | LRCLK1 | BCLK1 | LRCLK2 | BCLK2 |

|------|--------|-------|--------|-------|

| 1H   | IN     | IN    | OUT    | OUT   |

| 2H   | OUT    | OUT   | IN     | IN    |

## (3) TPMODE

These are register bits that control the transparency mode. Other than TPMODE = 0H, ASI1/ASI2 and ASO1/ASO2 are disconnected from internal circuits, and connected directly to each other in the DVDD1 domain.

#### TPMODE[1:0]

| Data | Mode    | Initial Value | Description                                           |

|------|---------|---------------|-------------------------------------------------------|

| ОН   | Normal  | 1H            | Connects ASI1/ASI2 and ASO1/ASO2 to internal circuits |

| 1H   | TPMODE2 |               | Connects ASO1 to ASI2 and ASO2 to ASI1.               |

| 2H   | TPMODE2 |               | Connects ASO1to ASI1, and ASO2 to ASI2.               |

| ЗH   | _       |               | Setting prohibited                                    |

## 5.2.6 General-purpose output port setting register: POUT (Address: 020H)

The PO0 to PO7 pins output the POUT register value written from the host.

This register is placed into the DVDD1 domain. This is therefore not related to the ON/OFF state of the DVDD2 domain and can control the PO0 to PO7 pins while the DVDD2 domain is OFF.

## POUT[7:0]

| Data | Mode | Initial Value | Description                                             |

|------|------|---------------|---------------------------------------------------------|

| 0    | Low  | 0             | Low-level output from corresponding pins to PO0 to PO7  |

| 1    | High |               | High-level output from corresponding pins to PO0 to PO7 |

Note: The PO0 to 07 pins output 0 (low) during RESET\_B = Low, and POUT values after reset.

### 5.2.7 Interrupt source register: INTSRC (Address: 030H)

This register is used to distinguish sources of interrupts generated by some function blocks. This register is set to 1 when an internal function block requests interruption.

#### INTSRC[7:0]

| Data    | Mode | Initial Value | Description             |

|---------|------|---------------|-------------------------|

| 15 to 8 | R    | 0             | Reserved                |

| 7 to 0  | R    |               | 0: No interrupt request |

|         |      |               | 1: Interrupt request    |

Note: This register is controlled by the API software on the host.

#### 5.2.8 Timer interrupt clear register: ITIM (Address: 032H)

This register clears the timer interrupts. When this register is set to 1, the interrupt request is cleared. When this register is set to 0, the interrupt state is held.

#### ITIM[2:0]

| Data | Mode  | Initial Value | Description                   |

|------|-------|---------------|-------------------------------|

| 0    | Keep  | 0             | Holds interrupt request state |

| 1    | Clear |               | Clears interrupt requests     |

Note: This register is controlled by the API software on the host...

### 5.2.9 Interrupt mask register: INTM (Address: 034H)

This register masks interrupt requests issued by function blocks.

#### INTM[7:0]

| Data    | Mode | Initial Value               | Description                         |  |  |  |  |

|---------|------|-----------------------------|-------------------------------------|--|--|--|--|

| 15 to 8 | R    | 0                           | Reserved                            |  |  |  |  |

| 7 to 0  | R/W  |                             | Mask of interrupt request input     |  |  |  |  |

|         |      | 0: Masks interrupt requests |                                     |  |  |  |  |

|         |      |                             | 1: Does not mask interrupt requests |  |  |  |  |

Note: This register is controlled by the API software on the host.

## 5.2.10 PLL activation enable flag register: ENFLG (Address: 040H)

This register indicates whether the PLL operation is active. This register is set to 1 after PLL is stabilized.

## ENFLG

| Data | Mode     | Initial Value | Description                    |  |  |  |  |

|------|----------|---------------|--------------------------------|--|--|--|--|

| 0    | Inactive | 0             | The PLL operation is active.   |  |  |  |  |

| 1    | Active   |               | The PLL operation is inactive. |  |  |  |  |

## 5.2.11 Continuous data access control registers: CSTA (Address: 042H), CCLR (Address: 044H)

#### (1) CSTDSP

This register indicates that the host accesses data in the continuous mode for the DSP. This register holds 1 during the continuous data access mode.

This register is reset to 0 when the data access is complete correctly.

This register is reset to 0 when the CCLRDSP register is set to 1.

#### CSTDSP

| Data | Mode       | Initial Value | Description            |  |  |  |

|------|------------|---------------|------------------------|--|--|--|

| 0    | Normal     | 0             | Normal                 |  |  |  |

| 1    | Continuous |               | Keeps continuous mode. |  |  |  |

## (2) CSTCPU

This register indicates that the host accesses data in the continuous mode for the CPU. This register holds 1 during the continuous data access mode.

This register is reset to 0 when the data access is complete correctly.

This register is reset to 0 when the CCLRCPU register is set to 1.

## CSTCPU

| Data | Mode       | Initial Value | Description            |

|------|------------|---------------|------------------------|

| 0    | Normal     | 0             | Normal                 |

| 1    | Continuous |               | Keeps continuous mode. |

## (3) CCLRDSP

This register forcedly releases the DSP continuous access mode.

While the host accesses data in the continuous mode (CSTDSP indicates 1), the host can release the continuous access mode by writing 1 to CCLRDSP.

The host must write 0 to this register after writing 1. This register is write-only.

#### CCLRDSP

| Data | Mode  | Initial Value | Description             |  |  |  |  |

|------|-------|---------------|-------------------------|--|--|--|--|

| 0    | _     | 0             | _                       |  |  |  |  |

| 1    | Clear |               | Clears continuous mode. |  |  |  |  |

## (4) CCLRCPU

This register forcedly releases the CPU continuous access mode. While the host accesses data in the continuous mode (CSTCUP indicates 1), the host can release the continuous access mode by writing 1 to CCLRCPU.

The host must write 0 to this register after writing 1. This register is write-only.

#### CCLRCPU

| Data | Mode  | Initial Value | Description             |  |  |  |  |

|------|-------|---------------|-------------------------|--|--|--|--|

| 0    | _     | 0             | _                       |  |  |  |  |

| 1    | Clear |               | Clears continuous mode. |  |  |  |  |

## 5.3 DSP Registers

DSP registers are used to control the audio processor (DSP). These registers can be accessed after PLL is activated and the standby mode is released. Furthermore, these registers are initialized by the RESET\_B pin or the RSTBFNC bit of the RSTB register.

The setting values of this area and related information are provided with the firmware.

#### 5.4 CPU Registers

CPU registers are used to control the internal CPU (CPU). These registers can be accessed after PLL is activated and the standby mode is released. Furthermore, these registers are initialized by the RESET\_B pin or the RSTBFNC bit of the RSTB register.

The setting values of this area and related information are provided with the firmware.

#### 5.5 SD Registers

SD registers are used to control the SD interface (SD). These registers can be accessed after PLL is activated and standby mode is released. Furthermore, these registers are initialized by the RESET\_B pin or the RSTBSD bit of the RSTB register.

## 6. POWER MANAGEMENT

## 6.1 Acceptable Power Supply Combinations

There are six power domains on this LSI. Acceptable combinations thereof are described below. (See Table 6.1).

|     | 1            |       |       |       |        |       |               | wer Supp  | iy oomon     |           |           |                      |

|-----|--------------|-------|-------|-------|--------|-------|---------------|-----------|--------------|-----------|-----------|----------------------|

| No. | Power Supply |       |       |       |        |       | Function/Mode |           |              |           |           | Comment/Restriction  |

|     | EVDD         |       | DVDD  |       | PLLVDD | SDVDD | Deep          | Sleep     | Transparency | Audio     | SD        |                      |

|     |              | DVDD1 | DVDD2 | DVDD3 |        |       | Sleep         |           |              | Decode    | Access    |                      |

| 1   | _            | _     | -     | _     | _      | _     | I             | -         | -            | -         | -         | Fully OFF            |

| 2   | ON           | -     | _     | _     | _      | -     | Available     | -         | -            | -         | _         | RESET_B = Low level  |

| 3   | ON           | ON    | _     | _     | ON     | -     | _             | Available | Available    | -         | _         | RSTBFNC = RSTBSD = 0 |

| 4   | ON           | ON    | ON    | -     | ON     | -     | -             | Available | Available    | Available | _         | RSTBSD = 0           |

| 5   | ON           | ON    | _     | ON    | ON     | ON    | _             | Available | Available    | -         | Available | RSTBFNC = 0          |

| 6   | ON           | ON    | ON    | ON    | ON     | ON    | -             | Available | Available    | Available | Available |                      |

| 7   | ON           | ON    | _     | _     | ON     | ON    | _             | Available | Available    | -         | _         | SD_RSTB = Low level  |

| 8   | ON           | ON    | ON    | _     | ON     | ON    | -             | Available | Available    | Available | _         | SD_RSTB = Low level  |

| 9   | ON           | -     | -     | -     | -      | ON    | Available     | -         | -            | -         | -         | RESET_B = Low level, |

|     |              |       |       |       |        |       |               |           |              |           |           | SD_RSTB = Low level  |

| 10  | -            | _     | -     | _     | _      | ON    | Available     | -         | -            | -         | _         | SD_RSTB = Low level  |

Table 6.1 Acceptable Power Supply Combinations

**Note:** DVDD2 and DVDD3 are internal power domains. They are controllable by the command registers (PWFNC, PWSD).

Caution: DVDD and PLLVDD must be supplied from the same source.

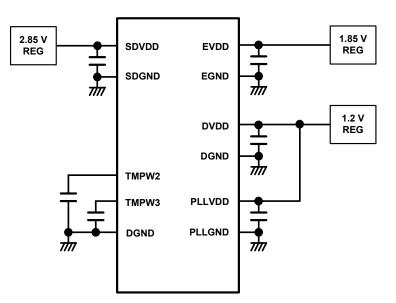

Figure 6.1 Power Supply Connection

Note: 1. It is recommended to minimize common impedance between pins DVDD and PLLVDD.

- 2. Connect capacitors as close as possible to the pins.

- 3. The capacitors of TMPW2 and TMPW3 are decoupling capacitors for pins DVDD2 and DVDD3.

## 6.2 Standby Modes

### 6.2.1 Sleep mode

This mode is used to reduce the time to return from the standby mode while power is being supplied. Data values of command registers and memory are kept during this mode, so it is not necessary to rewrite command registers or to re-download firmware.

The internal clock must be stopped by the command register during this mode, and power supply to the internal power domains must be kept on during this mode.

Caution: Data will be lost if the power domain is turned off.

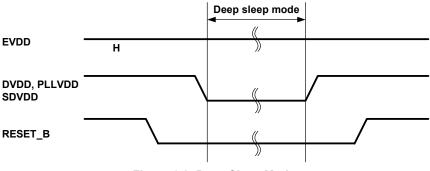

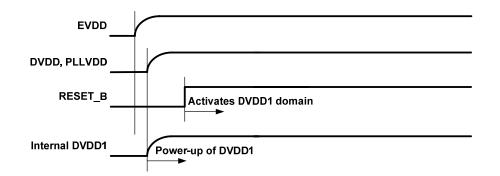

## 6.2.2 Transparency mode