# Power Management IC for Single-Cell Li-Ion Devices

#### **POWER MANAGEMENT**

#### **Features**

- Single Cell Li-lon battery charger CC/CV charging with current soft start

- Charger regulated output voltage 4.2V ±1% over temperature with Kelvin sense of battery voltage

- Charger input protection withstands 28V indefinitely

- Charger max constant current setting 500mA

- Adjustable charge termination current down to 10mA

- Battery NTC interface disables charging if battery temperature out of range

- Programmable low battery detector threshold

- Four status indicators

- Programmable charge completion timer

- Buck converter with enable output programmable from 1V to 3V, 150mA max output

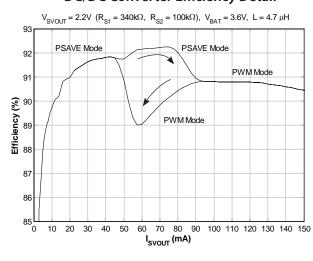

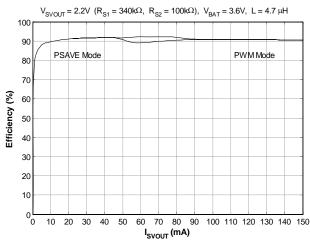

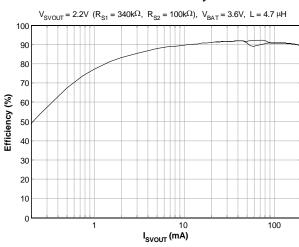

- Buck converter efficiency 88% at 50mA

- General purpose low noise LDO regulator with fast enable, active shutdown

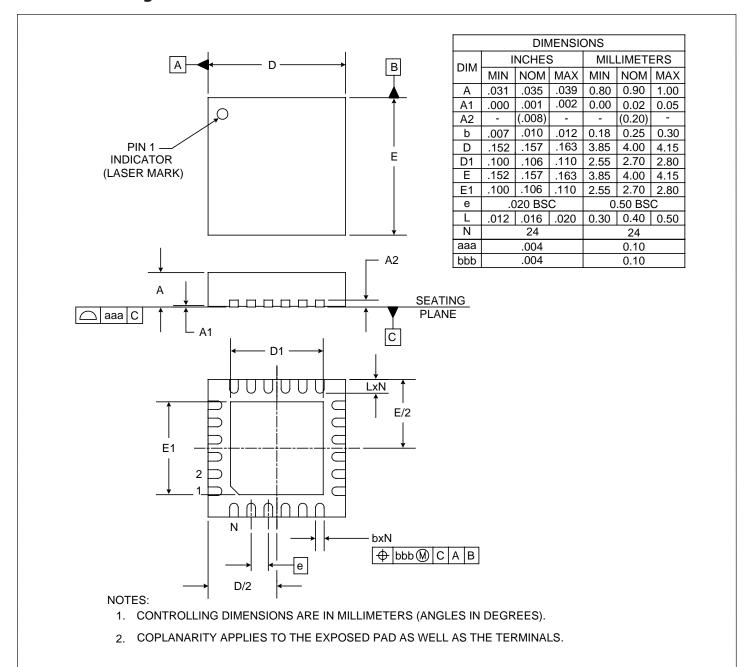

- 4x4x0.9 (mm) MLPQ package

- WEEE and RoHS compliant

# **Applications**

- Bluetooth headsets

- MP3 players

- Low cost mobile phones

# **Description**

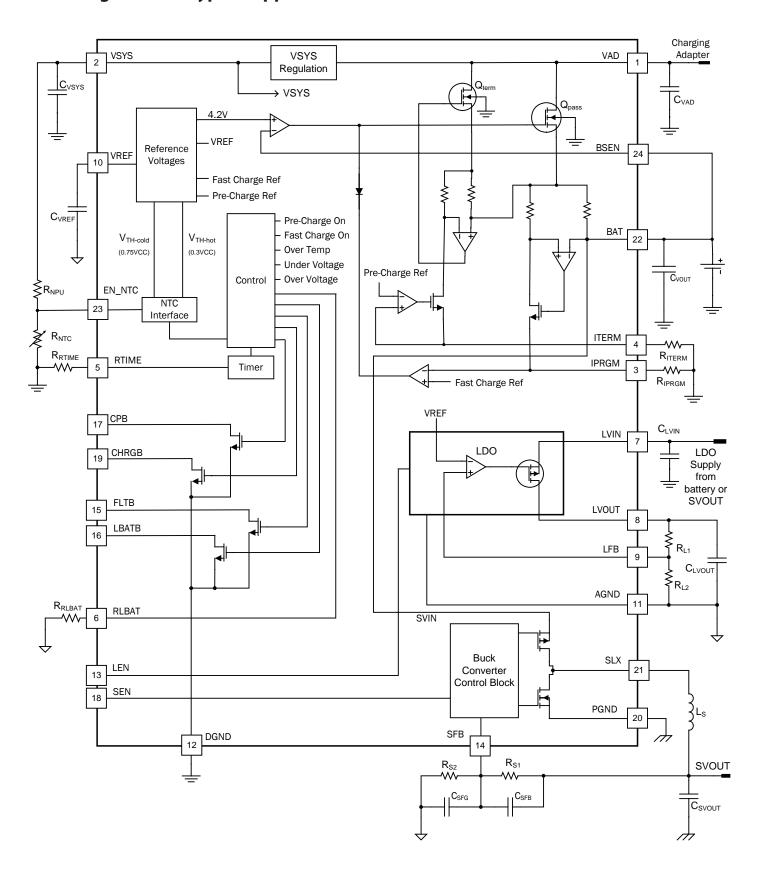

The SC908 is a complete power management system designed for use in Bluetooth wireless headsets, portable media players, and other battery-powered electronics where size is critical. Included are a full featured standalone Li-Ion battery charger with a programmable low-battery monitor, a low noise LDO regulator, and a DC-DC buck converter.

Battery charging features include programmable precharge, fast-charge, and termination current settings. Charge termination is controlled by a programmable timer and by a resistor that sets the termination current. The 28V max input voltage protects against hotplug overshoot and faulty adapters without additional protection circuitry. The battery voltage Kelvin sense input eliminates errors due to high charging currents. A battery thermistor interface disables charging when the battery temperature exceeds safe-to-charge limits.

The step-down switching regulator (buck converter) improves system efficiency and extends battery life. The LDO regulator can be powered directly from the battery or from the buck converter output when efficiency is critical. The fast-starting low noise LDO regulator is suitable for audio, RF, or general purpose regulation required by peripheral devices, such as a vibrating alert motor. The low battery detector warns when the battery level is below 3.3V, and when the battery has discharged below a lower programmable voltage limit.

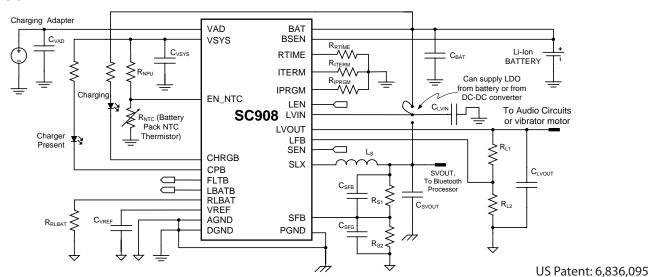

# **Typical Application Circuit**

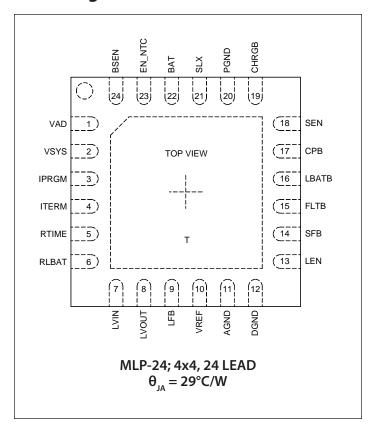

# **Pin Configuration**

# **Ordering Information**

| Device                      | Package          |

|-----------------------------|------------------|

| SC908MLTRT <sup>(1,2)</sup> | MLPQ-24          |

| SC908EVB                    | Evaluation Board |

#### Notes

- (1) Available in tape and reel only. A reel contains 3,000 devices.

- (2) Lead-free package only. Device is WEEE and RoHS compliant.

# **Marking Information**

# **Absolute Maximum Ratings**(1)

| VAD (V)0.3 to +28.0                                          |

|--------------------------------------------------------------|

| BAT, VSYS, CHRGB, FLTB, LBATB (V)0.3 to +5.5                 |

| CPB (V)0.3 to V <sub>SRC</sub> <sup>(2)</sup> + 0.3          |

| SLX, LVIN, LEN, SEN (V) $V_{BAT} + 0.3$                      |

| LVOUTV <sub>LVIN</sub> + 0.3                                 |

| AGND0.3 to +0.3                                              |

| PGND1.0 to +0.3                                              |

| Pin Voltage — All Other Pins (V)0.3 to +6.5                  |

| BAT Output Current (A)                                       |

| BAT Short Circuit Duration (s)Continuous                     |

| DC-DC Converter Output Current (mA) <sup>(3)</sup> 265, +180 |

| DC-DC Converter Output Current (mA) <sup>(4)</sup> ±600      |

| Total Power Dissipation (W)                                  |

| ESD Protection Level (kV) (5)                                |

|                                                              |

# **Recommended Operating Conditions**

| Ambient Temperature Range (°C)40 to +85                      |

|--------------------------------------------------------------|

| Charger Input Voltage Range (V)4.45 to 7.05                  |

| LDO Regulator Input Voltage Range (V)2.2 to $V_{\text{BAT}}$ |

| Switching Regulator Input Voltage (V)                        |

## **Thermal Information**

| Thermal Resistance, Junction to Ambient (°C/W) <sup>(6)</sup> 29 |

|------------------------------------------------------------------|

| Junction Temperature Range (°C)40 to +150                        |

| Storage Temperature Range (°C)65 to +150                         |

| IR Reflow Temperature (°C) +260                                  |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES:

- (1) All absolute maximum ratings are with respect to DGND unless otherwise noted.

- (2)  $V_{SRC} = \text{larger of } V_{BAT} \text{ and } V_{VSYS}$

- (3) Continuous

- (4) Peak

- (5) Tested according to JEDEC standard JESD22-A114-B.

- (6) Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

## **Electrical Characteristics** –

Test Conditions:  $V_{VAD} = 4.75V$  to 5.25 V;  $V_{BAT} = 3.7V$ ;  $V_{LEN} = V_{VAD}$ ; Typ values at 25°C; Min and Max at -40°C <  $T_A$  < 85°C, unless specified.

|                             | · · · · · · · · · · · · · · · · · · · |                                                                     | 1    |      |      |       |  |  |

|-----------------------------|---------------------------------------|---------------------------------------------------------------------|------|------|------|-------|--|--|

| Parameter                   | Symbol                                | Conditions                                                          | Min  | Тур  | Max  | Units |  |  |

| Charger                     |                                       |                                                                     |      |      |      |       |  |  |

|                             | VAD <sub>OP</sub> <sup>(1)</sup>      | Operating Voltage                                                   | 4.45 | 5    | 7.05 | V     |  |  |

|                             | VAD <sub>UVLO-R</sub>                 | UVLO Rising Threshold                                               | 4.05 | 4.25 | 4.45 | V     |  |  |

|                             | VAD <sub>UVLO-F</sub>                 | UVLO Falling Threshold                                              | 3.8  | 4    | 4.2  | V     |  |  |

| VAD Input Voltage           | VAD <sub>UVLO-H</sub>                 | UVLO Hysteresis<br>(VAD <sub>UVLO-R</sub> - VAD <sub>UVLO-F</sub> ) | 150  |      |      | mV    |  |  |

|                             | VAD <sub>OVP-R</sub>                  | OVP Rising Threshold                                                |      | 7.5  | 7.80 | ٧     |  |  |

|                             | VAD <sub>OVP-F</sub>                  | OVP Falling Threshold                                               | 7.05 | 7.3  |      | V     |  |  |

|                             | VAD <sub>OVP-H</sub>                  | OVP Hysteresis<br>(VAD <sub>OVP-R</sub> - VAD <sub>OVP-F</sub> )    | 50   |      |      | mV    |  |  |

| Battery Leakage Current (2) | lleak <sub>BAT</sub>                  | $V_{VAD} = V_{SEN} = V_{LEN} = 0V, V_{BAT} = 4.2V$                  |      | 0.1  | 2    | μΑ    |  |  |

| Parameter                                                   | Symbol                 | Conditions                                                                                                                                                                                   | Min   | Тур  | Max   | Units              |  |  |

|-------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|--------------------|--|--|

| Charger (continued)                                         | Charger (continued)    |                                                                                                                                                                                              |       |      |       |                    |  |  |

| Charging Adapter Operating Current                          | VAD <sub>ICCQ</sub>    | $\begin{aligned} V_{EN\_NTC} &= 0.5 \times V_{VSYS'} \ I_{CPB} = I_{CHRGB} = I_{FLTB} = \\ I_{LBATB} &= I_{ITERM} = I_{IPRGM} = 0 \text{mA}, \ V_{SEN} = V_{LEN} = 0 \text{V} \end{aligned}$ |       | 1.5  |       | mA                 |  |  |

| CV Regulation Voltage                                       | $V_{cv}$               | Measured at BSEN pin $20\text{mA} < I_{BAT} < 500\text{mA}$ $0^{\circ}\text{C} < T_{J} < 125^{\circ}\text{C}$                                                                                | 4.16  | 4.2  | 4.24  | V                  |  |  |

| Precharge Threshold (Rising)                                | $VT_{PreQ}$            | Measured at BSEN pin                                                                                                                                                                         | 2.7   | 2.8  | 2.9   | V                  |  |  |

| Recharge Threshold (Falling)                                | $VT_{ReQ}$             | V <sub>CV</sub> - V <sub>BSEN</sub>                                                                                                                                                          | 65    | 113  | 160   | mV                 |  |  |

| VSYS output voltage (3)                                     | V <sub>VSYS</sub>      | $V_{VAD} \ge 5V$ , $I_{VSYS} \le 5mA$                                                                                                                                                        |       | 4.7  |       | V                  |  |  |

| VSYS output current                                         | I <sub>VSYS</sub>      |                                                                                                                                                                                              |       |      | 5     | mA                 |  |  |

| ITERM Programming Resistor                                  | R <sub>ITERM</sub>     | Nominal 1%-tol Standard Value                                                                                                                                                                | 2.67  |      | 17.4  | kΩ                 |  |  |

| I <sub>BAT</sub> Pre-Charge Current                         | l <sub>PreQ</sub>      | $R_{ITERM} = 4.99k\Omega$ to GND                                                                                                                                                             | 27    | 39   | 52    | mA                 |  |  |

| I <sub>BAT</sub> Termination Current                        | I <sub>TERM</sub>      | $R_{ITERM} = 4.99k\Omega$ to GND                                                                                                                                                             | 27    | 39   | 52    | mA                 |  |  |

| IPRGM Programming Resistor                                  | R <sub>IPRGM</sub>     | Nominal 1%-tol Standard Value                                                                                                                                                                | 2.15  |      | 15.0  | kΩ                 |  |  |

| I <sub>BAT</sub> Fast-Charge Current                        | I <sub>FQ</sub>        | $R_{IPRGM} = 6.04k\Omega, V_{BAT} = 3.7V$                                                                                                                                                    | 167   | 173  | 179   | mA                 |  |  |

| VAD - BAT Dropout Voltage                                   | $V_{DO}$               | $I_{BAT} = 500 \text{mA}, 0^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                                                                                                                |       |      | 0.8   | V                  |  |  |

| IPRGM Regulated Voltage                                     | $V_{IPRGM}$            | $R_{IPRGM} = 6.04 k\Omega$ to GND                                                                                                                                                            | 1.45  | 1.5  | 1.55  | V                  |  |  |

| ITERM Regulated Voltage                                     | $V_{\text{ITERM}}$     | $R_{ITERM} = 4.99k\Omega$ to GND                                                                                                                                                             | 1.45  | 1.5  | 1.55  | V                  |  |  |

| RTIME Regulated Voltage                                     | V <sub>RTIME</sub>     | $R_{RTIME} = 37.4k\Omega$ to GND                                                                                                                                                             | 1.475 | 1.56 | 1.625 | V                  |  |  |

| Drocharge Fault Time Out                                    |                        | $R_{RTIME} = 37.4k\Omega$ to GND                                                                                                                                                             | 38    | 47   | 57    | mins               |  |  |

| Precharge Fault Time-Out                                    | t <sub>PreQF</sub>     | R <sub>RTIME</sub> connected to VSYS                                                                                                                                                         | 32    | 42   | 53    | mins               |  |  |

| Chausa Caranlata Tima Out                                   |                        | $R_{RTIME} = 37.4k\Omega$ to GND                                                                                                                                                             | 2.50  | 3.10 | 3.70  | hrs                |  |  |

| Charge Complete Time-Out                                    | t <sub>QComp</sub>     | R <sub>RTIME</sub> connected to VSYS                                                                                                                                                         | 2.10  | 2.67 | 3.50  | hrs                |  |  |

|                                                             | VT <sub>NTC_DIS</sub>  | Charger Disable/Reset (Falling)                                                                                                                                                              | 9     | 10   | 11.5  | %V <sub>VSYS</sub> |  |  |

| EN_NTC Thresholds                                           | $VT_{NTC\_HF}$         | NTC Hot (Falling)                                                                                                                                                                            | 27.5  | 30   | 31.5  | %V <sub>VSYS</sub> |  |  |

|                                                             | VT <sub>NTC_CR</sub>   | NTC Cold (Rising)                                                                                                                                                                            | 74    | 75   | 76.5  | %V <sub>VSYS</sub> |  |  |

| EN_NTC Hysteresis                                           | $VT_{NTC\_HYS}$        | V <sub>VAD</sub> = 5V                                                                                                                                                                        |       | 45   |       | mV                 |  |  |

| EN_NTC Disable/Reset Hold<br>Time                           | t <sub>NTC_DIS_H</sub> | Momentary disable resets charger                                                                                                                                                             | 500   |      |       | ns                 |  |  |

| Charger Over-Temperature Shut-<br>down Temperature (Rising) | $T_{CHRGR\_OT}$        | Hysteresis = 10°C typical                                                                                                                                                                    |       | 145  |       | °C                 |  |  |

| Parameter                                                              | Symbol                                   | Conditions                                                                                                                                                               | Min   | Тур              | Max   | Units |

|------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|-------|

| Core Functions (Excluding Charg                                        | jer)                                     |                                                                                                                                                                          |       |                  | •     | 1     |

| Core Circuits Quiescent Current (4)                                    | l <sub>Q-Core</sub>                      | $V_{VAD} = V_{SEN} = 0V,$ $V_{LEN} = V_{BAT} = 4.2V$                                                                                                                     |       | 100              |       | μΑ    |

| VREF Reference Voltage                                                 | $V_{_{\mathrm{VREF}}}$                   |                                                                                                                                                                          |       | 0.75             |       | V     |

| VREF Power Supply Rejection                                            | PSRR <sub>REF</sub>                      | $V_{BAT} = 3.7V \text{ with } 0.5V_{P-to-P} \text{ ripple,}$<br>f \le 10kHz, $C_{VREF} = 10$ nF                                                                          |       | 70               |       | dB    |

| VREF Reference Voltage Start-Up<br>Time (5, 10)                        | t <sub>su_ref</sub>                      | Delay from first of SEN high  LEN high, $V_{BAT} = 3.7V$ $C_{VREF} = 10nF$ VREF from 0V to 95% of final                                                                  |       | 0.4              |       | ms    |

| DC-DC Buck Converter                                                   |                                          |                                                                                                                                                                          |       |                  |       |       |

| Buck Converter Input Voltage                                           | $V_{\scriptscriptstyle{\sf SVIN}}$       | BAT pin is also the switching regulator supply input                                                                                                                     |       | V <sub>BAT</sub> |       | V     |

| Buck Converter Under-Voltage<br>Lockout Rising Threshold               | VT <sub>SUVLO-R</sub>                    |                                                                                                                                                                          |       |                  | 2.8   | V     |

| Buck Converter Under-Voltage<br>Lockout Falling Threshold              | $VT_{SUVLO-F}$                           |                                                                                                                                                                          | 2.55  |                  |       | V     |

| Buck Converter Under-Voltage<br>Lockout Hysteresis                     | VT <sub>suvlo-HYS</sub>                  |                                                                                                                                                                          |       | 84               |       | mV    |

| Buck Converter Quiescent<br>Current <sup>(2)</sup>                     | I <sub>BAT-Q</sub>                       | $V_{SEN} = V_{BAT'} I_{SVOUT} = 10 \text{mA}$<br>Low $I_{Q}$ mode of $P_{SAVE}$                                                                                          |       | 115              |       | μΑ    |

| Buck Converter Minimum<br>On-Time                                      | t <sub>son_min</sub>                     |                                                                                                                                                                          |       |                  | 60    | ns    |

| Buck Converter Maximum<br>Duty Cycle (10)                              | $SDC_{MAX}$                              |                                                                                                                                                                          | 92    |                  |       | %     |

| Buck Converter Program Output<br>Voltage Minimum (6,10)                | $V_{\text{SVOUT\_MIN}}$                  |                                                                                                                                                                          |       |                  | 1     | V     |

| Buck Converter Program Output<br>Voltage Maximum <sup>(6,7,8,10)</sup> | $V_{\scriptscriptstyle{\sf SVOUT\_MAX}}$ | $V_{BAT} \ge V_{SVOUT\_MAX}/SDC_{MAX} + 150mV$                                                                                                                           | 3     |                  |       | V     |

| Buck Converter Feedback<br>Regulation Voltage                          | $V_{SFB}$                                |                                                                                                                                                                          | 0.480 | 0.500            | 0.520 | V     |

| Buck Converter Output Voltage <sup>(6)</sup>                           | V <sub>svout</sub>                       | $\begin{aligned} V_{BAT} &= 3.7 \text{V, L} = 4.7 \mu \text{H} \\ I_{SVOUT} &= 100 \text{mA} \\ R_{S1} &= 340 \text{k}\Omega, R_{S2} = 100 \text{k}\Omega \end{aligned}$ |       | 2.2              |       | V     |

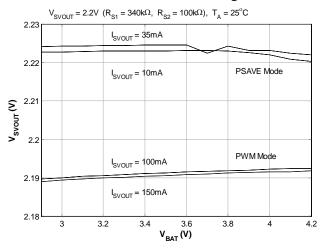

| Buck Converter<br>Line Regulation <sup>(6)</sup>                       | ${\sf V}_{\sf SVOUT\_LINE}$              | $2.8V \le V_{BAT} \le 4.5V$ $I_{SVOUT} = 100\text{mA}$ $R_{S1} = 340\text{k}\Omega, R_{S2} = 100\text{k}\Omega$                                                          | -0.3  |                  | 0.3   | %/V   |

| Buck Converter<br>Load Regulation <sup>(6)</sup>                       | $V_{SVOUT\_LOAD}$                        | $5\text{mA} \le I_{\text{SVOUT}} \le 150\text{mA}$ $V_{\text{BAT}} = 3.7V$ $R_{\text{S1}} = 340\text{k}\Omega, R_{\text{S2}} = 100\text{k}\Omega$                        |       | 0.002            |       | %/mA  |

| Parameter                                             | Symbol                   | Conditions                                                                                                                        | Min  | Тур                       | Max              | Units |  |

|-------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|---------------------------|------------------|-------|--|

| DC-DC Buck Converter (continued)                      |                          |                                                                                                                                   |      |                           |                  |       |  |

| Buck Converter P-Channel Peak<br>Current Limit        | I <sub>LIM_P</sub>       |                                                                                                                                   | 410  | 440                       | 470              | mA    |  |

| Buck Converter P-Channel<br>On-Resistance             | R <sub>DS(ON)P</sub>     | I <sub>svout</sub> = 150mA                                                                                                        |      | 0.75                      |                  | Ω     |  |

| Buck Converter N-channel<br>On-Resistance             | R <sub>DS(ON)N</sub>     | I <sub>svout</sub> = 150mA                                                                                                        |      | 1.05                      |                  | Ω     |  |

| Buck Converter<br>Oscillator Frequency                | f <sub>osc</sub>         |                                                                                                                                   | 0.85 | 1.00                      | 1.15             | MHz   |  |

| Buck Converter<br>Start-Up Time (5,10)                | t <sub>su-svout</sub>    | $I_{SVOUT} = 150 \text{mA}, V_{SVOUT} \text{ to } 95\%$ $V_{SVOUT} = 1V$ $V_{SVOUT} = 1.8V$ $V_{SVOUT} = 2.2V$ $V_{SVOUT} = 3.0V$ |      | 0.3<br>1.3<br>1.45<br>1.8 | 2                | ms    |  |

| Linear Low Drop-Out (LDO) Reg                         | ulator                   |                                                                                                                                   |      |                           |                  |       |  |

| LDO Input Voltage                                     | V <sub>LVIN</sub>        | $V_{BAT} \ge 2.8V$                                                                                                                | 2.2  |                           | V <sub>BAT</sub> | V     |  |

| LDO Under Voltage<br>Lockout Rising Threshold         | VT <sub>LUVLO-R</sub>    |                                                                                                                                   |      | 1.95                      | 2.05             | V     |  |

| LDO Under Voltage<br>Lockout Falling Threshold        | VT <sub>LUVLO-F</sub>    |                                                                                                                                   | 1.75 | 1.85                      |                  | V     |  |

| LDO Under Voltage<br>Lockout Hysteresis               | VT <sub>LUVLO-HYS</sub>  |                                                                                                                                   |      | 120                       |                  | mV    |  |

| LDO Nominal Output<br>Voltage Minimum <sup>(10)</sup> | V <sub>LVOUT_MIN</sub>   | $V_{LVIN} > V_{LVOUT} + 300 mV$                                                                                                   |      |                           | 1.5              | V     |  |

| LDO Nominal Output<br>Voltage Maximum <sup>(10)</sup> | V <sub>LOUT_MAX</sub>    | $V_{LVIN} > V_{LVOUT} + 300 mV$                                                                                                   | 3.3  |                           |                  | V     |  |

| LDO Feedback<br>Regulation Voltage                    | V <sub>LFB</sub>         | $V_{LVIN} = 3.7V$ , $I_{LVOUT} = 1 \text{mA}$                                                                                     |      | 0.75                      |                  | V     |  |

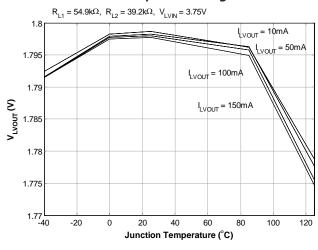

| LDO Output Voltage                                    | V <sub>LVOUT</sub>       | $R_{L1} = 54.9k\Omega, R_{L2} = 39.2k\Omega$<br>$V_{LVIN} = 3.7V, I_{LVOUT} = 1 mA$                                               | 1.73 | 1.8                       | 1.85             | V     |  |

| LDO Disamout Valta sa                                 | V                        | V <sub>LVOUT</sub> = 2.2V, I <sub>LVOUT</sub> = 100mA                                                                             |      | 115                       | 200              | mV    |  |

| LDO Dropout Voltage                                   | V <sub>L_DO</sub>        | $V_{LVOUT} = 3.0V$ , $I_{LVOUT} = 150$ mA                                                                                         |      | 130                       | 225              | mV    |  |

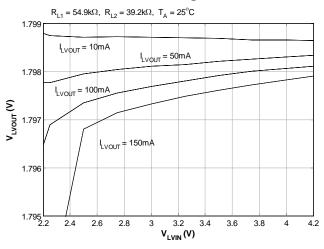

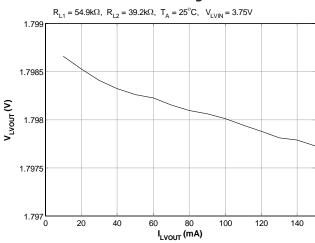

| LDO Load Regulation                                   | ۸۷                       | $R_{L1} = 54.9k\Omega, R_{L2} = 39.2k\Omega$<br>$(V_{LVOUT} = 1.8V), V_{LVIN} = 2.2V$<br>$1mA \le I_{LVOUT} \le 100mA$            | -10  |                           | 10               | mV    |  |

| (with respect to 1mA load) (9)                        | ΔV <sub>LVOUT_LOAD</sub> | $R_{L1} = 54.9k\Omega, R_{L2} = 39.2k\Omega$<br>$(V_{LVOUT} = 1.8V), V_{LVIN} = 3.7V$<br>$1mA \le I_{LVOUT} \le 150mA$            | -10  |                           | 10               | mV    |  |

| Parameter                                                  | Symbol                                          | Conditions                                                                                                              | Min  | Тур  | Max  | Units             |  |  |

|------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------|--|--|

| Linear Low Drop-Out (LDO) Reg                              | Linear Low Drop-Out (LDO) Regulator (continued) |                                                                                                                         |      |      |      |                   |  |  |

| LDO Line Regulation <sup>(9)</sup>                         | $\Delta V_{	ext{LVOUT\_LINE}}$                  | $2.2V \le V_{LVIN} \le 4.2V$ referenced to 3.7V, $I_{LVOUT} = 1$ mA, RL1 = 54.9k $\Omega$ , RL2 = 39.2k $\Omega$        | -5   |      | 5    | mV                |  |  |

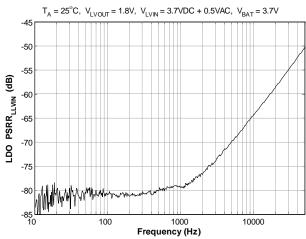

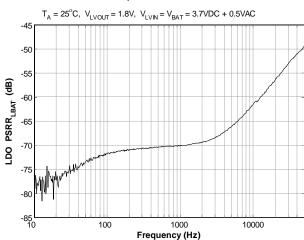

| LDO LVOUT/LVIN Power Supply<br>Rejection Ratio             | PSRR <sub>LLVIN</sub>                           | $V_{LVIN} = 3.7VDC$ with 0.5V P-to-P Ripple, $f \le 10kHz$ , $V_{BAT} = 3.7VDC$ $V_{LVOUT} = 1.8V$ , $I_{LVOUT} = 30mA$ |      | 60   |      | dB                |  |  |

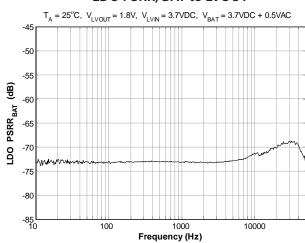

| LDO LVOUT/(BAT and LVIN)<br>Power Supply Rejection Ratio   | PSRR <sub>LBAT</sub>                            | $V_{LVIN} = V_{BAT} = 3.7VDC$ with 0.5V P-to-P Ripple, $f \le 10kHz$ $V_{LVOUT} = 1.8V$ , $I_{LVOUT} = 30mA$            |      | 60   |      | dB                |  |  |

| LDO Output Noise Voltage (9)                               | $V_{L_{NOISE}}$                                 | $10Hz \le f \le 100kHz$ $C_{LVOUT} = 1\mu F, V_{LVOUT} = 3.0V$ $V_{LVIN} = 3.7V, I_{LVOUT} = 50mA$                      |      | 50   |      | μV <sub>RMS</sub> |  |  |

| LDO Quiescent Current $(I_{LVIN} - I_{LVOUT})^{(4)}$       | I <sub>LQ</sub>                                 | $V_{LVIN} = V_{LEN} = V_{BAT} = 4.2V,$<br>$V_{VAD} = 0V, I_{LVOUT} = 1 \text{ mA}$                                      |      | 91   |      | μА                |  |  |

| LDO Current Limit                                          | I <sub>L_LIM</sub>                              | $V_{LVOUT} = 0V, V_{LEN} = V_{BAT}$                                                                                     | 300  | 380  | 450  | mA                |  |  |

| LDO Charle Har Time a (5.10)                               |                                                 | Time from LEN (with $V_{SEN} = V_{BAT'}$<br>disregard $t_{SU\_REF}$ ),<br>$V_{LVOUT}$ from 0V to 95% of final           |      | 0.1  |      | ms                |  |  |

| LDO Start-Up Time (5, 10)                                  | t <sub>su-lvout</sub>                           | Time from LEN  (with $V_{VAD} = V_{SEN} = 0$ , $t_{SU\_REF}$ dominates) $V_{LVOUT}$ from 0V to 95% of final             |      | 0    |      | ms                |  |  |

| LDO Turn-Off Time                                          | t <sub>TO-LVOUT</sub>                           | Time from LEN = 0, $V_{LVOUT}$ from 100% to 10% of regulation                                                           |      | 0.5  |      | ms                |  |  |

| Battery Voltage Detector                                   |                                                 |                                                                                                                         |      |      |      |                   |  |  |

| Battery Detector Minimum<br>Operating Voltage              | V <sub>DET_MINOP</sub>                          |                                                                                                                         |      |      | 2.3  | V                 |  |  |

| Battery Detector Maximum<br>Operating Voltage              | V <sub>DET_MAXOP</sub>                          |                                                                                                                         | 4.5  |      |      | V                 |  |  |

| Battery Detector Voltage<br>Warning, Decreasing            | V <sub>WARN</sub>                               | $V_{DET\_MINOP} \le V_{Battery} \le V_{DET\_MAXOP}$                                                                     | 3.21 | 3.28 | 3.35 | V                 |  |  |

| Battery Detector Voltage Fault,<br>Decreasing              | V <sub>DET</sub>                                | $R_{RLBAT} = 309k\Omega$                                                                                                |      | 2.92 |      | V                 |  |  |

| Battery Detector Threshold<br>Hysteresis, Warning or Fault | V <sub>DET_HYS</sub>                            | $V_{DET\_MINOP} \le V_{Battery} \le V_{DET\_MAXOP}$                                                                     | 150  | 200  | 250  | mV                |  |  |

| Parameter                                            | Symbol                                | Conditions                                                                  | Min | Тур | Max | Units |  |  |  |

|------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|--|--|--|

| Logic Control Inputs & Status Ou                     | Logic Control Inputs & Status Outputs |                                                                             |     |     |     |       |  |  |  |

| Battery Detector Sense Leakage (BSEN Current)        | I <sub>BSEN_DET</sub>                 | $V_{VAD} > VAD_{UVLO'}$ or SEN or LEN high,<br>$V_{BSEN} = 4.2V$            |     | 5   | 10  | μΑ    |  |  |  |

| Battery Detector Activation<br>Delay <sup>(10)</sup> | V <sub>DET_DEL</sub>                  | Time from first of LEN or SEN high until LBATB/FAULTB valid, $V_{VAD} = 0V$ |     | 70  |     | μs    |  |  |  |

| Logic Input Low                                      | V <sub>IL</sub>                       | LEN, SEN; V <sub>BAT</sub> = 2.7V                                           | 0.4 |     |     | V     |  |  |  |

| Logic Input High                                     | V <sub>IH</sub>                       | LEN, SEN; $V_{BAT} = 2.7V$                                                  |     |     | 1.5 | V     |  |  |  |

| Logic Input Current High                             | I <sub>IL</sub>                       | LEN, SEN; V <sub>BAT</sub> = 2.7V                                           |     |     | 1   | μΑ    |  |  |  |

| Logic Input Current Low                              | I <sub>IH</sub>                       | LEN, SEN; V <sub>BAT</sub> = 2.7V                                           |     |     | 1.5 | μΑ    |  |  |  |

| CPB, CHRGB, FLTB, LBATB                              | V <sub>OL</sub>                       | I <sub>SINK</sub> = 2mA                                                     |     |     | 0.5 | V     |  |  |  |

| Outputs                                              | I <sub>oh</sub>                       | $V = 5V (V_{VAD} = 8V \text{ for CPB})$                                     |     |     | 1   | μΑ    |  |  |  |

#### Notes:

- (1) VAD<sub>op</sub> is the "Maximum Vsupply" as defined in EIA/JEDEC Standard No. 78, paragraph 2.11.

- (2) The value of the buck converter disabled battery leakage current is included in the charger section battery leakage since it cannot be independently measured (because SVIN is tied to BAT internally). The buck converter contribution to this value is also included in the Buck Converter section for design guidance only.

- (3) VSYS regulation voltage assumes that  $V_{VAD}$  exceeds  $V_{VSYS}$  by the VSYS regulator dropout (typically 0.5V at 5mA, for a minimum regulator  $R_{DS} = 71\Omega$ ). If this condition is not met, then  $V_{VSYS} = V_{VAD}$  minus the VSYS regulator dropout.

- (4) I<sub>Q-Core</sub> is the supply current from the battery for common reference circuits into the BAT pin when either the buck converter or LDO or charger are enabled.

- (5)  $t_{SU\_REF}$  is the start-up time of the voltage reference buffer for both the DC-DC buck converter and the LDO, and should be added to the start-up time ( $t_{SU\_SVOUT}$  or  $t_{SU\_LVOUT}$  respectively) of the first regulator enabled. In the case of the LDO start-up with the switcher disabled, the LDO start-up time  $t_{SU\_LVOUT}$  is concurrent with the reference start-up time  $t_{SU\_REF}$  and so  $t_{SU\_LVOUT}$  is specified as typically zero.

- (6) SVOUT is the buck converter output node, which is the node at which the output inductor is connected to the load. It is the top of the feedback resistor divider network. See the Typical Application Circuit.

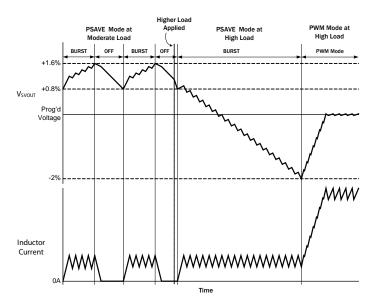

- (7) To guarantee positive load threshold hysteresis for PSAVE-to-PWM mode switching with SVOUT > 2.2V, contact your Semtech representative for application assistance.

- (8) If  $V_{BAT} < V_{SVOUT\_Max} / SDC_{MAX} + 150$ mV, then the maximum output setting is  $V_{BAT} \times SDC_{MAX} + 150$ mV. Higher output voltage settings are feasible, but are subject to load-dependent dropout.

- (9) Specified with  $V_{BAT} = V_{LVIN}$ .

- (10) Guaranteed by design.

# **Typical Characteristics**

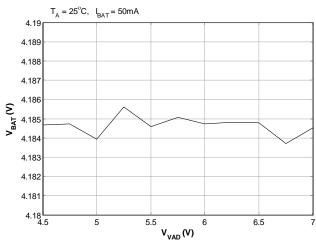

# **Charger CV Line Regulation**

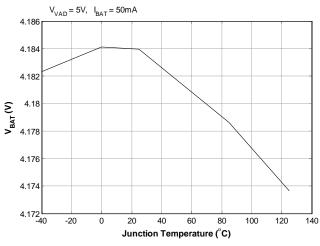

# **Charger CV Temperature Regulation**

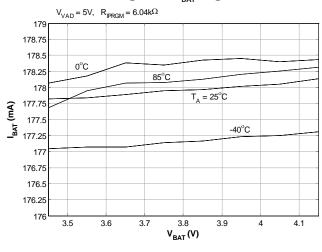

# Charger CC V<sub>BAT</sub> Regulation

# **Charger CV Load Regulation**

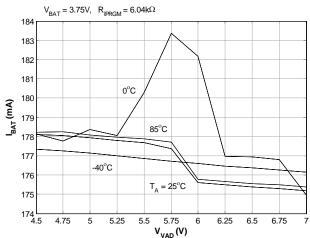

# **Charger CC Line Regulation**

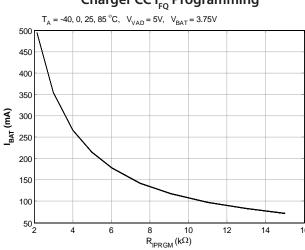

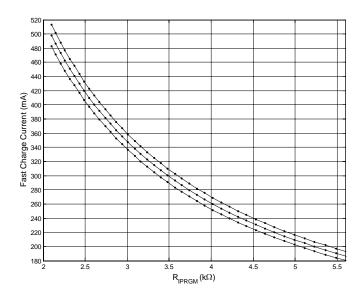

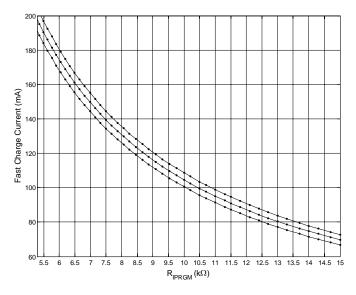

# ${\sf Charger}\,{\sf CC}\,{\sf I}_{\sf FQ}\,{\sf Programming}$

# **Typical Characteristics (continued)**

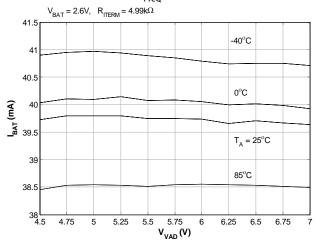

# ${\it Charger}\ {\it I}_{{\it PreQ}}\ {\it Line}\ {\it Regulation}$

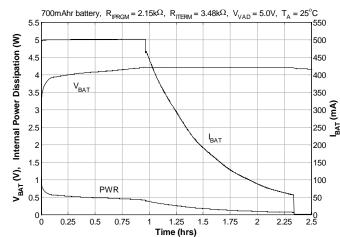

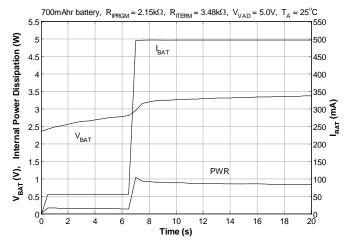

# **Charging Cycle Battery Voltage and Current**

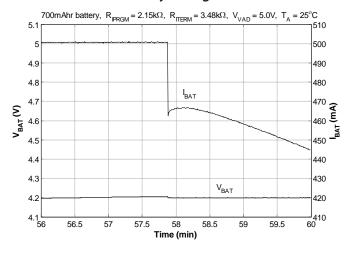

## **CC-to-CV Battery Voltage and Current**

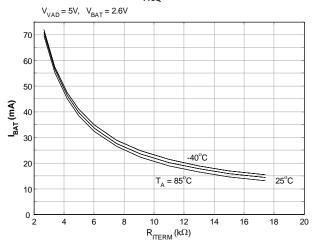

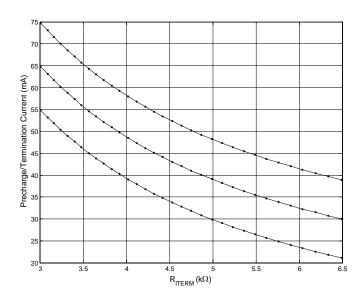

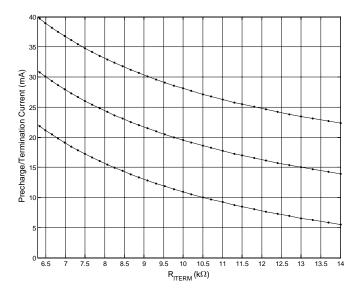

# **Charger I**<sub>PreQ</sub> **Programming**

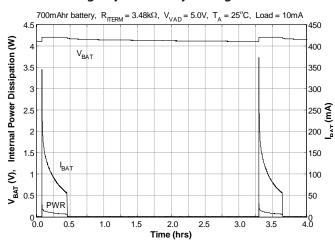

# **Pre-Charging Battery Voltage and Current**

## **Re-Charge Cycle Battery Voltage and Current**

## **LDO Line Regulation**

# **LDO Load Regulation**

## **LDO Temperature Regulation**

## LDO PSRR, LVIN to LVOUT

# LDO PSRR, BAT to LVOUT

# LDO PSRR, LVIN and BAT to LVOUT

# **Typical Characteristics (continued)**

## DC/DC Converter Line Regulation

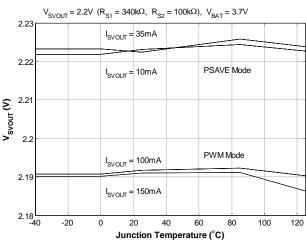

# DC/DC Converter Temperature Regulation

#### DC/DC Converter Efficiency Detail

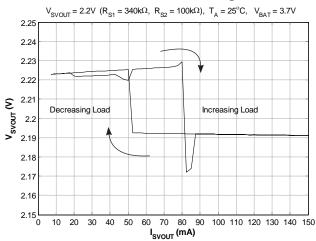

## **DC/DC Converter Load Regulation**

# **DC/DC Converter Efficiency**

# DC/DC Converter Efficiency — Low Loads

# **Pin Descriptions**

| Pin # | Pin Name    | Pin Function                                                                                                                                                                                                                                      |

|-------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VAD         | Charger input pin                                                                                                                                                                                                                                 |

| 2     | VSYS        | Adapter input internal-regulation node which also serves as supply for EN_NTC, RTIME, and all input-referenced (vs. battery-referenced or regulated output-referenced) pull-ups; load must not exceed 5mA.                                        |

| 3     | IPRGM       | Pin for setting constant current charging current — connect resistor to ground to set current.                                                                                                                                                    |

| 4     | ITERM       | Pin for setting termination and precharge current — connect resistor to ground to set current.                                                                                                                                                    |

| 5     | RTIME       | Charge timer pin — connect a resistor to ground to set timer, ground to disable the timer. Timer enabled with internally programmed default time is selected with RTIME tied to VSYS.                                                             |

| 6     | RLBAT       | Resistor is connected to ground to set Low Battery voltage threshold.                                                                                                                                                                             |

| 7     | LVIN        | LDO voltage input — can be connected to either the battery supply (BAT) or the switching regulator output (SVOUT). No other connections are permitted.                                                                                            |

| 8     | LVOUT       | LDO voltage output                                                                                                                                                                                                                                |

| 9     | LFB         | LDO feedback voltage input                                                                                                                                                                                                                        |

| 10    | VREF        | Bandgap reference bypass pin — connected to a 10nF capacitor to analog ground. No other connections are permitted.                                                                                                                                |

| 11    | AGND        | Analog ground pin — refer to grounding considerations in application section.                                                                                                                                                                     |

| 12    | DGND        | Digital ground pin — refer to grounding considerations in application section.                                                                                                                                                                    |

| 13    | LEN         | LDO enable pin — active high                                                                                                                                                                                                                      |

| 14    | SFB         | DC-DC converter feedback input — connect voltage divider from output to this pin to set output voltage.                                                                                                                                           |

| 15    | FLTB        | Charging Fault indicator — open drain output is active low when a charging fault has occurred. Also, together with LBATB, indicates when battery discharges below a programmable voltage set by RLBAT resistor.                                   |

| 16    | LBATB       | Low Battery indicator — open drain output is active low when battery discharges below 3.3V, and, together with LBATB, indicates when battery discharges below a programmable voltage set by RLBAT resistor.                                       |

| 17    | СРВ         | Charger Present indicator — open drain output is active low when a valid VAD input voltage is present.                                                                                                                                            |

| 18    | SEN         | DC-DC converter enable pin — active high                                                                                                                                                                                                          |

| 19    | CHRGB       | Charging-In-Progress indicator — open drain output is active low when charging until charging current drops below the programmed termination current, or until charging is disabled by charge timeout or EN_NTC disable or NTC temperature fault. |

| 20    | PGND        | DC-DC converter power ground pin — No other connection is permitted.                                                                                                                                                                              |

| 21    | SLX         | DC-DC converter output — connect to an inductor between this point and SVOUT (the DC-DC converter load connection).                                                                                                                               |

| 22    | BAT         | Charger output pin, also DC-DC converter input pin — connect to the positive battery terminal.                                                                                                                                                    |

| 23    | EN_NTC      | NTC thermistor input — charger is enabled if voltage is between $0.3 \times VSYS$ and $0.75 \times VSYS$ . Charger is disabled if voltage is below 1V. Battery temperature fault otherwise.                                                       |

| 24    | BSEN        | Battery Kelvin sense pin — independent connection is tied directly to the battery positive terminal.                                                                                                                                              |

| Т     | Thermal Pad | Connect to ground plane with thermal vias directly under pad.                                                                                                                                                                                     |

# **Block Diagram With Typical Application Circuit**

# **Applications Information**

## **Charger Operation**

The SC908 Li-lon battery charger can be configured independently with respect to fast-charge, termination current, and timing. The charging and battery voltage status are indicated by the four status outputs.

A charge cycle is initiated when the power adapter is connected to the device and the SC908 VAD pin voltage is between the Under-Voltage LockOut (UVLO) rising threshold and the input Over Voltage Protection (OVP) threshold. If the battery voltage is less than the pre-charge threshold, the output current is regulated to the programmed precharge current. When the pre-charge threshold voltage is exceeded, the fast-charge Constant Current (CC) mode begins, with the charge current rising to the programmed fast-charge current in three soft-start current steps. The charger enters the Constant Voltage (CV) mode when the battery voltage rises to its final value (V<sub>CV</sub>), typically 4.2V. In the CV mode the BAT voltage is regulated to V<sub>CV</sub> and as the battery continues to charge it accepts decreasing current. The CHRGB output turns off when IRAT drops below the programmed termination current. If the charge timer is active, the battery is held in the CV charge mode until the timer cycle ends. The charger then enters the monitor mode, where the output remains off until the voltage at BAT drops by  $VT_{ReO'}$  and a new charge cycle is initiated. If the charge timer is disabled, the monitor mode is immediately entered upon charge termination.

#### **Pre-Charge Mode**

The pre-charge mode is automatically entered when the battery voltage is below the pre-charge threshold voltage, which preconditions the battery for fast charging. The pre-charge current value is set by the resistor on the ITERM pin, and is programmable from 14mA to 65mA. The pre-charge current is determined by

$$I_{PreQ} = \frac{V_{ITERM\_Typ}}{R_{ITERM}} \times 130$$

where  $V_{ITERM\_Typ}$  designates the typical value of  $V_{ITERM}$ . (See the Termination Current section for precharge current accuracy.) When the timer is enabled, there is a maximum allowed pre-charge duration. If the pre-charge time exceeds 25% of the total charge cycle, the charger will turn off due to a pre-charge fault. This fault is cleared

when VAD is cycled off and on, or when the EN\_NTC pin is forced low to disable the charger.

# **Fast-Charge Constant Current Mode**

The fast-charge CC mode is active when the battery voltage is above  $VT_{PreQ}$  and less than  $V_{CV}$ . The current can be set to a maximum of 0.5A and is selected by the program resistor on the IPRGM pin. The voltage on this pin represents the charger output current. This allows the charging current to be measured by sensing the IPRGM pin voltage using a general purpose Analog-to-Digital Converter (ADC) and the host microporocessor. The fast-charge current is determined by

$$I_{FQ} = \frac{V_{IPRGM\_Typ}}{R_{IPRGM}} \times 697$$

Excellent fast-charge current accuracy is obtained by the use of a patented polarity-switched current sense amplifier (US Patent 6,836,095). This nullifies current measurement offset errors, leaving only a small gain error. The range of expected fast-charge output current versus programming resistance  $R_{IPRGM}$  is shown in Figures 1a and 1b.

Figure 1a — Fast-charge Current Variation vs. IPRGM Resistance, Low Resistance Range

Figure 1b — Fast-charge Current Variation vs. IPRGM Resistance, High Resistance Range

The figures show the nominal current versus nominal R<sub>IPRGM</sub> resistance as the center plot and two theoretical limit plots indicating maximum and minimum current versus nominal programming resistance. These plots are derived from models of the expected worst-case contribution of error sources depending on programmed current. The current range includes the uncertainty due to 1% tolerance resistors. The dots on each plot indicate the currents obtained with standard value 1% tolerance resistors. The figures show low and high resistance ranges.

#### **Termination Current**

When the battery voltage reaches  $V_{\text{CV}}$ , the SC908 transitions from constant current mode to constant voltage mode. As the output holds the voltage measured at the BSEN pin constant, the current through the battery will decrease as the battery becomes fully charged. CHRGB is disabled when the output current drops below the programmed termination current. If the timer is enabled, the output will continue to float-charge in CV mode until the charge timer expires. If the timer is disabled, the output will turn off as soon as the termination current level is reached. The termination current is determined by

$$I_{\text{TERM}} = I_{\text{Pr\,eQ}} = \frac{V_{\text{ITERM\_Typ}}}{R_{\text{ITERM}}} \times 130$$

Termination current can be programmed from 14mA to 65mA, and must be less than  $I_{FO}$  for correct operation of the charge cycle. Pre-charge and termination current regulation accuracy is dominated by offset error. The range of expected pre-charge output current and termination threshold current versus programming resistance  $R_{\text{ITERM}}$  is shown in Figures 2a and 2b. The figures show the nominal pre-charge and termination current versus nominal resistance as the center plot. Two theoretical limit plots indicate maximum and minimum current versus nominal programming resistance. These plots are derived from models of the expected worst-case contribution of error sources depending on programmed current. The current range includes the uncertainty due to 1% tolerance resistors. The dots on each plot indicate the currents obtained with standard value 1% tolerance resistors. The figures show low and high resistance ranges.

A sufficient separation between  $I_{FQ}$  and  $I_{TERM}$  must be maintained to ensure proper operation of the constant current regulator and charge termination detector.  $R_{IPRGM}$  and  $R_{ITERM}$  must be chosen to nominally satisfy

$$I_{FO} > I_{TERM} + 90 \text{mA}$$

Figure 2a — Pre-charge and Termination Current Variation vs. ITERM Resistance, Low Resistance Range

Figure 2b — Pre-charge and Termination Current Variation vs. ITERM Resistance, High Resistance Range

# **Charge Timer**

The timer provides over-charging protection in the event of a faulty battery and maximizes charging capacity. The RTIME pin is connected to VSYS to select the internal (default) time duration of three hours, and to GND to disable the timer. Connecting a resistor between RTIME and GND will program the Charge Complete Time-Out, in hours, according to the equation

$$t_{QComp} = \frac{R_{RTIME}}{3.334} \times \frac{1}{3600}$$

The timer is programmable over the range of 2 to 6 hours. The output is automatically turned off when the charge timer cycle ends.

If the charge cycle remains in precharge for longer than one fourth of the Charge Complete Time-Out period, a charging fault is detected and the charger turns off. The Precharge Fault Time-Out period, in minutes, is

$$t_{\text{PreQF}} = \frac{t_{\text{QComp}}}{4} \times 60$$

#### **Monitor Mode**

When a charge cycle is complete (termination if the timer is disabled, charge timeout if the timer is enabled), the output turns off and the device enters monitor mode. If

the battery voltage falls below the recharge threshold  $(V_{CV} - V_{ReQ})$ , the charger will clear the charge timer and initiate a charge cycle. The status of the charger output as a function of the Charge Complete timer status and  $I_{BAT}$  is shown in Table 1.

Table 1 — Charger Output Status

| Timer       | lout                       | Output State |

|-------------|----------------------------|--------------|

| t < Timeout | N/A                        | On           |

| t > Timeout | N/A                        | Off          |

| Disabled    | < I <sub>termination</sub> | Off          |

#### **Remote Kelvin Sensing at the Battery**

The BSEN pin provides for Kelvin sensing of the battery positive terminal voltage. This prevents feedback error due to charging, battery load, and switching regulator input currents flowing over resistive PCB traces.

Optimal PCB layout routes the BSEN trace directly to the battery positive terminal connection on the PCB to achieve the most accurate sensing of battery cell voltage. Connecting BSEN to BAT directly at the SC908 will introduce battery voltage measurement error that can cause an improper transition from CC to CV regulation, lengthening the charge time. This error could also raise or lower the final battery voltage, and may alter the final state-of-charge.

#### **EN NTC Interface**

The EN\_NTC pin is the interface to a battery pack temperature sensing Negative Temperature Coefficient (NTC) thermistor, which can be used to suspend charging if the battery pack temperature is outside of a safe-to-charge range. It is also the charger-disable input. The typical EN\_NTC network is a fixed resistor from VSYS to the EN\_NTC pin, and the battery pack EN\_NTC thermistor from the EN\_NTC pin to ground. In this configuration, an increasing battery temperature produces a decreasing NTC pin voltage.

When  $V_{\text{EN\_NTC}}$  is greater than the high (cold) threshold or less than the low (hot) threshold, the charge cycle is suspended by turning off the output. This suspends but does not reset the charge timer, and indicates a fault on the FLTB pin. Hysteresis is included for both high and low

NTC thresholds to avoid chatter at the NTC fault thresholds. When  $V_{\text{EN\_NTC}}$  returns to the valid range, the charge timer resumes and the charge cycle continues. The charge timer will expire when the output on-time exceeds the timer setting, regardless of how long it has been disabled due to an NTC fault.

Using the recommended NTC external network, the EN\_NTC pin voltage and the internal hot and cold NTC thresholds are all ratios of  $V_{vsys'}$  rather than absolute voltages. This ensures that the hot and cold OK-to-charge thresholds are insensitive to the VSYS pin output voltage. The ratiometric thresholds are given by the parameters  $RT_{NTCH}$  and  $RT_{NTCC}$ . EN\_NTC pin voltage  $V_{EN_NTC}$  between  $RT_{NTCH} \times V_{vsys}$  and  $RT_{NTCC} \times V_{vsys}$  enables charging. When  $V_{EN_NTC}$  is outside this range, charging is suspended and the FLTB output is asserted (pulled low).

When  $V_{EN\_NTC} < VT_{NTCDIS}$  (nominally 0.6V), the SC908 charger is disabled. The EN\_NTC pin can be pulled to ground by an external n-channel FET or microprocessor GPIO to asnychronously disable or reset the device. When  $V_{EN\_NTC} < VT_{NTC\_DIS}$ , the charger is turned off, the charge timer is reset, and the CHRGB status output is turned off. While disabled, the VAD input UVLO and OVP threshold detectors remain active, and the CPB pin continues to indicate whether the VAD input voltage is valid for charging.

The response of the SC908 to an EN\_NTC pin voltage above the high threshold or below the low threshold (but above VT<sub>NTCDIS</sub>) is the same. Therefore the EN\_NTC network can be configured with the battery pack thermistor between EN\_NTC and VSYS, and a fixed resistor between EN\_NTC and ground. This configuration may be used to reset the charge timer (and the CHRGB output) when the battery pack is removed; the fixed resistor pulls the NTC pin to ground to disable the charger without indicating a fault.

# **NTC Design Example**

This example uses the conventional NTC network configuration shown in the block diagram. A fixed resistor ( $R_{NPU}$ ) is connected between EN\_NTC and VSYS, and a battery NTC thermistor ( $R_{NTC}$ ) is connected between the EN\_NTC pin and ground. The battery temperature range over which charging is permitted is from 0°C to 40°C. The data-

sheet for the proposed NTC thermistor, the Mitsubishi TH11-3T223F, indicates that  $R_{\text{NTC}}=11.93 k\Omega$  at  $40^{\circ}\text{C}$ , and  $R_{\text{NTC}}=69.41 k\Omega$  at  $0^{\circ}\text{C}$ , with a dissipation constant DC =  $3.0 \text{mW/}^{\circ}\text{C}$ . So  $R_{\text{HOT}}=11.93 k\Omega$  and  $R_{\text{COLD}}=69.41 k\Omega$ .

#### Step 1

Select  $R_{NPU}$  to obtain one of the desired temperature thresholds. This example will solve for the hot threshold for the normal (NTC thermistor to ground) configuration, then evaluate the cold threshold. Solve the NTC network voltage divider for  $R_{NPU}$  to place the NTC voltage at  $RT_{NTC\ HF} \times V_{VSYS}$  when  $R_{NTC} = R_{HOT}$ .

$$RT_{\text{NTC\_HF}} \times V_{\text{VSYS}} = \frac{V_{\text{VSYS}} \times R_{\text{HOT}}}{R_{\text{NPLI}} + R_{\text{HOT}}}$$

or, solving for R<sub>NPU</sub>,

$$R_{NPU} = \frac{1 - RT_{NTC\_HF}}{RT_{NTC\_HF}} \times R_{HOT}$$

Using RT<sub>NTC\_HF</sub> = 0.3, we obtain R<sub>NPU</sub> = 27.837k $\Omega$  exactly. The closest 1% standard nominal value is R<sub>NPU</sub> = 28.0k $\Omega$ .

#### Step 2

Evaluate the NTC network at the cold threshold. Compute the NTC network resistor divider voltage as a function of  $V_{vsys}$  at the desired cold threshold.

$$NTC_{COLD} = \frac{V_{VSYS} \times R_{COLD}}{R_{NPU} + R_{COLD}} = 0.7126 \times V_{VSYS}$$

The value 0.7126 should be close to the nominal value of  $RT_{NTC\_CR} = 0.75$ . To evaluate the significance of the discrepancy, an estimate of the actual cold threshold is obtained by evaluating the value of  $R_{NTC\_Cold\_Actual}$  that produces the nominal value of  $RT_{NTC\_CR} = 0.75$ .

$$RT_{\text{NTC\_CR}} = \frac{R_{\text{NTC\_Cold\_Actual}}}{R_{\text{NTC\_Cold\_Actual}} + R_{\text{NPU}}}$$

The solution shows  $R_{NTC\_Cold\_Actual} = 84.0k\Omega$ . Examination of the thermistor specification resistance versus temperature data indicates that the resulting actual cold threshold is approximately -4°C, compared to the target of 0°C.

#### Step 3

With the example thermistor, there is no choice of  $R_{NPU}$  that will yield the specified results at both hot and cold limits. A more sensitive thermistor, one with a wider percentage variation in resistance at the desired threshold temperatures, may provide a better solution. Steps 1 and 2 are repeated using other devices from the same vendor, seeking a closer match at the cold threshold.

The Mitsubishi TH11-4C153F was the final selection. Its characteristics are:  $R_{HOT}$  is 7.73k $\Omega$  (at 40°C),  $R_{COLD}$  is 53.94k $\Omega$  (at 0°C). Its dissipation constant DC = 3.0mW/°C. Step 1 yields  $R_{NPU}=18.2k\Omega$ , with the result that NTC $_{COLD}/V_{VSYS}=0.748\approx RT_{NTC\_CR'}$  NTC $_{HOT}/V_{VSYS}=0.298\approx RT_{NTC\_HF'}$ . The NTC resistances that give the exact cold and hot thresholds  $RT_{NTC\_CR}$  and  $RT_{NTC\_HF}$  are 54.6k $\Omega$  (which is  $R_{NTC}$  at approximately -0.5°C) and 7.80k $\Omega$  respectively, closely matching the resistance of the thermistor at the targeted threshold temperatures.

#### Step 4

Verify acceptable thermistor self heating. The dissipation constant is the power rating of the thermistor resulting in a 1°C self heating error. Since accuracy is important only at the thresholds, self heating is assessed only at 0°C and 40°C.

For  $V_{VSYS} = 4.6V$ , the 0°C NTC network current is

$$I_{NTC\_COLD} = V_{VSYS}/(R_{NPU} + R_{COLD}) = 63.8 \mu A$$

Power dissipation in the thermistor at this temperature is

$$P_{COLD} = R_{COLD} \times (I_{NTC\_COLD})^2 = 0.219 \text{mW}$$

The self heating error is

$$T_{\text{SH\_COLD}} = \frac{0.219 mW}{3^{mW}\!/\!c} = 0.073^{\circ}C$$

The 40°C NTC network current

$$I_{NTC\_HOT} = V_{VSYS}/(R_{NPU} + R_{HOT}) = 0.177 mA$$

Power dissipation in the thermistor at this temperature is

$$P_{HOT} = R_{HOT} \times (I_{NTC\_HOT})^2 = 0.243 \text{mW}$$

for self heating of approximately 0.081°C. The actual cold and hot thresholds will be 0.073 and 0.081 degrees lower than designed, respectively, which are negligible errors.

#### **Logical CC-to-CV Transition**

The SC908 differs from most monolithic linear single cell Li-lon chargers, which implement a linear transition from CC to CV regulation. The linear transition method uses two simultaneous feedback signals — output voltage and output current — to the closed-loop controller. When the output voltage is sufficiently below the CV regulation voltage, the influence of the voltage feedback is negligible and the output current is regulated to the desired current. As the battery voltage approaches the CV regulation voltage (4.2V), the voltage feedback signal begins to influence the control loop, which causes the output current to decrease although the output voltage has not reached 4.2V. The output voltage limit dominates the controller when the battery reaches 4.2V and eventually the controller is entirely in CV regulation. This system may be characterized as a dual-constraint (voltage and current) controller, with a soft transition between constraints. The soft transition effectively reduces the charge current below that which is permitted for a portion of the charge cycle, which increases charge time.

In the SC908, a logical transition is implemented from CC to CV to recover the charge current lost due to the soft transition. The controller regulates only current until the output voltage exceeds the transition threshold voltage. It then asynchronously switches to CV regulation. The transition voltage from CC to CV regulation is typically less than 10mV higher than the CV regulation voltage, which provides a sharp and clean transition free of chatter between regulation modes. The difference between the transition voltage and the regulation voltage is the CC/CV overshoot. While in CV regulation, the output current is limited to approximately 105% of the fast-charge current programmed by the IPRGM pin or the IPUSB pin, depending on the charging input selected, providing mode transition hysteresis. If the output current exceeds this current limit threshold, the controller asynchronously reverts to current regulation.

The logical transition from CC to CV results in the fastest possible charging cycle that is compliant with the speci-

fied current and voltage limits of the Li-lon cell. The output current is constant at the CC limit, then decreases abruptly when the output voltage steps from the overshoot voltage to the regulation voltage at the transition to CV control. This can be compared to voltage and current trajectories for other monolithic charger devices to show the softness of the linear crossover. This explains the charge-time advantage of the SC908 logical crossover method.

#### **Charger Protection Features**

The protection features are:

- Short Circuit Protection

- Over Current and Max Temperature Protection

- Input Overvoltage Protection

- Thermal Protection

#### **Short Circuit Protection**

The BAT output can tolerate an indefinite short circuit to ground. The current into a ground short will be equal to the precharge current.

The ITERM pin voltage prior to termination, and the IPRGM pin voltage while in CC mode, are regulated to 1.5V. Precharge current and termination current are proportional to the resulting ITERM current, and CC current is proportional to the resulting IPRGM current. High battery current is prevented by pinshort detectors on both programming pins. Pinshort detection asynchronously forces the charger into reset, turning off the output and clearing the charge timer. When the pinshort condition is removed, the charger begins normal operation automatically.

#### **Over Current and Max Temperature Protection**

Over current protection is provided in all modes of operation. When the device is in the charge mode the output is current-limited to either the programmed pre-charge current or the programmed fast charge current, depending on the voltage at the output. Junction over-temperature protection allows operation with maximum power dissipation by disabling the charger output current when the die temperature reaches the maximum operating temperature. This results in operation as a pulse charger in extreme power dissipation applications, delivering the maximum allowable output current while limiting the internal die temperature to a safe level.

#### **Input Over-Voltage Protection**

The VAD input is protected from adapter over-voltage to at least 28V above  $V_{DGND}$ . When  $V_{VAD}$  exceeds its OVP rising threshold VAD over the charger turns off its output while the charge timer continues to run, and the FLTB status indicator is asserted. When  $V_{VAD}$  subsequently falls below the VAD OVP falling threshold VAD over charging continues normally and FLTB is released.

#### **Thermal Protection**

The charger's internal over-temperature (OT) threshold is set to approximately 145°C. If the temperature exceeds this threshold prior to termination, the charger output is turned off. All other functions remain active, the charger logical state is preserved, and no fault is indicated. This allows thermal pulse charging in conditions of high power dissipation. Following termination, a charger OT condition will be indicated as a fault. Refer to the Indicator Flags subsection for more information.

A second high OT threshold is set to approximately 165°C. Should the die temperature exceed this threshold, all SC908 functions are disabled, and the status outputs indicate an exceptional condition fault. Refer to the Indicator Flags subsection for more information.

#### **Low Battery Detector Operation**

The low battery detector provides two low battery detection voltage thresholds: a fixed warning threshold and a resistor programmable detection (shutdown request) threshold. The low battery detector is enabled when either the buck converter is enabled (SEN is high) or the LDO regulator is enabled (LEN is high). The warning and shutdown request are provided by the status output pins FLTB and LBATB, as described in the Status Outputs subsection. When a charging adapter is present (V<sub>VAD</sub> > VAD<sub>UVLO-x</sub>), the FLTB and LBATB outputs are redefined to reflect the interaction of battery voltage and charging state.

The low battery detector warning threshold is fixed at  $3.28V \pm 70$ mV. The battery voltage fault threshold is programmable, with a resistor from the RLBAT pin to ground,

from 2.77V to 2.98V,  $\pm 10\%$ . The low battery fault threshold is set by the relationship

$$V_{DFT} = 3.9 \, \mu A \times R_{RIRAT} \times 2.42$$

$R_{RIBAT}$  must satisfy the condition

$$294k\Omega \le R_{\text{rirat}} \le 316k\Omega$$

Connect RLBAT to GND to disable the Low Battery Detector fault. The Low Battery Detector warning remains active.

#### **Status Outputs**

Four charger status outputs/LED drivers are provided.

- CPB (Charger Present)

- CHRGB (Charge Active)

- FLTB (Fault)

- LBATB (Low Battery Warning)

These outputs are active-low, open drain NMOS drivers capable of sinking up to 2mA each. The state of each, in various operating conditions, is defined in Tables 2, 3, and 4.

When the VAD voltage is below its UVLO threshold (no charging adapter is present), the CPB and CHRGB outputs are off (high impedance). The FLTB and LBATB outputs indicate the battery voltage as defined in Table 2.

When  $V_{VAD}$  is between its UVLO and OVP thresholds,  $V_{VAD}$  is valid to charge, and the CPB output is low indicating that a charging adapter is present.

The CHRGB output indicates the battery charging status. The charger-present status output states are described in Table 3. When pre-charging or when the output current is greater than  $I_{TERM}$ , CHRGB is low. The CHRGB output is latched off (high) when the output current becomes less than  $I_{TERM}$  during the charge cycle (and the battery voltage is above the recharge threshold,  $V_{BSEN} > V_{CV} - VT_{ReQ}$ ). This latch is reset when the battery enters a recharge cycle ( $V_{BSEN} < V_{CV} - VT_{ReQ}$ ), or for any NTC\_EN range other than OK-to-charge, or if  $V_{VAD}$  is above or below the VAD valid-to-charge range, allowing CHRGB to become active again when charging resumes.

When a charging adapter is present, the FLTB and LBATB outputs are redefined to reflect the interaction of the battery voltage, charging state, and charging faults, as described in Table 3. The FLTB output is activated when the device experiences a charger fault condition, or (together with LBATB output) when the battery voltage is less than the resistor-programmed low-battery detector threshold, V<sub>DET</sub>. This output can be used to notify the system controller of a fault condition when connected to an interrupt input, or it can be used like CPB and CHRGB to drive an indicator LED.

Table 2 — Status Output State, Charging Adapter Absent

| <b>.</b> | <b>D</b> : |                | <i>.</i> |                                        |                                                             | Cond                 | itions         |                         |                                      | Description                                                                                                                    |  |  |

|----------|------------|----------------|----------|----------------------------------------|-------------------------------------------------------------|----------------------|----------------|-------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| Statu    |            | Output<br>low) | State    | Adapter Voltage (mutually exclusive)   |                                                             |                      |                | ery Vol                 |                                      | and                                                                                                                            |  |  |

|          |            |                |          | 0                                      | AD <sub>OVP</sub>                                           |                      |                | V                       |                                      | Comments                                                                                                                       |  |  |

| CPB      | CHRGB      | FLTB           | LBATB    | V <sub>VAD</sub> < VAD <sub>UVLO</sub> | VAD <sub>UVLO</sub> < V <sub>VAD</sub> < VAD <sub>OVP</sub> | > VAD <sub>OVP</sub> | V SSEN Z VWARN | > V <sub>BSEN</sub> > V | V <sub>DET</sub> ≥ V <sub>BSEN</sub> | on = open drain output driver is active off = output is not active T = listed condition is true                                |  |  |

|          | )          |                | _        | V                                      | VAD <sub>UNLO</sub> <                                       | V                    | V              | Vwarn                   | >                                    | F = listed condition is true  F = listed condition is false  - = don't care  Blank = mutually exclusive with another condition |  |  |

| off      | off        | off            | off      | Т                                      |                                                             |                      | Т              |                         |                                      | No Charging Adapter, Battery Voltage Good                                                                                      |  |  |

| off      | off        | off            | on       | Т                                      |                                                             |                      |                | Т                       |                                      | No Charging Adapter, Low Battery Voltage Warning                                                                               |  |  |

| off      | off        | on             | on       | Т                                      |                                                             |                      |                |                         | Т                                    | No Charging Adapter, Low Battery Shutdown Request                                                                              |  |  |

The fault modes signaled by FLTB are:

- input over-voltage

- battery NTC temperature out of range

- pre-charge timeout.

- charger-only over-temperature (low OT, post-termination only)

When any of these conditions occurs the FLTB output goes low; otherwise it remains high impedance.

The LBATB output is active when the battery voltage is below the low-battery warning voltage,  $V_{WARN'}$  if the charging adapter is absent. If CPB and CHRGB outputs are both active, LBATB indicates when the charger is in precharge mode. However, LBATB and FLTB active together always

Table 3 — Status Output State, Charging Adapter Present

|     |                        |       |       | Conditions                                  |                                    |                       |                         |                                                      |                        |         |                      |                 |            |                       |              |                   |                    |                                                                                                                                                                                                |

|-----|------------------------|-------|-------|---------------------------------------------|------------------------------------|-----------------------|-------------------------|------------------------------------------------------|------------------------|---------|----------------------|-----------------|------------|-----------------------|--------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|