## **Multi-Channel AAL2 SAR**

Data Sheet

Features May 2006

- AAL2 Segmentation Reassembly device capable of simultaneously processing up to 1023 active CIDs (AAL2 Channel Identifier) and 1023 active VCs (Virtual Circuits)

- Support for up to 255 CIDs per VC. Maximum of 1023 CIDs

- Implements AAL2 Common Part Sub-layer (CPS) functions specified in ITU I.363.2

- Implements AAL2 Service Specific Convergence Sub-layer (SSCS) functions for G.711 PCM and G.726 ADPCM voice

- Supports 44-byte PCM or ADPCM packet profiles specified in AF-VMOA-0145.00

- CPS packet payload can support up to 64-bytes

- Supports over-subscription of 10:1

- H.100/H.110 compatible TDM bus for PCM or ADPCM data. Supports both master and slave TDM bus clock operation

#### **Ordering Information**

MT90502AG 456 PBGA Trays MT90502AG2 456 PBGA\*\* Trays \*\*Pb Free Tin/Silver/Copper

0 to +70°C

- TDM bus also supports compressed voice such as ITU G.723, G.728 and G.729 through HDLC encapsulation

- Three UTOPIA Level 1 ports configurable as PHY or ATM allowing for connection to an external AAL5 SAR processor, or for chaining multiple MT90502 devices. Ports A & B are configurable as a single 8-bit UTOPIA Level 2 PHY port with 5 ADDR lines

- UTOPIA module provides a cell switching function with a header translation

- Performs silence suppression for PCM and ADPCM

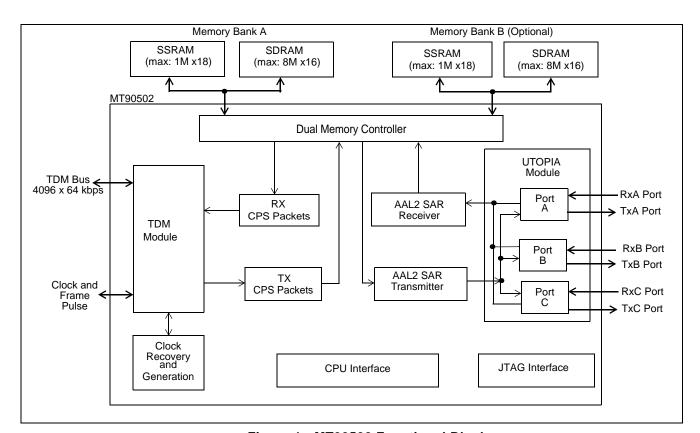

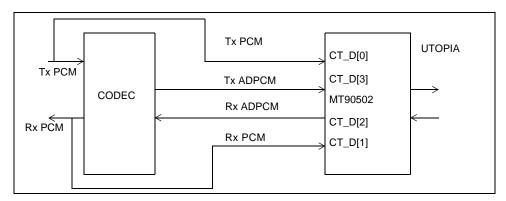

Figure 1 - MT90502 Functional Block

- Comfort noise generation

- · Capability to inject and recover CPS packets through the CPU host processor bus

- 8-bit or 16-bit microprocessor port, configurable to Motorola or Intel timing

- Single rail 3.3 V, 456 PBGA

- IEEE 1149 (JTAG) interface

## **Applications**

- Gateway

- ATM Edge Switch

- Next Generation Digital Loop Carrier

- Multiservice Switching Platform

- 3rd Generation Mobile System Equipment

## Description

The MT90502 Multi-Channel AAL2 SAR bridges a standard TDM (Time Division Multiplexed) backplane to a standard ATM (Asynchronous Transfer Mode) bus. The device provides the CPS (Common Part Sublayer) and SAR (Segmentation and Reassembly) engines. The MT90502 has the capability of simultaneously processing 1023 bi-directional CIDs (AAL2 Channel Identifiers) and 1023 bi-directional VCs (Virtual Circuits). The device can be connected directly to an H.110 compatible bus. The TDM bus consists of 32 bi-directional serial data streams operating at 2.048, 4.096, or 8.192 Mbits/s.

The MT90502 directly accepts G.711 PCM (Pulse Code Modulation) and G.726 ADPCM (Adaptive Differential Pulse Code Modulation) traffic for packetisation. For these two data formats, the device also implements silence suppression and comfort noise generation. To support other voice compression algorithms, the MT90502 connects directly to commercially available DSPs through synchronous serial data streams. The Variable Bit Rate (VBR) traffic is HDLC encapsulated and carried over the serial data streams.

The interface to the ATM domain is provided by three UTOPIA Level 1 ports (Ports A, B, and C). All three of the UTOPIA ports can operate in ATM (master) or PHY (slave) mode. Ports A and B combined, architects a compliant UTOPIA Level 2 Multi-PHY port. The MT90502 provides the capability of routing ATM cells to different UTOPIA interfaces, SAR engine or CPU. This feature can be used to connect another MT90502 (to support up to 2046 CID channels or 2046 phone calls) and/or to connect an external AAL1 and/or AAL5 SAR.

# **Table of Contents**

| 1.0 | Pin-out                                         |      |

|-----|-------------------------------------------------|------|

|     | 1.1 Pin Description Tables                      | . 14 |

| 2.0 | Functional Description                          | . 21 |

|     | 2.1 CPU Interface                               |      |

|     | 2.1.1 CPU Interrupts                            | . 21 |

|     | 2.1.1.1 Example Interrupt Flow                  | .21  |

|     | 2.1.2 Intel/Motorola Interface                  |      |

|     | 2.1.2.1 Extended Indirect Accessing             | . 24 |

|     | 2.1.2.2 Extended Direct Accessing               |      |

|     | 2.1.3 MT90502 Reset Procedure                   |      |

|     | 2.2 TDM Transmission                            | . 26 |

|     | 2.2.1 Low-Latency Loopback Channels             | . 28 |

|     | 2.2.2 Treatment of PCM/ADPCM Data               | . 28 |

|     | 2.2.2.1 CPS-Packet Length                       | .30  |

|     | 2.2.2.2 TDM Data Formats                        | . 30 |

|     | 2.2.2.3 Phase Alignment                         | . 36 |

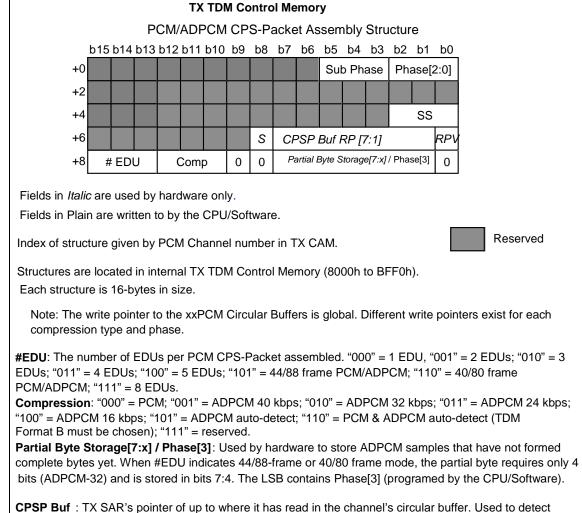

|     | 2.2.2.4 PCM/ADPCM CPS-Packet Assembly Structure | . 38 |

|     | 2.2.3 Treatment of HDLC Data                    | . 39 |

|     | 2.2.3.1 HDLC Streams                            |      |

|     | 2.2.3.2 Address Bytes                           |      |

|     | 2.2.3.3 Control Bytes and Length                |      |

|     | 2.2.3.4 "Raw" AAL2 CPS-Packets                  |      |

|     | 2.2.4 CPS-Packet Final Assembly                 |      |

|     | 2.2.4.1 CPU CPS-Packets                         |      |

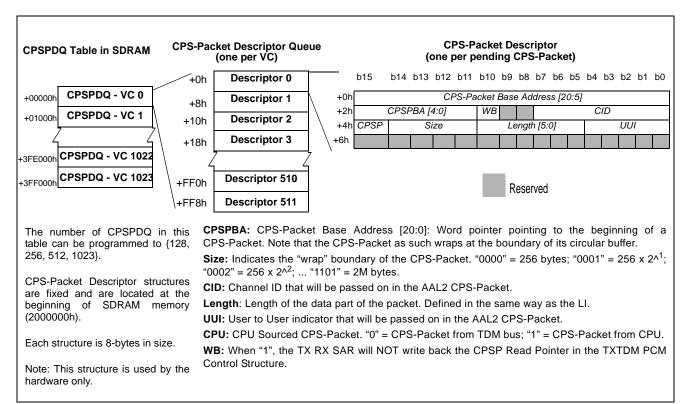

|     | 2.2.4.2 CPS-Packet Descriptor Queue             |      |

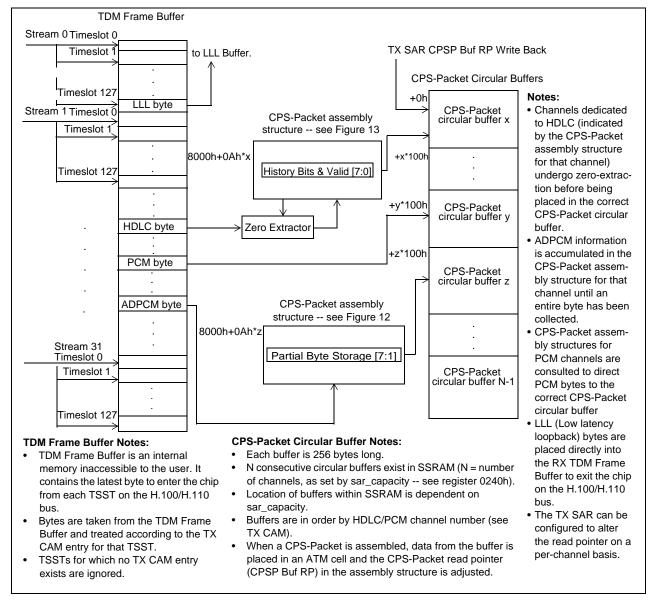

|     | 2.2.4.3 TDM Frame Buffer                        |      |

|     | 2.3 TX SAR                                      |      |

|     | 2.3.1 Overview                                  |      |

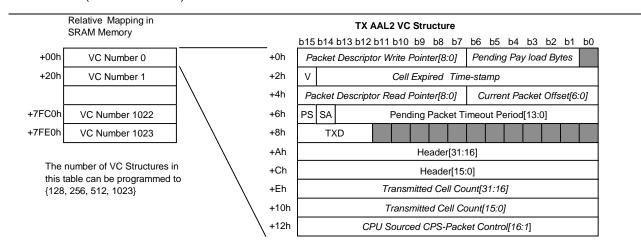

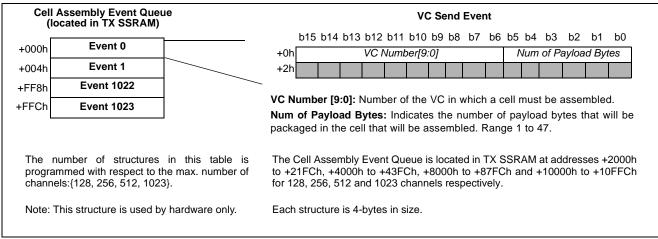

|     | 2.3.2 AAL2 Cell Assembly Process                |      |

|     | 2.3.2.1 AAL2 Cell Assembly Procedure            |      |

|     | 2.3.3 AAL0 Cells                                |      |

|     | 2.4 RX SAR                                      |      |

|     | 2.4.1 RX AAL2 VC Structure                      |      |

|     | 2.4.2 CID Structure                             |      |

|     | 2.4.3 CPS-Packet Disassembly Structures         |      |

|     | 2.4.4 CPS-Packet Loss Compensation              |      |

|     | 2.4.5 CPU CPS-Packets                           |      |

|     | 2.4.6 Treatment of Data Cells                   |      |

|     | 2.5 TDM Reception                               |      |

|     | 2.5.1 Overview                                  |      |

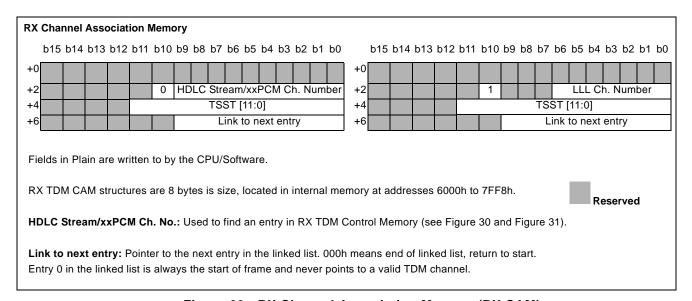

|     | 2.5.2 RX Channel Association Memory             |      |

|     | 2.5.3 RX Channel Underrun Condition             |      |

|     | 2.5.4 Compression                               |      |

|     | 2.5.5 HDLC                                      |      |

|     | 2.6 UTOPIA                                      |      |

|     | 2.6.1 Overview                                  |      |

|     | 2.6.2 UTOPIA Interfaces.                        |      |

|     | 2.6.3 LED Operation                             |      |

|     | 2.6.4 Errors on Received Cells                  |      |

|     | 2.6.5 Cell Routing                              |      |

|     | 2.6.5.1 Mask & Match Process                    |      |

|     |                                                 |      |

# **Table of Contents**

| 2.6.5.2 Look-Up Tables Entries               | 73  |

|----------------------------------------------|-----|

| 2.6.5.3 LUT Addressing                       | 74  |

| 2.6.6 UTOPIA Clocks                          | 75  |

| 2.6.7 External Interface Signals             | 77  |

| 2.6.8 UTOPIA Flow Control.                   | 77  |

| 2.7 H.100/H.110 Interface                    | 77  |

| 2.7.1 Overview                               |     |

| 2.7.2 Bus Signalling                         |     |

| 2.7.3 H.100/H.110 Slave                      |     |

| 2.7.4 Operating as a Slave                   |     |

| 2.7.5 Operating as a Master                  |     |

| 2.7.6 H.100/H.110 Clock Selection Guide.     |     |

| 2.8 Clock Recovery                           |     |

| 2.8.1 Overview                               |     |

| 2.8.1.1 Adaptive Clock Recovery Modules      |     |

| 2.8.1.2 Multiplexers                         |     |

| 2.8.2 Adaptive Clock Recovery Modules        |     |

| 2.8.2.1 adapx_ref Clock Generation.          |     |

| 2.8.3 Multiplexers                           |     |

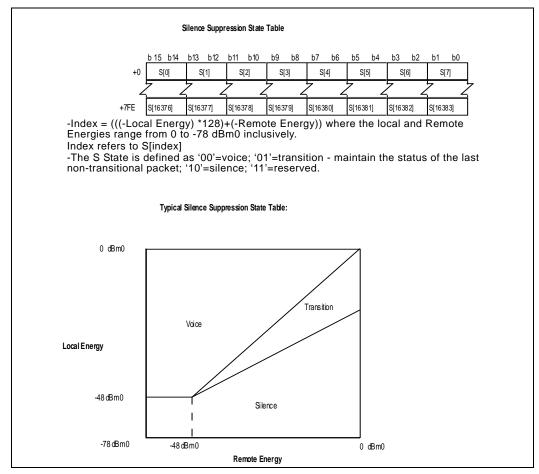

| 2.9 Silence Suppression                      |     |

| 2.9.1 Overview                               |     |

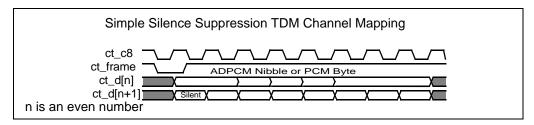

| 2.9.2 Simple Silent Suppression              |     |

| 2.9.2.1 Silent Bit Indication                |     |

| 2.9.2.2 Last Byte Indication                 |     |

| 2.9.2.3 Match and Mask Determines Silence    |     |

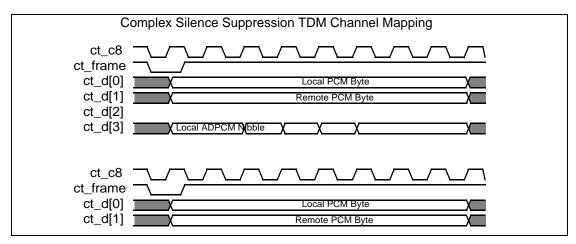

| 2.9.3 Complex Silent Suppression             |     |

| 2.9.3.1 Complex Silent Suppression Operation |     |

| 2.9.3.2 CPS-Packet Silence State             |     |

| 2.9.4 Voice/Silence Timer.                   |     |

| 2.10 HDLC.                                   |     |

| 2.10.1 HDLC Overview                         |     |

| 2.10.2 HDLC Format.                          |     |

| 2.10.3 HDLC Bit-Wise Format.                 |     |

| 2.10.4 HDLC Byte-Wise Format                 |     |

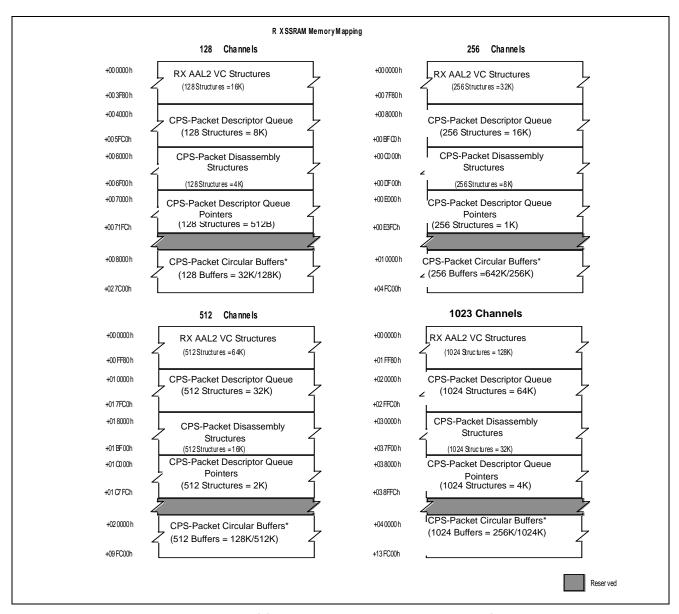

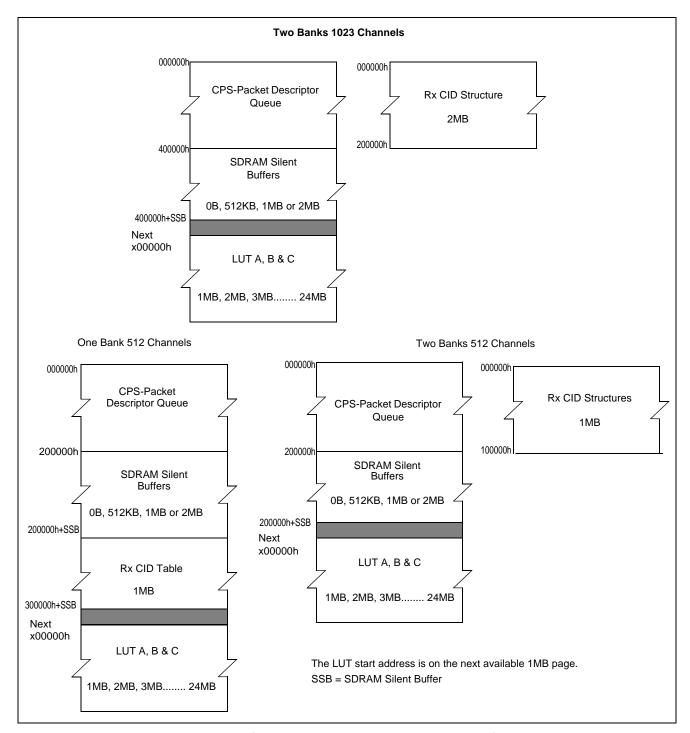

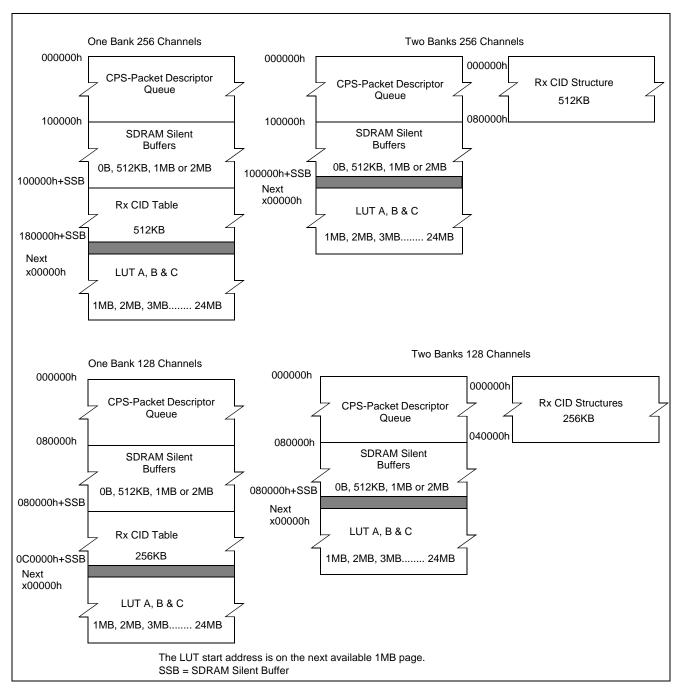

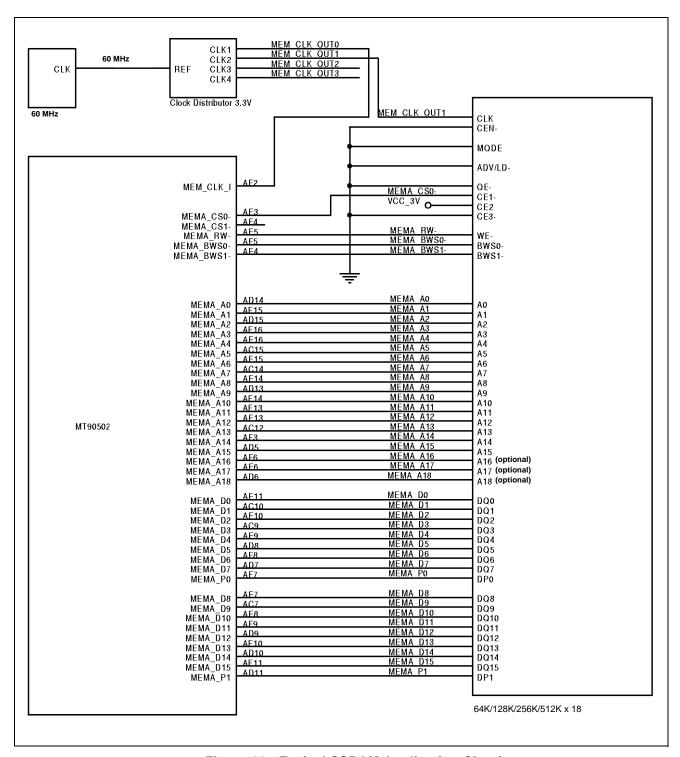

| 2.11 Memory                                  |     |

| 2.11.1 Memory Map                            |     |

| 2.11.2 Memory Structures.                    |     |

| 2.11.3 Mem_Clk and Upclk.                    |     |

| 2.11.4 Memory Controller                     |     |

| 2.11.4.1 Overview.                           |     |

| 2.11.4.2 Functionality                       |     |

| 2.11.5 Initializing SSRAM and SDRAM.         |     |

| 2.11.6 Memory Configuration                  |     |

| 3.0 Register List                            |     |

| 3.1 CPU Register.                            |     |

| 3.2 Main Registers.                          |     |

|                                              |     |

| 3.3 TX Registers                             |     |

| 3.4 RX Registers                             |     |

| 3.5 TX TDM Registers                         |     |

| 3.6 UTOPIA Registers                         |     |

| 3.7 H.100/H.110 Registers                    |     |

| 3.0 Iviiscellarieuus Registers               | 1/8 |

# **Table of Contents**

| 3.9 RX TDM Registers                     | 181 |

|------------------------------------------|-----|

| 4.0 Electrical Specification             | 183 |

| 4.1 DC Characteristics                   | 183 |

| 4.2 AC Characteristics                   | 185 |

| 4.3 Intel/Motorola Interface             |     |

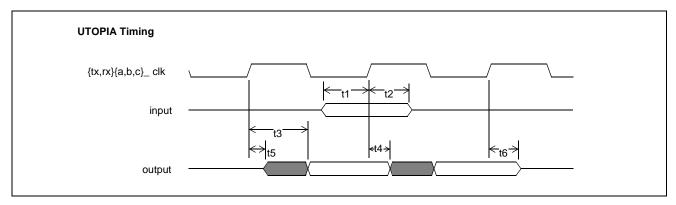

| 4.3.1 UTOPIA Interface                   | 195 |

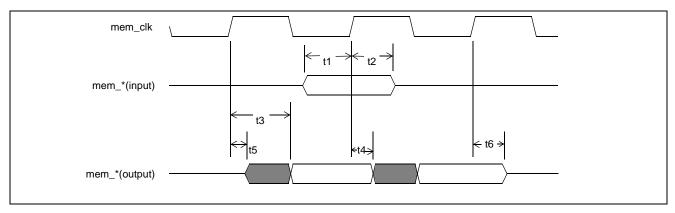

| 4.3.2 External Memory Interface          | 196 |

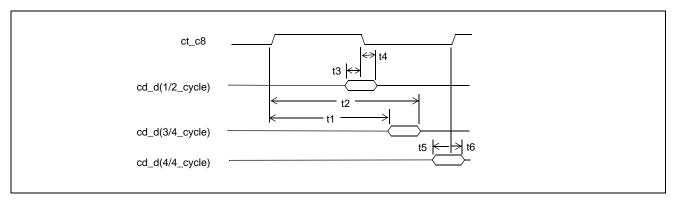

| 4.3.3 H.100/H.110 Interface              |     |

| 5.0 Glossary of Terminology              | 201 |

| 5.1 Standard Terms and Abbreviations     | 201 |

| 5.2 Terms Specific to AAL2               | 202 |

| 5.3 Terms Specific to this Specification | 202 |

| 5.4 Register Types                       | 203 |

| 5.5 Units and Conventions                |     |

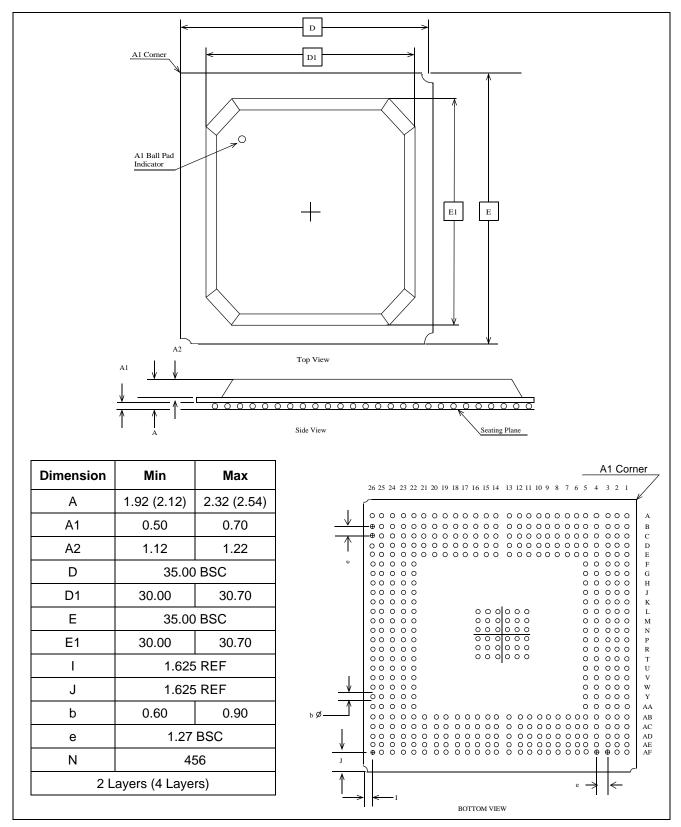

| 6.0 Mechanical Drawing                   | 204 |

# **List of Figures**

| Figure 1 - MT90502 Functional Block                                                   | 1  |

|---------------------------------------------------------------------------------------|----|

| Figure 2 - 456 PBGA                                                                   | 13 |

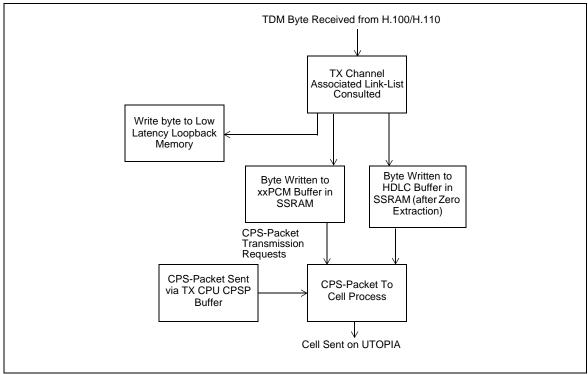

| Figure 3 - TX Cell Flow                                                               | 27 |

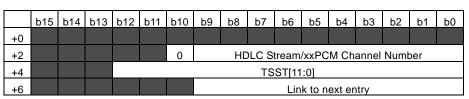

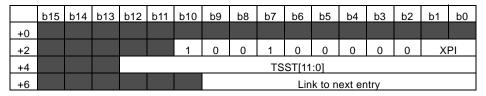

| Figure 4 - TX Channel Association Memory (TX CAM)                                     | 29 |

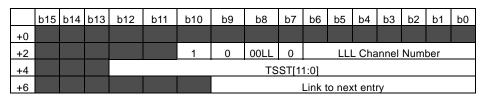

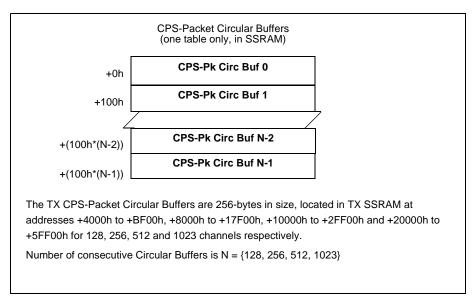

| Figure 5 - TX CPS-Packet Circular Buffers                                             | 30 |

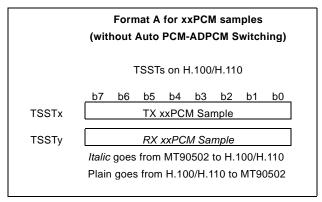

| Figure 6 - PCM/ADPCM Data Format A                                                    |    |

| Figure 7 - PCM/ADPCM RX Data Format A                                                 | 32 |

| Figure 8 - PCM/ADPCM TX Data Format A                                                 | 33 |

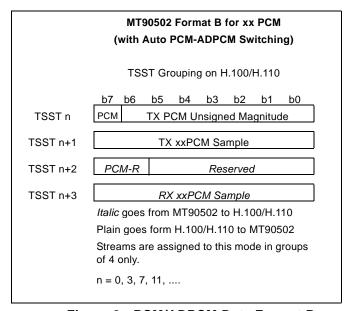

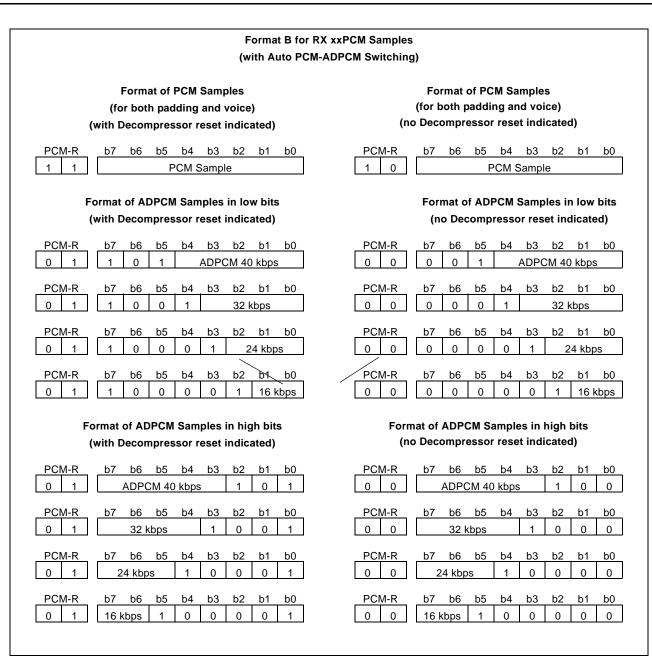

| Figure 9 - PCM/ADPCM Data Format B                                                    | 34 |

| Figure 10 - PCM/ADPCM RX Data Format B                                                | 35 |

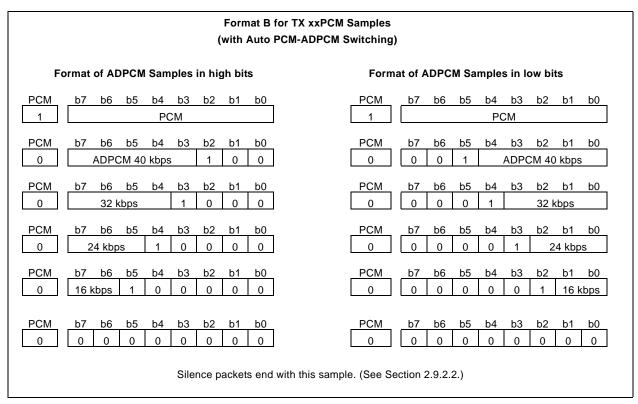

| Figure 11 - PCM/ADPCM TX Data Format B                                                | 36 |

| Figure 12 - PCM/ADPCM CPS-Packet Assembly Structure                                   | 38 |

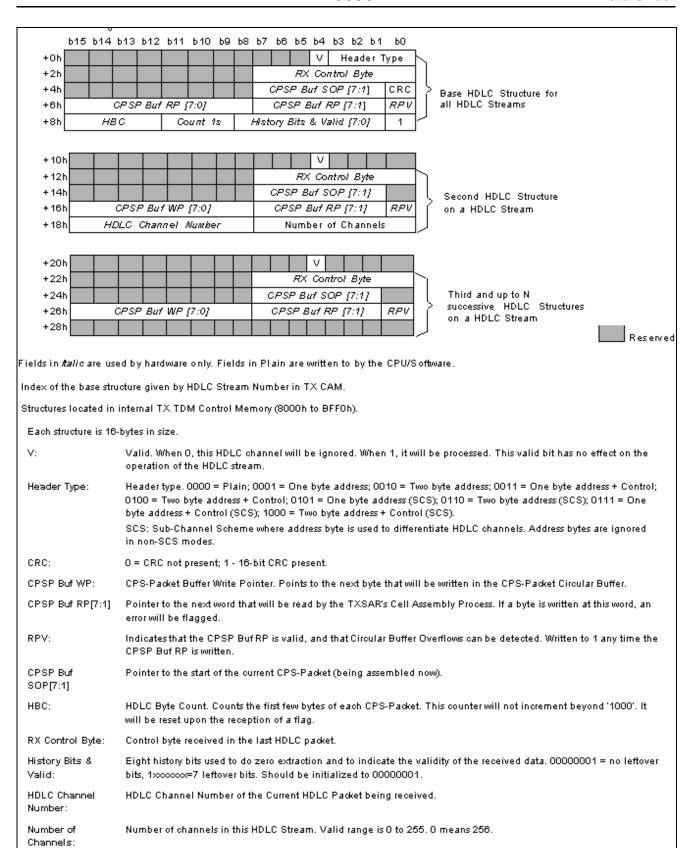

| Figure 13 - HDLC CPS-Packet Assembly Structure                                        | 40 |

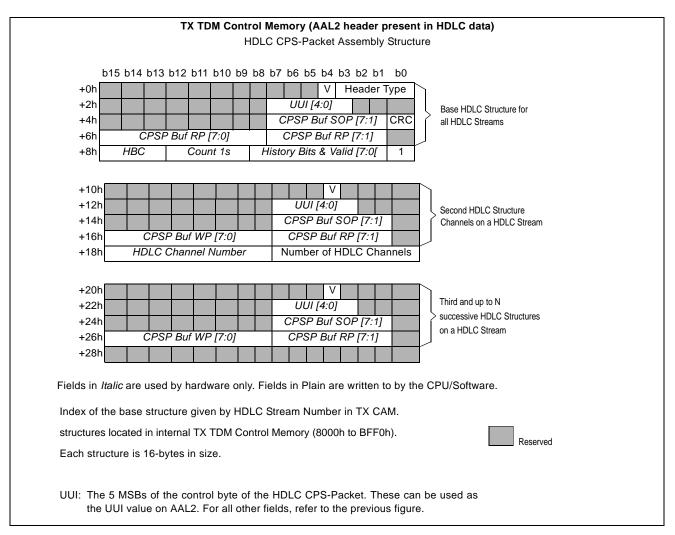

| Figure 14 - HDLC CPS-Packet Assembly Structure                                        | 41 |

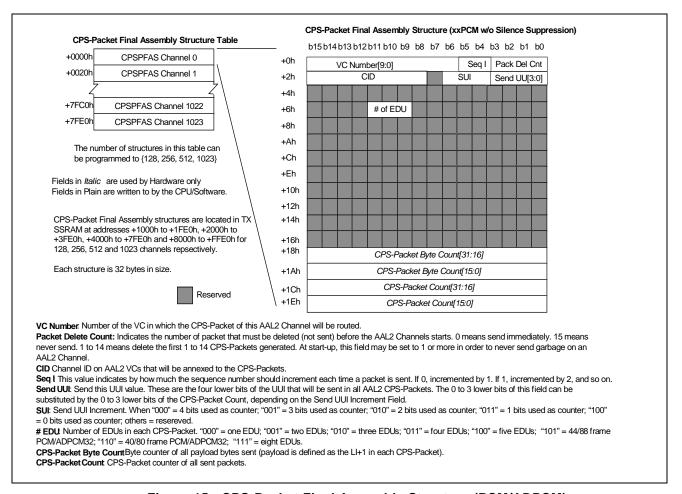

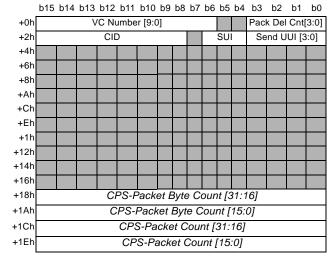

| Figure 15 - CPS-Packet Final Assembly Structure (PCM/ADPCM)                           | 42 |

| Figure 16 - CPS-Packet Final Assembly Structure (HDLC Channel)                        |    |

| Figure 17 - CPS-Packet Descriptor Queue                                               | 45 |

| Figure 18 - TDM Frame Buffer                                                          | 46 |

| Figure 19 - TX AAL2 VC Structure                                                      | 47 |

| Figure 20 - Cell Assembly Event Queue                                                 | 50 |

| Figure 21 - TX Cell Format                                                            | 50 |

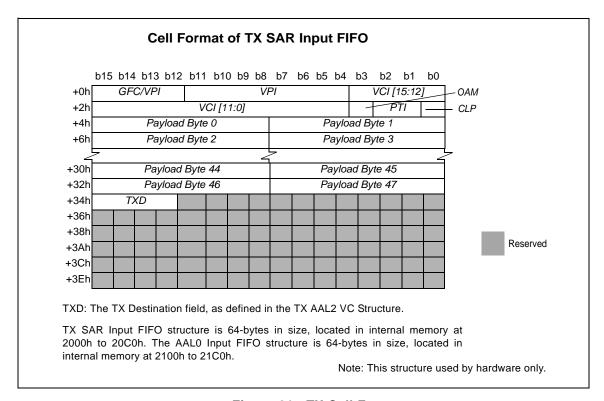

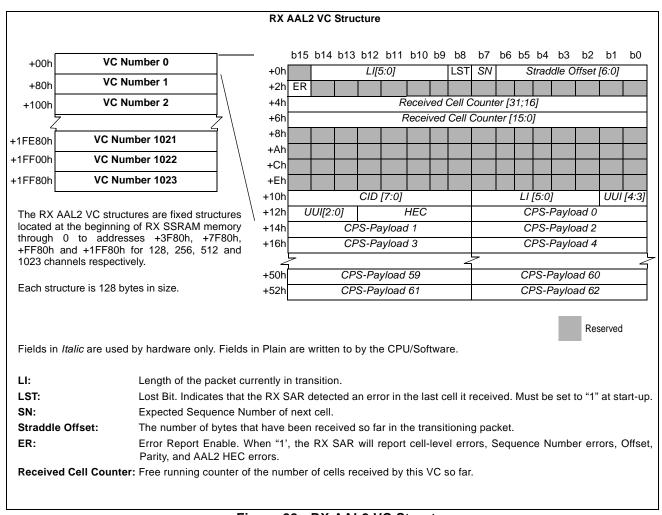

| Figure 22 - RX AAL2 VC Structure                                                      | 52 |

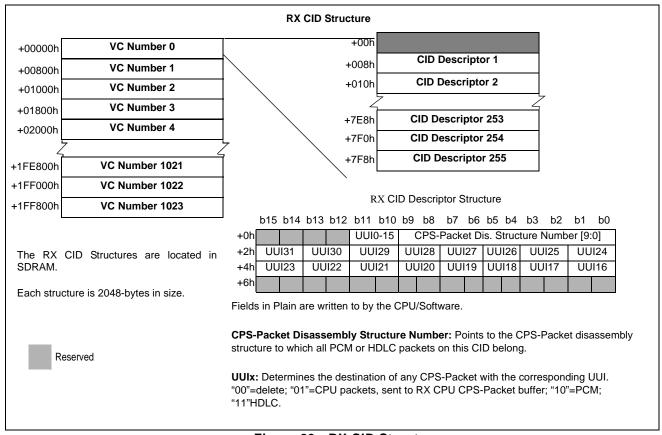

| Figure 23 - RX CID Structure                                                          | 53 |

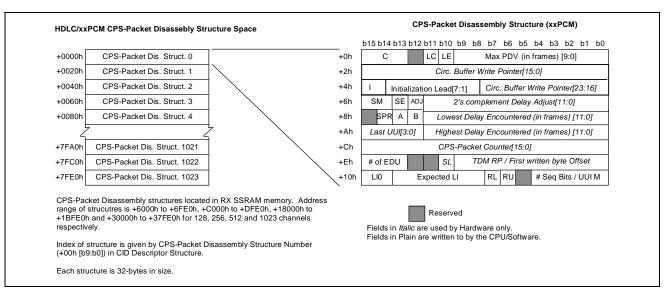

| Figure 24 - CPS-Packet Disassembly Structure (PCM/ADPCM)                              | 54 |

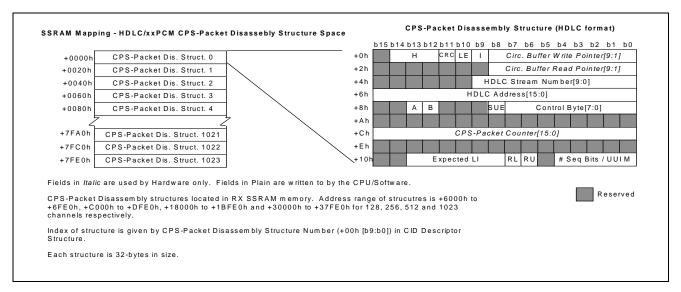

| Figure 25 - CPS-Packet Disassembly Structure (HDLC Format)                            | 57 |

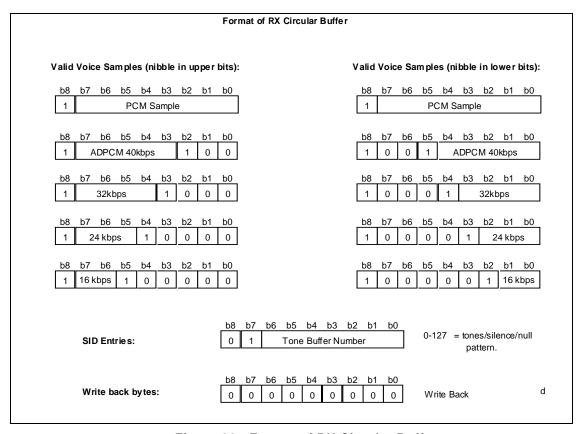

| Figure 26 - Format of RX Circular Buffer                                              | 60 |

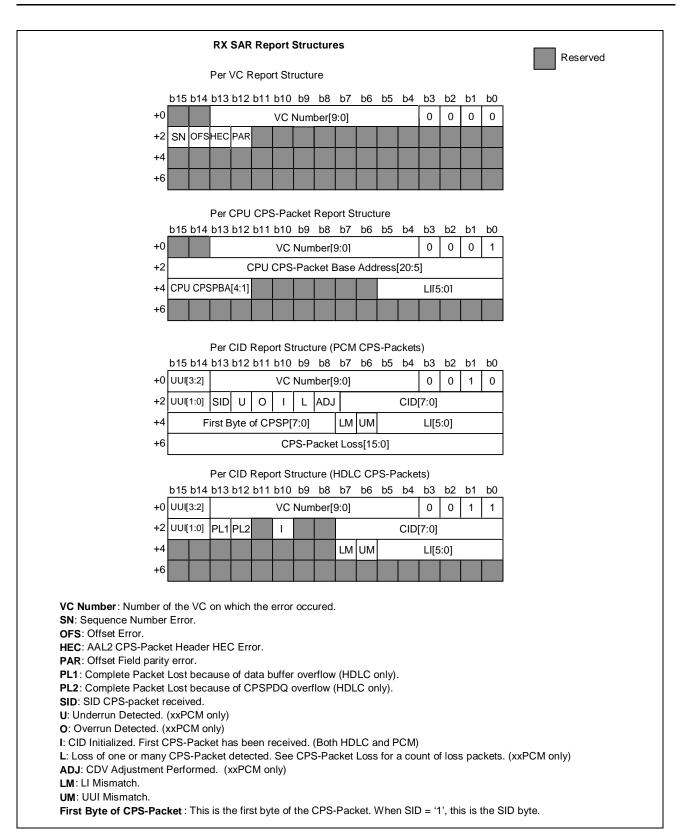

| Figure 27 - RX Error Report FIFO Structures                                           | 62 |

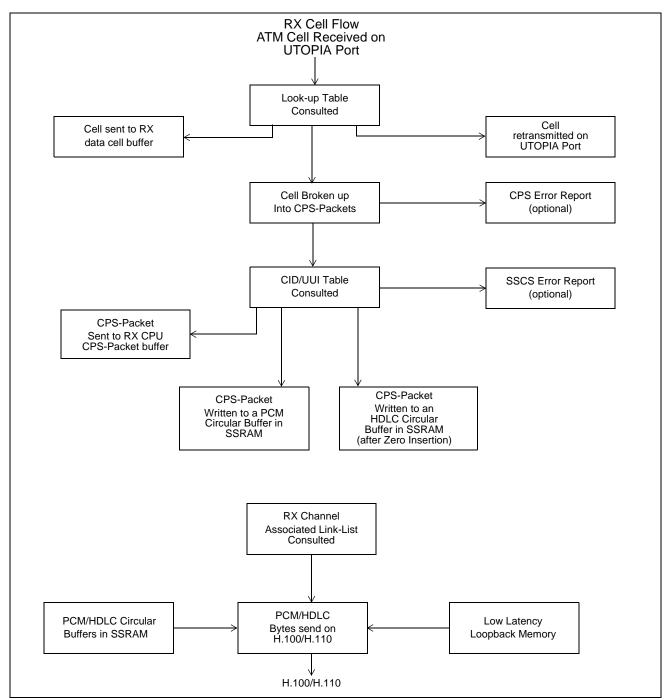

| Figure 28 - RX Cell Flow                                                              |    |

| Figure 29 - RX Channel Association Memory (RX CAM)                                    |    |

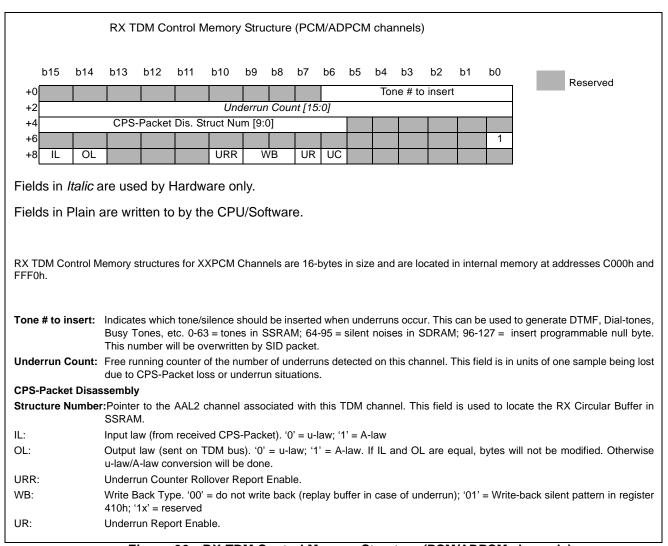

| Figure 30 - RX TDM Control Memory Structure (PCM/ADPCM channels)                      | 66 |

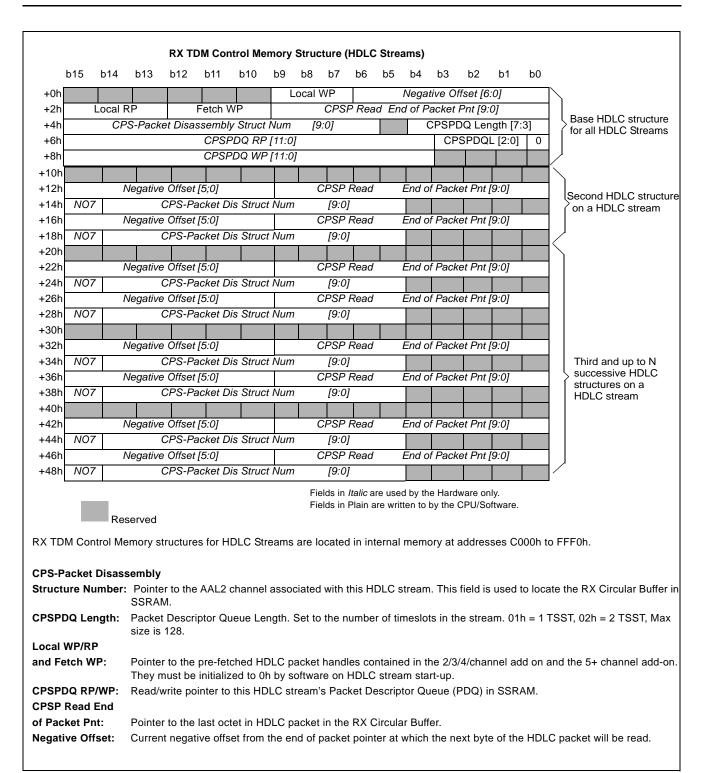

| Figure 31 - RX TDM Control Memory Structure (HDLC Streams)                            |    |

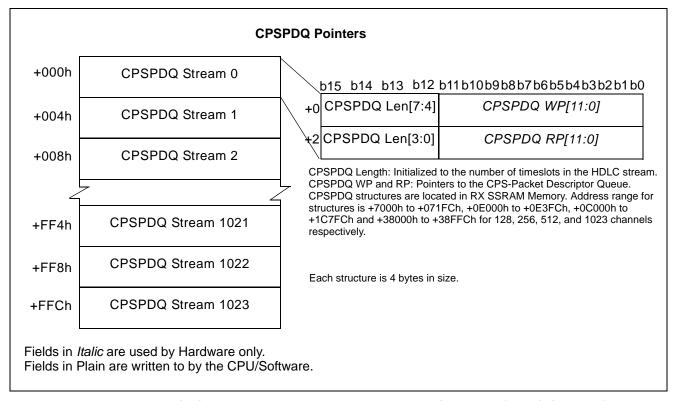

| Figure 32 - CPS-Packet Descriptor Queue Pointers Structure (HDLC Streams)             |    |

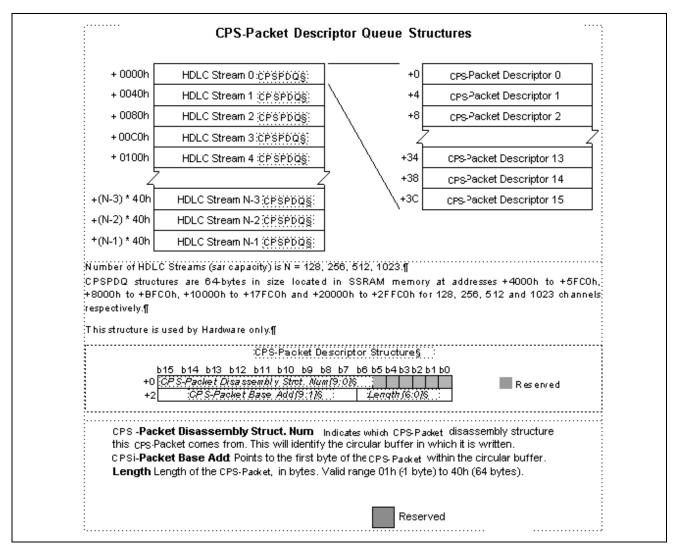

| Figure 33 - CPS-Packet Descriptor Queue Structures (HDLC Streams)                     |    |

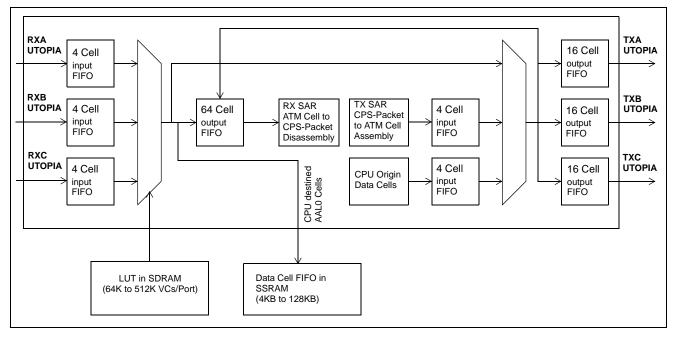

| Figure 34 - SAR and UTOPIA Block                                                      |    |

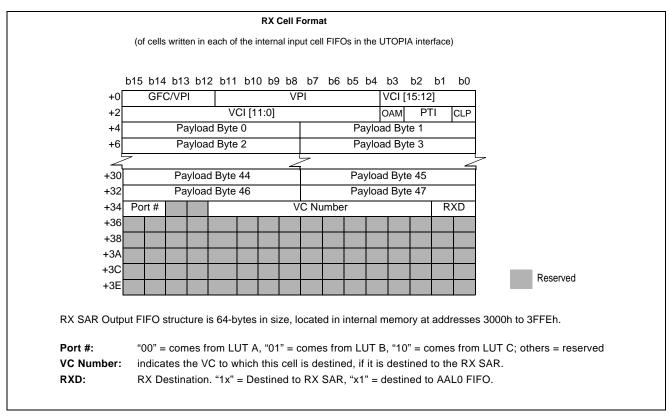

| Figure 35 - RX Cell Format                                                            |    |

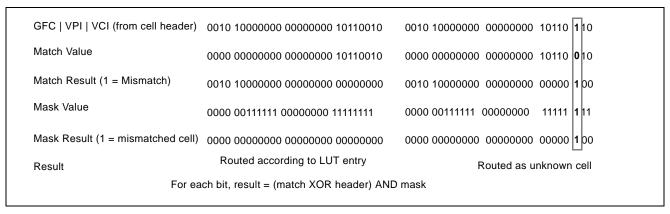

| Figure 36 - Mask & Match Example                                                      |    |

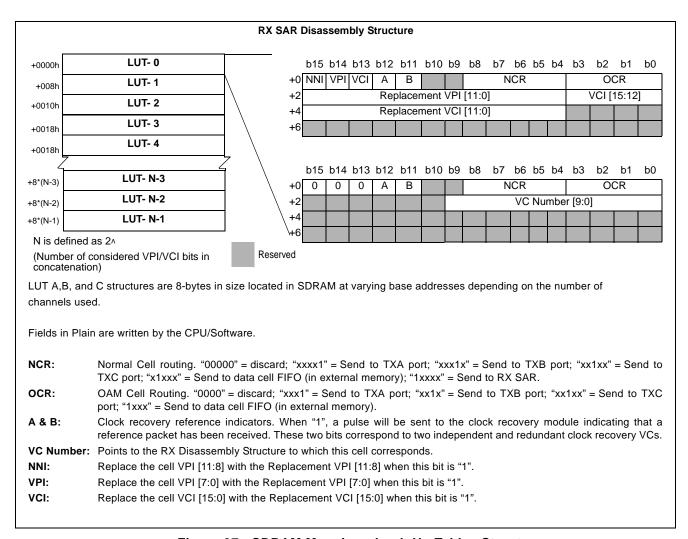

| Figure 37 - SDRAM Mapping - Look-Up Tables Structure                                  |    |

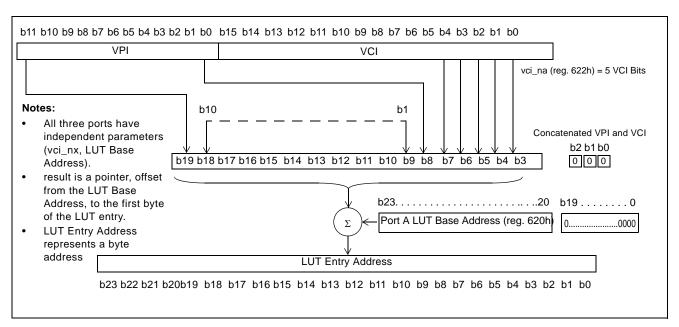

| Figure 38 - VPI/VCI Concatenation and LUT Entry Address Example                       |    |

| Figure 39 - UTOPIA Clocks Selection                                                   |    |

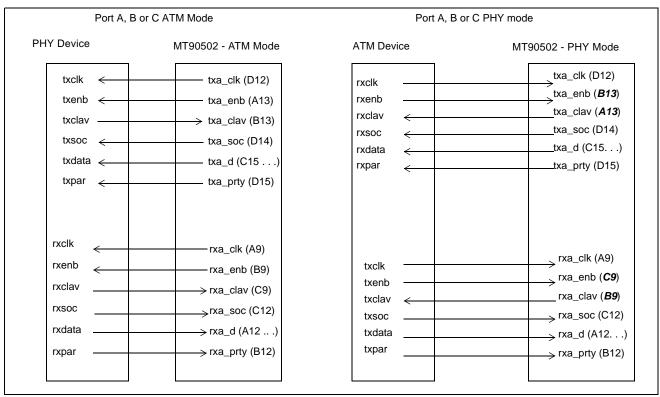

| Figure 40 - External UTOPIA Interface                                                 |    |

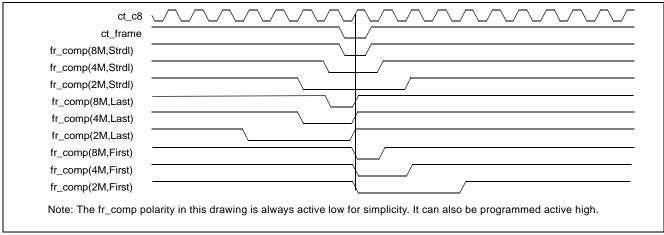

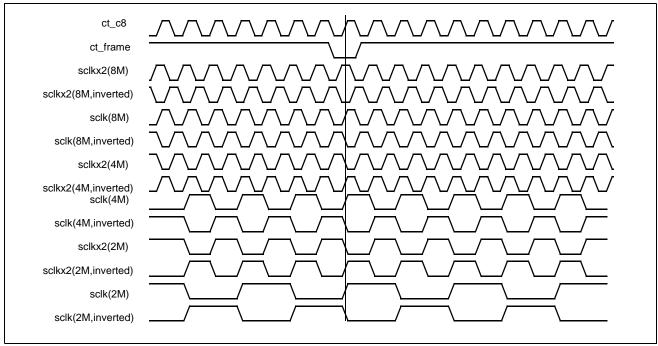

| Figure 41 - TDM Bus Timing - Fr_Comp Generation                                       |    |

| Figure 42 - TDM Bus Timing - sclkx2 Generation                                        |    |

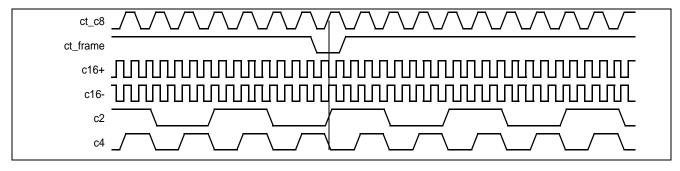

| Figure 43 - TDM Bus Timing - Compatibility Clock Generation (other than sclk, sclkx2) |    |

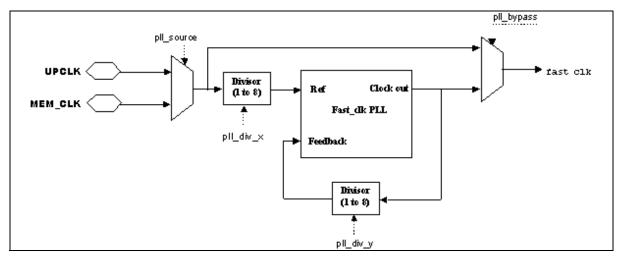

| Figure 44 - Fast Clock Generation                                                     |    |

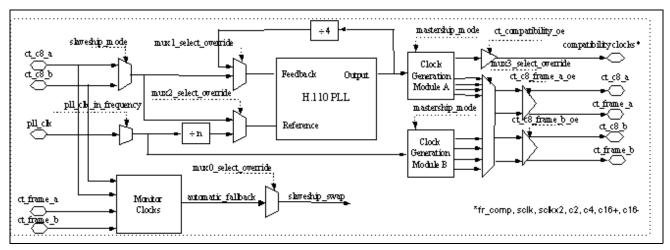

| Figure 45 - H.100/H.110 PLL Clock Selection                                           |    |

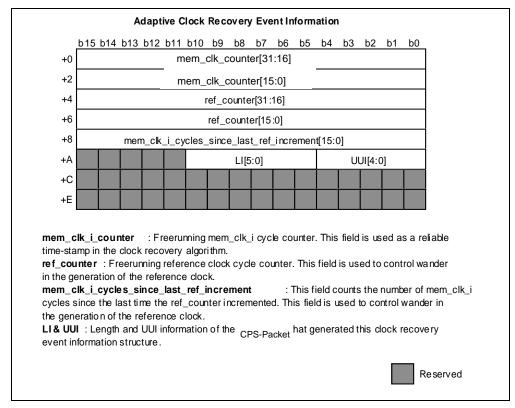

| Figure 46 - Adaptive Clock Recovery Event Information                                 |    |

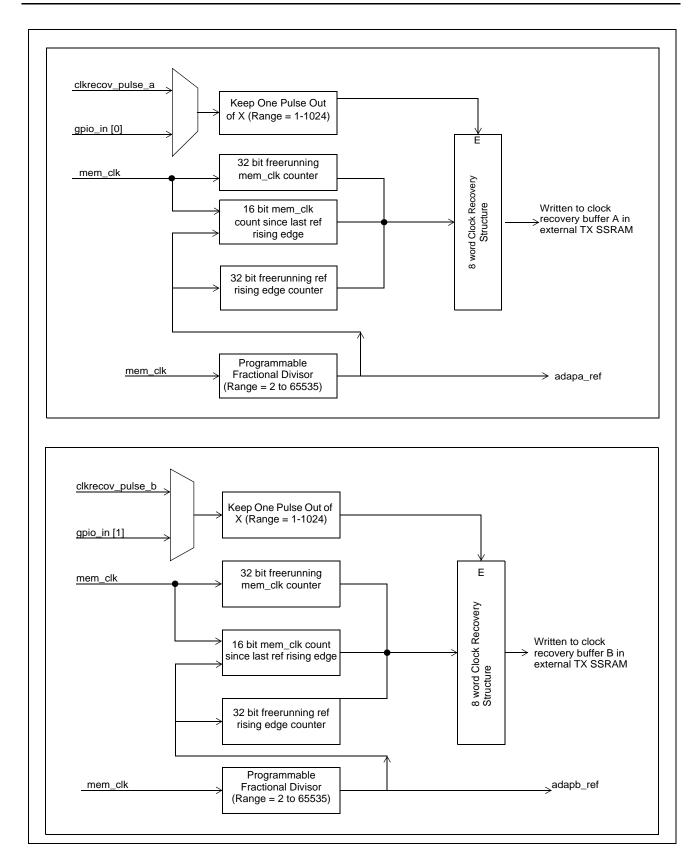

| Figure 47 - Adaptive Clock Recovery Modules                                           |    |

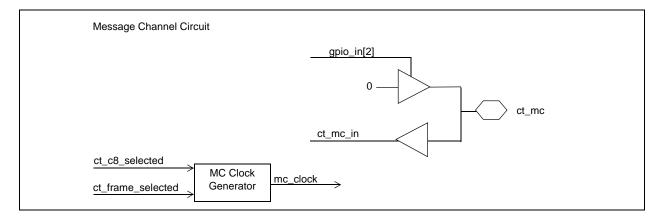

| Figure 48 - Message Channel                                                           | 86 |

# **List of Figures**

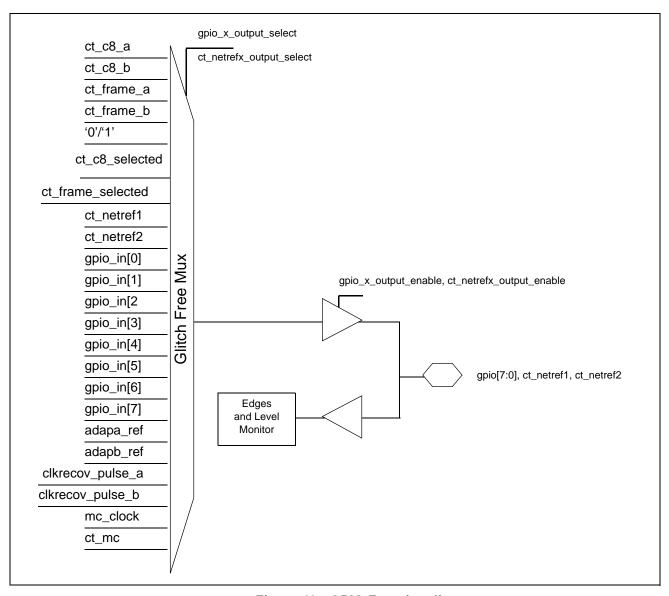

| Figure 49 - GPIO Functionality                                                | 87  |

|-------------------------------------------------------------------------------|-----|

| Figure 50 - Simple Silent Suppression Stream Configuration                    | 91  |

| Figure 51 - Silent Suppression Mask & Match Example                           |     |

| Figure 52 - Complex Silent Suppression Configurable State Graph               | 92  |

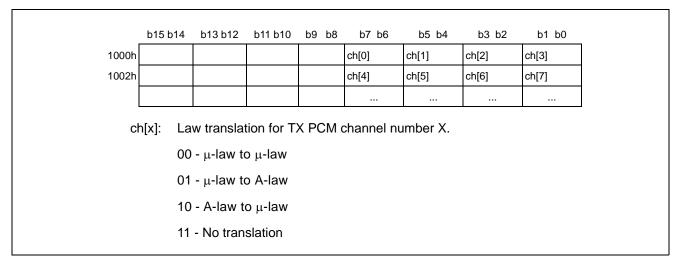

| Figure 53 - PCM Law Table                                                     | 93  |

| Figure 54 - Complex Silent Suppression Stream Configuration                   | 94  |

| Figure 55 - ADPCM Complex Silent Suppression Stream Configuration             | 94  |

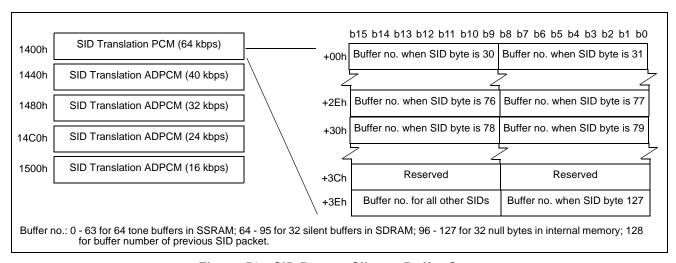

| Figure 56 - SID Byte to Silence Buffer Structure                              | 95  |

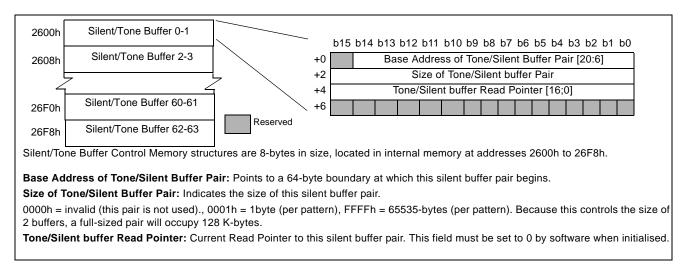

| Figure 57 - SSRAM Tone Buffer Control Memory                                  | 96  |

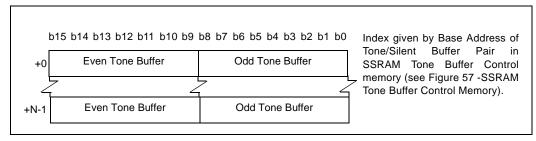

| Figure 58 - Silent Tone Buffer Pair in TX SSRAM                               | 96  |

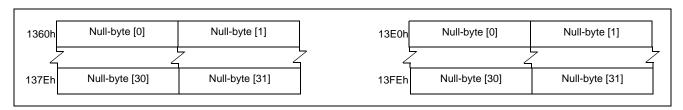

| Figure 59 - Null Bytes in Tone Data Buffer Memory                             | 96  |

| Figure 60 - 32 SDRAM Silence Buffers                                          | 97  |

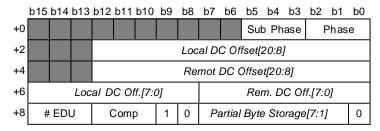

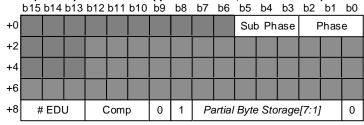

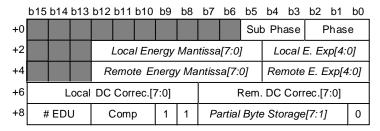

| Figure 61 - Silent Suppression PCM/ADPCM CPS-Packet Assembly Structures       | 98  |

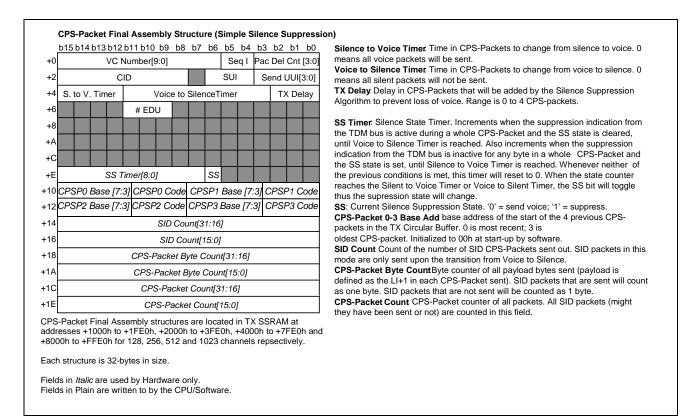

| Figure 62 - CPS-Packet Final Assembly Structure (Simple Silence Suppression)  | 99  |

| Figure 63 - CPS-Packet Final Assembly Structure (Complex Silence Suppression) | 100 |

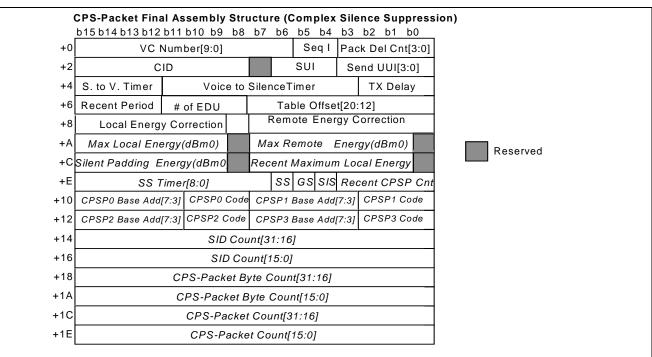

| Figure 64 - Supported HDLC Formats                                            | 102 |

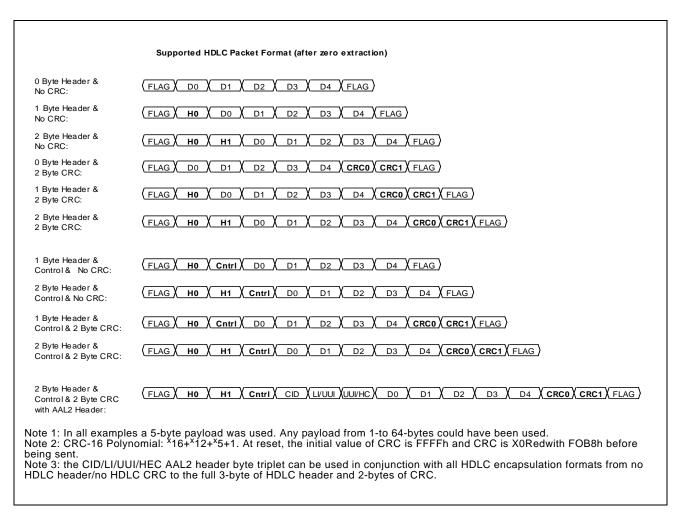

| Figure 65 - TX SSRAM Memory Mapping for Fixed Structures                      | 107 |

| Figure 66 - RX SSRAM Memory Mapping for Fixed Structures                      | 108 |

| Figure 67 - SDRAM Memory Map for 512 & 1023 Channels                          | 109 |

| Figure 68 - SDRAM Memory Map for 128 and 256 Channels                         | 110 |

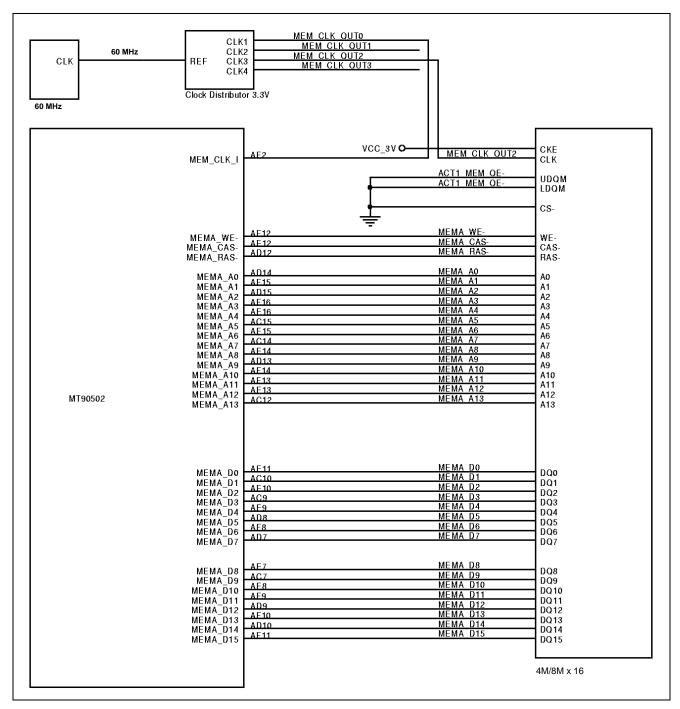

| Figure 69 - Typical SSRAM Application Circuit                                 | 112 |

| Figure 70 - Typical SDRAM Application Circuit                                 | 113 |

|              | PU Bus Interface                                      |     |

|--------------|-------------------------------------------------------|-----|

| Table 2 - UT | TOPIA Interface Pins                                  | 14  |

| Table 3 - H. | 100/H.110 Interface Pins                              | 17  |

| Table 4 - Me | emory Interface Pins                                  | 18  |

| Table 6 - JT | AG Pins                                               | 19  |

| Table 8 - VS | SS (0 V) Pins                                         | 19  |

|              | DD3 (3.3 V) Pins                                      |     |

|              | /DD5 (3.3 V or 5.0 V) Pins                            |     |

| Table 5 - Mi | scellaneous Pins                                      | 19  |

| Table 11 - N | lot Connected (Leave Floating) Pins                   | 20  |

|              | Pinout Summary                                        |     |

|              | CPU Interface Mode Selection                          |     |

|              | Control Register (000h)                               |     |

|              | Read/Write Data Register (004h)                       |     |

|              | Address High Register (008h)                          |     |

|              | Address Low Register (00Ah)                           |     |

|              | (PI Selection Table                                   |     |

|              | Format for writing CPS-Packet payload to memory       |     |

|              | Example of Written Payload Bytes                      |     |

|              | AAL2 VC Structure Fields                              |     |

|              | CPS-Packet Disassembly Structure (PCM/ADPCM) Fields   |     |

|              | CPS-Packet Disassembly Structure (HDLC format) Fields |     |

|              | RX SAR Errors and Events                              |     |

|              | JTOPIA Clocks Selection Registers                     |     |

|              | CT-Bus Signalling Function.                           |     |

|              | Fast Clock PLL Divisor Values                         |     |

|              | Fast Clock Registers                                  |     |

|              | H.100/H110 PLL Clock Selection Registers              |     |

|              | Clock Recovery Registers                              |     |

|              | Buffer Sizes                                          |     |

|              | GPIO mux, Output Selection.                           |     |

|              | HDLC Packet Formats and Header Types                  |     |

|              | /IT90502 Memory Map                                   |     |

|              | CPU Control Register                                  |     |

|              | CPU Status Register                                   |     |

|              | Mem_clk Frequency Control Register                    |     |

|              | Jpclk Frequency Control Register                      |     |

|              | CPU Interrupt Enable Register                         |     |

|              | Fast Clock PLL Configuration Register 0               |     |

|              | LED Timing Control Register                           |     |

|              | H100/H110 PLL Configuration Register 0                |     |

|              | D Register                                            |     |

|              | Fast Clock PLL Configuration Register 1               |     |

|              | Aain Status Register                                  |     |

|              | Nain Interrupt Enable Register                        |     |

|              | nterrupt Flag Register                                |     |

|              | Ninimum Interrupt Interval Register                   |     |

|              | Interrupt Polarity & O/P Enable Register              |     |

| 149 - 1      | interrupt Folianty α O/F Enable Register              | 4 I |

| Table 50 - | Interrupt 1 Enable Register                | 121 |

|------------|--------------------------------------------|-----|

| Table 51 - | Interrupt 2 Enable Register                | 122 |

| Table 52 - | Tx A Clock Division Register               | 123 |

| Table 53 - | Tx B Clock Division Register               | 124 |

|            | · Tx C Clock Division Register             |     |

|            | Rx A Clock Division Register               |     |

|            | Rx B Clock Division Register               |     |

|            | Rx C Clock Division Register               |     |

|            | Memory Parity Register 0                   |     |

|            | Memory Parity Register 1                   |     |

|            | Memory Configuration Register 0            |     |

|            | Memory Configuration Register 1            |     |

|            | Memory Parity Register 2                   |     |

|            | SDRAM Configuration Register 0             |     |

|            | SDRAM Configuration Register 1             |     |

|            | SDRAM Configuration Register 2             |     |

|            | SDRAM Configuration Register 3             |     |

|            | SDRAM Configuration Register 4             |     |

|            |                                            |     |

|            | SDRAM Configuration Register 5             |     |

|            | TX Control Register.                       |     |

|            | TX AALO Maritan Bagister                   |     |

|            | TX AAL0 Monitor Register                   |     |

|            | RX Control Register                        |     |

|            | TX Interrupt Enable Register               |     |

|            | RX Interrupt Enable Register               |     |

|            | PCM Silent Pattern Register                |     |

|            | RX Status Register                         |     |

|            | CRC Configuration Register 0               |     |

|            | CRC Configuration Register 1               |     |

|            | AAL0 FIFO Management Register              |     |

|            | AAL0 Read Pointer Register                 |     |

|            | AAL0 Write Pointer Register                |     |

|            | Error Management Register                  |     |

|            | Error Write Pointer Register               |     |

|            | CPU Management Register 0                  |     |

|            | CPU Management Register 1                  |     |

|            | · AAL0 Timeout Period (High Word) Register |     |

|            | Error Read Pointer Register                |     |

| Table 88 - | AAL0 Timeout Period (Low Word) Register    | 139 |

| Table 89 - | Error Timeout Period (High Word) Register  | 139 |

| Table 90 - | Error Timeout Period (Low Word) Register   | 139 |

| Table 91 - | AAL0 & Error Treated Register              | 139 |

| Table 92 - | TX TDM Control Register                    | 140 |

| Table 93 - | TDM TX Status Register                     | 140 |

| Table 94 - | TDM TX Interrupt Enable Register           | 142 |

|            | Silent Pattern Detection Match Register A  |     |

|            | Silent Pattern Detection Match Register B  |     |

|            | TDM Pointer Monitor Register               |     |

|            |                                            |     |

| Table 98 - CPU CPS-Packet Register 0                  |     |

|-------------------------------------------------------|-----|

| Table 99 - CPU CPS-Packet Register 1                  |     |

| Table 100 - CPU CPS-Packet Register 2                 | 144 |

| Table 101 - CPU CPS-Packet Register 3                 | 144 |

| Table 102 - UTOPIA Control Register 1                 | 145 |

| Table 103 - UTOPIA Status Register 0                  | 146 |

| Table 104 - UTOPIA Interrupt Enable Register 0        |     |

| Table 105 - UTOPIA Status Register 2                  |     |

| Table 106 - UTOPIA Interrupt Enable Register 2        |     |

| Table 107 - UTOPIA Control Register 2                 |     |

| Table 108 - Lost Cells Counter                        |     |

| Table 109 - General Purpose I/O Register 0            |     |

| Table 110 - Port A LUT Base Address Register          |     |

| Table 111 - Port A VCI Bits in LUT                    |     |

| Table 112 - Port A VPI Match Register                 |     |

| Table 113 - Port A VPI Mask Register                  |     |

| Table 114 - Port A VCI Match Register                 |     |

| Table 115 - Port A VCI Mask Register                  |     |

| Table 116 - Port A Overflow Register 0                |     |

| Table 117 - Port A Overflow Register 1                |     |

| Table 117 - Port A Overflow Register 1                |     |

| Table 119 - Port A Cell Arrival Counter (Low Word)    |     |

| Table 119 - Port A Cell Arrival Counter (Low Word)    |     |

| Table 120 - Port A Cell Departure Counter (High Word) |     |

| Table 121 - Port A Cell Departure Counter (Low Word)  |     |

|                                                       |     |

| Table 123 - Port B VCI Bits in LUT                    |     |

| Table 124 - Port B VPI Match Register                 |     |

| Table 125 - Port B VPI Mask Register                  |     |

| Table 126 - Port B VCI Match Register                 |     |

| Table 127 - Port B VCI Mask Register                  |     |

| Table 128 - Port B Overflow Register 0                |     |

| Table 129 - Port B Overflow Register 1                |     |

| Table 130 - Port B Cell Arrival Counter (High Word)   |     |

| Table 131 - Port B Cell Arrival Counter (Low Word).   |     |

| Table 132 - Port B Cell Departure Counter (High Word) |     |

| Table 133 - Port B Cell Departure Counter (Low Word)  |     |

| Table 134 - Port C LUT Base Address Register          |     |

| Table 135 - Port C VCI Bits in LUT                    |     |

| Table 137 - Port C VPI Mask Register                  |     |

| Table 138 - Port C VCI Match Register                 |     |

| Table 139 - Port C VCI Mask Register                  | 156 |

| Table 136 - Port C VPI Match Register                 |     |

| Table 140 - Port C Overflow Register 0                |     |

| Table 141 - Port C Overflow Register 1                | 157 |

| Table 142 - Port C Cell Arrival Counter (High Word)   | 157 |

| Table 143 - Port C Cell Arrival Counter (Low Word)    | 157 |

| Table 144 - Port C Cell Departure Counter (High Word) |     |

| Table 145 - Port C Cell Departure Counter (Low Word)  | 158 |

|                                                       |     |

| Table 146 - AAL0 Cell Arrival Counter (High Word)                | 158 |

|------------------------------------------------------------------|-----|

| Table 147 - AAL0 Cell Arrival Counter (Low Word)                 | 158 |

| Table 148 - AAL0 Overflow Register 0                             | 158 |

| Table 149 - AAL0 Overflow Register 1                             | 159 |

| Table 150 - TX_SAR Cell Arrival Counter (High Word)              |     |

| Table 151 - TX_SAR Cell Arrival Counter (Low Word)               |     |

| Table 153 - RX_SAR Cell Departure Counter (Low Word)             |     |

| Table 154 - TX_SAR Overflow Register 0                           |     |

| Table 155 - TX_SAR Overflow Register 1                           |     |

| Table 152 - RX_SAR Cell Departure Counter (High Word)            |     |

| Table 156 - Port A Address Register                              |     |

| Table 157 - HEC Byte Control Register                            |     |

| Table 158 - Unknown Header Routing Register                      |     |

| Table 160 - H.100/H.110 Control Register                         |     |

| Table 159 - Unknown OAM Routing Register                         |     |

| Table 161 - H.100/H.110 Status Register 0                        |     |

| Table 162 - H.100/H.110 Interrupt Enable Register 0              |     |

| Table 164 - Memory Clock Counter 1                               |     |

| Table 165 - Memory Clock Alarm Register 0                        |     |

| Table 166 - Memory Clock Alarm Register 1                        |     |

| Table 167 - Adaptive Module A Register 0                         |     |

| Table 163 - Memory Clock Counter 0                               |     |

| Table 168 - Adaptive Module A Register 1                         |     |

| Table 169 - Adaptive Module A Register 2                         |     |

| Table 170 - Adaptive Module B Register 0                         |     |

| Table 171 - Adaptive Module B Register 1                         |     |

| Table 172 - Adaptive Module B Register 2                         |     |

| Table 174 - H.100/H.110 Master Register 1                        |     |

| Table 173 - H.100/H.110 Master Register 0                        |     |

| Table 175 - Clock Rates Register                                 |     |

| Table 176 - Timing Configuration Register                        |     |

| Table 177 - General Purpose I/O Output Register 0                |     |

| Table 178 - General Purpose I/O Output Register 1                |     |

| Table 179 - General Purpose I/O Output Register 2                |     |

| Table 180 - General Purpose I/O Output Register 3                |     |

| Table 182 - General Purpose I/O Input Register                   |     |

| Table 181 - General Purpose I/O Output Register 4                |     |

| Table 183 - General Purpose I/O Status Register                  |     |

| Table 185 - H.100/H.110 Master Hidden Register 0                 |     |

| Table 184 - General Purpose I/O Status Interrupt Enable Register |     |

| Table 186 - H.100/H.110 Master Hidden Register 1                 |     |

| Table 187 - H.100/H.110 Master Hidden Register 2                 |     |

| Table 188 - Miscellaneous Status Register                        |     |

| Table 189 - Miscellaneous Interrupt Enable Register              |     |

| Table 190 - Tone Buffer Control Register                         |     |

| Table 191 - Point A Buffer Management Register                   |     |

| Table 192 - Point A Read Pointer Register                        |     |

| Table 193 - Point A Write Pointer Register                       |     |

| Table 100 Tollic A Write Folliter Negloter                       | 113 |

| Table 194 - Point B Buffer Management Register                        | 179 |

|-----------------------------------------------------------------------|-----|

| Table 195 - Point B Read Pointer Register                             | 180 |

| Table 196 - Point B Write Pointer Register                            | 180 |

| Table 197 - CID Base Address Register                                 | 180 |

| Table 198 - RX TDM Control Register                                   | 181 |

| Table 199 - RX TDM Status Register 0                                  | 181 |

| Table 200 - RX TDM Interrupt Enable Register 0                        | 182 |

| Table 201 - RX TDM Channel Number Monitor Register                    | 182 |

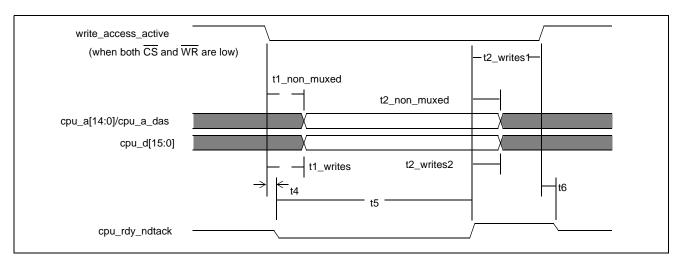

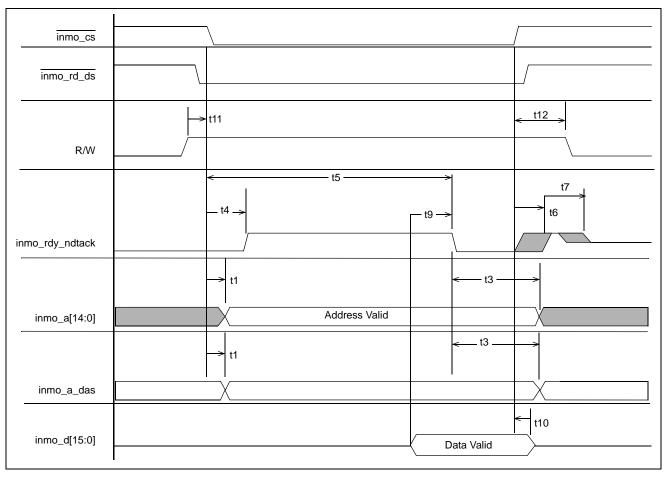

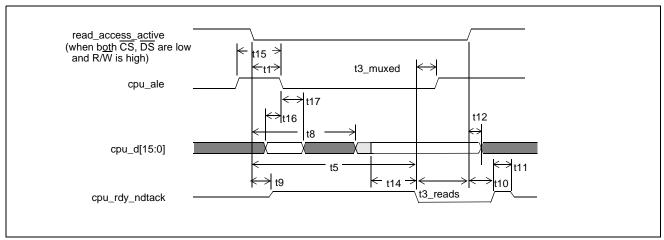

| Table 202 - Non-Multiplexed CPU Interface - Intel Mode - Write Access | 185 |

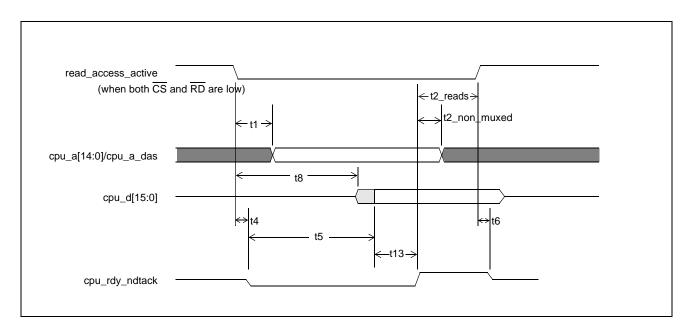

| Table 203 - Non-Multiplexed CPU Interface - Intel Mode - Read Access  | 186 |

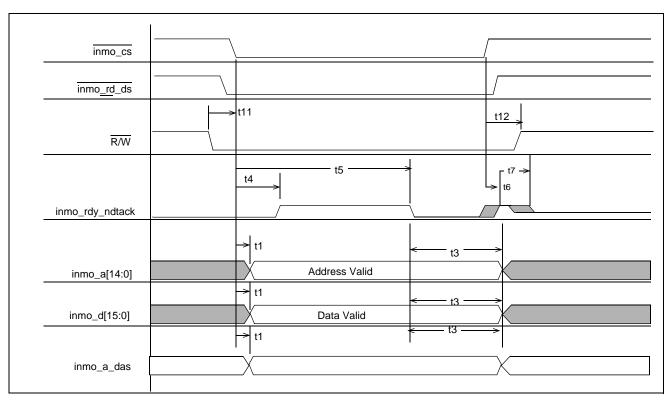

| Table 204 - Non-Multiplexed CPU Interface - Motorola Mode             | 189 |

| Table 205 - t5 Read Access Times                                      | 190 |

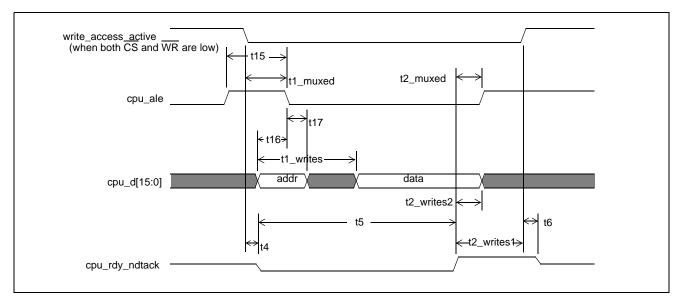

| Table 206 - Multiplexed CPU Interface - Intel Mode - Write Access     | 191 |

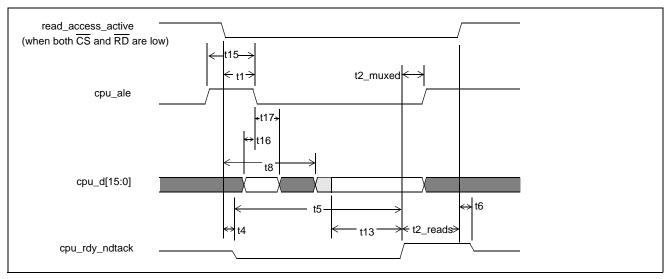

| Table 207 - Multiplexed CPU Interface - Intel Mode - Read Access      | 192 |

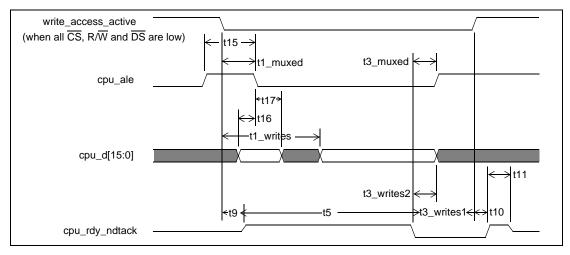

| Table 208 - Multiplexed CPU Interface - Motorola Mode - Write Access  | 193 |

| Table 209 - Multiplexed CPU Interface - Motorola Mode - Read Access   | 194 |

| Table 210 - UTOPIA Timing                                             | 195 |

| Table 211 - External Memory Timing                                    | 196 |

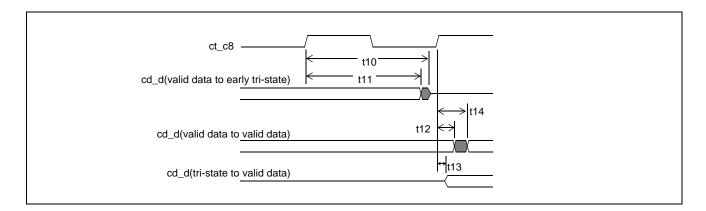

| Table 212 - H.100/H.110 Timing - H.100 Input Sampling                 |     |

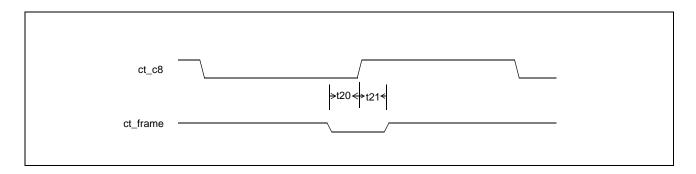

| Table 214 - H.100/H.110 Timing - H.100 Frame Sampling                 | 198 |

| Table 213 - H.100/H.110 Timing - H.100 Output                         | 198 |

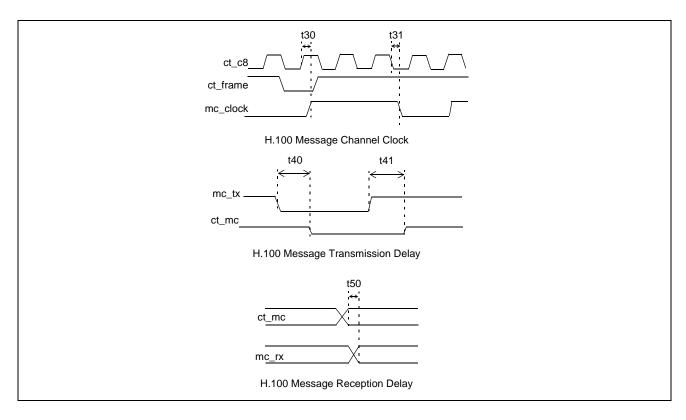

| Table 215 - H.100/H.110 Message Timing                                | 199 |

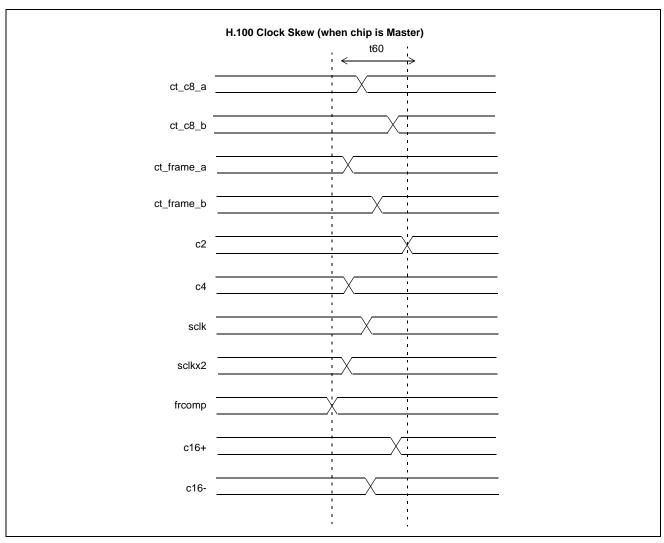

| Table 216 - H 100/H 110 Clock Skew Table                              | 200 |

### 1.0 Pin-out

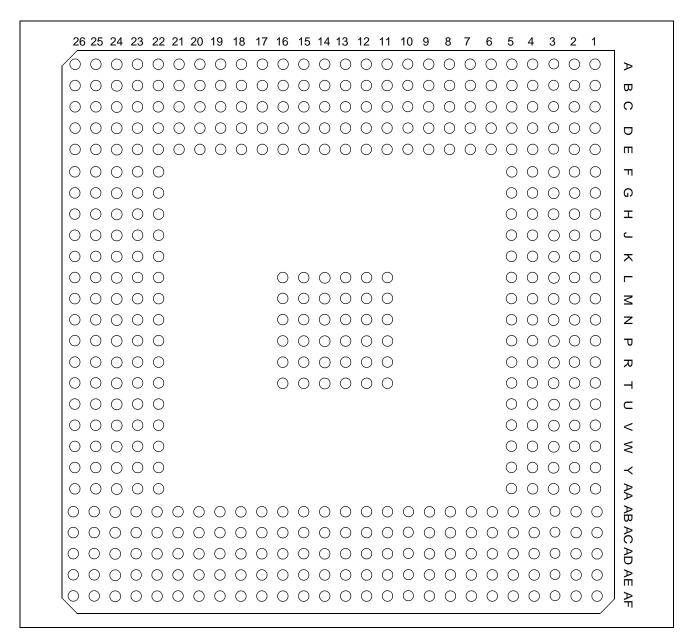

Figure 2 - 456 PBGA

The following tables contain each pin of the MT90502's main functional areas. A description of each pin is also provided.

#### Notes:

- All outputs are +3.3 V<sub>DC</sub>.

- All input and output pins that are designated (F) can withstand 5  $V_{DC}$  being applied to them.

- All input and output pins that are designated (F) are tested with a 50 pF load unless otherwise specified.

- Designations under the "rst" (reset condition) table column are: X = undefined; Z = high impedance; 1 = high (+3.3 V<sub>DC</sub>).

- I/O types include: Output (O), Input (I), Bidirectional (I/O), Power (PWR) and Ground (GND).

- All buses have pins listed in order from MSB to LSB.

- Pins with more than one function have their functions numbered.

- Unused H.100/H.110 input pins should be tied high with an external pull-up.

## 1.1 Pin Description Tables

| Pin                                                                  | rst | Name          | 1/0 | Туре           | Description                                                                                                                                                                               |

|----------------------------------------------------------------------|-----|---------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC3                                                                  |     | upclk         | I   | LVTTL (F)      | CPU Clock.                                                                                                                                                                                |

| F25, F23, J24, J23                                                   |     | cpu_mode[3:0] | - 1 | LVTTL (F)      | CPU Interface Mode Select (4 bits).                                                                                                                                                       |

| AA3, AA4, Y1, Y2, Y3,<br>Y4, W1, W2, W3, W4,<br>V1, V2, V3, V4, U1   |     | cpu_a[14:0]   | I   | LVTTL (F)      | CPU Address bus.                                                                                                                                                                          |

| T2                                                                   |     | cpu_wr_r/w    |     | LVTTL (F)      | Intel Write or Motorola Read/Write                                                                                                                                                        |

| T1                                                                   |     | cpu_rd_ds     |     | LVTTL (F)      | Intel Read or Motorola Data Strobe                                                                                                                                                        |

| U4                                                                   |     | cpu_ale       |     | LVTTL (F)      | Address Latch Enable                                                                                                                                                                      |

| Т4                                                                   |     | cpu_a_das     | I   | LVTTL (F)      | Direct Access Select. '1' selects the direct address space. '0' selects the indirection registers contained in the CPU interface. This pin can be connected to the MSB of an address bus. |

| U3                                                                   |     | cpu_cs        | I   | LVTTL (F)      | CPU chip select                                                                                                                                                                           |

| T3, R1, R2, R3, R4, P1,<br>P2, P3, P4, N1, N2, N3,<br>N4, M1, M2, M3 | Z   | cpu_d[15:0]   | I/O | LVTTL 6 mA (F) | CPU Data bus                                                                                                                                                                              |

| U2                                                                   | Z   | cpu_rdy_dtack | I/O | LVTTL 6 mA (F) | Intel Ready or Motorola Data Ack.                                                                                                                                                         |

| AC2                                                                  | Z   | interrupt1    | 0   | LVTTL 6 mA (F) | Interrupt 1 (configurable polarity)                                                                                                                                                       |

| AC1                                                                  | Z   | interrupt2    | 0   | LVTTL 6 mA (F) | Interrupt 2 (configurable polarity)                                                                                                                                                       |

Table 1 - CPU Bus Interface

| Pins | rst | Name      | I/O | Туре            | Description             |

|------|-----|-----------|-----|-----------------|-------------------------|

| C21  | Z   | txa_led   | I/O | LVTTL 12 mA (F) | UTOPIA port A TX LED    |

| A19  | Z   | rxa_led   | I/O | LVTTL 12 mA (F) | UTOPIA port A RX LED    |

| D21  |     | rxa_alarm | I   | LVTTL (F)       | UTOPIA port A PHY alarm |

**Table 2 - UTOPIA Interface Pins**

| Pins                                      | rst | Name                         | I/O | Туре            | Description                                                                                 |

|-------------------------------------------|-----|------------------------------|-----|-----------------|---------------------------------------------------------------------------------------------|

| D12                                       | Z   | txa_clk                      | I/O | LVTTL 6 mA (F)  | UTOPIA port A TX clock                                                                      |

| D14                                       | Z   | txa_soc                      | 0   | LVTTL 6 mA (F)  | UTOPIA port A TX Start of Cell                                                              |

| A13                                       | Z   | 1. txa_enb 2. txa_clav       | 0   | LVTTL 6 mA (F)  | UTOPIA port A TX Enable in ATM mode     UTOPIA port A TX Cell Available in PHY mode         |

| B13                                       |     | 1. txa_clav<br>2. txa_enb    | I   | LVTTL (F)       | UTOPIA port A TX Cell     Available in ATM mode     UTOPIA port A TX Enable in     PHY mode |

| C15, B15, A15, C14, B14, A14, D13, C13    | Z   | txa_d[7:0]                   | 0   | LVTTL 6 mA (F)  | UTOPIA port A TX Data bus                                                                   |

| D15                                       | Z   | txa_prty                     | 0   | LVTTL 6 mA (F)  | UTOPIA port A TX Parity                                                                     |

| A9                                        | Z   | rxa_clk                      | I/O | LVTTL 6 mA (F)  | UTOPIA port A RX clock                                                                      |

| C12                                       |     | rxa_soc                      | I   | LVTTL (F)       | UTOPIA port A RX Start of Cell                                                              |

| В9                                        | Z   | 1. rxa_enb 2. rxa_clav       | 0   | LVTTL 6 mA (F)  | UTOPIA port A RX Enable in ATM mode     UTOPIA port A RX Cell Available in PHY mode         |

| C9                                        |     | 1. rxa_clav<br>2. rxa_enb    | I   | LVTTL (F)       | UTOPIA port A RX Cell     Available in ATM mode     UTOPIA port A RX Enable in     PHY mode |

| A12, C11, B11, A11, D10, C10,<br>B10, A10 |     | rxa_d[7:0]                   | I   | LVTTL (F)       | UTOPIA port A RX Data bus                                                                   |

| B12                                       |     | rxa_prty                     | 1   | LVTTL (F)       | UTOPIA port A RX Parity                                                                     |

| D17                                       | Z   | txb_led                      | I/O | LVTTL 12 mA (F) | UTOPIA port B TX LED                                                                        |

| C17                                       | Z   | rxb_led                      | I/O | LVTTL 12 mA (F) | UTOPIA port B RX LED                                                                        |

| B17                                       |     | rxb_alarm                    | ı   | LVTTL (F)       | UTOPIA port B PHY alarm                                                                     |

| D5                                        | Z   | txb_clk                      | I/O | LVTTL 6 mA (F)  | UTOPIA port B TX clock                                                                      |

| D8                                        | Z   | txb_soc                      | 0   | LVTTL 6 mA (F)  | UTOPIA port B TX Start of Cell                                                              |

| A6                                        | Z   | 1. txb_enb 2. txb_clav       | 0   | LVTTL 6 mA (F)  | UTOPIA port B TX Enable in ATM mode     UTOPIA port B TX Cell Available in PHY mode         |

| B6                                        |     | 1. txb_clav<br>2. txb_enb    | I   | LVTTL (F)       | UTOPIA port B TX Cell     Available in ATM mode     UTOPIA port B TX Enable in     PHY mode |

| B8, A8, D7, C7, B7, A7, D6, C6            | Z   | txb_d[7:0]                   | 0   | LVTTL 6 mA (F)  | UTOPIA port B TX Data bus                                                                   |

| C8                                        | Z   | txb_prty                     | 0   | LVTTL 6 mA (F)  | UTOPIA port B TX Parity                                                                     |

| E4                                        | Z   | rxb_clk                      | I/O | LVTTL 6 mA (F)  | UTOPIA port B RX clock                                                                      |

| A4                                        |     | 1. rxb_soc<br>2. txa_addr[4] | I   | LVTTL (F)       | UTOPIA port B RX Start of Cell     txa_addr[4] when port A and B     are combined           |

Table 2 - UTOPIA Interface Pins (continued)

| Pins                           | rst | Name                              | I/O                              | Туре                                                                              | Description                                                                                 |  |

|--------------------------------|-----|-----------------------------------|----------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|

| D3                             | Z   | 1. rxb_enb 2. rxb_clav            | 0                                | LVTTL 6 mA (F)                                                                    | UTOPIA port B RX Enable in ATM mode     UTOPIA port B RX Cell Available in PHY mode         |  |

| C1                             |     | 1. rxb_clav<br>2. rxb_enb         | Available in A                   |                                                                                   | UTOPIA port B RX Cell     Available in ATM mode     UTOPIA port B RX Enable in     PHY mode |  |

| A2, D4, A1, B1, C2             |     | 1. rxb_d[4:0]<br>2. rxa_addr[4:0] | [4:0]<br>xa_addr[4:0]            |                                                                                   | 1. UTOPIA port B RX Data bus [4:0] 2. rxa_addr[4:0] when port A and B are combined          |  |

| A3, B3, B2                     |     | 1. rxb_d[7:5] 2. txa_addr[2:0]    | I                                | I LVTTL (F)  1. UTOPIA port B RX Da [7:5] 2. txa_addr[2:0] when po B are combined |                                                                                             |  |

| B4                             |     | 1. rxb_prty<br>2. txa_addr[3]     | I                                | LVTTL (F)                                                                         | UTOPIA port B RX Parity.     txa_addr[3] when port A and E are combined.                    |  |

| J4                             | Z   | txc_clk                           | I/O LVTTL 6 mA (F) UTOPIA port C |                                                                                   | UTOPIA port C TX clock                                                                      |  |

| D2                             | Z   | txc_soc                           | 0                                | LVTTL 6 mA (F)                                                                    | UTOPIA port C TX Start of Cell                                                              |  |

| G1                             | Z   | 1. txc_enb 2. txc_clav            | 0                                | LVTTL 6 mA (F)                                                                    | UTOPIA port C TX Enable in ATM mode     UTOPIA port C TX Cell Available in PHY mode         |  |

| G2                             |     | 1. txc_clav 2. txc_enb            | I                                | LVTTL (F)                                                                         | UTOPIA port C TX Cell     Available in ATM mode     UTOPIA port C TX Enable in PHY mode     |  |

| E3, E2, E1, F3, F2, F1, G4, G3 | Z   | txc_d[7:0]                        | 0                                | LVTTL 6 mA (F)                                                                    | UTOPIA port C TX Data bus                                                                   |  |

| D1                             | Z   | txc_prty                          | 0                                | LVTTL 6 mA (F)                                                                    | UTOPIA port C TX Parity                                                                     |  |

| L1                             | Z   | rxc_clk                           | I/O                              | LVTTL 6 mA (F)                                                                    | UTOPIA port C RX clock                                                                      |  |

| H3                             |     | rxc_soc                           | I                                | LVTTL (F)                                                                         | UTOPIA port C RX Start of Cell                                                              |  |

| L2                             | Z   | 1. rxc_enb 2. rxc_clav            | 0                                | LVTTL 6 mA (F)                                                                    | 1. UTOPIA port C RX Enable in ATM mode 2. UTOPIA port C RX Cell Available in PHY mode       |  |

| L3                             |     | 1. rxc_clav 2. rxc_enb            | I                                | LVTTL (F)                                                                         | UTOPIA port C RX Cell     Available in ATM mode     UTOPIA port C RX Enable in PHY mode     |  |

| H1, J3, J2, J1, K4, K3, K2, K1 |     | rxc_d[7:0]                        | I                                | LVTTL (F)                                                                         | UTOPIA port C RX Data bus                                                                   |  |

| H2                             |     | rxc_prty                          | I                                | LVTTL (F)                                                                         | UTOPIA port C RX Parity                                                                     |  |

Table 2 - UTOPIA Interface Pins (continued)

| Pin                                                                                                                                                                              | rst | Name       | I/O | Туре               | Description                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|--------------------|----------------------------------------------------------------------------------------------------|

| A22                                                                                                                                                                              | Z   | ct_c8_a    | I/O | LVTTL 24 mA<br>(F) | H.100 8MHz clock A                                                                                 |

| A21                                                                                                                                                                              | Z   | ct_c8_b    | I/O | LVTTL 24 mA<br>(F) | H.100 8MHz clock B                                                                                 |

| A24                                                                                                                                                                              | Z   | ct_frame_a | I/O | LVTTL 24 mA<br>(F) | H.100 Frame A                                                                                      |

| B22                                                                                                                                                                              | Z   | ct_frame_b | I/O | LVTTL 24 mA<br>(F) | H.100 Frame B                                                                                      |

| A17                                                                                                                                                                              | Z   | ct_netref1 | I/O | LVTTL 24 mA<br>(F) | H.100 Netref 1                                                                                     |

| A16                                                                                                                                                                              | Z   | ct_netref2 | I/O | LVTTL 24 mA<br>(F) | H.100 Netref 2                                                                                     |

| D18                                                                                                                                                                              | Z   | ct_mc      | I/O | LVTTL 24 mA<br>(F) | H.100 Message Channel. If this pin is connected to the H100 bus, gpio[2] must be used to drive it. |

| C25, D25, E26, E25, E24,<br>F26, F24, G26, G25, G24,<br>G23, H24, J26, J25, K26,<br>K24, L23, L24, M25, M24,<br>N25, P24, P23, R24, R25,<br>T26, U23, U26, V23, V24,<br>V26, W23 | Z   | ct_d[31:0] | I/O | PCI (F)            | H.100 serial data bus                                                                              |

| B20                                                                                                                                                                              | Z   | sclk       | 0   | LVTTL 24 mA<br>(F) | H.100 SCBUS system clock                                                                           |

| C20                                                                                                                                                                              | Z   | sclkx2     | 0   | LVTTL 24 mA<br>(F) | H.100 SCBUS system clock x 2                                                                       |

| C18                                                                                                                                                                              | Z   | c16p       | 0   | LVTTL 24 mA<br>(F) | H.100 H-MVIP 16 MHz clock positive output                                                          |

| A18                                                                                                                                                                              | Z   | c16n       | 0   | LVTTL 24 mA<br>(F) | H.100 H-MVIP 16 MHz clock negative output                                                          |

| D20                                                                                                                                                                              | Z   | c2         | 0   | LVTTL 24 mA<br>(F) | H.100 MVIP-90 2 MHz clock                                                                          |

| C19                                                                                                                                                                              | Z   | c4         | 0   | LVTTL 24 mA<br>(F) | H.100 MVIP-90 4 MHz clock                                                                          |

| B21                                                                                                                                                                              | Z   | frcomp     | 0   | LVTTL 24 mA<br>(F) | H.100 compatibility frame pulse                                                                    |

Table 3 - H.100/H.110 Interface Pins

| Pin                                                                                                                           | rst | Name          | I/O | Туре       | Description                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-----|------------|-----------------------------------------------------------------------------------------------|

| AF2                                                                                                                           |     | mem_clk       | 1   | LVTTL      | memory clock (common to both bank A and B). It is also employed as the internal master clock. |

| AF11, AD10, AF10, AD9,<br>AF9, AE8, AC7, AE7,<br>AD7, AF8, AD8, AE9,<br>AC9, AE10, AC10, AE11                                 | Z   | mema_d[15:0]  | I/O | LVTTL 6 mA | SDRAM/SSRAM bank A data bus                                                                   |

| AD11, AF7                                                                                                                     | Z   | mema_p[1:0]   | I/O | LVTTL 6 mA | SDRAM/SSRAM bank A parity bits                                                                |

| AF4, AE3                                                                                                                      | 1   | mema_cs[1:0]  | 0   | LVTTL 6 mA | SSRAM bank A Chip selects 1, 0                                                                |

| AE5                                                                                                                           | Z   | mema_r/w      | 0   | LVTTL 6 mA | SSRAM bank A Read/Write                                                                       |

| AE4, AF5                                                                                                                      | Z   | mema_bws[1:0] | 0   | LVTTL 6 mA | SSRAM bank A Byte Write Selects 1:0                                                           |

| AE12                                                                                                                          | Z   | mema_cas      | 0   | LVTTL 6 mA | SDRAM bank A Column Address Select                                                            |

| AD12                                                                                                                          | Z   | mema_ras      | 0   | LVTTL 6 mA | SDRAM bank A Row Address Select                                                               |

| AF12                                                                                                                          | Z   | mema_we       | 0   | LVTTL 6 mA | SDRAM bank A Write Enable                                                                     |

| AD6, AE6, AF6, AD5,<br>AF3, AC12, AE13, AF13,<br>AF14, AD13, AE14,<br>AC14, AE15, AC15,<br>AE16, AF16, AD15,<br>AF15, AD14    |     | mema_a[18:0]  | 0   | LVTTL 6 mA | SDRAM/SSRAM bank A address bus                                                                |

| AE22, AD22, AF24,<br>AE24, AD25, AC25,<br>AB24, AB26, AB25,<br>AC26, AD26, AE26,<br>AE23, AF23, AD21, AE21                    | Z   | memb_d[15:0]  | I/O | LVTTL 6 mA | SDRAM/SSRAM bank B data bus                                                                   |

| AF22, AA24                                                                                                                    | Z   | memb_p[1:0]   | I/O | LVTTL 6 mA | SDRAM/SSRAM bank B parity bits                                                                |

| W25, W26                                                                                                                      | 1   | memb_cs[1:0]  | 0   | LVTTL 6 mA | SSRAM bank B Chip selects 1,0                                                                 |

| Y25                                                                                                                           | Z   | memb_r/w      | 0   | LVTTL 6 mA | SSRAM bank B Read/Write                                                                       |

| W24, Y26                                                                                                                      | Z   | memb_bws[1:0] | 0   | LVTTL 6 mA | SSRAM bank B Byte Write Selects 1,0                                                           |

| AC20                                                                                                                          | Z   | memb_cas      | 0   | LVTTL 6 mA | SDRAM bank B Column Address Select                                                            |

| AD20                                                                                                                          | Z   | memb_ras      | 0   | LVTTL 6 mA | SDRAM bank B Row Address Select                                                               |

| AF21                                                                                                                          | Z   | memb_we       | 0   | LVTTL 6 mA | SDRAM bank B Write Enable                                                                     |

| AA25, AA26, Y23, Y24,<br>AC21, AE20, AC19,<br>AF20, AE19, AD19,<br>AF19, AE18, AC17,<br>AE17, AD16, AF17,<br>AD17, AF18, AD18 |     | memb_a[18:0]  | 0   | LVTTL 6 mA | SDRAM/SSRAM bank B address bus                                                                |

**Table 4 - Memory Interface Pins**

| Pin                                              | rst | Name      | 1/0 | Туре              | Description                        |

|--------------------------------------------------|-----|-----------|-----|-------------------|------------------------------------|

| AA1                                              |     | reset     | I   | LVTTL (F)         | Global Hardware Reset (active low) |

| AF26, AC24, AB23,<br>AA23, T24, R26, N23,<br>M23 | Z   | gpio[7:0] | I/O | LVTTL 6 mA<br>(F) | General Purpose I/Os               |

Table 5 - Miscellaneous Pins

| Pin | Name | I/O | Туре           | Description           |

|-----|------|-----|----------------|-----------------------|

| A26 | trst | I   | LVTTL (F)      | JTAG Test Reset       |

| D22 | tck  | I   | LVTTL (F)      | JTAG Test Clock       |

| A25 | tdi  | I   | LVTTL (F)      | JTAG Test Data In     |

| C23 | tms  | ļ   | LVTTL (F)      | JTAG Test Mode Select |

| A23 | tdo  | 0   | LVTTL 6 mA (F) | JTAG Test Data Out    |

**Table 6 - JTAG Pins**

| Pin | Name    | I/O | Туре      | Description                                                                                               |

|-----|---------|-----|-----------|-----------------------------------------------------------------------------------------------------------|

| AB2 | pll_clk | I   | LVTTL (F) | PLL reference clock used for H.100 Master clock generation                                                |

| A5  | PLLVDD1 |     |           | PLL Power Pin (3.3 V). Place one.01 uF, one 10 uF and one 100 pF capacitor near PLL_VDD1 / PLL_GND1 pins. |

| AB3 | PLLVDD2 |     |           | PLL Power Pin (3.3V). Place one.01 uF, one 10 uF and one 100 pF capacitor near PLL_VDD2 / PLL_GND2 pins.  |

| AE2 | PLLVDD3 |     |           | PLL Power Pin (3.3 V). Place one.01 uF, one 10 uF and one 100 pF capacitor near PLL_VDD3 / PLL_GND3 pins. |

| B5  | PLLGND1 |     |           | PLL Ground Pin (0 V).                                                                                     |

| AB1 | PLLGND2 |     |           | PLL Ground Pin (0 V).                                                                                     |

| AE1 | PLLGND3 |     |           | PLL Ground Pin (0 V).                                                                                     |

Table 7 - Phase Lock Loop (PLL) Pins

VSS (0 V): D9, D11, E5, E6, E9, E10, E13, E14, E17, E18, E21, E22, F4, F5, F22, H4, J5, J22, K5, K22, L4, L11, L12, L13, L14, L15, L16, M4, M11, M12, M13, M14, M15, M16, N5, N11, N12, N13, N14, N15, N16, N22, P5, P11, P12, P13, P14, P15, P16, P22, R11, R12, R13, R14, R15, R16, T11, T12, T13, T14, T15, T16, U5, U22, V5, V22, AA5, AA22, AB5, AB6, AB9, AB10, AB13, AB14, AB17, AB18, AB21, AB22, AF25.

### Table 8 - VSS (0 V) Pins

VDD3 (3.3 V): C3, C24, D23, E7, E8, E11, E12, E15, E16, E19, E20, G5, G22, H5, H22, L5, L22, M5, M22, R5, R22, T5, T22, W5, W22, Y5, Y22, AB7, AB8, AB11, AB12, AB15, AB16, AB19, AB20, AC4, AC23, AD3, AD24, AF1

### Table 9 - VDD3 (3.3 V) Pins

Note: If MT90502 is only connected to 3.3 V devices on the H.100/H.110 bus, then 3.3 V can be connected to the following pins. If any devices are 5 V then these pins must be connected to 5 V.

VDD5 (3.3 V or 5.0 V): B25, D24, H26, L26, P25, U24

#### Table 10 - VDD5 (3.3 V or 5.0 V) Pins

Not Connected (Leave Floating): A20, B16, B18, B19, B23, B24, B26, C4, C5, C16, C22, C26, D16, D19, D26, E23, H23, H25, K23, K25, L25, M26, N24, N26, P26, R23, T23, T25, U25, V25, AA2, AB4, AC5, AC6, AC8, AC11, AC13, AC16, AC18, AC22, AD1, AD2, AD4, AD23, AE25

Table 11 - Not Connected (Leave Floating) Pins

| Туре          | Input | Output | I/O | Power | Ground | N/C | Total |

|---------------|-------|--------|-----|-------|--------|-----|-------|

| CPU Bus       | 25    | 2      | 17  |       |        |     | 44    |

| UTOPIA Port A | 13    | 12     | 4   |       |        |     | 29    |

| UTOPIA Port B | 13    | 12     | 4   |       |        |     | 29    |

| UTOPIA Port C | 12    | 12     | 2   |       |        |     | 26    |

| H.100/H.110   | 0     | 7      | 39  |       |        |     | 46    |

| Memory        | 1     | 54     | 36  |       |        |     | 91    |

| Miscellaneous | 1     | 0      | 8   |       |        |     | 9     |

| JTAG          | 4     | 1      | 0   |       |        |     | 5     |

| PLL           | 1     | 0      | 0   | 3     | 3      |     | 7     |

| Power         |       |        |     | 46    |        |     | 46    |

| Ground        |       |        |     |       | 79     |     | 79    |

| No Connect    |       |        |     |       |        | 45  | 45    |

| Total:        | 71    | 101    | 110 | 48    | 81     | 45  | 456   |

Note: Pins are listed under their main (default) function for UTOPIA ports A and B

**Table 12 - Pinout Summary**

## 2.0 Functional Description

#### 2.1 CPU Interface

The MT90502 CPU module provides an interface permitting programmability from an external microprocessor or CPU. The CPU module permits read/write access to the MT90502's internal registers, internal memory and external memories.

The CPU interface is comprised of the following:

- [1] Direct Access Select (DAS) as the MSB bit concatenated with a 15-bit address bus

- [2] 16-bit data bus

- [3] 2 interrupt signals

- [4] associated control signals.

The CPU interface can be configured to operate in either Intel or Motorola mode. The MT90502 supports both 8-bit or 16-bit data bus and multiplexed or non-multiplexed address/data pins.

If the CPU is operating in 16-bit byte mode with the LSB of its address bus as a byte field, then the cpu\_a[14:0] pins of the MT90502 can be connected to the a[15:1] pins of the CPU. If both the MT90502 and the CPU are in 16-bit word mode, then the cpu\_a[14:0] pins should be connected to the a[14:0] pins of the CPU.

A reduced set of registers, the 'CPU Interface Registers' (000h to 00Ah), are employed to optimise access time and to permit the CPU to execute indirect read/write accesses. The CPU also engages these registers to perform direct read/write accesses. The MT90502 and CPU timing relationship is described in Section 4.3, "Intel/Motorola Interface," on page 185.

The CPU Control Register (100h) provides a software reset capability that allows the CPU to reset the MT90502 except for the CPU interface. The CPU interface can only be reset by a hardware reset.

### 2.1.1 CPU Interrupts

The CPU interface provides a programmable global interrupt capability. The interrupt signal names are 'interrupt1' and 'interrupt2', pins AC2 and AC1 respectively. Both interrupts have programmability to select their polarity (open collector drive) via registers 'interrupt1\_conf' and 'interrupt2\_conf', addresses 214h and 216h respectively. Interrupt1 provides the capability to program a minimum acceptable period between interrupts. The period is programmed in  $\mu$ s units via the 'interrupt1\_conf' register. This provides a 'frequency interrupt controller' facility and masks the assertion of further interrupts until the specified period of time has elapsed. The mask period will start when the interrupt1\_treated [15] bit in the register 'interrupt\_flags' (address 210h) is set. When Interrupt2 is enabled it is always activated when an interrupt condition occurs.

The operation of the CPU interrupt network is common for all modules. When an interrupt is asserted, an interrupt flag is set to identify the module where the interrupt was generated. Each module has one or more Interrupt Enable Registers where a set interrupt enable bit enables an interrupt source. On completion of the ISR the interrupt must be cleared as the interrupt will remain asserted until it is de-asserted by the user. All Interrupt Enable Registers have a mirror Status Register. Hence, the bit positioning of the interrupt enables and the corresponding status bits are identical.

Note: Interrupt pins are always tri-stated when inactive.

### 2.1.1.1 Example Interrupt Flow

Upon the initialisation of the Global Interrupt pins the following methodology is adopted to identify the source of the interrupt. For this example Interrupt2 is employed and the CPU module will be the source of the interrupt.

#### Interrupt Initialization

- Set interrupt polarity, register interrupt2\_conf[15:14].

- Enable Interrupt2 for the CPU module by setting bit 0 in interrupt2\_enable register (21Ah). The MT90502 will generate an interrupt on interrupt2 according to the modules enabled in interrupt2\_enable.

- Set the individual CPU interrupt sources by enabling the respective bits in the 'status0\_ie' register (104h). Within the 'status0\_ie' register there are two possible interrupt sources: internal\_read\_timeout\_ie and cpu\_read\_done\_ie. In the MT90502 Register Description the interrupt bits are labelled IE (Interrupt Enable) in the 'Type' column. This register offers the facility to mask/disable unwanted interrupts.

### **Interrupt Servicing**

When interrupt2 is asserted ('interrupt2' pin):

- Read the interrupt flags to ascertain the module raising the interrupt. The CPU module interrupt flag is located in register interrupt\_flags (210h), this bit is named cpureg\_interrupt\_active.

- If the cpureg\_interrupt\_active bit is set, locate the source of the CPU interrupt by reading the 'status0' at 102h, either internal\_read\_timeout and/or cpu\_read\_done.

- To de-assert the interrupt the user must write a 1 to register 102h bits 3 and/or 4, internal\_read\_timeout and cpu\_read\_done respectively. Only then will the interrupt be de-asserted.

#### 2.1.2 Intel/Motorola Interface

| 000h | Control Register         |

|------|--------------------------|

| 004h | Read/Write Data Register |

| 008h | Address High Register    |

| 00Ah | Address Low Register     |

The MT90502 CPU interface supports both Intel and Motorola modes with an 8-bit or 16-bit data bus and multiplexed or non-multiplexed address/data pins. The MT90502 supports 68 MB of addressable space, therefore indirection addressing is necessary. The CPU interface directly addresses four control words, delegated for indirection accessing. The Indirection Register contents are shown in Table 14 to Table 17 inclusively. The timing relationship pertaining to the CPU Interface Registers and Extended Access is defined in Section 4.3 on page 185.

| cpu_mode<br>[3:0] | Interface Type                             | ale      | address pins                                    | data pins   | direct_access |

|-------------------|--------------------------------------------|----------|-------------------------------------------------|-------------|---------------|

| 0000              | Intel, 16 bit data bus,<br>non-multiplexed | cpu_ale* | cpu_a[14:0]**<br>(word address)                 | cpu_d[15:0] | cpu_a_das     |

| 0001              | Intel, 16 bit data bus,<br>multiplexed     | cpu_ale* | cpu_d[15:1]**<br>(word address)                 | cpu_d[15:0] | cpu_a_das     |

| 0010              | Intel, 8 bit data bus,<br>non-multiplexed  | cpu_ale* | cpu_a[14:0]** (byte<br>address)                 | cpu_d[7:0]  | cpu_a_das     |

| 0011              | Intel, 8 bit data bus,<br>multiplexed      | cpu_ale* | cpu_a[14:8]** &<br>cpu_d[7:0]<br>(byte address) | cpu_d[7:0]  | cpu_a_das     |

| 0100              | Motorola, 16 bit data bus, non-multiplexed | cpu_ale* | cpu_a[14:0]**<br>(word address)                 | cpu_d[15:0] | cpu_a_das     |

| 0101              | Motorola, 16 bit data bus, multiplexed     | cpu_ale* | cpu_d[15:1]**<br>(word address)                 | cpu_d[15:0] | cpu_a_das     |

| 0110              | Motorola, 8 bit data bus, non-multiplexed  | cpu_ale* | cpu_a[14:0]** (byte<br>address)                 | cpu_d[7:0]  | cpu_a_das     |

| 0111              | Motorola, 8 bit data<br>bus, multiplexed   | cpu_ale* | cpu_a[14:8]**&<br>cpu_d[7:0]<br>(byte address)  | cpu_d[7:0]  | cpu_a_das     |

| 1xxx              | Reserved                                   |          |                                                 |             |               |

<sup>\*</sup> The cpu\_ale pin is interpreted in all modes. However, it is not necessary in the non-multiplexed modes and can be tied to VCC.

**Table 13 - CPU Interface Mode Selection**

| Field             | Bit  | Туре | Reset | Description                                                                                                                                     |

|-------------------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| read_burst_length | 6:0  | RW   | 01h   | Number of words to prefetch: $00h = 128$ ; $01h = 1$ ; $02h = 2$ , etc. This field is set to 01h for individual (non-sequential) reads.         |

| reserved          | 7    | RO   | 0h    | Reserved.                                                                                                                                       |

| access_req        | 8    | PC   | 0h    | Set by software when an extended access is initialized. Reset by hardware when the access is completed. Used for extended indirect access only. |

| extended_a[3:1]   | 11:9 | RW   | 0h    | Extended address bits 3:1. Invalid for extended direct access.                                                                                  |

Table 14 - Control Register (000h)

<sup>\* \*</sup>The address placed on the cpu\_a[14:0] pin is a word address in 16-bit mode and a byte address in 8-bit mode. The address, when placed on the cpu\_d pins, is always a byte address.

| write_enable    | 13:12 | RW | 0h | Active high write enables.  00 = read access.  01 = write to lower byte.  10 = write to upper byte.  11 = write to entire word.  This field is ignored for extended direct reads and all byte wide extended direct accesses. |

|-----------------|-------|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| extended_parity | 15:14 | RW | 0h | Read/Write Parity bits.                                                                                                                                                                                                      |

Table 14 - Control Register (000h)

| Field               | Bit  | Туре | Reset | Description                                                                              |

|---------------------|------|------|-------|------------------------------------------------------------------------------------------|