### **RF2642** 3V 900 MHz UPCONVERTER/ DRIVER AMPLIFIER WITH BYPASS MODE

RoHS Compliant & Pb-Free Product Package Style: QFN, 16-Pin, 4x4

### Features

- Single Supply 3.0V Operation

- Step Gain Control

- Power Down Control

- ACPR1=61dBc@885kHz with P<sub>OUT</sub>=+5dBm

- Small QFN 16-Pin Package

### **Applications**

- CDMA/AMPS Cellular Systems

- TDMA/AMPS Cellular Systems

- General Purpose Upconverter/Driver

- Portable Battery-Powered Equipment

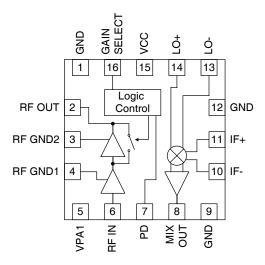

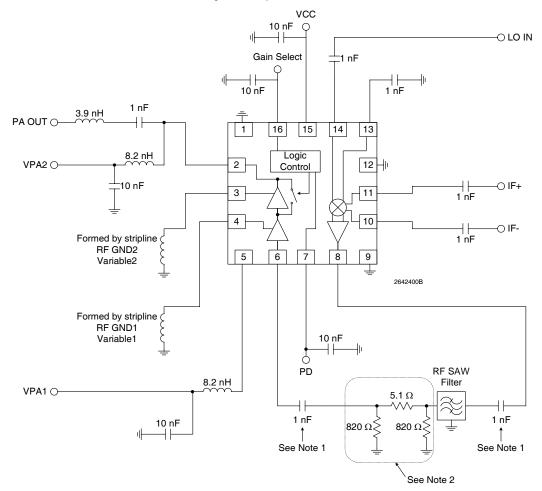

Functional Block Diagram

### **Product Description**

The RF2642 is a complete upconverter and power amplifier driver designed for CDMA applications. The design features driver amplifier high and low gain states. In the low gain state, the gain is adjustable and the device draws less current. The upconverter is always on. The power down mode turns off the driver amplifier. The device features balanced IF inputs, single-ended LO input and RF output for ease of interface. Packaged in an industry standard 4mmx4mm, 16-pin, leadless chip carrier, the device provides a low-cost solution while easing board space limitations.

#### **Ordering Information**

RF2642 RF2642PCBA-41X

3V 900MHz Upconverter/ Driver Amplifier with Bypass Mode Fully Assembled Evaluation Board

#### **Optimum Technology Matching® Applied**

| 🗌 GaAs HBT  | □_SiGe BiCMOS | 🗌 GaAs pHEMT | 🗌 GaN HEMT |

|-------------|---------------|--------------|------------|

| GaAs MESFET | 🗹 Si BiCMOS   | Si CMOS      |            |

| 🗌 InGaP HBT | SiGe HBT      | 🗌 Si BJT     |            |

RF MICRO DEVICES®, RFMD®, Optimum Technology Matching®, Enabling Wireless Connectivity<sup>M</sup>, PowerStar®, POLARIS<sup>M</sup> TOTAL RADIO<sup>M</sup> and UltimateBlue<sup>M</sup> are trademarks of RFMD, LLC. BLUETOOTH is a trade mark owned by Bluetooth SIG, Inc., U.S.A. and licensed for use by RFMD. All other trade names, trademarks and registered trademarks are the property of their respective owners. @2006. RF Micro Devices. Inc.

7628 Thorndike Road, Greensboro, NC 27409-9421 · For sales or technical support, contact RFMD at (+1) 336-678-5570 or sales-support@rfmd.com.

#### **Absolute Maximum Ratings**

| Parameter                     | Rating       | Unit            |

|-------------------------------|--------------|-----------------|

| Supply Voltage                | -0.5 to +4.5 | V <sub>DC</sub> |

| Input RF Power                | +3           | dBm             |

| Operating Ambient Temperature | -30 to +85   | °C              |

| Storage Temperature           | -30 to +150  | °C              |

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EUDirective2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application or circuitry and specifications at any time without prior notice.

| Devementer                                   | Specification |            | Unit | Condition |                                                                                           |  |

|----------------------------------------------|---------------|------------|------|-----------|-------------------------------------------------------------------------------------------|--|

| Parameter                                    | Min.          | Min. Typ.  |      | Unit      | Condition                                                                                 |  |

| Overall                                      |               |            |      |           | T=25 ° C, V <sub>CC</sub> =3.0V, RF <sub>OUT</sub> =830MHz,<br>L0=960MHz@-3dBm, IF=130MHz |  |

| RF Output Frequency Range                    |               | 824 to 849 |      | MHz       |                                                                                           |  |

| IF Frequency Range                           |               | 130        |      | MHz       |                                                                                           |  |

| Output Power                                 | +5            |            |      | dBm       | CW                                                                                        |  |

| High Gain Mode                               |               |            |      |           | GAIN SELECT=2.7 V, V <sub>PD</sub> =2.7 V                                                 |  |

| Gain                                         | 33            | 34.5       | 36   | dB        |                                                                                           |  |

| Noise Figure                                 |               | 12         | 14   | dB        |                                                                                           |  |

| IF Input Impedance                           |               | 250        |      | Ω         | Differential @ 130MHz                                                                     |  |

| RF Output VSWR                               |               | 1.5        | 2:1  |           | 824MHz to 849MHz, external components required                                            |  |

| Current Consumption                          |               | 52         |      | mA        |                                                                                           |  |

| Adjacent Channel Power<br>Rejection (ACPR1)  | 55            | 61         |      | dBc       | P <sub>OUT</sub> =+5dBm, 885kHz offset                                                    |  |

| Alternate Channel Power<br>Rejection (ACPR2) | 65            | 78         | 80   | dBc       | P <sub>OUT</sub> =+5dBm, 1.98MHz offset                                                   |  |

| Bypass Mode                                  |               |            |      |           | GAIN SELECT=0V, V <sub>PD</sub> =2.7V                                                     |  |

| Gain                                         |               | 11.9       |      | dB        |                                                                                           |  |

| Noise Figure                                 |               | 11.9       | 14   | dB        |                                                                                           |  |

| IF Input Impedance                           |               | 250        |      | Ω         | Differential @ 130MHz                                                                     |  |

| RF Output VSWR                               |               | 1.5        | 2:1  |           | 824MHz to 849MHz, external components required                                            |  |

| Output IP3                                   | -4            | +5.4       |      | dBm       |                                                                                           |  |

| Current Consumption                          |               | 26         |      | mA        |                                                                                           |  |

| LO Input                                     |               |            |      |           | 954MHz to 979MHz                                                                          |  |

| LO Frequency Range                           |               | 954 to 979 |      | MHz       |                                                                                           |  |

| LO Level                                     | -6            | -3         | 0    | dBm       |                                                                                           |  |

| LO Input Impedance                           |               | 50         |      | Ω         |                                                                                           |  |

| LO to Mixer RF Output Leakage                |               | -33        | -20  | dBm       |                                                                                           |  |

| LO Input VSWR                                |               | 1.4        | 2:1  |           | GAIN SELECT=0V                                                                            |  |

|                                              |               | 1.7        | 2:1  |           | GAIN SELECT=2.7V                                                                          |  |

| Power Supply                                 |               |            |      |           |                                                                                           |  |

| Voltage                                      | 2.7           | 3.0        | 3.3  | V         |                                                                                           |  |

| Current Consumption                          |               |            | 18   | mA        | V <sub>PD</sub> =0V                                                                       |  |

NOTE: The measured results <u>do not</u> include the losses from the IF balun and SAW filter. On the evaluation board, those losses are as follows: IF Balun=1dB, SAW Filter=2.5dB to 3.5dB.

rfmd.com

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Interface Schematic       |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1   | GND      | Ground connection. For best performance, keep traces physically short<br>and connect immediately to ground plane. This pin is internally connected<br>to the die flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| 2   | RF OUT   | Output match of the second stage of the power amplifier driver. This amplifier output pin is open collector. It is matched to $50\Omega$ externally using a simple LC match. Refer to the application schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Gain<br>Select<br>ORF OUT |

| 3   | RF GND2  | The ground connection for the second stage of the power amplifier driver. The inductance between this pin and the ground plane determines the gain of the second stage. Increased inductance results in reduced gain. On the evaluation board, the emitter ground inductance is set by the length of the PCB trace connected between this pin and the ground. By sliding a 0 $\Omega$ ground jumper along this line, the inductance, and hence the gain, may be varied. The evaluation board is shipped with the 0 $\Omega$ jumper very close to the part, resulting in minimum inductance, and therefore maximum second stage gain. This translates to higher output IP3 and maximum ACPR1. This setting results in performance 6dB better than the ACPR1 minimum specification of 50dBc in the CDMA IS-95 specification for a P <sub>OUT</sub> =+5dBm. | PCB<br>Trace              |

| 4   | RF GND1  | The ground connection for the first stage of the power amplifier driver. The inductance between this pin and the ground plane determines the gain of the first stage. Increased inductance results in reduced gain. On the evaluation board, the emitter ground inductance is set by the length of the PCB trace connected between this pin and the ground. By sliding a $0\Omega$ ground jumper along this line, the inductance, and hence the gain, may be varied. The evaluation board is shipped with the $0\Omega$ jumper far away from the part, resulting in maximum inductance, and therefore minimum first stage gain. More gain may be obtained by shifting the $0\Omega$ jumper toward the part. A maximum total gain of 40dB may be achieved if the first stage is set to minimum emitter inductor trace length.                             | See pin 3.                |

| 5   | VPA1     | Power supply pin for the first stage power amplifier. External components provide tuning for the interstage match.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |

| 6   | RF IN    | RF input to the power amplifier. This input is DC-coupled, so an external blocking capacitor is needed if the pin is connected to a DC path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bias VPA1                 |

| 7   | PD       | Power Down control When this pin is low, the amplifier section of the IC is shut off. When this pin is high, the amplifier section of the IC is turned on. The upconverter portion of the IC remains on regardless of the state of PD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| 8   | ΜΙΧ ΟυΤ  | Output for the upconverting mixer. This input is DC-coupled, so an external blocking capacitor is needed if the pin is connected to a DC path. The output impedance is $50\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           |

| 9   | GND      | Same as pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

RFMD w

| Pin         | Function    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Interface Schematic |

|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 10          | IF-         | Balanced IF Input Pin. This pin is internally DC-biased and should be DC-blocked if connected to a device with a DC level present. For single-ended input operation, one pin is used as an input and the other IF input is AC coupled to ground. The input impedance is $250\Omega$ in both the balanced and single-ended modes.                                                                                                                                       | IF+0                |

| 11          | IF+         | Same as pin 10, except complementary input.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 12          | GND         | Ground connection. For best performance, keep traces physically short and connect immediately to ground plane.                                                                                                                                                                                                                                                                                                                                                         |                     |

| 13          | LO-         | Balanced LO Input Pin. This pin is internally DC-biased and should be DC-<br>blocked if connected to a device with a DC level present. For single-ended<br>input operation, one pin is used as an input and the other LO input is AC<br>coupled to ground. The input impedance is $50\Omega$ in both the balanced and<br>single-ended modes.                                                                                                                           |                     |

| 14          | LO+         | Same as pin 13, except complementary input.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 15          | VCC         | Supply voltage for all bias circuits and logic circuits.                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

| 16          | GAIN SELECT | When GAIN SELECT is high: the driver amplifier is switched to high gain mode; both amplifier stages are active; the gain is maximized; and, the entire device draws approximately 51mA. When GAIN SELECT is low, the second stage of the PA driver is turned off and bypassed. This results in a device current of 26mA, which is approximately a 50% current reduction. The upconverting mixer remains on in both the high and low gain modes to prevent VCO pulling. |                     |

| Pkg<br>Base | GND         | Ground connection. The backside of the package should be soldered to a top side ground pad which is connected to the ground plane with multiple vias.                                                                                                                                                                                                                                                                                                                  |                     |

| PD | Gain<br>Select | Mixer | Amplifier<br>First Stage | Amplifier<br>Second Stage | Gain<br>(dB)* |

|----|----------------|-------|--------------------------|---------------------------|---------------|

| 0  | 0              | ON    | OFF                      | OFF                       |               |

| 0  | 1              | ON    | OFF                      | OFF                       |               |

| 1  | 0              | ON    | ACTIVE                   | BYPASSED                  | 11.9          |

| 1  | 1              | ON    | ACTIVE                   | ACTIVE                    | 34.5          |

\*See parameter specifications for conditions.

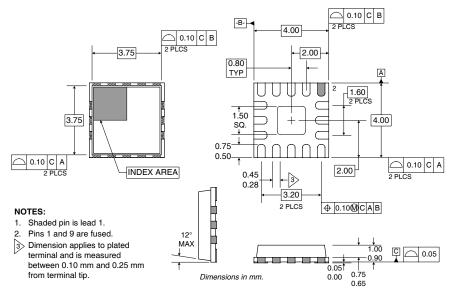

### **Package Drawing**

## **Application Schematic**

NOTE:

1 nF: DC blocking capacitor - this can be removed if the filter is DC blocked.

T-attenuator - this is to control the overall gain of the upconverter + PA driver. This can be set to zero if it is desired.

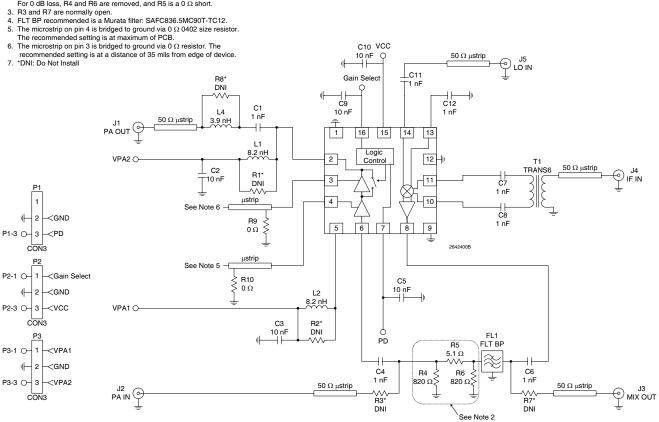

### **Evaluation Board Schematic**

NOTE:

- 1. R1, R2 and R8 are optional. 2. R4, R5 and R6 form T-attenuator with a loss of 1 dB. For 0 dB loss, R4 and R6 are removed, and R5 is a 0  $\Omega$  short.

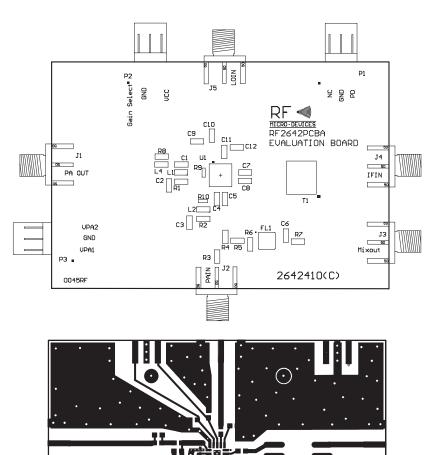

### Evaluation Board Layout Board Size 2.981" x 2.981" Board Thickness 0.031", Board Material FR-4

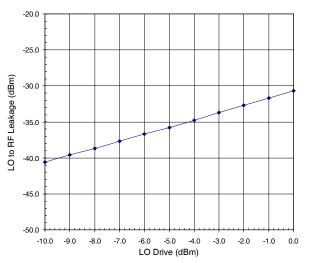

LO to RF Leakage for Upconverter Mixer Alone

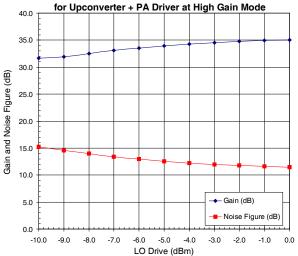

Gain and Noise Figure versus LO Drive at  $V_{cc}$ =3.0V

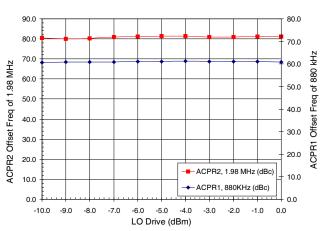

ACPR1 and ACPR2 versus LO Drive at  $V_{CC}$ =3.0V for Upconverter + PA Driver at High Gain Mode

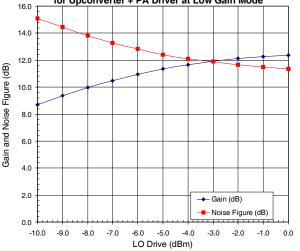

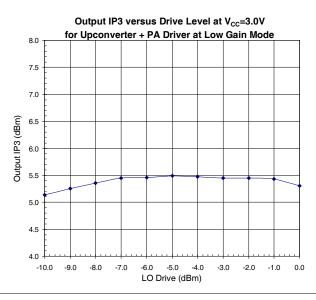

Gain and Noise Figure versus LO Drive at V<sub>cc</sub>=3.0V for Upconverter + PA Driver at Low Gain Mode