# PRELIMINARY DATA SHEET

# CCD595 9216 x 9216 Pixel Image Area Full Frame CCD Image Sensor

#### **FEATURES**

- 9216 x 9216 Full Frame CCD Array

- 8.75 μm x 8.75 μm Pixels

- 80.64mm x 80.64mm Image Area

- 100% Fill Factor

- Non Multi-Pinned Phase (MPP) Operation

- 8 Outputs (4 on each side)

- Readout Noise Less Than 30 e at 100MHz (25MHz x 4)

#### **GENERAL DESCRIPTION**

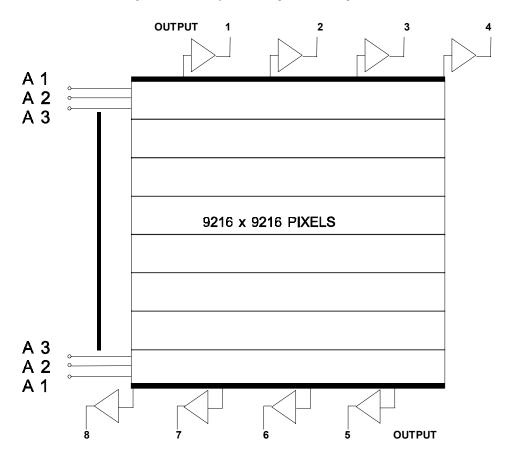

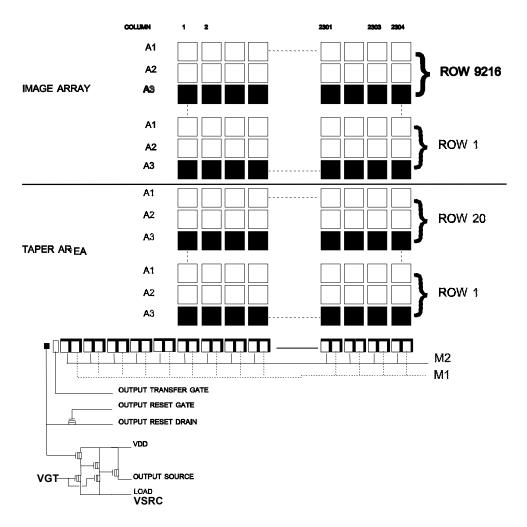

The CCD595 is a 9216 x 9216 active element solid state Charge Coupled Device (CCD) Full Frame sensor. The CCD is intended for advanced scientific, space, and aerial reconnaissance applications. The CCD595 is organized as an array of 9216 horizontal by 9216 vertical imaging elements. The pixel pitch is 8.75µm with a 100% fill factor. Three-phase clocking is employed in the imaging area with two-phase clocking in the serial readout registers. Image readout is performed via 4 serial registers containing 19 isolation rows between imaging and readout sections. The imaging array can be clocked unidirectional (4-output configuration) or bi-directional (8-output configuration). The imaging area segments are split in mid-array for the latter configuration. To maximize the exposure/readout cycle rate, concurrent array and serial register clocking is utilized. Fast transfer clocking between the array and serial registers is accomplished with strapped transfer gates that load each line in less than 5 microseconds.

The output circuit architecture features eight (four active, eight optional) three stage source follower readouts. The nominal read noise of the output amplifiers is less than 25 electrons at 25MHz. The combined data rates for 4 and 8 output configurations are 100MHz and 200MHz respectively. Internal temperature and humidity sensors are also located near the FPA for external monitoring.

The top of the package has an optical window over the CCD active area. The CCD595 is mounted in an environmentally sealed enclosure containing the CCD array with thermoelectric coolers for controlling the operating temperature of the array.

Pinouts are provided on three sides for electrical connections (4-output configuration). The package base serves as the heat sink interface for thermal management. A mounting flange at the package rim is used as a Z-axis reference datum for the planarization of the CCD focal plane with external optics.

# DC OPERATING CHARACTERISTICS

| SYMBOL          | PARAMETER               | RANGE |      |       | UNIT   | REMARKS |

|-----------------|-------------------------|-------|------|-------|--------|---------|

|                 |                         | MIN   | NOM  | MAX   |        |         |

| $V_{DD}$        | DC Supply Voltage       | 18.0  | 20.0 | 23.0  | V      |         |

| $V_{RD}$        | Reset Drain Voltage     | 14.0  | 17.0 | 20.0  | V      |         |

| $V_{OG}$        | Output Gate Voltage     | 0.0   | 1.0  | 5.0   | V      |         |

| V <sub>SS</sub> | Substrate Ground        |       | 0.0  |       | V      |         |

| $V_{odc}$       | Output DC Level         | VRD-5 |      | VRD-4 | V      |         |

| Z               | Suggested Load Resistor | 0.8   | 1.0  | 1.8   | K ohms |         |

# **TYPICAL CLOCK VOLTAGES**

| SYMBOL                              | PARAMETER                                                                                                             | HIGH            | LOW            | UNIT   | REMARKS                  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------|--------------------------|

| Vφ <sub>H(1,2),</sub><br>φSG        | Horizontal Transport Clock Voh Max-Min                                                                                | +7.5<br>+10     | -7.5           | V<br>V | +4.5, -0.5 Typical       |

| V <sub>0</sub> V <sub>(1,2,3)</sub> | Vertical Transport Clocks                                                                                             | +8.0            | -10.0          | V      | +5, -10 V Typical        |

| VφR                                 | Reset Gate Clock                                                                                                      | +15.0           | 0.0            | V      | +2.0 +8.0 V Typical      |

| Vφ <sub>VTG (2,3)</sub>             | Array Transfer Gate Clock                                                                                             | +8.0            | -10.0          | V      | +5, -10 Typical          |

| СфV <sub>(1,2,3)</sub>              | Vertical Array Gates $A_1$<br>Cap. (per $\phi$ V) $A_2$<br>$A_3$                                                      | 47<br>86<br>109 | 30<br>38<br>31 | nF     | Min @ +10V<br>Max @ -10V |

| C∳VTG <sub>2,3</sub>                | $ \begin{array}{ccc} \text{Array Transfer Gate} & \text{TG}_2 \\ \text{Cap. (per pin)} & \text{TG}_3 \\ \end{array} $ | 200<br>200      | 150<br>150     | pF     | Min @ +10V<br>Max @ -10V |

| СфН (1,2)                           |                                                                                                                       | 65<br>76        |                | pF     | Min @ +10V<br>Max @ -10V |

| СфН                                 |                                                                                                                       | 65<br>76        |                | pF     | Min @ +10V<br>Max @ -10V |

Note 1:  $\phi H = 400 \text{ pF}$ ,  $\phi V = 60,000 \text{ pF}$ . All clock rise and fall times should be > 10 ns.

# PRELIMINARY DATA SHEET

#### PERFORMANCE SPECIFICATIONS

| SYMBOL            | PARAMETER                                       | RANGE   |         |     | UNIT               | REMARKS                          |

|-------------------|-------------------------------------------------|---------|---------|-----|--------------------|----------------------------------|

|                   |                                                 | MIN     | NOM     | MAX |                    |                                  |

| V <sub>sat</sub>  | Saturation Output Voltage                       | 350     | 600     | 800 | mV                 | Note 1                           |

| Q <sub>sat</sub>  | Full Well Capacity (98% of Pixels)              | 70,000  |         |     | e-                 | Note 1                           |

| S <sub>V</sub>    | Output Amp Sensitivity                          |         | 8.0     |     | μV/e-              |                                  |

| H <sub>sat</sub>  | Horizontal Register Capacity                    |         | 130,000 |     | e-                 |                                  |

| PRNU              | Photo Response Non-Uniformity, Peak-to-<br>Peak |         |         | 5   | %V <sub>SAT</sub>  | Note 2                           |

| DSNU              | Dark Signal Non-Uniformity (RMS)                |         |         | 5.0 | mV                 | Note 3                           |

| DC                | Average Dark Current                            |         |         | 0.5 | nA/cm <sup>2</sup> | Note 3                           |

| $QE_A$            | Average Quantum Efficiency (550 – 800μm)        | 0.35    |         |     |                    |                                  |

| MTF               | MTF at Nyquist                                  | 50%     |         |     |                    | Note 4                           |

| V <sub>cte</sub>  | Vertical Transfer Efficiency                    | 0.99999 | 5       |     |                    | Per Transfer (each phase) Note 2 |

| H <sub>cte</sub>  | Horizontal Charge Transfer Efficiency           | 0.99995 |         |     |                    | Per Transfer (each phase) Note 2 |

| NE                | Total Read Noise Electrons                      |         |         | 30  | e-rms              | Less Shot Noise Note 6           |

| fMAX <sub>H</sub> | H Clock Frequency                               |         |         | 25  | MHz                |                                  |

| PD                | Power Dissipation On Chip                       |         |         | 2.9 | W                  | At 25MHz each register           |

Note 1: Minimum output voltage and/or well capacity is achieved operating in standard test condition mode and is the level above which saturation non-linearity of 50% from best straight line fit occurs.

Note 2: Measured at approximately 50% V<sub>sat</sub>.

Note 3: Value shown is for 15°C.

Note 4: Measured at the format center with 2854K tungsten source and Schott OG550 filter, 3mm thick.

Note 5: Standard test conditions are non-MPP clocks and DC operating voltages with 25MHz serial output rate/port.

Note 6: Measured in dark with correlated double sampling of amplifier output signal.

# READOUT AMPLIFIER CONFIGURATION

The CCD595 readout structure is shown in the diagram below. Array to serial register transfer gates are not shown.

#### PRELIMINARY DATA SHEET

#### SINGLE OUTPUT SECTION DIAGRAM

A Single Section of the CCD595 is shown below. The 20 Taper Rows include a single row of Transfer Gates nearest the serial readout register.

### **COSMETIC GRADING**

Device grading helps to establish a ranking for the image quality that a CCD will provide. Blemishes are characterized as spurious pixels exceeding 10% of  $Q_{SAT}$  with respect to neighboring elements. Blemish content is determined in the dark, at various illumination levels and at different operating temperatures.

The CCD595 is available in different grades, as well as custom selected grades. Consult Sales representative for available grading information and custom selections.

# Fairchild Imaging, Inc., 1801 McCarthy Blvd., Milpitas, CA 95035 (800) 325-6975, (408) 433-2500

<sup>©</sup>2001 Fairchild Imaging reserves the right to make changes to its products and/or their specifications at any time without notice. Printed in the U.S.A.

#### **WARRANTY**

Within twelve months of delivery to the end customer, Fairchild Imaging will repair or replace, at our option, any Fairchild Imaging camera product if any part is found to be defective in materials or workmanship. Contact Customer Service for assignment of warranty return number and shipping instructions to ensure prompt repair or replacement.

# **CERTIFICATION**

Fairchild Imaging certifies that all products are carefully inspected and tested at the factory prior to shipment and will meet all requirements of the specifications under which it is furnished.