# **DUAL TVS ZENER FOR ESD / TRANSIENT PROTECTION**

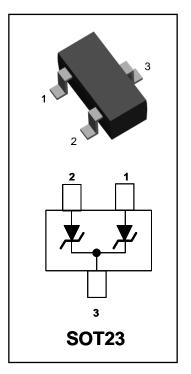

This Dual Zener ESD/Transient Protector with a Common Cathode Configuration has been designed to protect Sensitive Equipment against ESD and prevent Latch-Up events. The combination of a dual device protects up to two data lines in a single package giving the advantage of board space savings where this is a premium.

#### **SPECIFICATION FEATURES**

- Working Peak Reverse Voltage of 15V and 22V

- Maximum Leakage Current of 100nA and 50nA @ VWRM

- IEC61000-4-2 Compliance 15kV Air, 8kV Contact Discharge

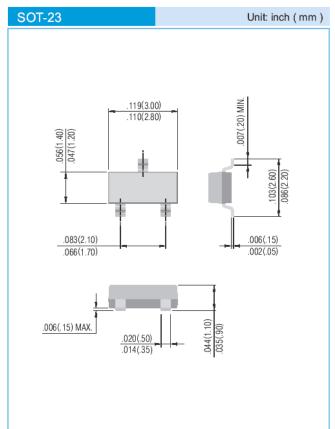

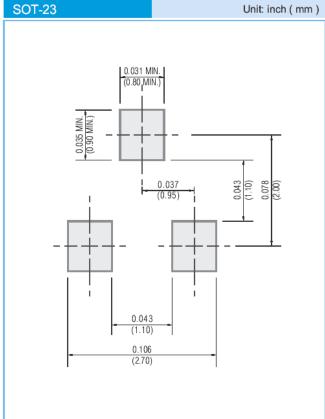

- Industry Standard SOT23 Package

#### **APPLICATIONS**

- Data Transmission Line Ports

- Computer Monitor Interface Port Protection

- Portable Consumer Electronics

- Instrumentation Equipment

### **MAXIMUM RATINGS**

| Rating                                   | Symbol           | Value       | Units |

|------------------------------------------|------------------|-------------|-------|

| Peak Pulse Power 8x20µsec Waveform       | $P_{pp}$         | 150         | W     |

| Peak Pulse Power 10x1000µsec Waveform    | РΡ               | 25          | W     |

| ESD Voltage (HBM)                        | V <sub>ESD</sub> | >25         | kV    |

| Operating Temperature Range              | TJ               | -55 to +125 | °C    |

| Storage Temperature Range                | T <sub>stg</sub> | -55 to +150 | °C    |

| Lead Soldering Temperature (max 10 secs) | TL               | 260         | °C    |

#### ELECTRICAL CHARACTERISTICS Tj = 25°C

#### PJMBZ15VD

| Parameter                      | Symbol          | Conditions                                        | Min   | Typical | Max   | Units |

|--------------------------------|-----------------|---------------------------------------------------|-------|---------|-------|-------|

| Reverse Stand-Off Voltage      | $V_{WRM}$       |                                                   |       |         | 12    | V     |

| Reverse Breakdown Voltage      | V <sub>BR</sub> | $I_{BR} = 1mA$                                    | 14.25 |         | 15.75 | V     |

| Reverse Leakage Current        | I <sub>R</sub>  | $V_R = 15V$                                       |       |         | 100   | nA    |

| Clamping Voltage (8x20µsec)    | $V_{cl}$        | $I_{pp} = 6 \text{ Amps}$                         |       |         | 24    | V     |

| Clamping Voltage (10x1000µsec) | V <sub>cl</sub> | I <sub>pp</sub> = 1 Amps                          |       |         | 23    | V     |

| Maximum Peak Pulse Current     | I <sub>pp</sub> | 8x20 µsec Waveform                                |       |         | 7     | Α     |

| Off State Junction Capacitance | Cj              | 0 Vdc Bias f = 1MHz<br>Between I/O pins and pin 3 |       |         | 80    | pF    |

## ELECTRICAL CHARACTERISTICS Tj = 25°C

#### PJMBZ27VC

| Parameter                      | Symbol           | Conditions                                        | Min   | Typical | Max   | Units |

|--------------------------------|------------------|---------------------------------------------------|-------|---------|-------|-------|

| Reverse Stand-Off Voltage      | V <sub>WRM</sub> |                                                   |       |         | 22    | V     |

| Reverse Breakdown Voltage      | V <sub>BR</sub>  | I <sub>BR</sub> = 1 mA                            | 25.65 |         | 28.35 | V     |

| Reverse Leakage Current        | I <sub>R</sub>   | $V_R = 22V$                                       |       |         | 50    | nA    |

| Clamping Voltage (8x20µsec)    | V <sub>cl</sub>  | $I_{pp} = 4 \text{ Amps}$                         |       |         | 36    | V     |

| Clamping Voltage (10x1000µsec) | V <sub>cl</sub>  | $I_{pp} = 0.85$                                   |       |         | 30    | V     |

| Maximum Peak Pulse Current     | I <sub>pp</sub>  | 8x20 µsec Waveform                                |       |         | 5     | Α     |

| Off State Junction Capacitance | Cj               | 0 Vdc Bias f = 1MHz<br>Between I/O pins and pin 3 |       |         | 50    | pF    |

### PACKAGE LAYOUT AND PAD DIMENSIONS