# TC6374AF (3in1 ATA)

# PC Card ATA to SD Memory Card, MultiMediaCard and SmartMedia™ Controller

# 1. Outline

TC6374AF is an SD memory card / MultimediaCard / SmartMedia™ controller with PC Card ATA bus interface. 3 in 1 PC Card ATA adapter card can be easily realized with a firmware-installed NOR flash memory.

# 2. Features

#### PC Card ATA controller

- Conforms to PC Card '97 Standard

- Conforms to ATA/ATAPI-5 Standard T13 1321

- Conforms to SD Card Association "SD Card PC Card Adopter Media Card Pass Throug"

- Supports 8/16 bit access

- Power mode: 4 states (Sleep, Standby, Idle, Active)

- Supports Auto power down

- > Supports Windows® standard ATA driver

#### SD Memory Card controller

- Conforms to SD Memory Card "Physical Layer Specification 1.0"

- Supports 4 bit MultiMediaCard mode interface

- > Supports Write protect function

- Supports Unique ID Read

#### MultiMediaCard controller

- Conforms to MultiMediaCard "System Specification 2.2"

- Supports 1 bit MultiMediaCard mode interface

- Supports Unique ID Read

#### SmartMedia™ Controller

- Conforms to SSFDC Forum "SmartMedia™ Physical Format"

- Supports 3.3V 1M 128M SmartMedia™

- Supports 3.3V 4M 128M MROM

- SmartMedia™, MROM automatic recognition function

- Supports Wear Leveling function

- > Supports Write protect function

- Supports ECCfunction (1 bit error correction / 2 bit error detect)

- Supports Unique ID Read

#### Controller firmware

- Installed on NORtype flash memory

- Supports Firmware Update

- Supply Firmware Object

- Licence free

## · Operation Voltage

Host Interface: 3.3V / 5V

Media Interface: 3.3V

Internal: 3.3V

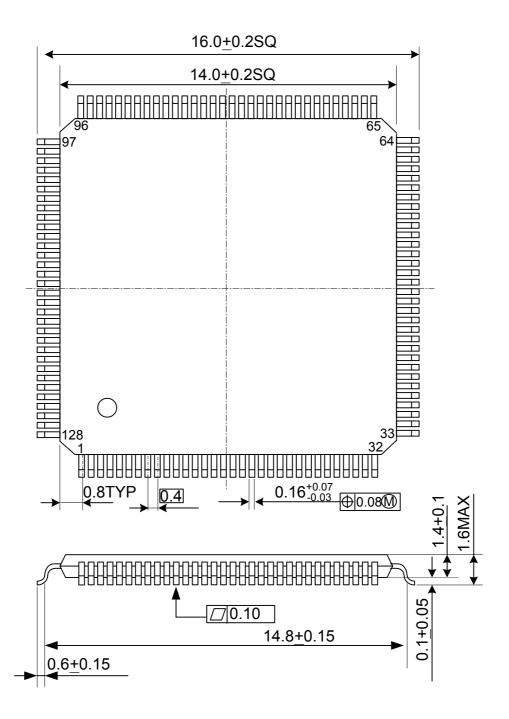

# Package

- Can be installed in PC Card Type II

- > 128-pin LQFP (Lead pitch: 0.4 mm)

# 3. Notes on Usage

- #1, Take a note on the information listed in the solid line frame at the bottom of this page.

- #2, Be sure to refer to the specification: "6-7. Notes on 3in1 PC Card ATA adapter".

- **#3**, In the system design, refer to the attached document: "Description on TC6374AF reference design (reference circuit diagram and information sheet)". These reference documents are updated time by time, therefore be sure to check the latest information by inquiry.

- #4, SmartMedia™ is a registered trademark of Toshiba.

- **#5**, Microsoft and Windows are a registered trademark of Microsoft Corporation in the United States and other countries.

Copyright© 1995 Microsoft Corporation. All Rights Reserved.

Portion Copyright© 1995 Microsoft Corporation

#6, In addition, system and product names referred to in this document are generally a registered trade mark or trade mark of respective developer or maker. Note that, in this document, marks such as ™ or ® may be omitted.

This data sheet is an interrim version arranging the target specification of products.

Note that the specific vation may be modified as necessary in the convenience of development. Copying by user is strictry prohibited in view of the confidentiality control.

If additional copies are required, contact with us so that we will prepare them by ourselves.

If the board design is based on this data sheet, contact with the Marketing staff in advance.

# 4. Contents

| 1. | Outline                                                                        | 1   |

|----|--------------------------------------------------------------------------------|-----|

| 2. | . Features                                                                     | 1   |

| 3. | Notes on Usage                                                                 | 2   |

| 4. | . Contents                                                                     | 3   |

| 5. | Pin assignment table                                                           | 6   |

|    | 5-1. Pin assignment table 1                                                    | 6   |

|    | 5-2. Pin assignment table 2                                                    | 7   |

|    | 5-3. Pin assignment table 3                                                    | 8   |

|    | 5-4. Pin assignment table 4                                                    | 9   |

|    | 5-5. Pin assignment table 5                                                    |     |

| 6. | Pin description                                                                |     |

|    | 6-1. Host interface 1                                                          |     |

|    | 6-2. Host interface 2                                                          | 12  |

|    | 6-3. SD memory card/ MultiMediaCard/ SmartMedia™/ NOR flash memory interface 1 |     |

|    | 6-4. SD memory card/ MultiMediaCard/ SmartMedia™/ NOR flash memory interface 2 |     |

|    | 6-5. Others                                                                    | 15  |

|    | 6-6. Oscillation Circuit                                                       | 16  |

|    | 6-7. Notes on 3in1 PC Card ATA adapter                                         |     |

| 7. | Operational descryption                                                        | 18  |

|    | 7-1. Outline of Interface                                                      |     |

|    | 7-2. Example of system configuration                                           | 18  |

|    | 7-3. Host interface                                                            |     |

|    | 7-4. PC Card interface                                                         | 19  |

|    | 7-5. Register description                                                      | 29  |

| 8. | ATA COMMAND                                                                    | 45  |

|    | 8-1. ATA COMMAND BLOCK                                                         |     |

|    | 8-2. Operation of ATA COMMAND BLOCK REGISTER                                   | 45  |

|    | 8-3. ATA COMMAND CODE and PARAMETERS                                           |     |

|    | 8-3-1. STANDARD ATA COMMAND                                                    | 46  |

|    | 8-3-2. VENDOR UNIQUE COMMAND                                                   | 47  |

|    | 8-4. Error indication report of ATA COMMAND                                    | 48  |

|    | 8-5. General description of ATA COMMAND                                        | 49  |

|    | 8-5-1. STANDARD ATA COMMAND                                                    | 49  |

|    | 8-5-2. VENDOR UNIQUE ATA COMMAND                                               | 86  |

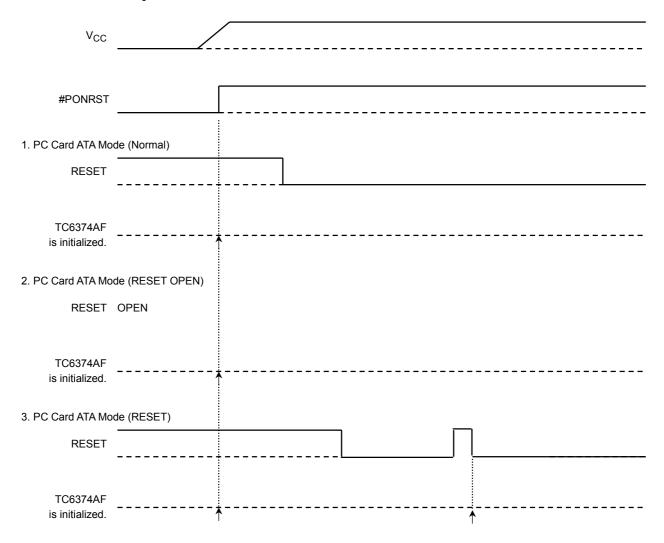

| 9. | Reset operation                                                                | 99  |

|    | 9-1. Hardware rest by #PONRST terminal                                         | 99  |

|    | 9-2. Hardware reset by RESET terminal                                          |     |

|    | 9-3. Software reset by FCR Configuration Option Register:SRESET "D7" bit       | 99  |

|    | 9-4. Software reset by ATA Device Control Register:SRST "D2" bit               | 99  |

| 10 | 0. Control of low power consumption                                            | 100 |

| 11 | 1. NOR flash memory                                                            | 101 |

|    |                                                                                |     |

| 12. Removable media memory capacity                     | 102 |

|---------------------------------------------------------|-----|

| 12-1. SmartMedia™                                       | 102 |

| 12-2. SD Memory Card/ MultiMediaCard                    | 102 |

| 13. Recognizing the removable media                     |     |

| 13-1. SmartMedia™                                       |     |

| 13-2. SD Memory Card/MultiMediaCard                     | 104 |

| 14. Others                                              | 105 |

| 14-1. System Performance                                | 105 |

| 14-2. The Calculation of Read and Write Performance     |     |

| 14-3. Setup Time                                        | 110 |

| 14-4. PC Card ATA Power Consumption of TC6374AF         |     |

| 14-5. MTBF                                              | 111 |

| 14-6. ECC                                               | 111 |

| 14-7. Reliability                                       | 111 |

| 15. Absolute maximum ratings (V <sub>SS</sub> = 0V)     | 112 |

| 16. Standard operation condition (V <sub>SS</sub> = 0V) | 112 |

| 17. DC electrical characteristic                        |     |

| 18. AC characteristics                                  | 114 |

| 18-1. PC Card interface                                 | 114 |

| 18-2. SmartMedia™ interface                             | 116 |

| 18-3. SD Memory Card/ MultiMediaCard interface          |     |

| 18-4. NOR flash memory interface                        |     |

| 18-4-1. Fujitsu (AMD) NOR flash memory interface        |     |

| 18-4-2. Sharp (Intel) NOR flash memory interface        |     |

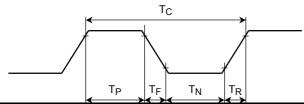

| 18-5. Clock input condition                             |     |

| 18-6. Reset input condition                             |     |

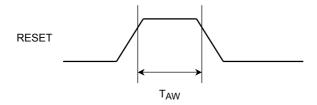

| 19. Reset sequence                                      |     |

| 20. Package outline                                     | 123 |

# [Notice]

- #1. This product conforms to PC Card '97 Standard.

- **#2**. This product conforms to SmartMedia<sup>™</sup> Physical format specification standardized and recommended by SSFDC Forum.

- **#3**. This product conforms to ATA/ATAPI-5 standard.

- **#4**. Voltage level indication differs per input/output signal.

- #5. "Hi-Z" used in this document represents the High impedance state.

| Voltage level | Input signal | Output signal |

|---------------|--------------|---------------|

| $V_{DD}$      | "1"          | "H"           |

| $V_{SS}$      | "0"          | "L"           |

# 5. Pin assignment table

# 5-1. Pin assignment table 1

For marks in the table, refer to the footnotes below the table.

| NO. | I/O | Symbol             | No           | ote           |

|-----|-----|--------------------|--------------|---------------|

| NO. | 1/0 | Symbol             | Input Buffer | Output Buffer |

| 1   | -   | $V_{DD3.3}$        | -            | -             |

| 2   | 0   | #NOR_CE            | -            | <u>B4</u>     |

| 3   | 0   | #NOR_OE            | -            | <u>B4</u>     |

| 4   | 0   | #NOR_WE            | -            | <u>B4</u>     |

| 5   | 0   | NOR_A0             | -            | <u>B4</u>     |

| 6   | 0   | NOR_A1             | -            | <u>B4</u>     |

| 7   | -   | V <sub>SS</sub>    | -            | -             |

| 8   | 1   | #NOR_BSY           | LVTTL, S     | -             |

| 9   | 0   | #NOR_RP            | -            | <u>B4</u>     |

| 10  | 0   | NOR_A2             | -            | <u>B4</u>     |

| 11  | 0   | NOR_A3             | -            | <u>B4</u>     |

| 12  |     | V <sub>SS</sub>    | -            | -             |

| 13  | 0   | NOR_A4             | -            | <u>B4</u>     |

| 14  | 0   | NOR_A5             | -            | <u>B4</u>     |

| 15  | Į.  | SH/#FJ             | LVTTL        | _             |

| 16  | -   | V <sub>SS</sub>    | TEST IN      | -             |

| 17  | -   | V <sub>DD3.3</sub> | -            | -             |

| 18  | 0   | NOR_A6             | -            | <u>B4</u>     |

| 19  | 0   | NOR_A7             | -            | <u>B4</u>     |

| 20  | 0   | NOR_A8             | -            | <u>B4</u>     |

| 21  | 0   | NOR_A9             | -            | <u>B4</u>     |

| 22  | -   | V <sub>SS</sub>    | -            | _             |

| 23  | 0   | NOR_A10            | -            | B4            |

| 24  | 0   | NOR_A11            | -            | <u>B4</u>     |

| 25  | I   | FPSD               | LVTTL        | -             |

| 26  | -   | $V_{DD3.3}$        | TEST IN      | -             |

| 27  | -   | V <sub>SS</sub>    | -            | -             |

| 28  | 0   | NOR_A12            | -            | <u>B4</u>     |

| 29  | 0   | NOR_A13            | -            | <u>B4</u>     |

| 30  | 1   | SDWP               | LVTTL        | -             |

I: Input

O: Output O (Tri): Tri-state

B: Bidirection

Notice: Buffer Type

S: Schmidt LVTTL: 3V LVTTL level (same with 5V) PU: Pulled-up

PD: Pulled-down B4/B8IF: 3V= B4, 5V= B8IF

5-2. Pin assignment table 2

| NO. | I/O     | Symbol             | No           | Note           |  |  |

|-----|---------|--------------------|--------------|----------------|--|--|

| NO. | 1/0     | Symbol             | Input Buffer | Output Buffer  |  |  |

| 31  | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 32  | -       | $V_{DD3.3}$        | -            | -              |  |  |

| 33  | -       | $V_{DD}$           | -            | -              |  |  |

| 34  | 1       | #FCD               | LVTTL        | -              |  |  |

| 35  | В       | D10                | LVTTL        | <u>B4/B8IF</u> |  |  |

| 36  | В       | D2                 | LVTTL        | B4/B8IF        |  |  |

| 37  | В       | D9                 | LVTTL        | B4/B8IF        |  |  |

| 38  | В       | D1                 | LVTTL        | B4/B8IF        |  |  |

| 39  | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 40  | I       | #CD                | LVTTL, S     | -              |  |  |

| 41  | I       | A3                 | LVTTL        | -              |  |  |

| 42  | -       | NC                 | -            | -              |  |  |

| 43  | I       | A0                 | LVTTL        | -              |  |  |

| 44  |         | V <sub>SS</sub>    | -            | -              |  |  |

| 45  | O (Tri) | #IOIS16 (WP)       | -            | B4/B8IF        |  |  |

| 46  | I       | A1                 | LVTTL        | -              |  |  |

| 47  | I       | #REG               | LVTTL, PU    | -              |  |  |

| 48  | I       | A2                 | LVTTL        | -              |  |  |

| 49  | -       | $V_{DD}$           | -            | -              |  |  |

| 50  | В       | D8                 | LVTTL        | B4/B8IF        |  |  |

| 51  | В       | D0                 | LVTTL        | <u>B4/B8IF</u> |  |  |

| 52  | O (Tri) | #INPACK            | -            | B4/B8IF        |  |  |

| 53  | I       | A4                 | LVTTL        | -              |  |  |

| 54  | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 55  | I       | RESET              | LVTTL        | -              |  |  |

| 56  | I       | A5                 | LVTTL        | -              |  |  |

| 57  | I       | A6                 | LVTTL        | -              |  |  |

| 58  | -       | V <sub>DD3.3</sub> | -            | -              |  |  |

| 59  | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 60  | I       | #WE                | LVTTL, S, PU | _              |  |  |

I: Input

O: Output O (Tri): Tri-state

B: Bidirection

Notice: Buffer Type

S: Schmidt LVTTL: 3V LVTTL level (same with 5V) PU: Pulled-up

PD: Pulled-down B4/B8IF: 3V= B4, 5V= B8IF

5-3. Pin assignment table 3

| NO. | I/O | Symbol          | No           | Note           |  |  |

|-----|-----|-----------------|--------------|----------------|--|--|

| NO. | I/O | Symbol          | Input Buffer | Output Buffer  |  |  |

| 61  | I   | #IOWR           | LVTTL, S, PU | -              |  |  |

| 62  | I   | A7              | LVTTL        | -              |  |  |

| 63  | -   | NC              | -            | -              |  |  |

| 64  | -   | V <sub>SS</sub> | -            | -              |  |  |

| 65  | -   | $V_{DD}$        | -            | -              |  |  |

| 66  | I   | A8              | LVTTL        | -              |  |  |

| 67  | I   | #IORD           | LVTTL, S, PU | -              |  |  |

| 68  | I   | #OE             | LVTTL, S, PU | -              |  |  |

| 69  | I   | #CE2            | LVTTL, PU    | -              |  |  |

| 70  | -   | V <sub>SS</sub> | -            | -              |  |  |

| 71  | I   | #CE1            | LVTTL, PU    | -              |  |  |

| 72  | I   | A9              | LVTTL        | -              |  |  |

| 73  | В   | D15             | LVTTL        | <u>B4/B8IF</u> |  |  |

| 74  | В   | D7              | LVTTL        | <u>B4/B8IF</u> |  |  |

| 75  | В   | D14             | LVTTL        | B4/B8IF        |  |  |

| 76  | -   | V <sub>SS</sub> | -            | -              |  |  |

| 77  | В   | D6              | LVTTL        | B4/B8IF        |  |  |

| 78  | В   | D13             | LVTTL        | <u>B4/B8IF</u> |  |  |

| 79  | В   | D5              | LVTTL        | B4/B8IF        |  |  |

| 80  | -   | $V_{DD}$        | -            | -              |  |  |

| 81  | -   | $V_{DD3.3}$     | -            | -              |  |  |

| 82  | I   | A10             | LVTTL        | -              |  |  |

| 83  | -   | V <sub>SS</sub> | TEST IN      | -              |  |  |

| 84  | -   | V <sub>SS</sub> | TEST IN      | -              |  |  |

| 85  | В   | D12             | LVTTL        | B4/B8IF        |  |  |

| 86  | -   | V <sub>SS</sub> | -            | -              |  |  |

| 87  | В   | D4              | LVTTL        | <u>B4/B8IF</u> |  |  |

| 88  | В   | D11             | LVTTL        | <u>B4/B8IF</u> |  |  |

| 89  | В   | D3              | LVTTL        | B4/B8IF        |  |  |

| 90  | l   | SELBSY          | LVTTL, PD    | -              |  |  |

I: Input

O: Output O (Tri): Tri-state

B: Bidirection

Notice: Buffer Type

S: Schmidt LVTTL: 3V LVTTL level (same with 5V) PU: Pulled-up

PD: Pulled-down B4/B8IF: 3V= B4, 5V= B8IF

5-4. Pin assignment table 4

| NO. | I/O     | Symbol             | No           | Note           |  |  |

|-----|---------|--------------------|--------------|----------------|--|--|

| NO. | 1/0     | Symbol             | Input Buffer | Output Buffer  |  |  |

| 91  | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 92  | 1       | #PONRST            | LVTTL, S     | -              |  |  |

| 93  | -       | V <sub>SS</sub>    | TEST IN      | -              |  |  |

| 94  | O (Tri) | #IREQ (READY)      | -            | <u>B4/B8IF</u> |  |  |

| 95  | -       | V <sub>SS</sub>    | TEST IN      | -              |  |  |

| 96  | -       | $V_{DD}$           | -            | -              |  |  |

| 97  | -       | $V_{DD3.3}$        | -            | -              |  |  |

| 98  | 1       | XI                 | CLOCK IN     | -              |  |  |

| 99  | 0       | XO                 | -            | CLOCK OUT      |  |  |

| 100 | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 101 | 0       | OSCOUT             | -            | <u>B4</u>      |  |  |

| 102 | -       | $V_{DD3.3}$        | -            | -              |  |  |

| 103 | 0       | FCLE / MMCLK       | -            | <u>B8</u>      |  |  |

| 104 | 0       | FALE               | -            | <u>B4</u>      |  |  |

| 105 | I       | #FBSY              | LVTTL, S     | -              |  |  |

| 106 | O (Tri) | #FCE               | -            | <u>B4</u>      |  |  |

| 107 | O (Tri) | #FRE               | -            | <u>B4</u>      |  |  |

| 108 | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 109 | В       | FD4                | LVTTL        | <u>B4</u>      |  |  |

| 110 | В       | FD5                | LVTTL        | <u>B4</u>      |  |  |

| 111 | В       | FD6                | LVTTL        | <u>B4</u>      |  |  |

| 112 | В       | FD7                | LVTTL        | <u>B4</u>      |  |  |

| 113 | -       | $V_{DD}$           | -            | -              |  |  |

| 114 | -       | V <sub>DD3.3</sub> | -            | -              |  |  |

| 115 | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 116 | В       | #FWE / MMCMD       | LVTTL        | <u>B4</u>      |  |  |

| 117 | 0       | #FWP               | -            | <u>B4</u>      |  |  |

| 118 | -       | V <sub>SS</sub>    | -            | -              |  |  |

| 119 | I       | RMCLK              | LVTTL, S     | -              |  |  |

| 120 | 0       | OCTL               | -            | <u>B4</u>      |  |  |

I: Input

O: Output O (Tri): Tri-state

B: Bidirection

Notice: Buffer Type

S: Schmidt LVTTL: 3V LVTTL level (same with 5V) PU: Pulled-up

PD: Pulled-down B4/B8IF: 3V= B4, 5V= B8IF

5-5. Pin assignment table 5

| NO. | I/O | Symbol | Note         |               |  |

|-----|-----|--------|--------------|---------------|--|

| NO. |     | Symbol | Input Buffer | Output Buffer |  |

| 121 | 0   | OUTCLK | -            | <u>B4</u>     |  |

| 122 | I   | MCLK   | LVTTL, S     | -             |  |

| 123 | -   | VSS    | -            | -             |  |

| 124 | В   | FD0    | LVTTL        | <u>B4</u>     |  |

| 125 | В   | FD1    | LVTTL        | <u>B4</u>     |  |

| 126 | В   | FD2    | LVTTL        | <u>B4</u>     |  |

| 127 | В   | FD3    | LVTTL        | <u>B4</u>     |  |

| 128 | -   | VSS    | -            | -             |  |

I: Input

O: Output O (Tri): Tri-state

B: Bidirection

Notice: Buffer Type

S: Schmidt LVTTL: 3V LVTTL level (same with 5V) PU: Pulled-up

PD: Pulled-down B4/B8IF: 3V= B4, 5V= B8IF

TEST IN: Should be tied to  $V_{\mbox{\scriptsize DD3.3}}$  or  $V_{\mbox{\scriptsize SS}}$  specified in Symbol column.

# 6. Pin description

# 6-1. Host interface 1

| Pin name           | Pin number        | I/O | Pin function                  | Functional description                                                                                                                                                                                                                                                                                                                      |

|--------------------|-------------------|-----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>    | 33,49,65,80,96,   | -   | POWER SUPPLY                  | A power terminal for PC card interface circuit.                                                                                                                                                                                                                                                                                             |

|                    | 113               |     |                               |                                                                                                                                                                                                                                                                                                                                             |

| V <sub>DD3.3</sub> | 1,17,26,32,58,81, | -   | POWER SUPPLY                  | A power terminal other than PC card interface circuit.                                                                                                                                                                                                                                                                                      |

| 220.0              | 97,102,114,       |     |                               |                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SS</sub>    | 7,12,16,22,27,31, | -   | GROUND                        | A ground terminal.                                                                                                                                                                                                                                                                                                                          |

|                    | 39,44,54,59,64,   |     |                               |                                                                                                                                                                                                                                                                                                                                             |

|                    | 70,76,83,84,86,   |     |                               |                                                                                                                                                                                                                                                                                                                                             |

|                    | 91,93,95,100,     |     |                               |                                                                                                                                                                                                                                                                                                                                             |

|                    | 108,115,118,123,  |     |                               |                                                                                                                                                                                                                                                                                                                                             |

|                    | 128               |     |                               |                                                                                                                                                                                                                                                                                                                                             |

| NC                 | 42,63             | -   | NON<br>CONNECTION             | An open terminal. Keep it in the open state.                                                                                                                                                                                                                                                                                                |

| RESET              | 55                | I   | CARD RESET                    | A reset terminal. If set to "1", all the internal states including FCR are initialized. Set to the reset state if an edge moved to the assert state is detected, and reset is cleared if the negate state is detected. If, when SD Memory Card is used, this terminal is cleared from "1" to "0", CMD0 for media reset is issued two times. |

| D15 - D0           | 73,75,78,85,88,   | В   | DATA BUS                      | Data bus of 16-bit width (2 bytes). D15 is MSB and D0 is                                                                                                                                                                                                                                                                                    |

|                    | 35,37,50,74,77,   |     |                               | LSB. Normally, this bus is set to the input state and, only if read by the host, set to the output state.                                                                                                                                                                                                                                   |

|                    | 79,87,89,36,38,51 |     |                               | ·                                                                                                                                                                                                                                                                                                                                           |

| A10 - A0           | 82,72,66,62,57,   | I   | ADDRESS BUS                   | Address bus. A10 is MSB and A0 is LSB. In TC6374AF,                                                                                                                                                                                                                                                                                         |

|                    | 56,53,41,48,46,43 |     |                               | maximum number of address is 11. Number of decodes differ per mode. In word access, A0 is disabled.                                                                                                                                                                                                                                         |

| #REG               | 47                | I   | ATTRIBUTE<br>MEMORY<br>SELECT | Set to "1", Memory Mapped mode allows accessing I/O space with #OE and #WE. If #REG set to "0", CIS and FCR can be accessed by #OE and #WE, or by #IORD and #IOWR, I/O space in each mode of Independent I/O, Primary/Secondary can be accessed.(with pull-up resistor)                                                                     |

| #CE1               | 71                | I   | CARD ENABLE 1                 | Set to "0" if accessed by host via D7 - D0 (with pull-up resistor)                                                                                                                                                                                                                                                                          |

| #CE2               | 69                | I   | CARD ENABLE 2                 | Set to "0" if accessed by host via D15 - D8. Odd number addresses only can be accessed from D15 - D8 irrespective of A0 (with pull-up resistor)                                                                                                                                                                                             |

| #OE                | 68                | I   | OUTPUT<br>ENABLE              | Used to read I/O space in the CIS, FCR and Memory Mapped modes. In the write operation, this terminal shall be disabled (with pull-up resistor)                                                                                                                                                                                             |

| #WE                | 60                | I   | WRITE ENABLE                  | Used to write I/O space in the FCR and Memory Mapped mode (with pull-up resistor)                                                                                                                                                                                                                                                           |

# 6-2. Host interface 2

| Pin name          | Pin number | I/O | Pin function                                 | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|------------|-----|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #IORD             | 67         | ļ   | I/O READ                                     | Used to read I/O space in Independent I/O, Primary and Secondary modes. In other modes than above, this terminal is disabled (with pull-up resistor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| #IOWR             | 61         | I   | I/O WRITE                                    | Used to write to I/O space in Independent I/O, Primary and Secondary modes. In other modes than above, this terminal is disabled (with pull-up resistor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| #IOIS16<br>(WP)   | 45         | 0   | I/O IS 16 bits<br>PORT<br>(WRITE<br>PROTECT) | Fixed to "L" in the Independent I/O mode. In Primary or Secondary mode, "L" is outputted if data bus allows 16-bit access. With memory card interface, this terminal indicates the media write protect state for WP, i.e. "H" for write protect state or "L" for non- write protect state. Input values from FPSD terminal (i.e. SmartMedia™ write protect seal detect signal) and SDWP terminal (i.e. SD Memory Card write protect switch detect signal) are OR'ed and directly outputted from this terminal (This terminal is, if in the memory card interface, is set to H if FPSD="1", MMWP="1" or MROM is inserted)                                                                                        |

| # IREQ<br>(READY) | 94         | 0   | INTERRUPT<br>REQUEST<br>(READY)              | Two types of output format are allowed for interrupt request in the I/O card interface. It can be changed by FCR Configuration Option register: LevIREQ"D6" bit. With this bit set to "1", the terminal is in the pulse mode ("L" pulse width of about 800ns) if it is in the level mode and set to "0". Initial value immediately after reset is set to the value in the level mode. Output timing of the terminal is when ATA Status register: BSY"D7" bit changes "H"->"L". The terminal provides RDY/BSY function in the memory card interface. Or, if ATA Status register: BSY"D7"! bit is set to "1", or FCR Card Configuration and Status register:PWRDWN bit are in the setting mode, "L" is outputted. |

| #INPACK           | 52         | 0   | INPUT PORT<br>ACKNOWLEDG<br>E                | Only if #CE1, #CE2 and #IORD are set to "0" and the address on address bus matches with that in I/O space, the terminal outputs "L". In the memory card interface, the terminal outputs "Hi-Z".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**TOSHIBA**

# 6-3. SD memory card/ MultiMediaCard/ SmartMedia™/ NOR flash memory interface 1

| Pin name       | Pin number | I/O | Pin function                                                                        | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------------|-----|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FD7 - FD4      | 112-109    | В   | MEDIA DATA<br>BUS                                                                   | The terminal is prepared to connect with media data bus. If clock is stabled after resetting and NOR flash memory is re-written, it takes the upper position of NOR flash memory data bus. In other modes, it takes the upper position of address/data common bus to SmartMedia™. Address and data (including command) are discriminated by FALE and FCLE. The terminal is set to Hi-Z when #CD="H" (media non-inserted).                                                                                                                                       |

| FD3 - FD0      | 127-124    | В   | MEDIA DATA<br>BUS                                                                   | The terminal is prepared to connect with media data bus. If clock is stabled after resetting and NOR flash memory is re-written, it takes the lower position of NOR flash memory data bus. In other modes, it takes the lower position of address/data common bus to SmartMedia™. Address and data (including command) are discriminated by FALE and FCLE. When SD Memory Card is used, it is used as 4 bit data bus. If MultiMediaCard is used and SD Memory Card is in the 1 bit mode, FD0 only is used. It is set to Hi-Z when #CD= "H"(media non-inserted). |

| #FCE           | 106        | 0   | SmartMedia™<br>CHIP ENABLE                                                          | The terminal indicates the chip enable output signal of SmartMedia™. If #CD="H"(media not-inserted), it indicates Hi-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FCLE/MMC<br>LK | 103        | 0   | SmartMedia™ COMMAND LATCH ENABLE/SD Memory Card & MultiMediaCar d CLOCK             | The terminal indicates, if SmartMedia™ is used, the command latch enable output signal to SmartMedia™. If command is outputted to FD bus, it outputs "H". If SD Memory Card and MultiMediaCard are used, it indicates 250KHz, 2MHz, 8MHz and16MHz clock output signal to SD Memory Card and MultiMediaCard. Clock output frequency is determined by the maximum operation frequency of media. It is set to "L" when #CD="H"(media not-inserted).                                                                                                                |

| FALE           | 104        | 0   | SmartMedia™<br>ADDRESS<br>LATCH<br>ENABLE                                           | Indicates address latch enable output signal to SmartMedia™. Outputs "H" if address is outputted to FD bus. The terminal is set to "L" if #CD="H"(media not-inserted).                                                                                                                                                                                                                                                                                                                                                                                          |

| #FRE           | 107        | 0   | SmartMedia™<br>READ<br>ENABLE                                                       | Indicates read enable output signal to SmartMedia™. Outputs "L" if address is outputted to FD bus. The terminal is set to "Hi-Z" if #CD="H"(media not-inserted).                                                                                                                                                                                                                                                                                                                                                                                                |

| #FWE/MM<br>CMD | 116        | В   | SmartMedia™<br>WRITE<br>ENABLE/SD<br>Memory Card<br>&<br>MultiMediaCar<br>d COMMAND | Indicates the write enable output signal to SmartMedia™ if used. Outputs "L" if written to FD bus. If SD Memory Card and MultiMediaCard are used, it becomes command/response input/output signal from/to SD Memory Card and MultiMediaCard. The terminal is set to Hi-Z when #CD="H" (media not inserted).                                                                                                                                                                                                                                                     |

| #FBSY          | 105        | I   | SmartMedia™<br>BUSY                                                                 | Indicates ready/busy input signal from SmartMedia™. Indicates the busy if "0" is inputted, or the ready if "1" is inputted. Connects with the terminal via pull-up resistor from SmartMedia™ ready/busy output.                                                                                                                                                                                                                                                                                                                                                 |

| #FWP           | 117        | 0   | SmartMedia™<br>WRITE<br>PROTECT                                                     | Indicates write protect output signal to SmartMedia™. Write protection is enabled except for the time when SmartMedia™ is accessed. The terminal is set to "L" if #CD= "H"(media not inserted).                                                                                                                                                                                                                                                                                                                                                                 |

# **TOSHIBA**

6-4. SD memory card/ MultiMediaCard/ SmartMedia™/ NOR flash memory interface 2

| Pin name       | Pin number                                | I/O | Pin function                                    | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-------------------------------------------|-----|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPSD           | 25                                        | I   | SmartMedia™<br>WRITE<br>PROTECT<br>LABEL DETECT | Indicates the write protect input signal from SmartMedia™ write protect seal. If "1" is inputted to the terminal, write related commands from host are aborted. The terminal input state is reflected to Pin Replacement Register: RWProt "D0" bit and ATA Error Register: WP"D6" bit on the to WP terminal and FCR, then the terminal input logic is directly outputted. The terminal will not change after the power is turned on, and must not be changed.                                                                                                                                                                                                                                                                                                                                                                          |

| SDWP           | 30                                        | l   | SD Memory Card<br>WRITE<br>PROTECT<br>DETECT    | Indicates the write protect input signal from SD Memory Card write protect switch. If "1" is inputted to the terminal, write related commands from host are aborted. The terminal input state is reflected to Pin Replacement Register: RWProt "D0" bit and ATA Error Register: WP"D6" bit on the to WP terminal and FCR, then the terminal input logic is directly outputted. The terminal will not change after the power is turned on, and must not be changed.                                                                                                                                                                                                                                                                                                                                                                     |

| #FCD           | 34                                        | I   | SELECT MEDIA<br>TYPE                            | Prepared to select the media type connected with TC6374AF. If the terminal input is set to "0", it is recognized as SmartMedia™, or if set to "1", it is recognized as SD Memory Card or MultiMediaCard.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| #CD            | 40                                        | I   | MEDIA DETECT                                    | Prepared to detect that TC6374AF is connected with media. If the terminal input is set to "0", it is recognized as media being connected, carrying out the normal operation. If the terminal input is set to "1", it is recognized that no media is connected, then TC6374AF enters the internal reset state and all removable media interface terminals turns to Hi-Z except for FCLE, FALE, and #FWP. In such event, OCTL="L", oscillation stops and ATA Status Register: BSY"D7" bit turns to "H". If the terminal state changes "1"->"0", the internal reset state is cleared, and the media is initialized 200ms after(with which contact between connector and media becomes stable). When SD Memory Card is used, the terminal is set to "0". If media insertion is detected, CMD0 is issued two times to initialize the media. |

| #NOR_CE        | 2                                         | 0   | NOR CHIP<br>ENABLE                              | Chip enable output signal used for the NOR flash memory in controller firmware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| #NOR_W<br>E    | 4                                         | 0   | NOR WRITE<br>ENABLE                             | Write enable output signal used for the NOR flash memory in controller firmware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| #NOR_O<br>E    | 3                                         | 0   | NOR OUTPUT<br>ENABLE                            | Output enable output signal used for the NOR flash memory in controller firmware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| #NOR_BS<br>Y   | 8                                         | I   | NOR BUSY                                        | Busy signal used for the NOR flash memory in controller firmware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NOR_A13<br>- 0 | 29,28,24,23<br>,21-18,14,1<br>3,11,10,6,5 | 0   | NOR ADDRESS<br>BUD                              | Chip enable output signal used for the NOR flash memory in controller firmware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SH/#FJ         | 15                                        | I   | SELECT NOR<br>TYPE                              | Prepared to select the NOR flash memory type in controller firmware. If the input is set to "0", unit-1 3.3V NOR flash memory of Fujitsu (AMD) may be used. If the input is set to "1", unit-1 3.3V NOR flash memory of Sharp (Intel) may be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| #NOR_RP        | 9                                         | 0   | NOR<br>RESET/DEEP<br>POWER-DOWN                 | Prepared to control #RP terminal of flash memory if NOR flash of Sharp is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# 6-5. Others

| Pin name | Pin<br>number | I/O | terminal<br>function                  | functional description                                                                                                                                                                                                                                                                                                               |

|----------|---------------|-----|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #PONRST  | 92            | I   | POWER ON<br>RESET                     | A terminal for performing the power-on reset to TC6374AF. Set to "0" to move TC6374AF internally to the reset state, or if set to "1", the reset is cleared. When SD Memory Card is used, #CD is set to "0"(media insertion state). If the terminal is cleared from "0" to "1", CMD0 is issued two times for media reset.            |

| ΧI       | 98            | I   | CLOCK<br>INPUT                        | Mask clock input to TC6374AF. Provides a terminal for duty ratio 45 - 55% 16 MHz oscillation module connection. Connect the terminal to the ground if an oscillator is connected with.                                                                                                                                               |

| хо       | 99            | 0   | CLOCK<br>INPUT                        | Mask clock input to TC6374AF. Provides a terminal for duty ratio 45 - 55% 16 MHz oscillation module connection. Keep the terminal open if an oscillator is connected with.                                                                                                                                                           |

| OSCOUT   | 101           | 0   | OSCILLATO<br>R OUTPUT<br>TO RMCLK     | Connect directly to RMCLK if oscillation module is used. If the oscillator is used, keep the terminal open.                                                                                                                                                                                                                          |

| SELBSY   | 90            | I   | SELECT<br>BUSY                        | A terminal to select busy time after ATA command is accepted. If set to "0", minimum busy time is about 150us immediately after ATA command is accepted. If set to "1", no busy time limit is imposed immediately after ATA command is accepted. Set ting to "0" as a default is recommended.                                        |

| RMCLK    | 119           | I   | DEFERENCE<br>MASTER<br>CLOCK<br>INPUT | Mask clock input to TC6374AF. Provides a terminal for duty ratio 45 – 55% 16 MHz oscillator connection. Directly connect with OSCOUT if an oscillation module is used.                                                                                                                                                               |

| OUTCLK   | 121           | 0   | CLOCK OUT                             | Clock output after the oscillation becomes stable. Directly connect with MCLK.                                                                                                                                                                                                                                                       |

| MCLK     | 122           | I   | MASTER<br>CLOCK<br>INPUT<br>TO OUTCLK | Master clock input to TC6374AF internal logic. Directly connect with OUTCLK.                                                                                                                                                                                                                                                         |

| OCTL     | 120           | 0   | CLOCK<br>CONTROL                      | Oscillator control signal. During the power-down and in the media not-connected state (#CD="1"), "L" is outputted and oscillation stop is requested. If the oscillator with oscillation control function is used, connect with the oscillator's oscillation control terminal. If oscillation module is used, keep the terminal open. |

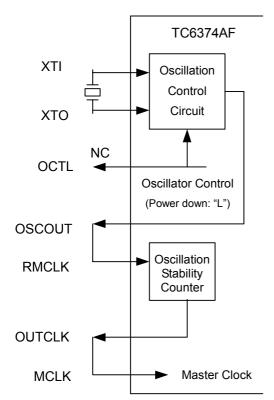

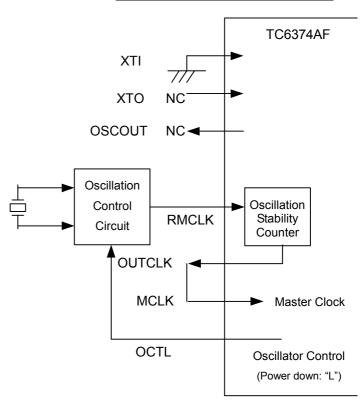

# 6-6. Oscillation Circuit

# The case which connected Oscillation Module

# The case which connected Oscillator

# 6-7. Notes on 3in1 PC Card ATA adapter

Note: For the system design, refer to the attached document: "TC6374AF reference design description (reference circuit diagram and information sheet)". This document is updated as necessary, check the latest version by inquiry.

- **#1**. RESET signal: For the compatibility with PC card interface, add a capacitor between a terminal and GND. Put pull-up resistors to the terminal. (see reference circuit diagram)

- **#2**. #CE1 signal: If, due to the crosstalk by simultaneous data bus switching by target system, add a capacitor between a terminal and GND. (see reference circuit design)

- **#3**. #CE2 signal: If, due to the crosstalk by simultaneous data bus switching by target system, add a capacitor between a terminal and GND. (see reference circuit design)

- **#4**. FPSD signal: Connect the terminal with the SmartMedia<sup>™</sup> write protect output using a resistor of about 100kΩ pull-down.

- #5. #PONRST signal: Apply a voltage detector of 2.9V in front stage of the terminal.

# 7. Operational descryption

# 7-1. Outline of Interface

TC6374AF has four types of interfaces listed below.

- Host interface

- SD Memory Card / MultiMediaCard interface

- SmartMedia™ interface

- NOR flash memory interface

For examples of system configuration and interface, refer to 7-2 and 7-3 respectively.

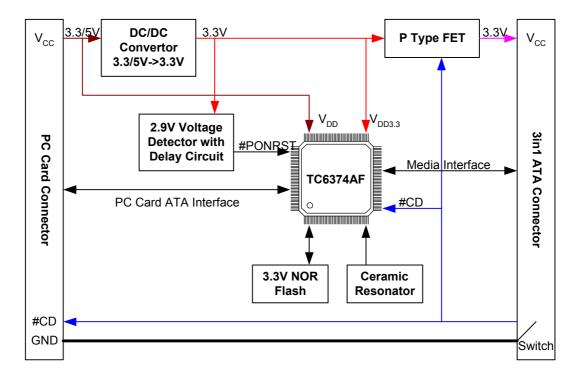

# 7-2. Example of system configuration

[3in1 PC Card ATA Adaptor]

Note: The diagram above is a simplified one. For the detailed information, refer to the attached document: "TC6374AF reference design description (reference circuit diagram and information sheet)". As the information is updated as necessary, keep the latest one by inquiry.

## 7-3. Host interface

TC6374AF supports as a host interface the PC Card (Memory, ATA) interface. In PC Card ATA interface, it supports 4 types of I/O mode(Memory Mapped I/O, Independent I/O, Primary and Secondary). Furthermore, PC Card interface has a memory space called attribute memory allowing the software to configure TC6374AF("\*" indicated in the table shown later means "Don't Care".).

#### 7-4. PC Card interface

## 7-4-1. Attribute Memory space

Attribute memory consists of CIS(Card Information Structure) with which a host recognizes the function type connected with TC6374AF and FCR (Function Configuration Register) for configuration. Attribute memory can be accessed of course in the memory interface state, and additionally, even after set to the I/O interface. Access methods and addresses of register in the attribute memory are listed below.

### 7-4-1-1. Attribute Memory read operation

During the Attribute Memory Read Cycle, set #WE to inactive "1", and #REG and #OE to active "0". #CE2, #CE1 and A0 are controlled at odd/even addresses, though Attribute Memory access is enabled only at even address data.

| Function Mode         | #REG | #CE2 | #CE1 | A0 | #OE | #WE | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|----|-----|-----|----------|-----------|

| Standby Mode          | *    | 1    | 1    | *  | *   | *   | Hi-Z     | Hi-Z      |

| Duto Access (9 Dita)  | 0    | 1    | 0    | 0  | 0   | 1   | Hi-Z     | Even byte |

| Byte Access (8 Bits)  | 0    | 1    | 0    | 1  | 0   | 1   | Hi-Z     | Invalid   |

| Word Access (16 Bits) | 0    | 0    | 0    | *  | 0   | 1   | Invalid  | Even byte |

| Odd Byte Only Access  | 0    | 0    | 1    | *  | 0   | 1   | Invalid  | Hi-Z      |

# 7-4-1-2. Attribute Memory write operation

During Attribute Memory Write Cycle, set #OE to inactive "1", and #REG and #WE to active "0".

| Function Mode         | #REG | #CE2 | #CE1 | A0 | #OE | #WE | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|----|-----|-----|----------|-----------|

| Standby Mode          | *    | 1    | 1    | *  | *   | *   | *        | *         |

| Puto Access (9 Pito)  | 0    | 1    | 0    | 0  | 1   | 0   | *        | Even byte |

| Byte Access (8 Bits)  | 0    | 1    | 0    | 1  | 1   | 0   | *        | *         |

| Word Access (16 Bits) | 0    | 0    | 0    | *  | 1   | 0   | *        | Even byte |

| Odd Byte Only Access  | 0    | 0    | 1    | *  | 1   | 0   | *        | *         |

# 7-4-1-3. Attribute Memory address

| Address             | #CE | #REG | #WE | #OE                          | FCR                                    | Read/Write |

|---------------------|-----|------|-----|------------------------------|----------------------------------------|------------|

| *                   | 1   | *    | *   | *                            | Standby                                | Invalid    |

| *                   | 0   | 1    | 1   | 0                            | Common Memory Read                     | R          |

| *                   | 0   | 1    | 0   | 1                            | Common Memory Write                    | W          |

| *                   | 0   | 0    | 1   | 0                            | Card Information Structure Read        | R          |

| *                   | 0   | 0    | *   | *                            | Invalid Access                         | Invalid    |

| 200h                | 0   | 0    | 1   | 0                            | Configuration Option Register          | R/W        |

| 20011               | 0   | 0    | 0   | 1                            | Configuration Option Register          | F/VV       |

| 202h                | 0   | 0    | 1   | 0                            | Card Configuration and Status Register | DAM        |

| 202h                | 0   | 0    | 0   | 1                            | Card Corniguration and Status Register | R/W        |

| 20.45               | 0   | 0    | 1   | 0                            | Dia Danlassusant Danister              | Б          |

| 204h                | 0   | 0    | 0   | 1                            | Pin Replacement Register               | R          |

| 2004                | 0   | 0    | 1   | 0                            | Cooket and Cook Posietes               | DAM        |

| 206h                | 0   | 0    | 0   | 1                            | Socket and Copy Register               | R/W        |

| 200h                | 0   | 0    | 1   | 0                            | Estanded Status Decistor               | R/W        |

| 208h                | 0   | 0    | 0   | 1                            | Extended Status Register               | R/VV       |

| 20Ah                | 0   | 0    | 1   | 0                            | I/O Base 0                             | R/W        |

| ZUAN                | 0   | 0    | 0   | 1                            | TO Base 0                              | R/VV       |

| 20Ch                | 0   | 0    | 1   | 0                            | - I/O Base 1                           | R/W        |

| 20011               | 0   | 0    | 0   | 1                            | TO Dase 1                              | FX/VV      |

| 20Eh                | 0   | 0    | 1   | 0                            | I/O Base 2                             | R/W        |

| ZULII               | 0   | 0    | 0   | 1                            | IIO Dase 2                             | FX/VV      |

| 210h                | 0   | 0    | 1   | 0                            | I/O Base 3                             | R/W        |

| Z 1011              | 0   | 0    | 0   | 1                            | IIO Dase 3                             | F7/VV      |

| 212h                | 0   | 0    | 1   | 0                            | - I/O Limit                            | R/W        |

| Z 1ZII              | 0   | 0    | 0   | 1                            | DO LITTLE                              | F7/VV      |

| 214h                | 0   | 0    | 1   | 0                            | Power Management Register              | R/W        |

| ∠ 1 <del>4</del> 11 | 0   | 0    | 0   | Power Management Register  1 | FX/VV                                  |            |

# 7-4-2. Common Memory space

# 7-4-2-1. Common Memory read operation

During Common Memory Read Cycle, set #REG and #WE to inactive "1", and #OE to active "0".

| Function Mode         | #REG | #CE2 | #CE1 | A0 | #OE | #WE | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|----|-----|-----|----------|-----------|

| Standby Mode          | *    | 1    | 1    | *  | *   | *   | Hi-Z     | Hi-Z      |

| Byte Access (8 Bits)  | 1    | 1    | 0    | 0  | 0   | 1   | Hi-Z     | Even byte |

| Byte Access (6 Bits)  | 1    | 1    | 0    | 1  | 0   | 1   | Hi-Z     | Odd byte  |

| Word Access (16 Bits) | 1    | 0    | 0    | *  | 0   | 1   | Odd byte | Even byte |

| Odd Byte Only Access  | 1    | 0    | 1    | *  | 0   | 1   | Odd byte | Hi-Z      |

# 7-4-2-2. Common Memory write operation

During Common Memory Write Cycle, set #REG and #OE to inactive "1", and #WE to active "0".

| Function Mode         | #REG | #CE2 | #CE1 | A0 | #OE | #WE | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|----|-----|-----|----------|-----------|

| Standby Mode          | *    | 1    | 1    | *  | *   | *   | *        | *         |

| Puto Access (9 Pito)  | 1    | 1    | 0    | 0  | 1   | 0   | *        | Even byte |

| Byte Access (8 Bits)  | 1    | 1    | 0    | 1  | 1   | 0   | *        | Odd byte  |

| Word Access (16 Bits) | 1    | 0    | 0    | *  | 1   | 0   | Odd byte | Even byte |

| Odd Byte Only Access  | 1    | 0    | 1    | *  | 1   | 0   | Odd byte | *         |

# 7-4-3. I/O space

# 7-4-3-1. Read operation in I/O Addressing mode

| Function Mode         | #REG | #CE2 | #CE1 | A0 | #IORD | #IOWR | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|----|-------|-------|----------|-----------|

| Standby Mode          | *    | 1    | 1    | *  | *     | *     | Hi-Z     | Hi-Z      |

| Byte Access (8 Bits)  | 0    | 1    | 0    | 0  | 0     | 1     | Hi-Z     | Even byte |

| Byte Access (6 Bits)  | 0    | 1    | 0    | 1  | 0     | 1     | Hi-Z     | Odd byte  |

| Word Access (16 Bits) | 0    | 0    | 0    | *  | 0     | 1     | Odd byte | Even byte |

| I/O Inhibit           | 1    | *    | *    | *  | 0     | 1     | Hi-Z     | Hi-Z      |

| Odd Byte Only Access  | 0    | 0    | 1    | *  | 0     | 1     | Odd byte | Hi-Z      |

# 7-4-3-2. Write operation in I/O Addressing mode

| Function Mode         | #REG | #CE2 | #CE1 | A0 | #IORD | #IOWR | D15 - D8 | D7 - D0   |

|-----------------------|------|------|------|----|-------|-------|----------|-----------|

| Standby Mode          | *    | 1    | 1    | *  | *     | *     | *        | *         |

| Byte Access (8 Bits)  | 0    | 1    | 0    | 0  | 1     | 0     | *        | Even byte |

| Byte Access (6 Bits)  | 0    | 1    | 0    | 1  | 1     | 0     | *        | Odd byte  |

| Word Access (16 Bits) | 0    | 0    | 0    | *  | 1     | 0     | Odd byte | Even byte |

| I/O Inhibit           | 1    | *    | *    | *  | 1     | 0     | *        | *         |

| Odd Byte Only Access  | 0    | 0    | 1    | *  | 1     | 0     | Odd byte | *         |

# 7-4-4. Access method in ATA register

TC6374AF supports four types of I/O addressing modes for PC Card ATA in the host interface. I/O Addressing mode is determined by the configuration in the FCR Configuration Option Register: D5 - D0 bit, "Function Configuration Index". Access method and addresses in each register are listed below for each I/O Addressing mode.

# 7-4-4-1. Memory Mapped mode

Each register address is shown in the Memory Mapped mode.

7-4-4-1-1. Lower byte access

| #CE2 | #CE1 | #REG  | Offset | A10 | A9-A4   | A3 | A2  | A1 | A0  | D15-D8 | D7-                        | -D0                         |

|------|------|-------|--------|-----|---------|----|-----|----|-----|--------|----------------------------|-----------------------------|

| #OLZ | #OL1 | #IXLO | Oliset | Α10 | 7,5-7,4 | 2  | 7,2 | Α' | 7.0 | 010-00 | #OE = "0"                  | #WE = "0"                   |

| 1    | 0    | 1     | 0h     | 0   | *       | 0  | 0   | 0  | 0   |        | Read Data                  | Write Data                  |

| 1    | 0    | 1     | 1h     | 0   | *       | 0  | 0   | 0  | 1   |        | Error                      | Features                    |

| 1    | 0    | 1     | 2h     | 0   | *       | 0  | 0   | 1  | 0   |        | Sector Count               | Sector Count                |

| 1    | 0    | 1     | 3h     | 0   | *       | 0  | 0   | 1  | 1   |        | Sector Number              | Sector Number               |

| 1    | 0    | 1     | 4h     | 0   | *       | 0  | 1   | 0  | 0   |        | Cylinder Low               | Cylinder Low                |

| 1    | 0    | 1     | 5h     | 0   | *       | 0  | 1   | 0  | 1   |        | Cylinder High              | Cylinder High               |

| 1    | 0    | 1     | 6h     | 0   | *       | 0  | 1   | 1  | 0   |        | Device/Head                | Device/Head                 |

| 1    | 0    | 1     | 7h     | 0   | *       | 0  | 1   | 1  | 1   | Hi-Z   | Status                     | Command                     |

| 1    | 0    | 1     | 8h     | 0   | *       | 1  | 0   | 0  | 0   |        | Duplicate Read Data        | Duplicate Write Data        |

| 1    | 0    | 1     | 9h     | 0   | *       | 1  | 0   | 0  | 1   |        | Duplicate Odd Read<br>Data | Duplicate Odd Write<br>Data |

| 1    | 0    | 1     | Dh     | 0   | *       | 1  | 1   | 0  | 1   |        | Duplicate Error            | Duplicate Features          |

| 1    | 0    | 1     | Eh     | 0   | *       | 1  | 1   | 1  | 0   |        | Alternate Status           | Device Control              |

| 1    | 0    | 1     | Fh     | 0   | *       | 1  | 1   | 1  | 1   |        | Device Address             | Reserved                    |

| 1    | 0    | 1     | -      | 1   | *       | *  | *   | *  | 0   |        | Read Data                  | Write Data                  |

| 1    | 0    | 1     | -      | 1   | *       | *  | *   | *  | 1   |        | Odd Read Data              | Odd Write Data              |

7-4-4-1-2. Upper byte access

|      | . I zi oppor syto doodoo |      |        |     |       |    |    |    |    |                            |                             |       |  |

|------|--------------------------|------|--------|-----|-------|----|----|----|----|----------------------------|-----------------------------|-------|--|

| #CE2 | #CE1                     | #REG | Offset | A10 | A9-A4 | A3 | A2 | A1 | A0 | D1                         | 5-8                         | D7-D0 |  |

| #CL2 | #CL1                     | #NLG | Oliset | Alo | A3-A4 | AS | AZ | Ai | Au | #OE = "0"                  | #WE = "0"                   | D7-D0 |  |

| 0    | 1                        | 1    | 0h,1h  | 0   | *     | 0  | 0  | 0  | *  | Error                      | Features                    |       |  |

| 0    | 1                        | 1    | 2h,3h  | 0   | *     | 0  | 0  | 1  | *  | Sector Number              | Sector Number               |       |  |

| 0    | 1                        | 1    | 4h,5h  | 0   | *     | 0  | 1  | 0  | *  | Cylinder High              | Cylinder High               |       |  |

| 0    | 1                        | 1    | 6h,7h  | 0   | *     | 0  | 1  | 1  | *  | Status                     | Command                     |       |  |

| 0    | 1                        | 1    | 8h,9h  | 0   | *     | 1  | 0  | 0  | *  | Duplicate Odd<br>Read Data | Duplicate Odd<br>Write Data | Hi-Z  |  |

| 0    | 1                        | 1    | Ch,Dh  | 0   | *     | 1  | 1  | 0  | *  | Duplicate Error            | Duplicate Features          |       |  |

| 0    | 1                        | 1    | Eh,Fh  | 0   | *     | 1  | 1  | 1  | *  | Device Address             | Reserved                    |       |  |

| 0    | 1                        | 1    | -      | 1   | *     | *  | *  | *  | *  | Odd Read Data              | Odd Write Data              |       |  |

# 7-4-4-1-3. Word access

|      |      |      |          |     |       |    |    |     |    | #OE = "0"                   | #WE = "0"                    |