### **FEATURES**

- On-chip tunable voltage-controlled crystal oscillator circuitry (VCXO) allows precise system frequency tuning (pull range 200ppm minimum).

- VCXO tuning range: 0-3.3V.

- Uses inexpensive fundamental-mode crystals.

- Integrated phase-locked loop (PLL) multiplies VCXO frequency to the higher system frequencies needed.

- 3.3V supply voltage.

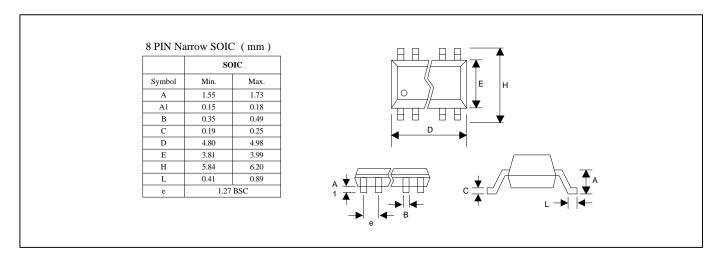

- Small circuit board footprint (8-pin 0.150 SOIC).

- Custom frequency selections available.

- 12mA output drives capability at TTL level.

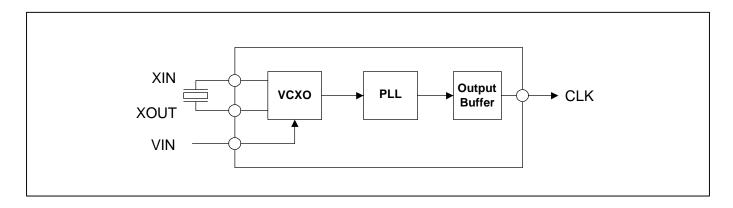

#### **DESCRIPTIONS**

The PLL501-21/23 is a monolithic low Jitter, high performance CMOS clock generator IC. It has a circuitry that implements a voltage-controlled crystal oscillator when an external resonator (nominally 13.5MHz) is attached. The VCXO allows device frequencies to be precisely adjusted for matching requirements.

This product is ideal for Set-Top Box and multimedia synthesizer applications.

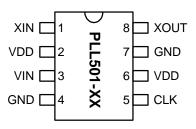

### PIN CONFIGURATION

**Table 1: Crystal / Output Frequencies**

| DEVICE    | F <sub>XIN</sub> (MHz) | CLK (MHz) |

|-----------|------------------------|-----------|

| PLL501-21 | 13.5                   | 27        |

| PLL501-23 | 13.5                   | 54        |

Note: Contact PhaseLink for custom PLL Frequencies

### **BLOCK DIAGRAM**

# **PIN DESCRIPTIONS**

| Name | Number | Туре | Description                                                              |  |  |

|------|--------|------|--------------------------------------------------------------------------|--|--|

| XIN  | 1      | I    | Crystal input connection (parallel mode crystal, C <sub>L</sub> = 14pF). |  |  |

| VDD  | 2      | Р    | 3.3V Power Supply.                                                       |  |  |

| VIN  | 3      | I    | Voltage Input for VCXO Frequency Control.                                |  |  |

| GND  | 4      | Р    | Ground for PLL Core.                                                     |  |  |

| CLK  | 5      | 0    | Clock Output.                                                            |  |  |

| VDD  | 6      | Р    | 3.3V Power Supply.                                                       |  |  |

| GND  | 7      | Р    | Ground.                                                                  |  |  |

| XOUT | 8      | 0    | Crystal connection.                                                      |  |  |

### **ELECTRICAL SPECIFICATIONS**

# 1. Absolute Maximum Ratings

| PARAMETERS                                | SYMBOL          | MIN.                 | MAX.                 | UNITS |

|-------------------------------------------|-----------------|----------------------|----------------------|-------|

| Supply Voltage                            | V <sub>DD</sub> |                      | 7                    | V     |

| Input Voltage, dc                         | Vı              | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                        | Vo              | V <sub>SS</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature                       | Ts              | -65                  | 150                  | °C    |

| Ambient Operating Temperature             | TA              | 0                    | 70                   | °C    |

| Junction Temperature                      | TJ              |                      | 125                  | °C    |

| Lead Temperature (soldering, 10s)         |                 |                      | 260                  | °C    |

| Input Static Discharge Voltage Protection |                 |                      | 2                    | KV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

# 2. DC Electrical Specifications

| PARAMETERS                        | SYMBOL           | CONDITIONS                 | MIN.                | TYP. | MAX. | UNITS |

|-----------------------------------|------------------|----------------------------|---------------------|------|------|-------|

| Supply Current, Dynamic,          | - 1              | f <sub>XTA</sub> = 13.5MHz |                     | 20   |      | mA    |

| with Loaded Outputs               | I <sub>DD</sub>  | Ouput load of 4pF          |                     |      |      |       |

| Operating Voltage                 | $V_{DD}$         |                            | 3.13                |      | 3.47 | V     |

| Output High Voltage               | V <sub>он</sub>  | I <sub>OH</sub> = -12mA    | 2.4                 |      |      | V     |

| Output Low Voltage                | V <sub>OL</sub>  | I <sub>LO</sub> = 12mA     |                     |      | 0.4  | V     |

| Output High Voltage at CMOS level | V <sub>онс</sub> | I <sub>OH</sub> = -4mA     | V <sub>DD</sub> 0.4 |      |      | V     |

| Operating Supply Current          | I <sub>DD</sub>  | No Load                    |                     | 7    |      | mA    |

| Short Circuit Current             |                  |                            |                     | ±50  |      | mA    |

| VIN, VCXO Control Voltage         |                  |                            | 0                   |      | 3.3  | V     |

# 3. AC Electrical Specifications

| PARAMETERS              | SYMBOL         | CONDITIONS      | MIN. | TYP. | MAX. | UNITS |

|-------------------------|----------------|-----------------|------|------|------|-------|

| Input Crystal Frequency |                |                 |      | 13.5 |      | MHz   |

| Input Crystal Accuracy  |                |                 |      |      | ±30  | ppm   |

| Output Clock Rise Time  | tr             | 0.8V ~ 2.0V     |      |      | 1.5  | ns    |

| Output Clock Fall Time  | t <sub>f</sub> | 2.0V ~ 0.8V     |      |      | 1.5  | ns    |

| Output Clock Duty Cycle |                | Measured @ 1.4V | 45   | 50   | 55   | %     |

| Max Absolute Jitter     |                | Short Term      |      | 100  |      | ps    |

| Short Circuit Current   |                |                 |      | ±50  |      | mA    |

| CLK output pullability  |                | 0V≤VIN≤3.3V     | ±100 |      |      | ppm   |

# 4. Voltage Control Crystal Oscillator

| PARAMETERS                                | SYMBOL               | CONDITIONS                                       | MIN. | TYP. | MAX. | UNITS |

|-------------------------------------------|----------------------|--------------------------------------------------|------|------|------|-------|

| PLL Stabilization Time *                  | T <sub>PLLSTB</sub>  | From VCXO stable                                 |      | 500  |      | us    |

| VCXO Stabilization Time *                 | Tvcxostb             | From power valid                                 |      | 10   |      | ms    |

| Output Frequency Synthesis<br>Error       |                      | (Unless otherwise noted in Frequency Table)      |      |      | ±30  | ppm   |

| Crystal Resonator<br>Frequency            | f <sub>XTAL</sub>    | Parallel Fundamental<br>Mode                     | 10   | 13.5 | 15   | MHz   |

| Crystal Loading<br>Capacitance            | C <sub>L(xtal)</sub> | V <sub>XTUNE</sub> =1.65V                        |      | 14   |      | pF    |

| Crystal Resonator Motional<br>Capacitance | C <sub>1(xtal)</sub> | At cut                                           |      | 25   |      | fF    |

| VCXO Tuning Range                         |                      | $f_{XTA} = 13.5MHz;$<br>$C_L=14pF; C_{MOT}=25fF$ |      | 200  |      | ppm   |

| VCXO Tuning Characteristic                |                      |                                                  |      | 100  |      | ppm/V |

Note: Parameters denoted with an asterisk ( \* ) represent nominal characterization data and are not production tested to any specific limits.

### **External Components**

The PLL501-21/23 requires a minimum number of external components for proper operation. A decoupling capacitor of  $0.01\mu F$  should be connected between VDD and GND on pin2 and 4, as close to the PLL501-21/23 as possible. A series termination resistor of  $33\Omega$  may be used for the clock output. The input crystal must be connected as close to the chip as possible. The input crystal should be a parallel mode, pullable, AT cut, 13.5MHz, with 14pF load capacitance and a C0/C1 ratio of maximum 250. Consult PhaseLink for recommended suppliers.

### **PACKAGE INFORMATION**

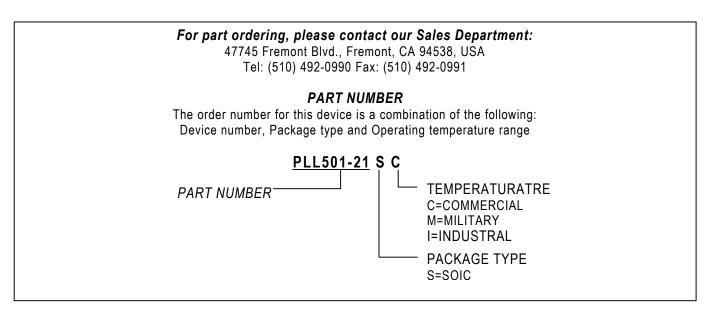

#### ORDERING INFORMATION

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Phaselink is believed to be accurate and reliable. However, PhaseLink makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: PhaseLink s products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.