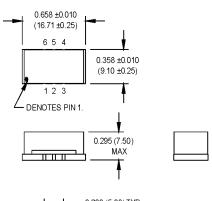

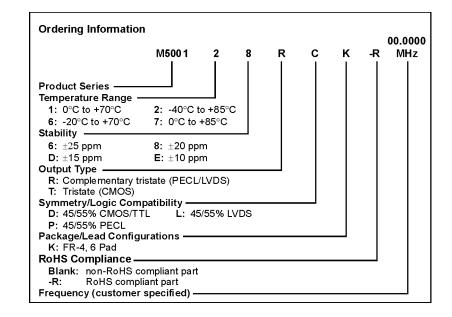

## M5001 Series

## 9x16 mm FR-4, 3.3 Volt, CMOS/TTL/PECL/LVDS, HPXO

Ideal for applications requiring long term (20 year) all-inclusive stability

## **Pin Connections**

| PIN | FUNCTION |  |  |  |  |

|-----|----------|--|--|--|--|

| 1   | N/C      |  |  |  |  |

| 2   | Tristate |  |  |  |  |

| 3   | Gro und  |  |  |  |  |

| 4   | Output 1 |  |  |  |  |

| 5   | Output 2 |  |  |  |  |

| 6   | +Vcc/Vdd |  |  |  |  |

|                           | PARAMETER             | Symbol  | Min.                                                                        | Тур.  | Max.   | Units   | Condition/Notes          |

|---------------------------|-----------------------|---------|-----------------------------------------------------------------------------|-------|--------|---------|--------------------------|

|                           | Frequency Range       | F       | 1                                                                           |       | 160    | MHz     | CMOS/TTL                 |

|                           |                       | ·       | 19.44                                                                       |       | 800    | MHz     | PECL/LVDS                |

|                           | Operating Temperature | TA      | (See Ordering Information)                                                  |       |        |         |                          |

|                           | Storage Temperature   | Ts      | -55                                                                         |       | +105   | °C      |                          |

|                           | Frequency Stability   | ∆F/F    | (See Ordering Information)                                                  |       |        |         | See Note 1               |

|                           | Aging                 |         |                                                                             |       |        |         |                          |

|                           | 1st Year              |         |                                                                             |       | 1.5    | ppm     |                          |

|                           | Thereafter (per year) |         |                                                                             |       | 0.5    | ppm     |                          |

|                           | Input Voltage         | Vcc/Vdd | 3.15                                                                        | 3.3   | 3.45   | V       |                          |

|                           | Input Current         | lcc/ldd | 5                                                                           |       | 50     | mA      | CMOS/TTL                 |

| ns                        |                       |         | 50                                                                          |       | 120    | mA      | PECL                     |

|                           |                       |         | 5                                                                           |       | 75     | mA      | LVDS                     |

| atio .                    | Output Type           |         |                                                                             |       |        |         | CMOS/TTL/PECL/LVDS       |

| Electrical Specifications | Load                  |         | 2 TTL or 15 pF Max.<br>50 Ohms to Vcc -2 Volts<br>100 Ohm differential load |       |        |         | CMOS/TTL<br>PECL<br>LVDS |

| trical S                  | Symmetry (Duty Cycle) |         | (See Ordering Information)                                                  |       |        |         |                          |

|                           | Output Skew           |         | `                                                                           | Ι     | 50     | ps      | PECL                     |

| ec                        | Differential Voltage  |         | 250                                                                         | 375   | 500    | mV      | LVDS                     |

|                           | Logic "1" Level       | Voh     | 2.5                                                                         |       |        | ٧       | CMOS/TTL                 |

|                           |                       |         | 2.2                                                                         |       | 2.4    | V       | PECL                     |

|                           |                       |         | 1.375                                                                       |       |        | v       | LVDS                     |

|                           | Logic "0" Level       | Vol     |                                                                             |       | 0.5    | ٧       | CMOS/TTL                 |

|                           |                       |         | 1.4                                                                         |       | 1.7    | V       | PECL                     |

|                           |                       |         |                                                                             |       | 1.125  | v       | LVDS                     |

|                           | Rise/Fall Time        | Tr/Tf   | 2.0                                                                         |       | 10     | ns      | CMOS/TTL                 |

|                           |                       |         | 0.25                                                                        |       | 3.0    | ns      | PECL/LVDS                |

|                           | Tristate Function     |         | Input Logic "1": output active                                              |       |        |         | Opposite tristate logic  |

|                           |                       |         | Input Logic "0": output disables                                            |       |        |         | Available upon request   |

|                           | Start up Time         |         | 10                                                                          |       |        | ms      |                          |

|                           | Phase Noise (Typical) | 10 Hz   | 100 Hz                                                                      | 1 kHz | 10 kHz | 100 kHz | Offset from carrier      |

|                           | @ 19.44 MHz           | -60     | -90                                                                         | -120  | -135   | -148    | dBc/Hz                   |

|                           | @ 155.52 MHz          | -60     | -90                                                                         | -110  | -120   | -120    | dBc/Hz                   |

|                           | @ 622.08 MHz          | -60     | -90                                                                         | -100  | -105   | -105    | dBc/Hz                   |

Stability includes initial tolerance, deviation over temperature, supply and load variation, and aging for 20 years @ 25°C.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

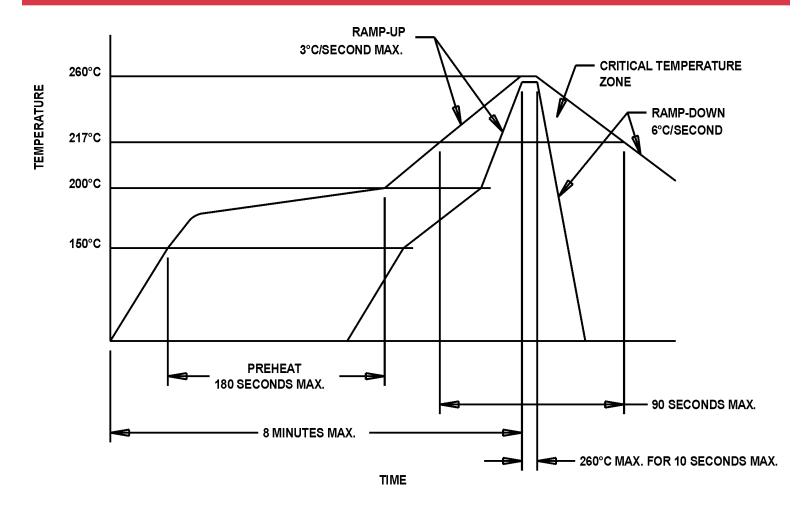

## MtronPTI Lead Free Solder Profile