01.08.28

### ♦ Features

- +5 V single power supply

- 20 dB typical gain

- 2.0 GHz typical -3 dB cutoff frequency

- On-chip matching to 50  $\Omega$

- 55 mA typical operating current

- Low-cost 18-lead MFP package

- Differential input and output

- Differential ECL compatible input

# F0321818M

2 GHz Bandwidth

Limiting Amplifier

## Applications

- Post-amplifier of an optical receiver circuit up to 2.5 Gb/s

- Logic gate buffer to interface between analog circuit and logic circuit

## ♦ Functional Description

The F0321818M is a stable GaAs integrated limiting amplifier for use in a post-amplifier of an optical receiver circuit up to 2.5 Gb/s. The F0321818M typically specifies a small signal gain of 20 dB (Rs=RL=50  $\Omega$ ) with a 3 dB-cutoff-frequency of 2.0 GHz. It features single +5 V supply operation, excellent VSWR's of 1.1:1, and a typical dissipation current of 55 mA.

The F0321818M can be also used as interface circuits in sensing systems and measurement instruments. Emitter coupled logic (ECL) or source coupled FET logic (SCFL) circuits are the most popular IC's for high speed digital circuits; the F0321818M operating under a differential ECL compatible input condition is the best choice as the interface IC to join analog circuits to ECL circuits or conventional GaAs logic IC's.

# ♦ Absolute Maximum Ratings

T<sub>a</sub>=25 °C, unless specified

| Parameter                     | Symbol                                  | Value                                      | Units |

|-------------------------------|-----------------------------------------|--------------------------------------------|-------|

| Supply Voltage                | V <sub>DD</sub>                         | V <sub>ss</sub> -0.5 to V <sub>ss</sub> +7 | V     |

| Supply Current                | I <sub>DD</sub>                         | 80                                         | mA    |

| Input Voltage Swing(AC)       | V <sub>IN+</sub> , V <sub>IN-</sub>     | 1                                          | V     |

| Output Voltage                | $V_{\text{OUT+},}^{}V_{\text{OUT-}}^{}$ | $V_{DD}$ -2.5 to $V_{DD}$                  | V     |

| Ambient Operating Temperature | T <sub>a</sub>                          | 0 to +70                                   | ° C   |

| Storage Temperature           | T <sub>stg</sub>                        | -55 to +125                                | ° C   |

# ♦ Recommended Operating Conditions

$$V_{SS} = GND$$

| Parameter                     | Symbol          | Value |      |      | Units  |  |

|-------------------------------|-----------------|-------|------|------|--------|--|

|                               |                 | Min.  | Тур. | Max. | Ullits |  |

| Supply Voltage                | V <sub>DD</sub> | 4.75  | 5    | 5.46 | V      |  |

| AC Coupled Load               | RL              | -     | 50   | -    | Ω      |  |

| Ambient Operating Temperature | T <sub>a</sub>  | 0     | 25   | 70   | ° C    |  |

## ♦ Electrical Characteristics

$$\rm T_a$$

= 25 °C,  $\rm V_{DD}$  = +5V,  $\rm V_{SS}$  = GND, unless specified

| Parameter                            | Symbol           | Test Conditions             | Value |      |      | Units  |

|--------------------------------------|------------------|-----------------------------|-------|------|------|--------|

|                                      |                  |                             | Min.  | Тур. | Max. | Offics |

| Supply Current                       | I <sub>DD</sub>  | Pin=-40dBm                  | -     | 55   | 70   | mA     |

| Input Bias Point                     | V <sub>IN</sub>  |                             | -     | 1.5  | -    | V      |

| Output bias Point                    | V <sub>OUT</sub> |                             | -     | 3.5  | -    | V      |

| VSWR (IN, OUT)                       | SWR              | Pin=-40dBm f=1MHz           | -     | 1.1  | 1.8  | -      |

| Gain                                 | GV               | Pin=-40dBm<br>RL=50Ω f=1MHz | 18    | 20   | -    | dB     |

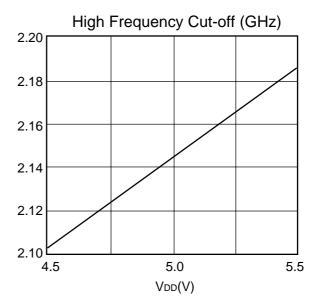

| -3dB High Frequency Cutoff           | Fc               | Pin=-40dBm<br>RL=50Ω        | 1.8   | 2.0  | -    | GHz    |

| Maximum Output Swing (single output) | Vom              | RL=50Ω                      | 0.4   | 0.6  | 0.8  | V      |

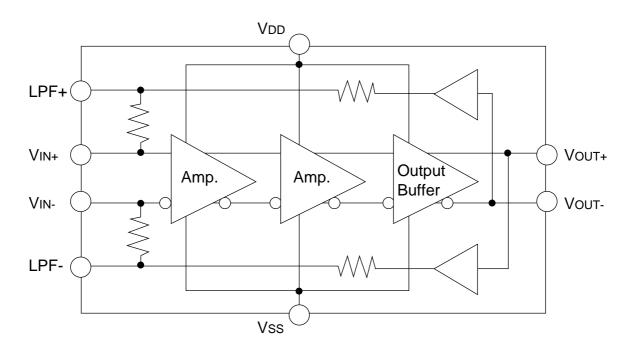

# ♦ Block Diagram

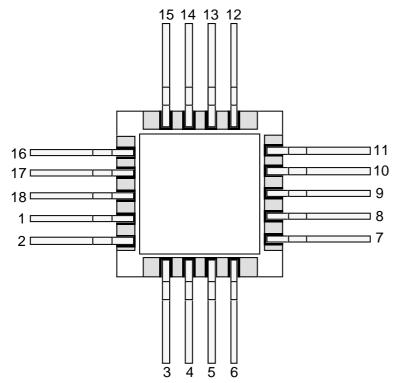

# ♦ Pin Assignments (Top View)

NOTE: Package bottom is Internally connected to  $\mathbf{V}_{\mathrm{SS}}$

# ♦ Pin Descriptions

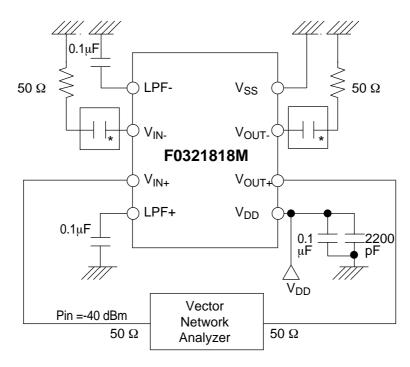

## **♦ Test Circuits**

## 1) AC Characteristics

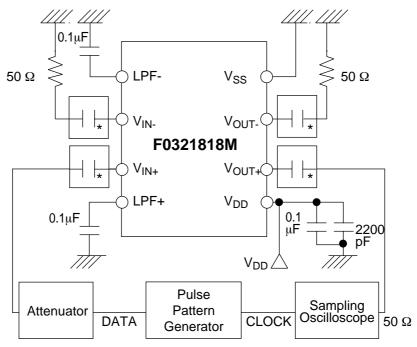

### 2) Limiting Characteristics

\* DC BLOCK (PICOSECIND PULSE LABS, MODEL 5501)

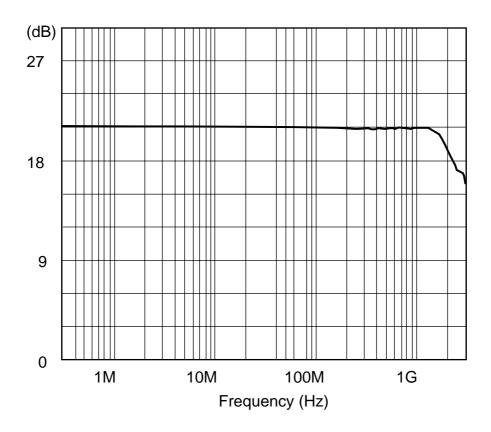

## ♦ Typical AC Characteristics

(1) Gain

$$\rm T_a$$

=25 °C,  $\rm V_{DD}$  =+5 V,  $\rm V_{SS}$  =GND, Pin =-40 dBm, RL =50  $\Omega,$  300 kHz-3 GHz

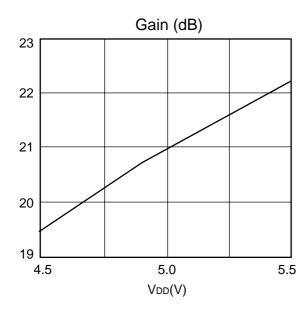

(2) Dependance of Gain and High Frequency Cutoff on Power Supply Variations  ${\rm T_a=}25~^{\circ}{\rm C},~{\rm V_{DD}=}-5~{\rm V},~{\rm V_{SS}=}{\rm GND},~{\rm Pin=}-40~{\rm dBm},~{\rm RL=}50~\Omega,~300~{\rm kHz-}3~{\rm GHz}$

# ◆ Typical AC Characteristics

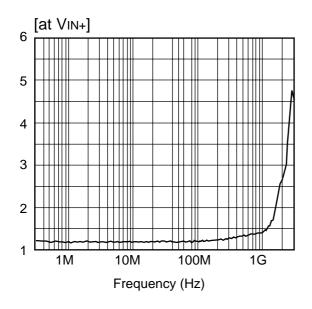

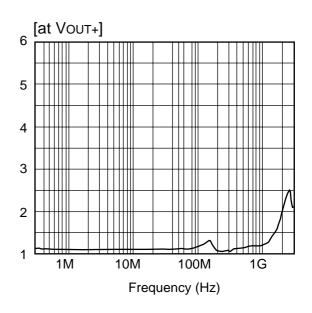

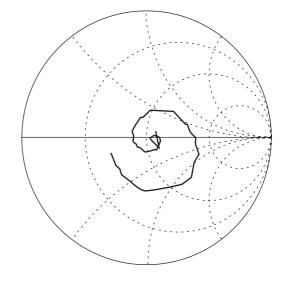

### (3) VSWR's

$\rm T_a$  =25 °C,  $\rm V_{DD}$  =+5 V,  $\rm V_{SS}$  =GND, Pin =-40 dBm, RL =50  $\Omega,\,300~kHz$  - 3 GHz

<sup>\*</sup>Almost same characteristics is exhibited at  $V_{\text{IN-}}$

\*Almost same characteristics is exhibited at  $V_{\text{OUT}}$

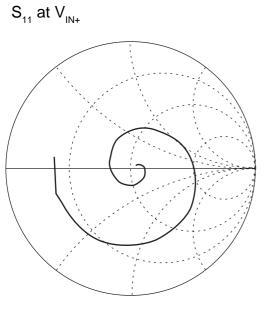

## (4) S parameters on Smith Chart

$$\rm T_a$$

=25 °C,  $\rm V_{DD}$  =+5 V,  $\rm V_{SS}$  =GND, Pin =-40 dBm, RL =50  $\Omega$

START 100 MHz STOF

STOP 3 GHz

START 100 MHz

STOP 3 GHz

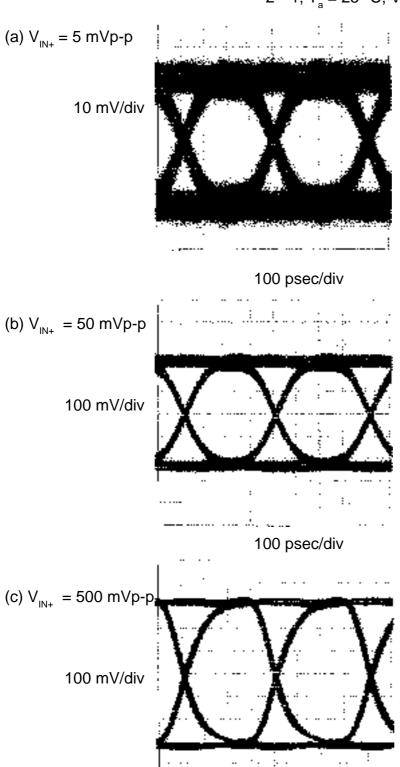

# ♦ Typical Limiting Characteristics

(1) Eye diagrams for 2.5 Gb/s NRZ Pseudo-random Data Response

2<sup>23</sup>-1,

$$T_a$$

= 25 °C,  $V_{DD}$  =5 V,  $V_{SS}$  =GND, RL =50  $\Omega$

100 psec/div

## ♦ General Description

A post-amplifier is positioned between a preamplifier (an amplifier for a faint photocurrent from PIN photo diode) and a decision circuit (a circuit to discriminate the logic level of the received signal), enlarging the output signal from the preamplifier to a higher level to discriminate the logic level. The input signal amplitude of the post-amplifier, meaning the output signal of the preamplifier, varies widely, because the optical signal power received by the PIN photo diode depends on the length of the transmission line. Therefore, the post-amplifier should function to output an almost constant signal level under widely varying input voltage. This is called a limiting function, and the F0321818M provides excellent limiting characteristics. As shown in the data sheet, the increase of only 200 mV (400 mV →600 mV) in the output voltage can be observed even if the 2.5 Gb/s input signal varies widely from 50 mV to 500 mV.

Wide use analog IC's having satisfactory limiting functions as described above can not be found except for the F0321818M. Customized IC's for each application or a circuit designed by discrete transistors are believed to have been developed.

### ♦ Post Matching

Input/output VSWR's of the F0321818M are well-designed for 50  $\Omega$ , typically showing excellent VSWR's of 1.1:1. Therefore, the F0321818M can be applied for 50  $\Omega$  systems with no external parts. Furthermore, the fine VSWR characteristics provide stable operation even for cascade connections of two IC's for a higher gain. The excellent VSWR characteristics of the F0321818M gives full play in a clock recovery system using SAW filters, because the impedance mismatch has a significant effect on the quality of the recovered clock signal.

#### ♦ Gain Consideration

The F0321818M has a small signal gain of 20 dB. A too high gain can be harmful because of parasitic oscillation. If a slightly higher gain is needed, a 6 dB higher gain of 26 dB can be obtained by a high impedance termination instead of a 50  $\Omega$  load. A double gain can be achieved by simple cascade connection if a still higher gain is required.

### ♦ Noise Performance

The F0321818M based on the GaAs FET fabrication process intrinsically has more excellent low-noise characteristics compared with IC's based on the silicon bipolar process. Many transmission systems often demand superior signal-to-noise ratio; the F0321818M is the best choice for such applications.

The differential circuit configuration in the input and output enable a complete differential operation to reduce common mode noise: simple single ended input and output operation is also available.

#### ♦ LPF+ & LPF-

The F0321818M has two terminals, LPF+ and LPF-, for AC ground. These terminals are connected to ground by a capacitor. The time constant of the feedback loop in the F0321818M depends on the capacitor, giving the lower frequency cutoff of the circuit by the large capacitor. A 0.1 micro farad is employed for conventional applications.

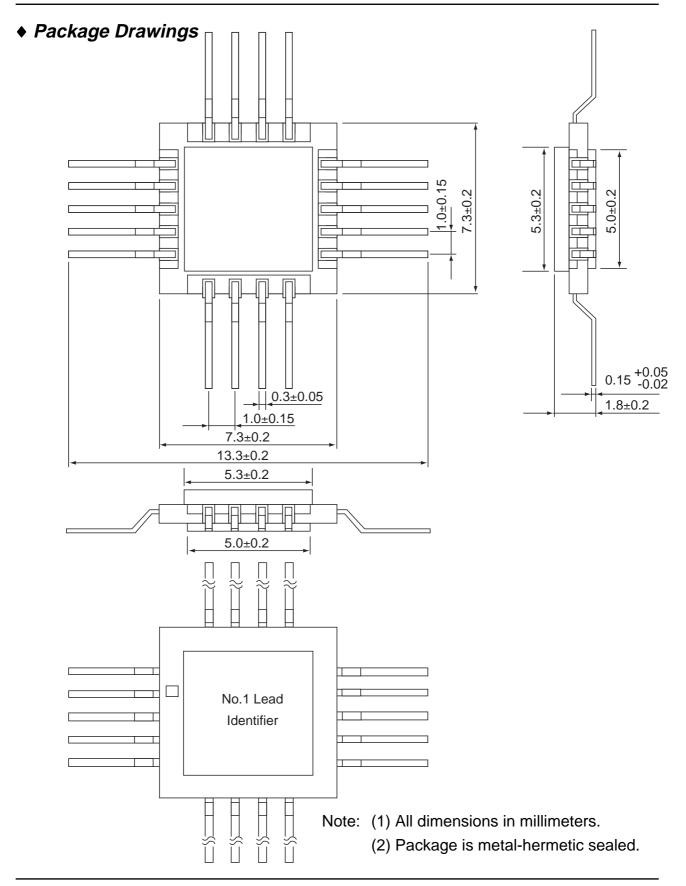

### ◆ Packaging

The F0321818M is in an 18-lead metal-based flat package (MFP) about 300 mil square with the lead pitch of 40 mil, achieving miniaturization and low cost. It is originally developed by SEI to improve RF performance and heat radiation. Comparing with the SOP, the ground potential steadier at microwave frequency range and the thermal receptivity is smaller due to the metal based bottom structure made from CuW (an alloy of copper and tungsten) with a high thermal conductivity. The intrinsic broad band performance of the F0321818M can not be brought out by the standard SOP and LCC, because it is difficult to overcome impedance mismatch at high frequency around 2 GHz. Therefore, SEI's superior package technology enable to achieve the excellent wide band limiting performance of the F0321818M.

#### ♦ Precautions

Owing to their small dimensions, the GaAs FET's from which the F0321818M is designed are easily damaged or destroyed if subjected to large transient voltages. Such transients can be generated by power supplies when switched on if not properly decoupled. It is also possible to induce spikes from static-electricity-charged operations or ungrounded equipment.