# **DS26303** 3.3V, E1/T1/J1, Short-Haul, Octal Line Interface Unit

#### www.maxim-ic.com

## **GENERAL DESCRIPTION**

The DS26303 is an 8-channel short-haul line interface unit (LIU) that supports E1/T1/J1 from a single 3.3V power supply. A wide variety of applications are supported through termination or external termination. A single bill of material can support E1/T1/J1 with minimum external components. Redundancy is supported through nonintrusive monitoring, optimal high-impedance modes, and configurable 1:1 or 1+1 backup enhancements. An on-chip synthesizer generates the E1/T1/J1 clock rates by a single master clock input of various frequencies. Two clock output references are also offered.

## **APPLICATIONS**

T1 Digital Cross-Connects ATM and Frame Relay Equipment Wireless Base Stations ISDN Primary Rate Interface E1/T1/J1 Multiplexer and Channel Banks E1/T1/J1 LAN/WAN Routers

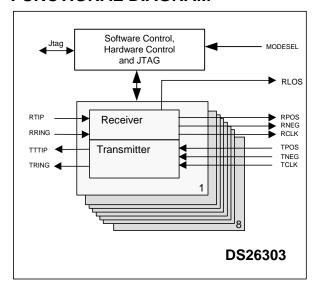

### **FUNCTIONAL DIAGRAM**

### **FEATURES**

- 8 Complete E1, T1, or J1 Short-Haul Line **Interface Units**

- Independent E1, T1, or J1 Selections

- Internal Software-Selectable Transmit and **Receive-Side Termination**

- **Crystal-Less Jitter Attenuator**

- Selectable Single-Rail and Dual-Rail Mode and AMI or HDB3/B8ZS Line Encoding and Decoding

- **Detection and Generation of AIS**

- Digital/Analog Loss-of-Signal Detection as per T1.231, G.775, and ETS 300 233

- **External Master Clock can be Multiple of** 2.048MHz or 1.544MHz for T1/J1 or E1 Operation; This Clock will be Internally Adapted for T1 or E1 Use

- **Built-In BERT Tester for Diagnostics**

- 8-Bit Parallel Interface Support for Intel or Motorola Mode or a 4-Wire Serial Interface

- **Hardware Mode Interface Support**

- **Transmit Short-Circuit Protection**

- **G.772 Nonintrusive Monitoring**

- Specification Compliance to the Latest T1 and E1 Standards—ANSI T1.102, AT&T Pub 62411, T1.231, T1.403, ITU-T G.703, G.742, G.775, G.823, ETS 300 166, and ETS 300 233

- Single 3.3V Supply with 5V Tolerant I/O

- JTAG Boundary Scan as per IEEE 1149.1

- 144-Pin eLQFP Package

#### ORDERING INFORMATION

| PART           | TEMP RANGE     | PIN-PACKAGE |

|----------------|----------------|-------------|

| DS26303L-XXX   | 0°C to +70°C   | 144 eLQFP   |

| DS26303L-XXX+  | 0°C to +70°C   | 144 eLQFP   |

| DS26303LN-XXX  | -40°C to +85°C | 144 eLQFP   |

| DS26303LN-XXX+ | -40°C to +85°C | 144 eLQFP   |

**Note:** When XXX is 075, the part defaults to  $75\Omega$  impedance in E1 mode; when XXX is 120, the part defaults to  $120\Omega$  impedance.

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 101 REV: 053107

<sup>+</sup> Denotes a lead-free/RoHS-compliant package.

e = Exposed Pad.

# **TABLE OF CONTENTS**

| 1 |            | DETAII           | LED DESCRIPTION                                 | 6               |

|---|------------|------------------|-------------------------------------------------|-----------------|

| 2 | 7          | TELEC            | OM SPECIFICATIONS COMPLIANCE                    | 7               |

| 3 |            |                  | ( DIAGRAMS                                      |                 |

| 4 |            |                  | SCRIPTION                                       | _               |

| 4 |            |                  | DWARE AND HOST PORT OPERATION                   |                 |

|   | 4.1        |                  | DWARE AND HOST PORT OPERATION                   |                 |

|   |            |                  | Serial Port Operation                           |                 |

|   |            |                  | Parallel Port Operation                         |                 |

|   |            |                  | Interrupt Handling                              |                 |

| 5 | F          | REGIS            | TERS                                            | 24              |

| _ | 5.1        |                  | ISTER DESCRIPTION                               |                 |

|   |            |                  | Primary Registers                               |                 |

|   |            |                  | Secondary Registers                             |                 |

|   |            | 5.1.3            | Individual LIU Registers                        | <b>40</b>       |

|   |            |                  | BERT Registers                                  |                 |

| 6 | F          | FUNCT            | TONAL DESCRIPTION                               | 54              |

|   | 6.1        | Pow              | ER-UP AND RESET                                 | 54              |

|   | 6.2        | MAS <sup>3</sup> | TER CLOCK                                       | 54              |

|   | 6.3        | TRAN             | NSMITTER                                        | 55              |

|   |            |                  | Transmit Line Templates                         |                 |

|   |            |                  | LIU Transmit Front-End                          |                 |

|   |            |                  | Dual-Rail Mode                                  |                 |

|   |            |                  | Single-Rail ModeZero Suppression—B8ZS or HDB3   |                 |

|   |            | 5.3.6            | Transmit Power-Down                             |                 |

|   |            | 6.3.7            | Transmit All Ones.                              |                 |

|   |            |                  | Driver Fail Monitor                             |                 |

|   | 6.4        | RECI             | EIVER                                           | 59              |

|   | $\epsilon$ | 6.4.1            | Peak Detector and Slicer                        | <mark>59</mark> |

|   |            |                  | Clock and Data Recovery                         |                 |

|   |            |                  | Loss of Signal                                  |                 |

|   |            |                  | AIS                                             |                 |

|   |            |                  | Bipolar Violation and Excessive Zero Detector   |                 |

|   | 6.5        |                  | ESS-PROTECTION SWITCHING (HPS)                  |                 |

|   | 6.6        |                  | ER ATTENUATOR                                   |                 |

|   | 6.7        |                  | '2 Monitor                                      |                 |

|   | 6.8        |                  | PBACKS                                          |                 |

|   |            |                  | Analog Loopback                                 |                 |

|   |            |                  | Digital Loopback                                |                 |

|   | $\epsilon$ |                  | Remote Loopback                                 |                 |

|   |            |                  | Dual Loopback                                   |                 |

|   |            | BER              |                                                 |                 |

|   |            |                  | Configuration and Monitoring                    |                 |

|   |            |                  | BERT Interrupt Handling                         |                 |

|   |            | 6.9.3<br>6.9.4   | Receive Pattern Detection                       |                 |

| 7 |            |                  |                                                 |                 |

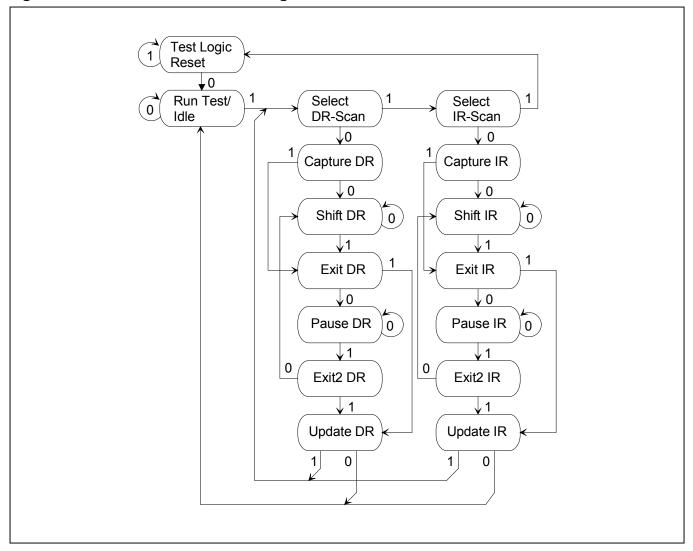

| 7 |            |                  | BOUNDARY SCAN ARCHITECTURE AND TEST ACCESS PORT |                 |

|   | 7.1        |                  | CONTROLLER STATE MACHINE                        |                 |

|   |            | 7.1.1<br>7.1.2   | Test-Logic-Reset                                |                 |

|   |            |                  | Select-DR-Scan                                  |                 |

|   |            |                  | Capture-DR                                      |                 |

|   |            |                  |                                                 |                 |

| 7.1.5 Shift-DR                                                                   | 73 |

|----------------------------------------------------------------------------------|----|

| 7.1.6 Exit1-DR                                                                   | 73 |

| 7.1.7 Pause-DR                                                                   | 73 |

| 7.1.8 Exit2-DR                                                                   | 73 |

| 7.1.9 Update-DR                                                                  | 73 |

| 7.1.10 Select-IR-Scan                                                            | 74 |

| 7.1.11 Capture-IR                                                                |    |

| 7.1.12 Shift-IR                                                                  |    |

| 7.1.13 Exit1-IR                                                                  |    |

| 7.1.14 Pause-IR                                                                  |    |

| 7.1.15 Exit2-IR                                                                  |    |

| 7.1.16 Update-IR                                                                 |    |

| 7.2 Instruction Register                                                         |    |

| 7.2.1 EXTEST                                                                     |    |

| 7.2.2 HIGHZ                                                                      |    |

| 7.2.3 CLAMP                                                                      |    |

| 7.2.4 SAMPLE/PRELOAD                                                             |    |

| 7.2.5 IDCODE                                                                     |    |

| 7.2.6 BYPASS                                                                     |    |

| 7.3 TEST REGISTERS                                                               |    |

| 7.3.1 Boundary Scan Register                                                     |    |

| 7.3.2 Bypass Register                                                            |    |

| 7.3.3 Identification Register                                                    |    |

| 8 OPERATING PARAMETERS                                                           | 78 |

| 9 THERMAL CHARACTERISTICS                                                        | 79 |

|                                                                                  |    |

|                                                                                  |    |

| 10.1 Line Interface Characteristics                                              |    |

| 10.2 PARALLEL HOST INTERFACE TIMING CHARACTERISTICS                              |    |

| 10.3 SERIAL PORT                                                                 | 93 |

| 10.4 SYSTEM TIMING                                                               | 94 |

| 10.5 JTAG TIMING                                                                 | 96 |

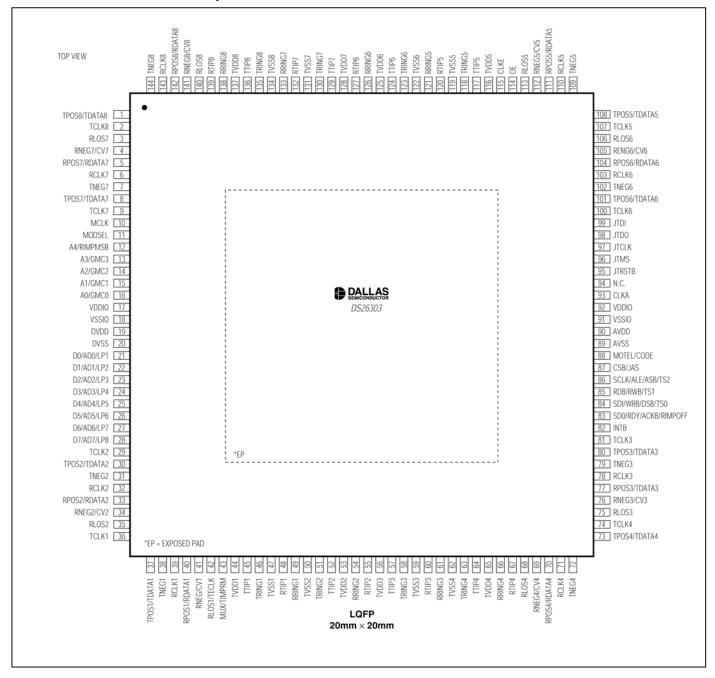

| 11 PIN CONFIGURATION                                                             | 97 |

| 11.1 144-PIN LQFP WITH EXPOSED PAD                                               |    |

|                                                                                  |    |

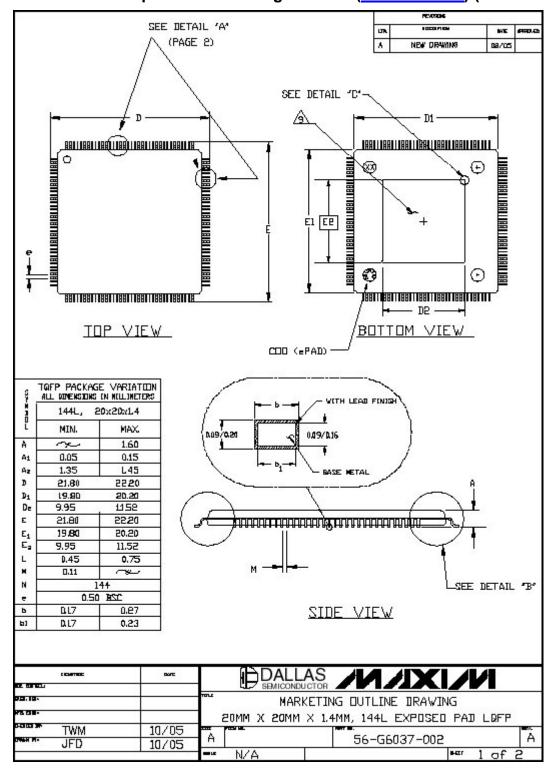

| 12 PACKAGE INFORMATION                                                           |    |

| 12.1 144-PIN LQFP WITH EXPOSED PAD PACKAGE OUTLINE (56-G6037-002) (SHEET 1 OF 2) | 98 |

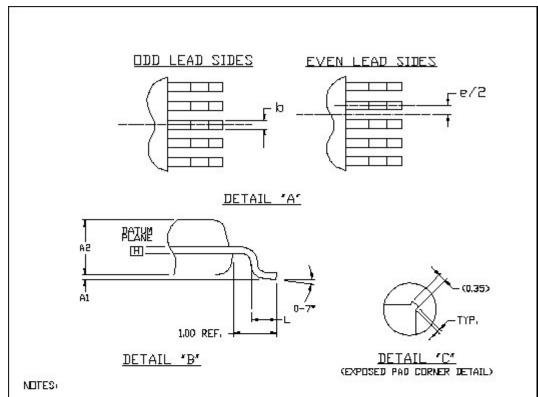

| 12.2 144-PIN LQFP WITH EXPOSED PAD PACKAGE OUTLINE (SHEET 2 OF 2)                |    |

| 13 DOCUMENT DEVISION HISTORY                                                     |    |

# **LIST OF FIGURES**

| Figure 3-1. Block Diagram                                       |    |

|-----------------------------------------------------------------|----|

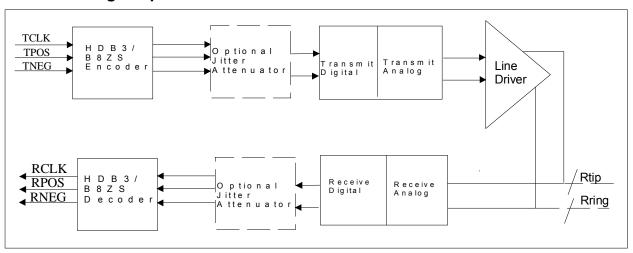

| Figure 3-2. Receive Logic Detail                                |    |

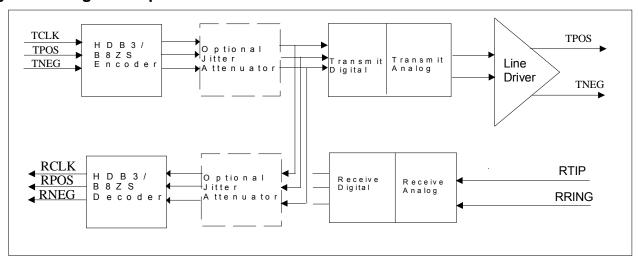

| Figure 3-3. Transmit Logic Detail                               | 10 |

| Figure 4-1. 144-Pin eLQFP Pin Assignment                        |    |

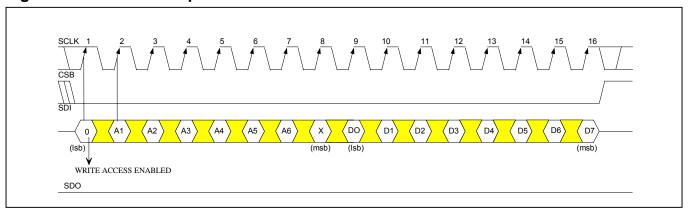

| Figure 4-2. Serial Port Operation for Write Access              |    |

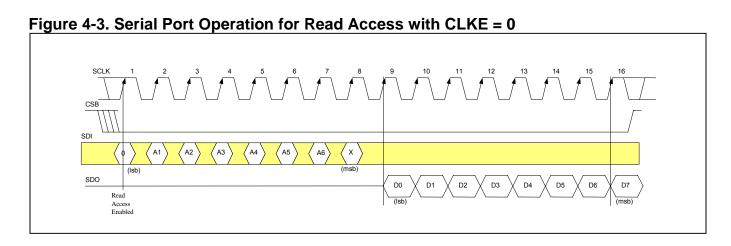

| Figure 4-3. Serial Port Operation for Read Access with CLKE = 0 | 21 |

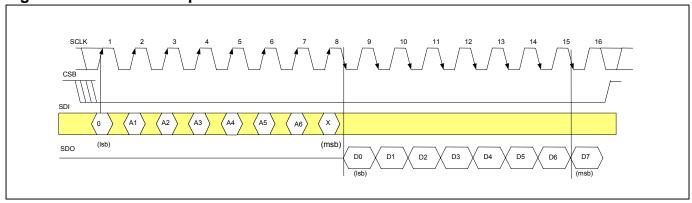

| Figure 4-4. Serial Port Operation for Read Access with CLKE = 1 | 22 |

| Figure 4-5. Interrupt Handling Flow Diagram                     | 23 |

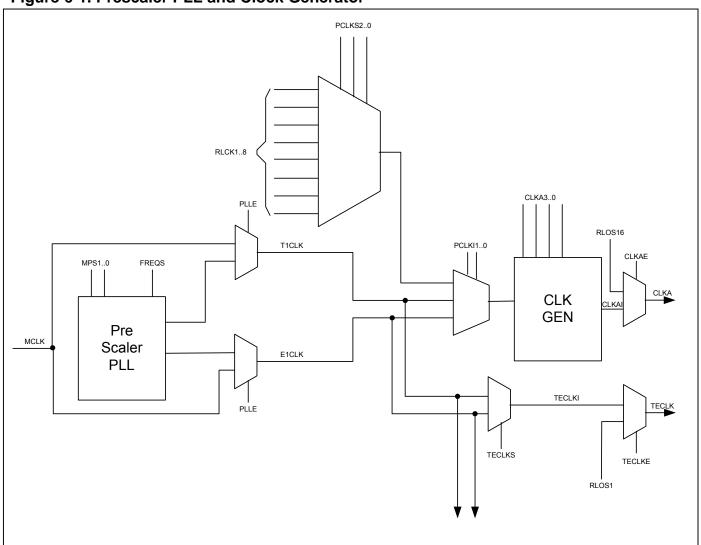

| Figure 6-1. Prescaler PLL and Clock Generator                   | 54 |

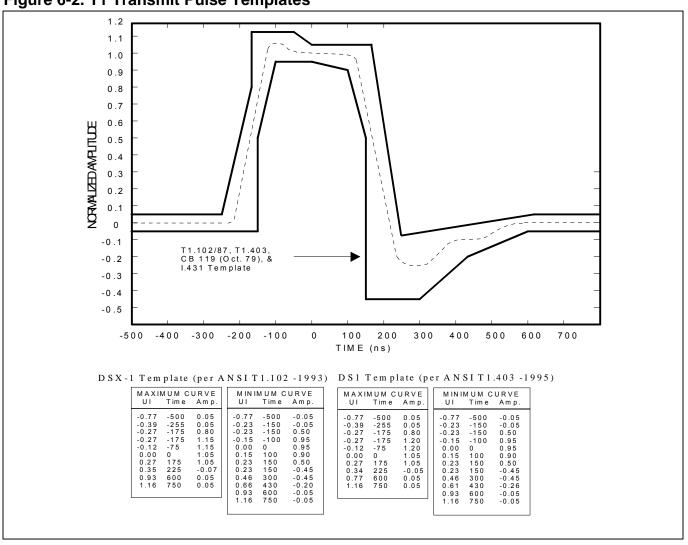

| Figure 6-2. T1 Transmit Pulse Templates                         | 56 |

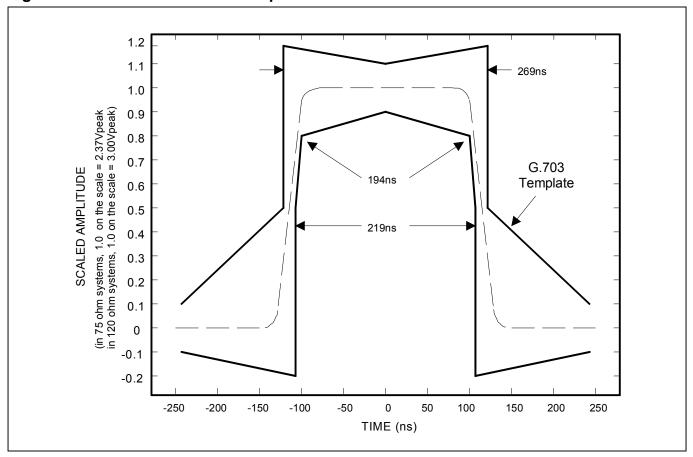

| Figure 6-3. E1 Transmit Pulse Templates                         |    |

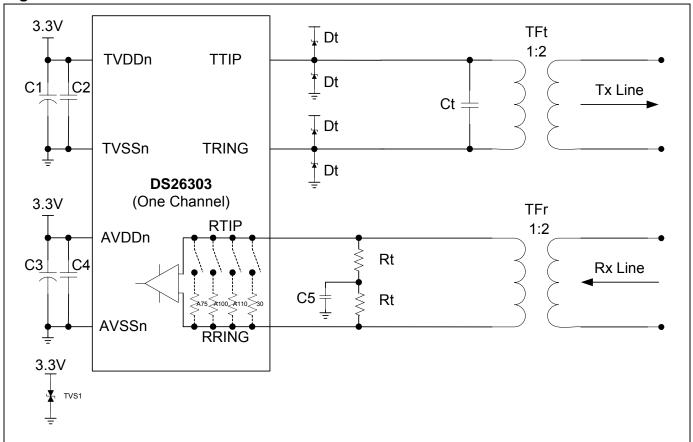

| Figure 6-4. LIU Front-End                                       |    |

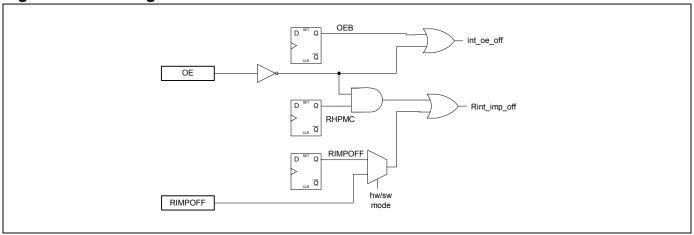

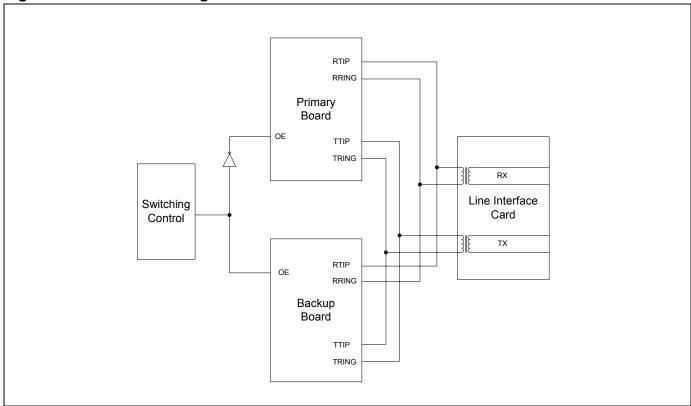

| Figure 6-5. HPS Logic                                           | 63 |

| Figure 6-6. HPS Block Diagram                                   |    |

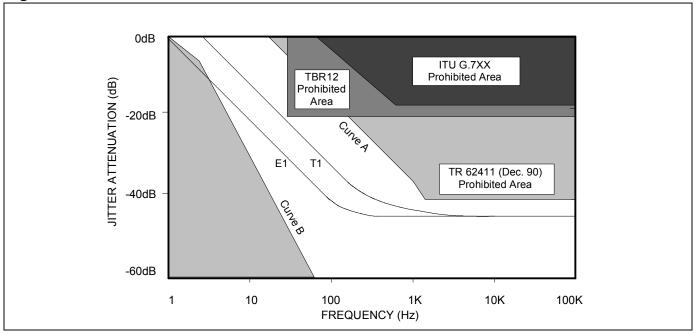

| Figure 6-7. Jitter Attenuation                                  |    |

| Figure 6-8. Analog Loopback                                     | 65 |

| Figure 6-9. Digital Loopback                                    | 66 |

| Figure 6-10. Remote Loopback                                    |    |

| Figure 6-11. Dual Loopback                                      |    |

| Figure 6-12. PRBS Synchronization State Diagram                 |    |

| Figure 6-13. Repetitive Pattern Synchronization State Diagram   |    |

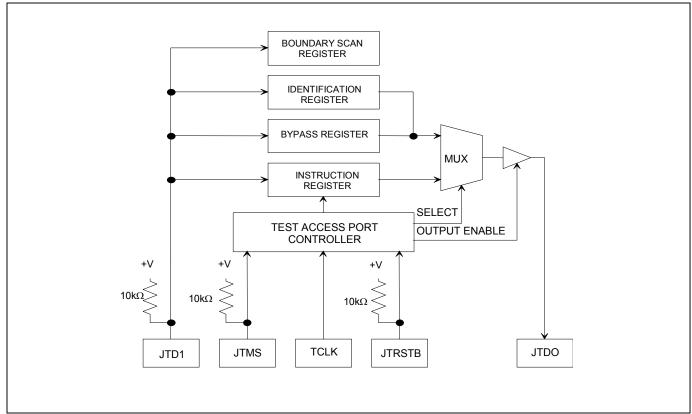

| Figure 7-1. JTAG Functional Block Diagram                       | 72 |

| Figure 7-2. TAP Controller State Diagram                        |    |

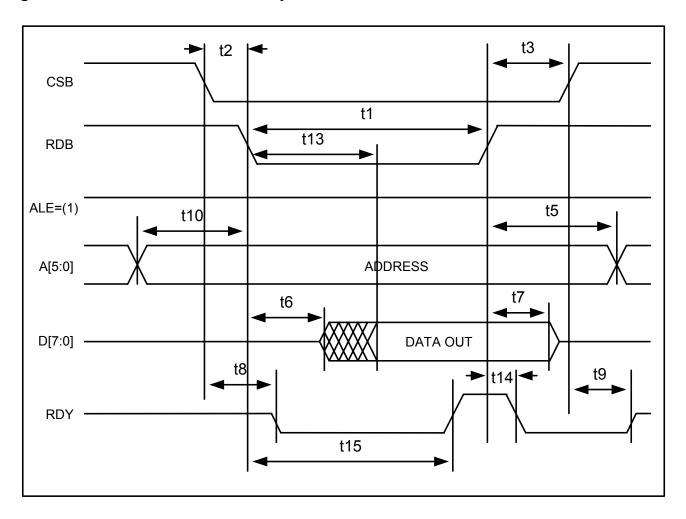

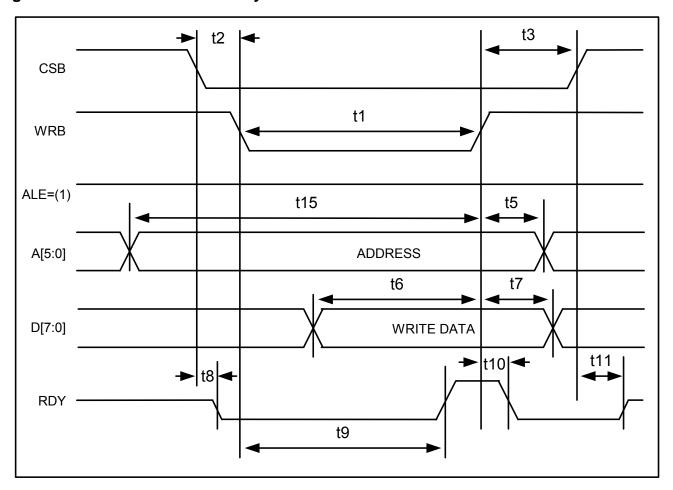

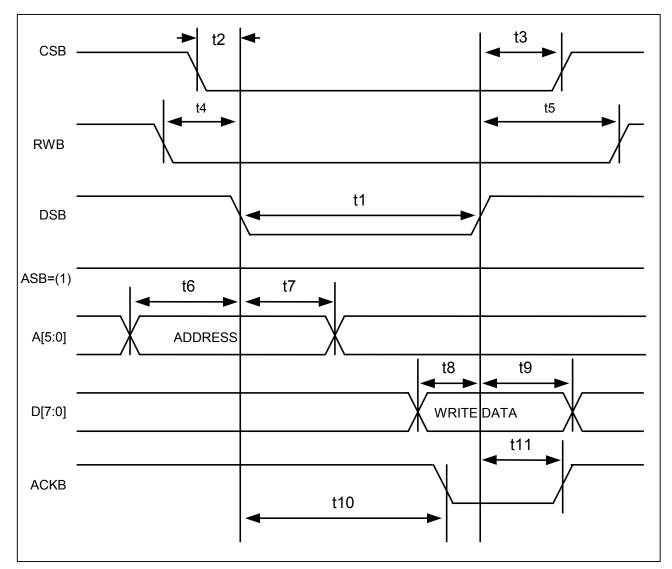

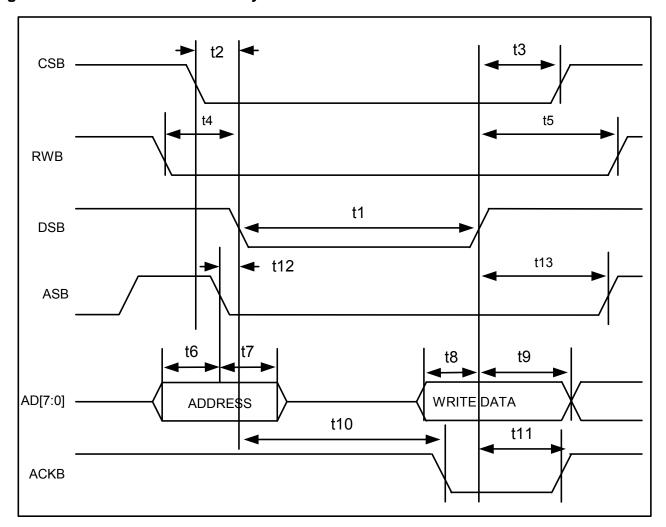

| Figure 10-1. Intel Nonmuxed Read Cycle                          |    |

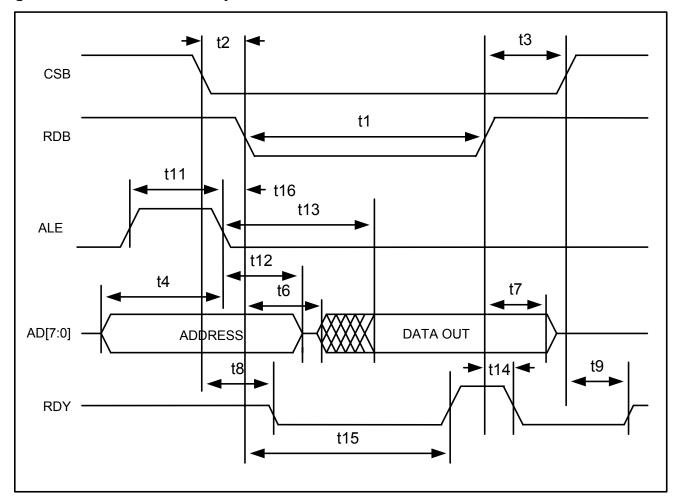

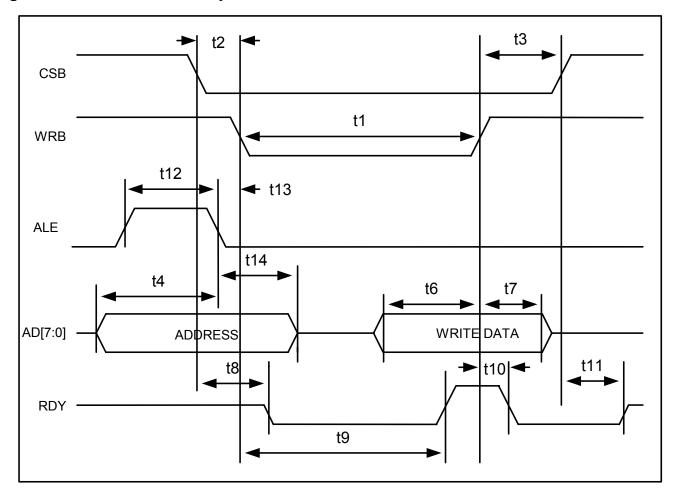

| Figure 10-2. Intel Mux Read Cycle                               |    |

| Figure 10-3. Intel Nonmux Write Cycle                           |    |

| Figure 10-4. Intel Mux Write Cycle                              |    |

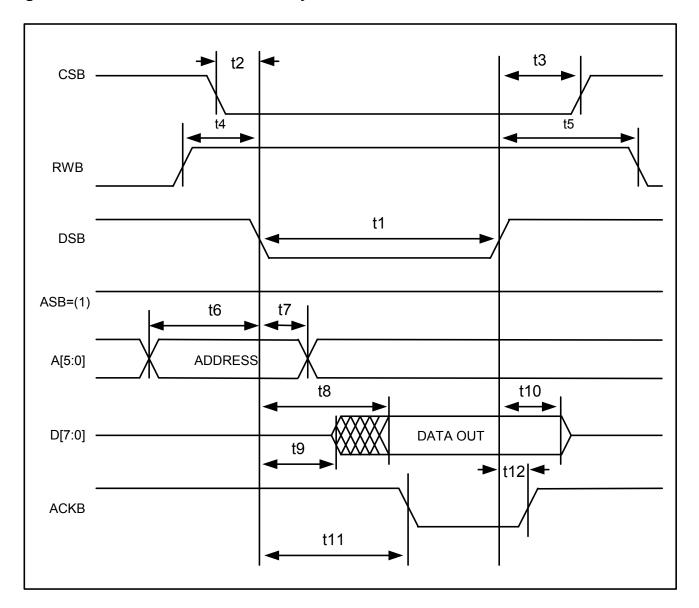

| Figure 10-5. Motorola Nonmux Read Cycle                         |    |

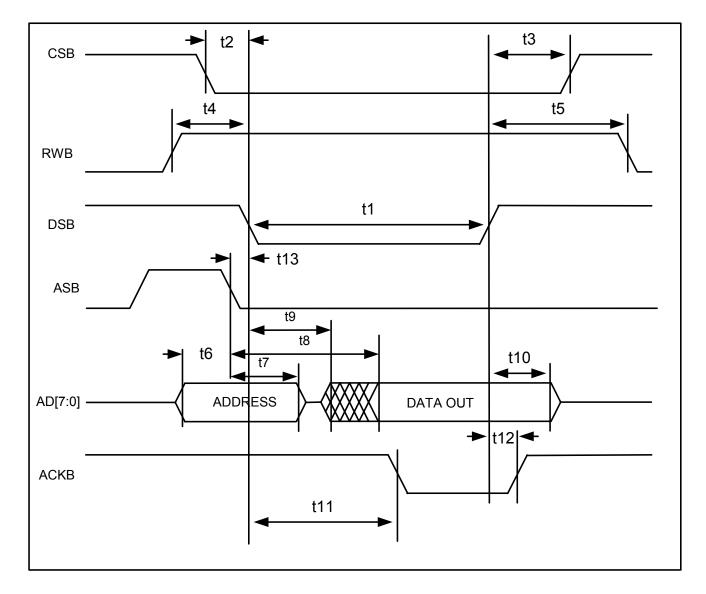

| Figure 10-6. Motorola Mux Read Cycle                            |    |

| Figure 10-7. Motorola Nonmux Write Cycle                        |    |

| Figure 10-8. Motorola Mux Write Cycle                           |    |

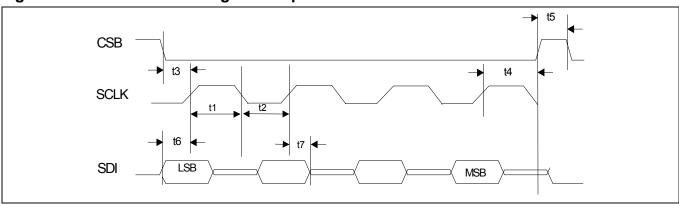

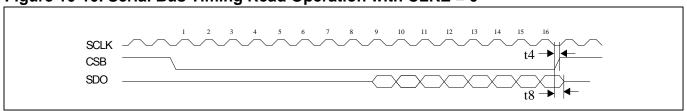

| Figure 10-9. Serial Bus Timing Write Operation                  |    |

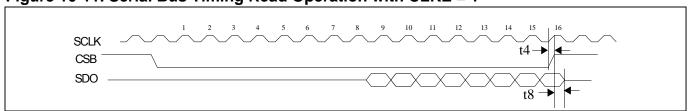

| Figure 10-10. Serial Bus Timing Read Operation with CLKE = 0    |    |

| Figure 10-11. Serial Bus Timing Read Operation with CLKE = 1    |    |

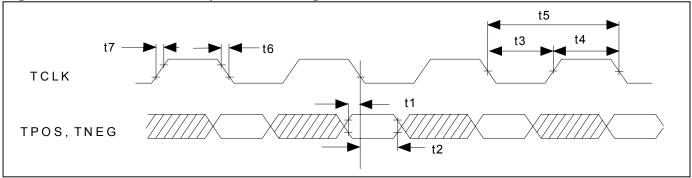

| Figure 10-12. Transmitter Systems Timing                        | 94 |

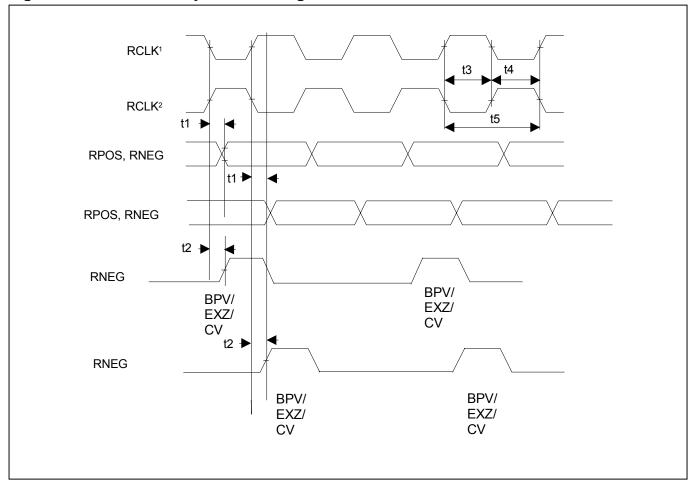

| Figure 10-13. Receiver Systems Timing                           | 95 |

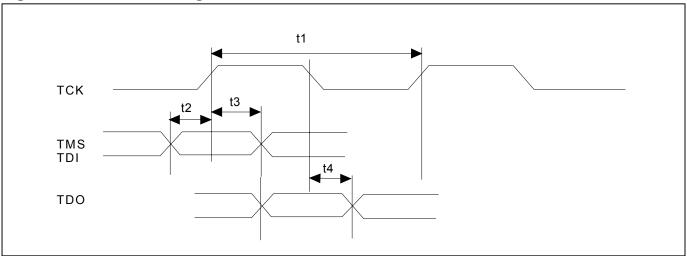

| Figure 10-14. JTAG Timing                                       | 96 |

# **LIST OF TABLES**

| Table 2-1. T1-Related Telecommunications Specifications                         | 7  |

|---------------------------------------------------------------------------------|----|

| Table 2-2. E1-Related Telecommunications Specifications                         | 8  |

| Table 4-1. Pin Descriptions                                                     |    |

| Table 4-2. Hardware Mode Configuration Examples                                 | 20 |

| Table 4-3. Parallel Port Mode Selection and Pin Functions                       | 22 |

| Table 5-1. Primary Register Set                                                 | 24 |

| Table 5-2. Secondary Register Set                                               | 25 |

| Table 5-3. Individual LIU Register Set                                          | 25 |

| Table 5-4. BERT Register Set                                                    |    |

| Table 5-5. Primary Register Set Bit Map                                         | 27 |

| Table 5-6. Secondary Register Set Bit Map                                       | 27 |

| Table 5-7. Individual LIU Register Set Bit Map                                  | 28 |

| Table 5-8. BERT Register Bit Map                                                | 28 |

| Table 5-9. G.772 Monitoring Control                                             | 32 |

| Table 5-10. TST Template Select Transceiver Register                            | 35 |

| Table 5-11. Template Selection                                                  | 35 |

| Table 5-12. Address Pointer for Bank Selection                                  | 37 |

| Table 5-13. MCLK Selections                                                     | 42 |

| Table 5-14. Jitter Attenuator Bandwidth Selections                              | 43 |

| Table 5-15. PLL Clock Select                                                    |    |

| Table 5-16. Clock A Select                                                      | 45 |

| Table 6-1. Telecommunications Specification Compliance for DS26303 Transmitters | 55 |

| Table 6-2. Registers Related to Control of DS26303 Transmitters                 | 55 |

| Table 6-3. DS26303 Template Selections                                          | 56 |

| Table 6-4. LIU Front-End Values                                                 |    |

| Table 6-5. Loss Criteria T1.231, G.775, and ETS 300 233 Specifications          | 60 |

| Table 6-6. AIS Criteria T1.231, G.775, and ETS 300 233 Specifications           |    |

| Table 6-7. AIS Detection and Reset Criteria                                     |    |

| Table 6-8. Registers Related to AIS Detection                                   | 61 |

| Table 6-9. BPV, Code Violation, and Excessive Zero Error Reporting              |    |

| Table 6-10. Pseudorandom Pattern Generation                                     |    |

| Table 6-11. Repetitive Pattern Generation                                       |    |

| Table 7-1. Instruction Codes for IEEE 1149.1 Architecture                       |    |

| Table 7-2. ID Code Structure                                                    |    |

| Table 7-3 Device ID Codes                                                       |    |

| Table 8-1. Recommended DC Operating Conditions                                  |    |

| Table 8-2. Capacitance                                                          |    |

| Table 8-3. DC Characteristics                                                   |    |

| Table 9-1. Thermal Characteristics                                              | 79 |

| Table 10-1. Transmitter Characteristics                                         |    |

| Table 10-2. Receiver Characteristics                                            |    |

| Table 10-3. Intel Read Mode Characteristics                                     |    |

| Table 10-4. Intel Write Cycle Characteristics                                   |    |

| Table 10-5. Motorola Read Cycle Characteristics                                 |    |

| Table 10-6. Motorola Write Cycle Characteristics                                |    |

| Table 10-7. Serial Port Timing Characteristics                                  |    |

| Table 10-8. Transmitter System Timing                                           |    |

| Table 10-9. Receiver System Timing                                              |    |

| Table 10-10. JTAG Timing Characteristics                                        | 96 |

## 1 DETAILED DESCRIPTION

The DS26303 is a single-chip, 8-channel, short-haul line interface unit (LIU) for T1 (1.544Mbps) and E1 (2.048Mbps) applications. Eight independent receivers and transmitters are provided in an eLQFP package. The LIUs can be individually selected for T1, J1, or E1 operation. The LIU requires a single reference clock called MCLK. MCLK can be either 1.544MHz or 2.048MHz or a multiple thereof, and either frequency can be internally adapted for T1, J1, or E1 mode. Internal impedance match provided for both transmit and receive paths reduces external component count. The transmit waveforms are compliant to G.703 and T1.102 specifications. The DS26303 provides software-selectable internal transmit termination for  $100\Omega$  T1 twisted pair,  $110\Omega$  J1 twisted pair,  $120\Omega$  E1 twisted pair, and  $75\Omega$  E1 coaxial applications. The transmitters have fast high-impedance capability and can be individually powered down.

The receivers can function with up to 15dB of receive signal attenuation for T1 mode and E1 mode. The DS26303 can be configured as a 7-channel LIU with channel 1 used for nonintrusive monitoring in accordance with G.772. The receivers and transmitters can be programmed into single-rail or dual-rail mode. AMI or HDB/B8ZS encoding and decoding is selectable in single-rail mode. A 128-bit crystal-less on-board jitter attenuator for each LIU can be placed in the receive or transmit directions. The jitter attenuator meets the ETS CTR12/13 ITU-T G.736, G.742, G.823, and AT&T Pub 62411 specifications.

The DS26303 detects and generates AIS in accordance with T1.231, G.775, and ETS 300 233. Loss of signal is detected in accordance with T1.231, G.775, and ETS 300 233. The DS26303 can perform digital, analog, remote, and dual loopbacks on individual LIUs. JTAG boundary scan is provided for the digital pins.

The DS26303 can be configured using an 8-bit multiplexed or nonmultiplexed Intel or Motorola port, a 4-pin serial port, or in limited modes of operation using hardware mode.

The analog AMI/HDB3 waveform of the E1 line or the AMI/B8ZS waveform of the T1 line is transformer coupled into the RTIP and RRING pins of the DS26303. The user has the option to select internal termination of  $75\Omega$ ,  $100\Omega$ , or  $120\Omega$  applications. The device recovers clock and data from the analog signal and passes it through a selectable jitter attenuator, outputting the received line clock at RCLK and data at RPOS and RNEG.

The DS26303 receivers can recover data and clock for up to 15dB of attenuation of the transmitted signals in T1 and E1 mode. Receiver 1 can monitor the performance of receivers 2 to 8 or transmitters 2 to 8.

The DS26303 contains eight identical transmitters. Digital transmit data is input at TPOS/TNEG with reference to TCLK. The data at these pins can be single-rail or dual-rail. This data is processed by waveshaping circuitry and line drivers to output a pulse at TTIP and TRING in accordance with ANSI T1.102 for T1/J1 or G.703 for E1 mask.

The DS26303 drives the E1 or T1 line from the TTIP and TRING pins through a coupling transformer. The DS26303 requires a 1:2 transformer for the transmit path and a 2:1 transformer for the receive path.

## 2 TELECOM SPECIFICATIONS COMPLIANCE

The DS26303 LIU meets all the relevant latest telecommunications specifications. <u>Table 2-1</u> provides the T1 specifications and <u>Table 2-2</u> provides the E1 specifications for the relevant sections applicable to the DS26303.

## Table 2-1. T1-Related Telecommunications Specifications

## ANSI T1.102-Digital Hierarchy Electrical Interface

**AMI** Coding

**B8ZS Substitution Definition**

DS1 Electrical Interface. Line rate ±32ppm; Pulse Amplitude between 2.4V to 3.6 V peak; Power level between 12.6dBm to 17.9dBm. The T1 pulse mask is provided that we comply. DSX-1 for cross connects the return loss is greater than 26dB. The DSX-1 cable is restricted up to 655 feet.

This specification also provides cable characteristics of DSX-Cross Connect cable—22 AVG cable of 1000 feet.

## ANSI T1.231-Digital Hierarchy-Layer 1 in Service Performance Monitoring

BPV Error Definition, Excessive Zero Definition, LOS description, AIS definition

### ANSI T1.403-Network and Customer Installation Interface-DS1 Electrical Interface

Description of the Measurement of the T1 Characteristics— $100\Omega$ , pulse shape and template according to T1.102; power level 12.4dBm to 19.7dBm when all ones are transmitted.

LBO for the Customer Interface (CI) is specified as 0dB, 7.5dB, and 15dB. Line rate is ±32ppm.

Pulse Amplitude is 2.4V to 3.6V.

AIS generation as unframed all ones is defined.

The total cable attenuation is defined as 22dB. The DS26303 functions up to 36dB cable loss.

Note that the pulse mask defined by T1.403 and T1.102 are different—specifically at Times 0.61, -0.27, -34, and 0.77. The DS26303 is compliant to both templates.

#### Pub 62411

This specification has tighter jitter tolerance and transfer characteristics than other specifications. The jitter transfer characteristics are tighter than G.736 and jitter tolerance is tighter the G.823.

# Table 2-2. E1-Related Telecommunications Specifications

### ITU-T G.703 Physical/Electrical Characteristics of G.703 Hierarchical Digital Interfaces

Defines the 2048kbps bit rate: 2048  $\pm 50$ ppm. The transmission media are  $75\Omega$  coax or  $120\Omega$  twisted pair; peak-to-peak space voltage is  $\pm 0.237$ V; nominal pulse width is 244ns.

Return loss: 51Hz to 102Hz is 6dB, 102Hz to 3072Hz is 8dB, 2048Hz to 3072Hz is 14dB

Nominal peak voltage is 2.37V for coax and 3V for twisted pair.

The pulse mask for E1 is defined in G.703.

Defines the 2048 kHz synchronization interface (Chapter 13). Contact factory for usage details.

## ITU-T G.736 Characteristics of Synchronous Digital Multiplex Equipment Operating at 2048kbps

The peak-to-peak jitter at 2048kbps must be less than 0.05UI at 20Hz to 100Hz.

Jitter transfer between 2.048 synchronization signal and 2.048 transmission signal is provided.

#### ITU-T G.742 Second-Order Digital Multiplex Equipment Operating at 8448kbps

The DS26303 jitter attenuator is compliant with jitter transfer curve for sinusoidal jitter input.

#### **ITU-T G.772**

This specification provides the method for using receiver for transceiver 0 as a monitor for the rest of the seven transmitter/receiver combinations.

#### **ITU-T G.775**

An LOS detection criterion is defined.

## ITU-T G.823-The control of jitter and wander within digital networks that are based on 2.048kbps Hierarchy

G.823 provides the jitter amplitude tolerance at different frequencies, specifically 20Hz, 2.4kHz, 18kHz, and 100kHz.

#### ETS 300 166

This specification provides transmit return loss of 6dB for a range of 0.25fb to 0.05fb, and 8dB for a range of 0.05fb to 1.5fb where fb equals 2.048kHz for 2.048kbps interface.

## ETS 300 233

This specification provides LOS and AIS signal criteria for E1 mode.

#### Pub 62411

This specification has tighter jitter tolerance and transfer characteristics than other specifications. The jitter transfer characteristics are tighter than G.736 and jitter tolerance is tighter than G.823.

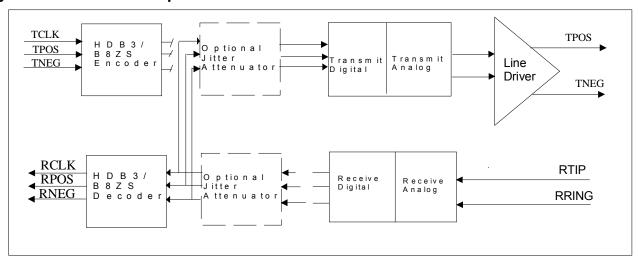

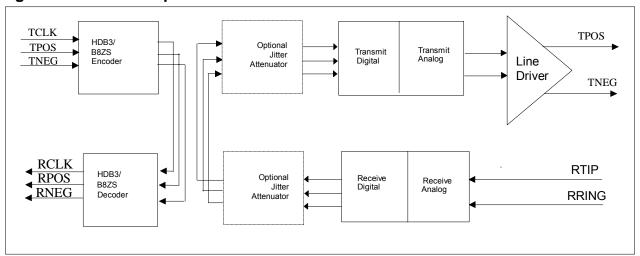

# 3 BLOCK DIAGRAMS

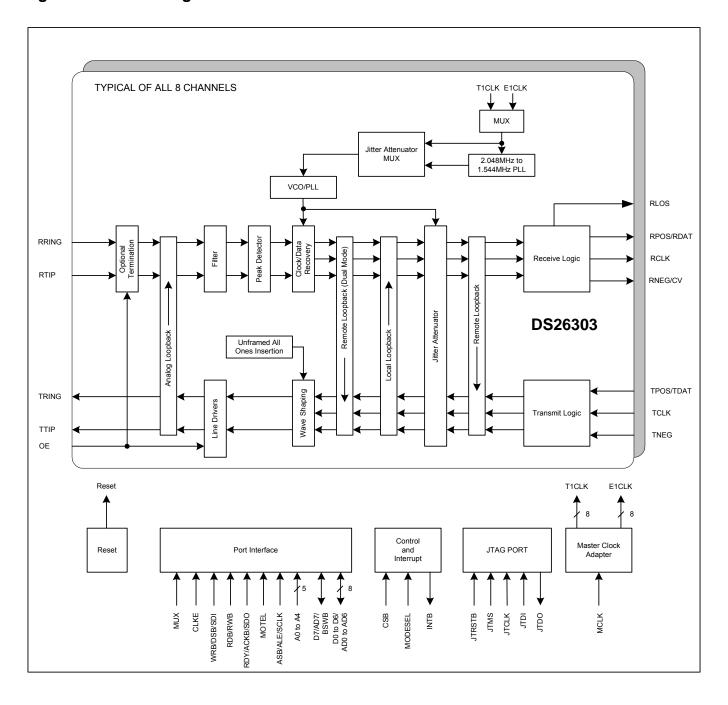

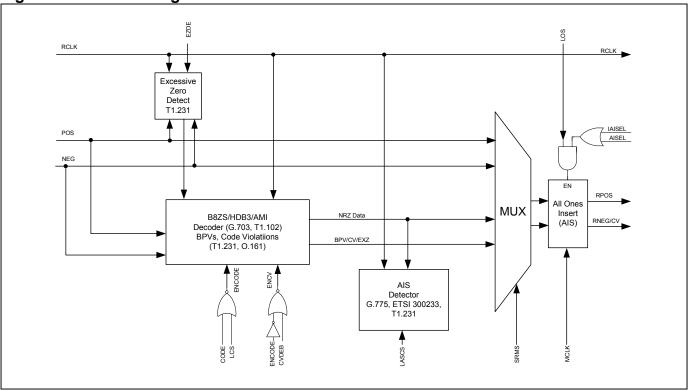

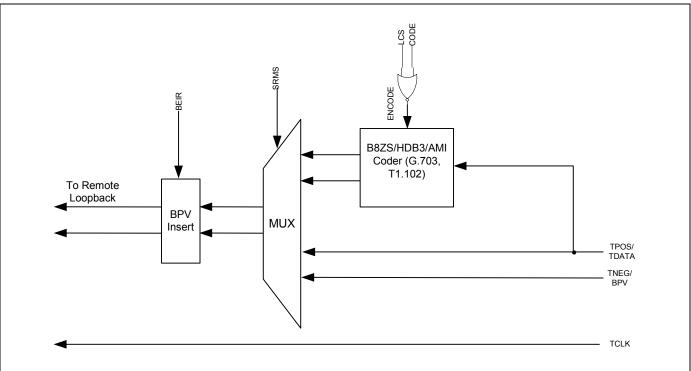

Figure 3-1. Block Diagram

Figure 3-2. Receive Logic Detail

Figure 3-3. Transmit Logic Detail

# 4 PIN DESCRIPTION

**Table 4-1. Pin Descriptions**

| NAME   | PIN                         | TYPE   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|--------|-----------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | ANALOG TRANSMIT AND RECEIVE |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TTIP1  | 45                          |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TTIP2  | 52                          |        | Transmit Bipolar Tip for Channel 1 to 8. These pins are                                                                                                                                                                                                                                                                                                                    |  |  |

| TTIP3  | 57                          |        | differential line-driver tip outputs. These pins will be high                                                                                                                                                                                                                                                                                                              |  |  |

| TTIP4  | 64                          | Analog | impedance if pin OE is low or the corresponding OEB.OEBn bit is                                                                                                                                                                                                                                                                                                            |  |  |

| TTIP5  | 117                         | Output | high. If the corresponding clock TCLK <i>n</i> is low for 64 MCLKs, the corresponding transmitter is put in power-down mode. The                                                                                                                                                                                                                                           |  |  |

| TTIP6  | 124                         | 1      | differential outputs of TTIP <i>n</i> and TRING <i>n</i> can provide internal                                                                                                                                                                                                                                                                                              |  |  |

| TTIP7  | 129                         |        | matched impedance for E1 75 $\Omega$ , E1 120 $\Omega$ , T1 100 $\Omega$ , or J1 110 $\Omega$ .                                                                                                                                                                                                                                                                            |  |  |

| TTIP8  | 136                         |        | materiod impodernoe for E1 7032, E1 12032, 11 10032, 01 01 11032.                                                                                                                                                                                                                                                                                                          |  |  |

| TRING1 | 46                          |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TRING2 | 51                          |        | Transmit Bipolar Ring for Channel 1 to 8. These pins are                                                                                                                                                                                                                                                                                                                   |  |  |

| TRING3 | 58                          |        | differential line-driver ring outputs. These pins will be high                                                                                                                                                                                                                                                                                                             |  |  |

| TRING4 | 63                          | Analog | impedance if pin OE is low or the corresponding $\underline{OEB}.OEBn$ bit is high. If the corresponding clock $TCLKn$ is low for 64 MCLKs, the corresponding transmitter is put in power-down mode. The differential outputs of $TTIPn$ and $TRINGn$ can provide internal matched impedance for $E1\ 75\Omega$ , $E1\ 120\Omega$ , $T1\ 100\Omega$ , or $J1\ 110\Omega$ . |  |  |

| TRING5 | 118                         | Output |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TRING6 | 123                         |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TRING7 | 130                         | 7      |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| TRING8 | 135                         |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RTIP1  | 48                          |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RTIP2  | 55                          |        | Beceive Bineles Tin fee Channel 4 to 9. Descive analog input for                                                                                                                                                                                                                                                                                                           |  |  |

| RTIP3  | 60                          |        | Receive Bipolar Tip for Channel 1 to 8. Receive analog input for differential receiver. Data and clock are recovered and output at                                                                                                                                                                                                                                         |  |  |

| RTIP4  | 67                          | Analog | RPOS <i>n</i> /RNEG <i>n</i> and RCLK <i>n</i> pins, respectively. The differential                                                                                                                                                                                                                                                                                        |  |  |

| RTIP5  | 120                         | Input  | inputs of RTIP <i>n</i> and RRING <i>n</i> can provide internal matched                                                                                                                                                                                                                                                                                                    |  |  |

| RTIP6  | 127                         |        | impedance for E1 75 $\Omega$ , E1 120 $\Omega$ , T1 100 $\Omega$ , or J1 110 $\Omega$ .                                                                                                                                                                                                                                                                                    |  |  |

| RTIP7  | 132                         |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RTIP8  | 139                         |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RRING1 | 49                          |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RRING2 | 54                          |        | Receive Bipolar Ring for Channel 1 to 8. Receive analog input                                                                                                                                                                                                                                                                                                              |  |  |

| RRING3 | 61                          | _      | for differential receiver. Data and clock are recovered and output                                                                                                                                                                                                                                                                                                         |  |  |

| RRING4 | 66                          | Analog | at RPOS $n$ /RNEG $n$ and RCLK $n$ pins, respectively. The differential                                                                                                                                                                                                                                                                                                    |  |  |

| RRING5 | 121                         | Input  | inputs of RTIP <i>n</i> and RRING <i>n</i> can provide internal matched                                                                                                                                                                                                                                                                                                    |  |  |

| RRING6 | 126                         |        | impedance for E1 75 $\Omega$ , E1 120 $\Omega$ , T1 100 $\Omega$ , or J1 110 $\Omega$ .                                                                                                                                                                                                                                                                                    |  |  |

| RRING7 | 133                         |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| RRING8 | 138                         |        |                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| NAME                         | PIN        | TYPE     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |            |          | DIGITAL Tx/Rx                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TPOS1/TDATA1                 | 37         |          | Transmit Positive-Data Input for Channel 1 to 8/Transmit Data Input for Channel 1 to 8                                                                                                                                                                                                                                                                                                                                                                |

| TPOS2/TDATA2                 | 30         |          | TPOS[1:8]: When the DS26303 is configured in dual-rail mode, the                                                                                                                                                                                                                                                                                                                                                                                      |

| TPOS3/TDATA3                 | 80         |          | data input to TPOS <i>n</i> is output as a positive pulse on the line (TTIP <i>n</i> and TRING <i>n</i> ) as follows:                                                                                                                                                                                                                                                                                                                                 |

| TPOS4/TDATA4                 | 73         |          | TPOSn TNEGn Output Pulse                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TPOS5/TDATA5                 | 108        |          | 0 0 Space<br>0 1 Negative Pulse                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TPOS6/TDATA6                 | 101        |          | 1 0 Positive Pulse<br>1 1 Space                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TPOS7/TDATA7                 | 8          |          | TDATA[1:8]: When the device is configured in single-rail mode,                                                                                                                                                                                                                                                                                                                                                                                        |

| TPOS8/TDATA8                 | 1          |          | NRZ data is input to TDATA <i>n</i> . The data is HDB3, B8ZS or AMI encoded before being output to the line.                                                                                                                                                                                                                                                                                                                                          |

| TNEG1                        | 38         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TNEG2                        | 31         |          | Transmit Negative Data for Channel 1 to 8. When the DS26303                                                                                                                                                                                                                                                                                                                                                                                           |

| TNEG3                        | 79         |          | is configured in dual-rail mode, the data input to TNEG <i>n</i> is output as a negative pulse on the line (TTIP <i>n</i> and TRING <i>n</i> ) as follows:                                                                                                                                                                                                                                                                                            |

| TNEG4                        | 72         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TNEG5                        | 109        | <u> </u> | TPOSn TNEGn Output Pulse 0 0 Space                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TNEG6                        | 102        | 1        | 0 1 Negative Pulse                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TNEG7                        | 7          |          | 1 0 Positive Pulse<br>1 1 Space                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TNEG8                        | 144        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCLK1                        | 36         |          | <b>Transmit Clock for Channel 1 to 8.</b> The transmit clock must be 1.544MHz for T1 or 2.048MHz for E1 mode. TCLK <i>n</i> is the clock                                                                                                                                                                                                                                                                                                              |

| TCLK2                        | 29         |          | used to sample the data on TPOS <i>n</i> /TNEG <i>n</i> or TDAT <i>n</i> on the falling edge. TCLK <i>n</i> can be inverted.  If TCLK <i>n</i> is high for 16 or more MCLKs, then an all-ones signal is transmitted on the corresponding line (TTIP <i>n</i> and TRING <i>n</i> ). When TCLK <i>n</i> starts clocking again, normal operation will resume on the corresponding line.  If TCLK <i>n</i> is low for 64 or more MCLKs, the corresponding |

| TCLK3                        | 81         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCLK4                        | 74         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCLK5                        | 107        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCLK6                        | 100        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCLK7                        | 9          |          | transmitter channel will power down and the line will be put into high impedance. When TCLK <i>n</i> starts clocking again the                                                                                                                                                                                                                                                                                                                        |

| TCLK8                        | 2          |          | corresponding transmitter will power up, resume normal operation, and the line will come out of high impedance.                                                                                                                                                                                                                                                                                                                                       |

| RPOS1/RDATA1                 | 40         |          | Receive Positive-Data Output for Channel 1 to 8/Receive Data                                                                                                                                                                                                                                                                                                                                                                                          |

| RPOS2/RDATA2                 | 33         |          | Output for Channel 1 to 8                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RPOS3/RDATA3                 | 77         | O,       | O, state  RPOS[1:8]: In dual-rail mode, this output indicates a positive pulse on RTIPn/RRINGn. If a given receiver is in power-down mode, the corresponding RPOSn pin is high impedance.  RDATA[1:8]: In single-rail mode, NRZ data is output to this pin.                                                                                                                                                                                           |

| RPOS4/RDATA4                 | 70         |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RPOS5/RDATA5<br>RPOS6/RDATA6 | 111<br>104 | แรงเสเซ  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RPOS6/RDATA6                 | 104        | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RPOS8/RDATA8                 | 142        | _        | <b>Note:</b> During an RLOS condition, the RPOSn/RDATAn output remainactive.                                                                                                                                                                                                                                                                                                                                                                          |

|                              | · ·=       |          | 10manaon vo.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NAME        | PIN | TYPE      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RNEG1/CV1   | 41  |           | Receive Negative-Data Output for Channel 1 to 8/Code Violation for Channel 1 to 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RNEG2/CV2   | 34  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RNEG3/CV3   | 76  |           | RNEG[1:8]: In dual-rail mode, this output indicates a negative pulse on RTIPn/RRINGn. If a given receiver is in power-down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RNEG4/CV4   | 69  | Ο,        | mode, the corresponding RNEG <i>n</i> pin is high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RNEG5/CV5   | 112 | tri-state | CV[1:8]: In single-rail mode, bipolar violation, code violation, and excessive zeros are reported by driving CVn high for one clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RNEG6/CV6   | 105 |           | cycle. If HDB3 or B8ZS encoding is not selected, this pin indicates only BPVs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RNEG7/CV7   | 4   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RNEG8/CV8   | 141 |           | <b>Note:</b> During an RLOS condition, the RNEGn/CVn output remains active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RCLK1       | 39  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RCLK2       | 32  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RCLK3       | 78  |           | Receive Clock for Channel 1 to 8. The receive data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RCLK4       | 71  | Ο,        | RPOS <i>n</i> /RNEG <i>n</i> or RDAT <i>n</i> is clocked out on the rising edge of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RCLK5       | 110 | tri-state | RCLKn. RCLKn can be inverted. If a given receiver is in power-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RCLK6       | 103 | 1         | down mode, RCLK <i>n</i> is high impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RCLK7       | 6   | 1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RCLK8       | 143 | 1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MCLK        | 10  | I         | Master Clock. This is an independent free-running clock that can be a multiple of 2.048MHz ±50ppm for E1 mode or 1.544MHz ±50ppm for T1 mode. The clock selection is available by MC bits MPS0, MPS1, FREQS, and PLLE. A multiple of 2.048MHz can be internally adapted to 1.544MHz and a multiple of 1.544MHz can be internally adapted to 2.048MHz. In hardware mode, internal adaptation is not available so the user must provide 2.048MHz ±50ppm for E1 mode or 1.544MHz ±50ppm for T1 mode.                                                                                                                                                                                          |

| RLOS1/TECLK | 42  | 0         | Loss-of-Signal Output/T1-E1 Clock  RLOS1: This output goes high when there are no transitions on the receiveline over a specified interval. The output goes low when there is sufficient ones density on the receiveline. The RLOS assertion and desertion criteria are described in the Functional Description section. The RLOS outputs can be configured to comply with T1.231, ITU-T G.775, or ETS 300 233. In hardware mode, ETS 300 233 "RLOS Criteria" is not available.  TECLK: When enabled (MC.TECLKE is set), this output becomes a T1- or E1-programmable clock output. For T1 or E1 frequency selection, see the CCR register. This option is not available in hardware mode. |

| RLOS2       | 35  |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RLOS3       | 75  |           | Loss-of-Signal Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RLOS4       | 68  | 0         | RLOS[2:8]: RLOS2: This output goes high when there are no transitions on the receiveline over a specified interval. The output goes low when there is sufficient ones density on the receiveline. The RLOS assertion and desertion criteria are described in the Functional Description (Section 6). The RLOS outputs can be configured to comply with T1.231, ITU-T G.775, or ETS 300 233. In hardware mode, ETS 300 233 "RLOS Criteria" is not available.                                                                                                                                                                                                                                |

| RLOS5       | 113 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RLOS6       | 106 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RLOS7       | 3   |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

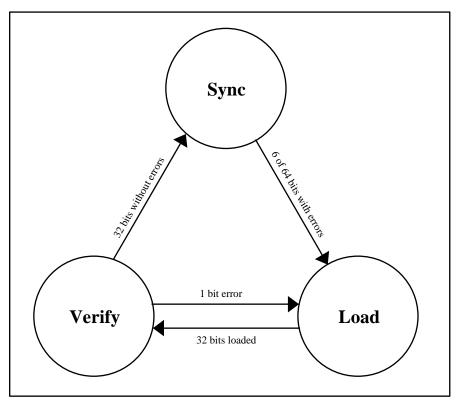

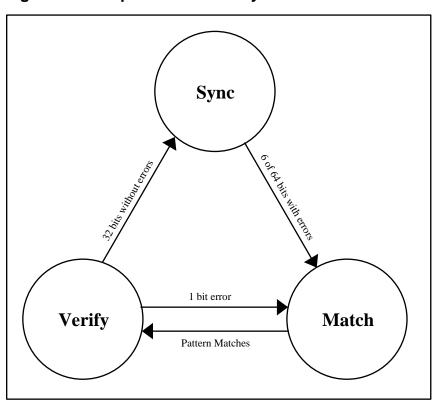

| RLOS8       | 140 |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |