# Design Idea DI-138

# LinkSwitch<sup>®</sup>TN

# **1.2 W, Non-isolated Dual Output Supply for White Goods**

| Application | Device   | Power Output | Input Voltage | Output Voltage | Topology     |

|-------------|----------|--------------|---------------|----------------|--------------|

| White Goods | LNK304DN | 1.2 W        | 85-265 VAC    | +7 V, -5 V     | Buck Derived |

#### **Design Highlights**

- Universal input

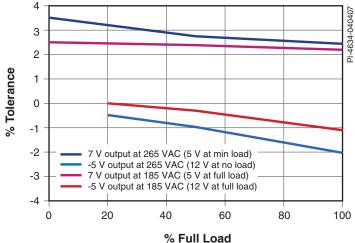

- Excellent regulation 12 V ±8% and 5 V ±5% (line, load, and tolerance)

- Temperature compensated

- Low stand-by input power consumption: <300 mW at 230 VAC with 50 mW output load

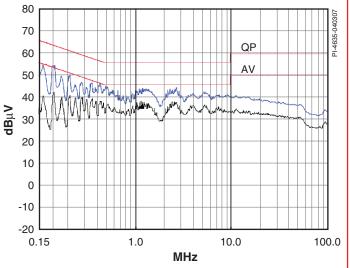

- Meets CISPR-22/EN55022B limits for conducted EMI with >10 dB margin

### Operation

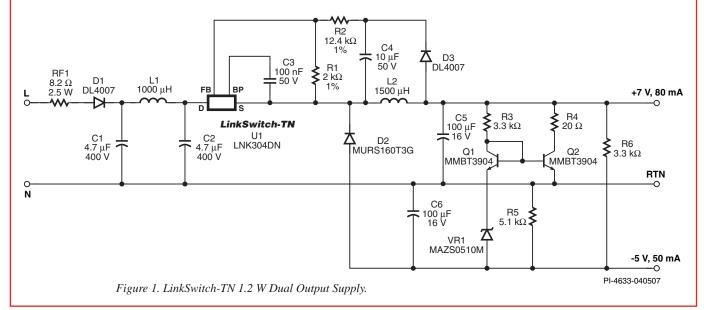

The circuit shown below provides two outputs, -5 V and +7 V. Referencing the load to the -5 V output creates a 5 V and 12 V output, the 5 V driving the control electronics and the 12 V output the mechanical relays.

This is ideal in applications where a negative gate drive is required for controlling a triac. As the triac gate is referenced to the RTN/N line when the control electronics are referenced to the -5 V output (V<sub>EE</sub>), the gate can be driven with a 0 V to -5 V signal (w.r.t. RTN/N).

Resistor RF1 is a fusible flame-proof type that acts as a fuse in the event of a catastrophic failure. Diode D1 provides AC input rectification while C1 and C2 provide smoothing and, together with L1, act as a  $\pi$  filter. This filtering, together with *LinkSwitch-TN*'s (U1) integrated switching frequency jitter, provides a generous EMI margin (see Figure 3).

During each enabled switching cycle, U1's internal MOSFET is enabled, causing a linear ramp in current through L2 and C5. Once the internal current limit is reached, the MOSFET turns off, and the inductor current can freewheel via D2, C5, and C6.

Regulation is maintained by adjusting the ratio of enabled to disabled cycles. A cycle is skipped once the current into the FEEDBACK (FB) pin exceeds 49  $\mu$ A. As this is specified at a voltage of 1.65 V, it allows this pin to can be used as a reference. With the values of R1 and R2 as shown, this sets the voltage across C5 plus C6 to 12 V.

The -5 V output is regulated by Q2 using VR1 as a reference. Zener VR1 is biased with a fixed current of approximately 2 mA, set by R3, to reduce the voltage variation of VR1 and therefore of the -5 V output over load changes. Resistor R4

#### **DI-138**

protects Q2 from short circuit conditions by limiting the collector current, while R5 maintains regulation even if the -5 V output is unloaded. Locating transistors Q1 and Q2 physically close to one another provides tracking of  $V_{\rm BE}$  drops, minimizing output voltage variation with temperature.

This arrangement works well in this application, where the load range is limited and the impact on efficiency of linear regulation is minimized.

## **Key Design Points**

- Diode D2 must be an ultra-fast type. The MURS160 selected has a t<sub>RR</sub> of 25 ns; a slower ultra-fast diode (≤50 ns) may be used, but efficiency may be reduced.

- A Zener with a low test current should be selected for VR1. The initial tolerance directly affects the output tolerance, a 2% part gives an overall variation including line and load regulation of ±5%.

- The temperature coefficient of VR1 is -0.8 mV/°C, giving a further ±0.4% variation over a temperature of 0 to 50 °C.

- R1 and R2 should be 1% parts for better accuracy of 12 V output.

- Pre-loads R5 and R6 are only necessary if regulation at no-load is required.

- For single 230 VAC applications, the value of C1 and C2 can be reduced to 2.2 μF, depending on differential surge

Figure 2. Worst Case Load and Line Regulation Results.

#### For the latest updates, visit www.powerint.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS. The products and applications illustrated herein (transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

The PI logo, TOPSwitch, TinySwitch, LinkSwitch, DPA-Switch, PeakSwitch, EcoSmart, Clampless, E-Shield, Filterfuse, StackFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2007, Power Integrations, Inc.

and EMI requirements. For single 100/115 VAC applications, the voltage of C1 and C2 can be reduced to 200 V.

- For correct operation of Q1, select the value of R5 to give 1 mA at no-load.

- Limit the maximum value of R4 such that a minimum V<sub>CE</sub> voltage of 1 V appears on Q2. This ensures that Q2 remains in linear operation when the 5 V output is at full load.

Figure 3. Conducted EMI Scan to EN55022B Limits Measured at 230 VAC Input.

Power Integrations 5245 Hellyer Avenue San Jose, CA 95138 Phone: 1-408-414-9200 Apps: 1-408-414-9660 Apps Fax: 1-408-414-9760

For a complete listing of worldwide sales offices, please visit www.powerint.com