# ACT-D1M96S High Speed 96 MegaBit 3.3V Synchronous DRAM Multichip Module

### **Features**

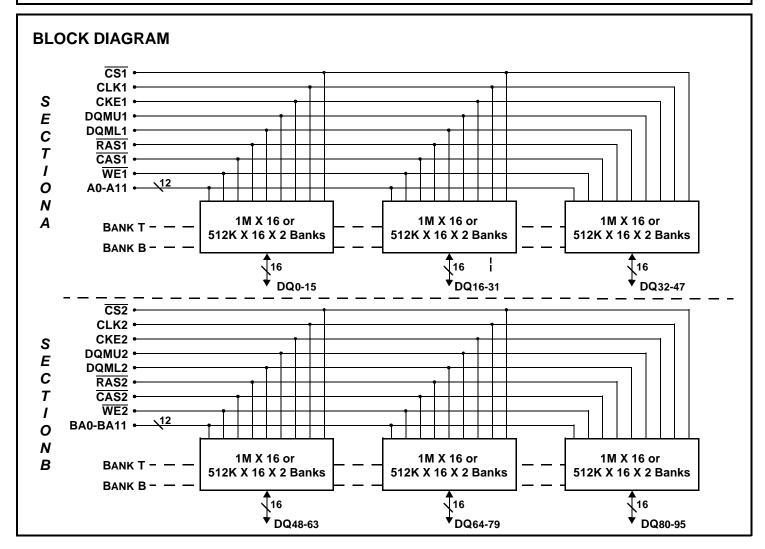

- 6 Low Power Micron 1M X 16 Synchronous Dynamic Random Access Memory Chips in one MCM

- User Configureable as "2" Independent 512K X 48 X 2 Banks

- High-Speed, Low-Noise, Low-Voltage TTL (LVTTL) Interface

- 3.3-V Power Supply (±10% Tolerance)

- Separate Logic and Output Driver Power Pins

- Two Banks for On-Chip Interleaving (Gapless Accesses)

- Up to 50-MHz Data Rates

- CAS Latency (CL) Programmable to 2 Cycles From Column-Address Entry

- Burst Length Programmable to 4 or 8

- **Pipeline Architecture**

- Cycle-by-Cycle DQ-Bus Write Mask Capability With Upper and Lower Byte Control

- Chip Select and Clock Enable for Enhanced-System Interfacing

- Serial Burst Sequence

- Auto-Refresh

- 4K Refresh (Total for Both Banks)

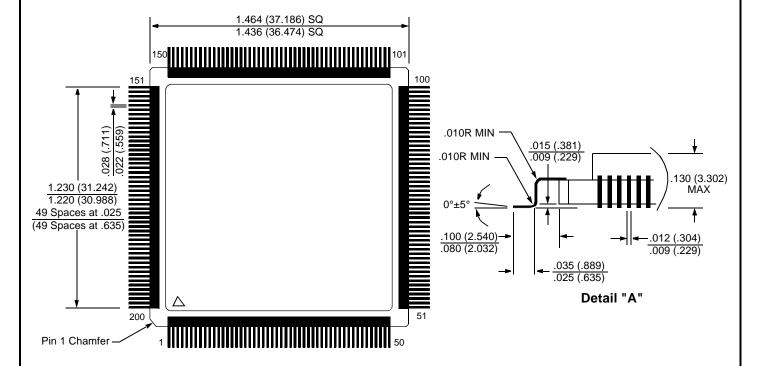

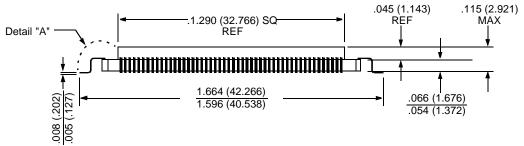

- 200-lead CQFP, cavity-up package

### **General Description**

The ACT-D1M96S device is a high-speed 96Mbit synchronous dynamic random access memory (SDRAM) organized as 2 independent 512K X 48 X 2 banks. All inputs and outputs of the ACT-D1M96S are compatible with the LVTTL interface. All inputs and outputs are synchronized with the CLK input to simplify system design and enhance use with high-speed microprocessors and caches.

### **Operation**

All inputs to the ACT-D1M96S SDRAM are latched on the rising edge of the system (synchronous) clock. The outputs, DQ0-DQ95, also are referenced to the rising edge of CLK. The ACT-D1M96S has two banks in each section that are accessed independently. A bank must be activated before it can be accessed (read from or written to). Refresh cycles refresh both banks alternately.

Five basic commands or functions control most operations of the ACT-D1M96S:

- Bank activate/row-address entry

- Column-address entry/write operation

- Column-address entry/read operation

- Bank deactivate

- Auto-refresh

Additionally, operations can be controlled by three methods:

- Chip select (CS) to select/ deselect the devices

- DQMx to enable/mask the DQ signals on a cycle-by-cycle basis

- CKE to suspend (or gate) the CLK input

The device contains a mode register that must be programmed for proper operation. Table 1 through Table 3 show the various operations that are available on the ACT-D1M96S. These truth tables identify the command and/or operations and their respective mnemonics. Each truth table is followed by a legend that explains the abbreviated symbols. An access operation refers to any read or write command in progress at cycle n. Access operations include the cycle upon which the read or write command is entered and all subsequent cycles through the completion of the access burst.

### **Burst Sequence**

All data for the ACT-D1M96S is written or read in a burst fashion, that is, a single starting address is entered into the device and then the ACT-D1M96S internally accesses a sequence of locations based on that starting address. After the first access some of the subsequent accesses can be at preceding as well as succeeding column addresses, depending on the starting address entered. This sequence is programmed to follow a serial burst (see Table 4 and 5). The length of the burst can be programmed is 4 or 8. After a read burst is

complete (as determined by the programmed-burst length), the outputs are in the high-impedance state until the next read access is initiated.

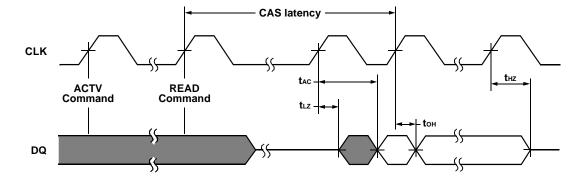

### Latency

The beginning data-out cycle of a read burst can be programmed to occur two CLK cycles after the read command. The delay between the READ command and the beginning of the output burst is known as CAS latency. After the initial output cycle begins, the data burst occurs at the CLK frequency without any intervening gaps.

There is no latency for data-in cycles (write latency). The first data-in cycle of a write burst is entered at the same rising edge of CLK on which the WRT command is entered. The write latency is fixed and is not determined by the mode-register contents.

### **Two-Bank Operation**

The ACT-D1M96S contains two independent banks that can be accessed individually or in an interleaved fashion. Each bank must be activated with a row address before it can be accessed. Each bank then must be deactivated before it can be activated again with a new row address. The bank-activate/row-address-entry command (ACTV) is entered by holding RAS low, CAS high, WE high, and A11 valid on the rising edge of CLK. A bank can be deactivated either automatically during a READ-P or a WRT-P command or by use of the deactivate-bank (DEAC) command. Both banks can be deactivated at once by use of the DCAB command (see Table 1 and the section on bank deactivation).

### Two-Bank Row-Access Operation

The two-bank feature allows access of information on random rows at a higher rate of operation than is possible with a standard DRAM, by activating one bank with a row address and, while the data stream is being accessed to/from that bank, activating the second bank with another row address. When the data stream to or from the first bank is complete, the data stream to or from the second bank can begin without interruption. After the second bank is activated, the first bank can be deactivated to allow the entry of a new row address for the next round of accesses. In this manner, operation can continue in an interleaved fashion.

### **Two-Bank Column-Access Operation**

The availability of two banks allows the access of data from random starting columns between banks at a higher rate of operation. After activating each bank with a row address (ACTV command), A11 can be used to alternate READ or WRT commands between the banks to provide gapless accesses at the CLK frequency, provided all specified timing requirements are met.

### **Bank Deactivation (Precharge)**

Both banks can be deactivated (placed in precharge) simultaneously by using the DCAB command. A single bank can be deactivated by using the DEAC command. The DEAC command is entered identically to the DCAB command except that A10 must be low and A11 used to select the bank to be precharged as shown in Table 1. A bank can be deactivated automatically by using A10 during a read or write command. If A10 is held high during the entry of a read or write command, the accessed bank (selected by A11) is deactivated automatically upon completion of the access burst. If A10 is held low during the entry of a read or write command, that bank remains active following the burst. The read and write commands with automatic deactivation are signified as READ-P and WRT-P.

### Chip Select (CS)

CS can be used to select or deselect the ACT-D1M96S for command entry, which might multiple-memory-device required for decoding. If  $\overline{\text{CS}}$  is held high on the rising edge of CLK (DESL command), the device does not respond to RAS, CAS, or WE until the device is selected again by holding  $\overline{CS}$  low on the rising edge of CLK. Any other valid command can be entered simultaneously on the same rising CLK edge of the select operation. The device can be selected/deselected on a cycle-by-cycle basis (see Table 1 and Table 2). The use of  $\overline{CS}$  does not affect an access burst that is in progress; the DESL command can only restrict RAS, CAS, and WE input to the ACT-D1M96S.

### Data Mask

The mask command or its opposite, the data-in enable (ENBL) command (see Table 3), is performed on a cycle-by-cycle basis to gate any data cycle within a write burst. DQML controls DQ0-7, DQ16-23, DQ32-39, DQ48-55, DQ64-71,

DQ80-87 and DQMU controls DQ8-15, DQ24-31, DQ40-47, DQ56-63, DQ72-79, and DQ88-95. The application of DQMx to a write burst has no latency (NDID = 0 cycle). During a write burst, if DQMx is held high on the rising edge of CLK, the data-input is ignored on that cycle.

### **CLK-Suspend**

For normal device operation, CKE should be held high to enable CLK. If CKE goes low during the execution of a READ (READ-P) or WRT (WRT-P) operation, the DQ bus occurring at the immediate next rising edge of CLK is frozen at its current state, and no further inputs are accepted until CKE returns high. This is known as a CLK-suspend operation, and its execution indicates a HOLD command. The device resumes operation from the point when it was placed in suspension, beginning with the second rising edge of CLK after CKE returns high.

### **Setting the Mode Register**

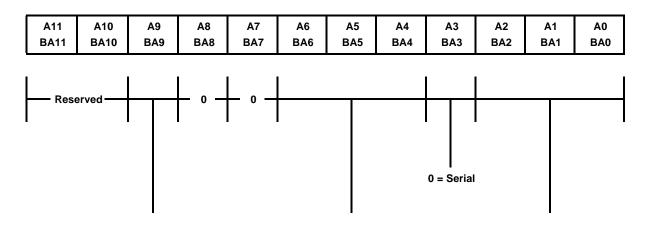

The ACT-D1M96S contains a mode register in each chip that must be programmed with the CAS latency, the burst type, and the burst length. accomplished This by executing mode-register set (MRS) command with the information entered on the address lines A0-A9. A logic 0 must be entered on A7 and A8, but A10 and A11 are don't-care entries for the ACT-D1M96S. When A9 = 0, the write-burst length is defined by A0-A2. Figure 1 shows the valid combinations for a successful MRS command. Only valid addresses allow the mode register to be changed. If the addresses are not valid, the previous contents of the mode register remain unaffected. The MRS command is executed by holding RAS, CAS, and WE low and the input mode word valid on A0-A9 on the rising edge of CLK (see Table 1). The MRS command can be executed only when both banks are deactivated.

### Refresh

The ACT-D1M96S must be refreshed at intervals not exceeding tref (see timing requirements) or data cannot be retained. Refresh can be accomplished by performing a read or write access to every row in both banks or 4096 auto-refresh (REFR) commands. Regardless of the method used, refresh must be accomplished before tref has expired.

### Auto Refresh (REFR)

Before performing a REFR, both banks of all 6 chips must be deactivated (placed in precharge). To enter a REFR command, RAS and CAS must be low and WE must be high upon the rising edge of CLK (see Table 1). The refresh address is generated internally such that, after 4096 REFR commands, both banks of all 6 chips of the ACT-D1M96S have been refreshed. The external address and bank select (A11) are ignored. The execution of a REFR command automatically deactivates both banks upon completion of the internal auto-refresh cycle, allowing consecutive REFR-only commands to be executed, if desired, without any intervening DEAC commands. The REFR commands do not necessarily have to be consecutive, but all 4096 must be completed before tree expires.

### **Power Up Initialization**

Device initialization should be performed after a power up to the full Vcc level. After power is established, a 200µs interval is required (with no inputs other than CLK). After this interval, both banks of the device must be deactivated. Eight REFR commands must be performed, and the mode register must be set to complete the device initialization.

### **General Information for AC Timing Measurements**

All specifications referring to READ commands are also valid for READ-P commands unless otherwise noted. All specifications referring to WRT commands are also valid for WRT-P commands unless otherwise noted. All specifications referring to consecutive commands are specified as consecutive commands for the same bank unless otherwise noted.

Note: For all pin references in the General Description, both sections apply. For example, A11 signals also apply for BA11 signals.

For additional Detail Information regarding the operation of the individual chip (MT48LC1M16A1) see Micron's 524,288-WORD BY 16-BIT BY 2-BANK SYNCHRONOUS DYNAMIC RANDOM-ACCESS MEMORY Datasheet Revision 8/99 or contact the Aeroflex Sales Department.

| Register<br>Bit A9/<br>BA9 | Write Burst<br>Length |

|----------------------------|-----------------------|

| 0                          | A2 - A0<br>BA2 - BA0  |

| Reg       | gister B  | its <sup>†</sup> |             |  |  |

|-----------|-----------|------------------|-------------|--|--|

| A6<br>BA6 | A5<br>BA5 | A4<br>BA4        | CAS Latency |  |  |

| 0         | 1         | 0                | 2           |  |  |

| Reg       | gister B  | its <sup>†</sup> |              |

|-----------|-----------|------------------|--------------|

| A2<br>BA2 | A1<br>BA1 | A0<br>BA0        | Burst Length |

| 0         | 1         | 0<br>1           | 4<br>8       |

**NOTES**: † All other combinations are reserved.

Figure 1 - Mode Register Programming

### **AC Test Conditions**

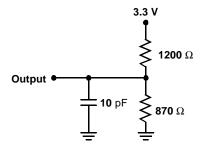

| Parameter                         | Typical   | Units |

|-----------------------------------|-----------|-------|

| Input Pulse Level                 | 0.4 - 2.4 | ٧     |

| Input Rise and Fall               | 5         | ns    |

| Input and Output Timing Reference | 1.5       | ٧     |

Figure 2 - LVTTL-Load Circuit

Table 1 — Basic Command Truth Table †

| Command <sup>‡</sup>                                      | State of Bank(s)     | CS1<br>CS2 | RAS1<br>RAS2 | CAS1<br>CAS2 | WE1<br>WE2 | A11<br>BA11 | A10<br>BA10 | A9-A0<br>BA9-BA0                                     | Mne-<br>monic |

|-----------------------------------------------------------|----------------------|------------|--------------|--------------|------------|-------------|-------------|------------------------------------------------------|---------------|

| Mode register set                                         | T = deac<br>B = deac | L          | L            | L            | L          | х           | x           | A9,BA9 = V<br>A8,BA8,A7,BA7 = 0<br>A6-A0,BA6-BA0 = V | MRS           |

| Bank deactivate (precharge)                               | Х                    | L          | L            | Н            | L          | BS          | L           | х                                                    | DEAC          |

| Deactivate all banks (precharge)                          | Х                    | L          | L            | Н            | L          | Х           | Н           | X                                                    | DCAB          |

| Bank activate/row-address entry                           | SB = deac            | L          | L            | Н            | Н          | BS          | ٧           | V                                                    | ACTV          |

| Column-address entry/write operation                      | SB = actv            | L          | н            | L            | L          | BS          | L           | V                                                    | WRT           |

| Column-address entry/write operation with auto-deactivate | SB = actv            | L          | Н            | L            | L          | BS          | Н           | V                                                    | WRT-P         |

| Column-address entry/read operation                       | SB = actv            | L          | н            | L            | н          | BS          | L           | V                                                    | READ          |

| Column-address entry/read operation with auto-deactivate  | SB = actv            | L          | Н            | L            | Н          | BS          | Н           | V                                                    | READ-P        |

| Burst stop                                                | SB = actv            | L          | Н            | Н            | L          | Х           | Х           | х                                                    | STOP          |

| No operation                                              | Х                    | L          | Н            | Н            | Н          | Х           | Х           | X                                                    | NOOP          |

| Control-input inhibit/no operation                        | Х                    | Н          | Х            | Х            | Х          | Х           | Х           | X                                                    | DESL          |

| Auto refresh <sup>§</sup>                                 | T = deac<br>B = deac | L          | L            | L            | Н          | х           | х           | х                                                    | REFR          |

### NOTES:

- † For execution of these commands on cycle n:

- -CKE (n-1) must be high, or

- -tCES and nCLE must be satisfied for clock-suspend exit.

- DQMx(n) is a don't care.

- ‡ All other unlisted commands are considered vendor-reserved commands or illegal commands.

- § Auto-refresh entry requires that all banks be deactivated or in an idle state prior to the command entry.

- Legend:

- n = CLK cycle number, L = Logic low, H = Logic high, X = Don't care, either logic low or logic high, V = Valid, T = Bank T, B = Bank B, actv = Activated, deac = Deactivated, BS = Logic high to select bank T; logic low to select bank B, SB = Bank selected by A11 at cycle n

### Table 2 — Clock Enable (CKE) Command Truth Table †

| Command <sup>‡</sup>              | State of Bank(s)                            | CKE<br>(n-1) | CKE<br>(n) | CS<br>(n) | RAS<br>(n) | CAS<br>(n) | WE<br>(n) | Mnemonic |

|-----------------------------------|---------------------------------------------|--------------|------------|-----------|------------|------------|-----------|----------|

| CLK suspend on cycle (n + 1)      | T = access operation¶ B = access operation¶ | н            | L          | х         | х          | х          | х         | HOLD     |

| CLK suspend exit on cycle (n + 1) | T = access operation¶ B = access operation¶ | L            | н          | Х         | Х          | х          | х         | _        |

### NOTES:

- † For execution of these commands, A0-A11 (n) and DQMx (n) are don't cares. ‡ All other unlisted commands are considered vendor-reserved commands or illegal commands.

- A bank is no longer in an access operation one cycle after the last data-out cycle of a read operation, and two cycles after the last data-in cycle of a write operation. Neither the PDE nor the HOLD command is allowed on the cycle immediately following the last data-in cycle of a write operation.

- Legend:

n = CLK cycle number, L = Logic low, H = Logic high, X = Don't care, either logic low or logic high, T = Bank T, B = Bank B

Table 3 — Data-Mask (DQM) Command Truth Table †

| Command <sup>‡</sup> | State of Bank(s)                             | DQML<br>DQMU <sup>S</sup><br>(n) | Data In (n) | Data Out<br>(n+2) | Mnemonic |

|----------------------|----------------------------------------------|----------------------------------|-------------|-------------------|----------|

| _                    | T = deac and<br>B = deac                     | х                                | N/A         | Hi-Z              | _        |

| _                    | T = actv and B = actv (no access operation)¶ | х                                | N/A         | Hi-Z              | -        |

| Data-in enable       | T = Write or<br>B = Write                    | L                                | V           | N/A               | ENBL     |

| Data-in mask         | T = Write or<br>B = Write                    | н                                | М           | N/A               | MASK     |

| Data-out enable      | T = Write or<br>B = Write                    | L                                | N/A         | V                 | ENBL     |

- † For execution of these commands on cycle n:

- CKE (n) must be high, or

- -t CES and n CLE must be satisfied for clock suspend exit.

- CS(n), RAS(n), WE(n), and A0-A11 are don't cares.

‡ All other unlisted commands are considered vendor-reserved commands or illegal commands.

§ DQML controlsDQ0-7, DQ16-23, DQ32-39, DQ48-55, DQ64-71, DQ80-87 and DQMU controls DQ8-15, DQ24-31, DQ40-47, DQ56-63, DQ72-79, and DQ88-95.

- A bank is no longer in an access operation one cycle after the last data-out cycle of a read operation, and two cycles after the last data-in cycle of a write operation. Neither the PDE nor the HOLD command is allowed on the cycle immediately following the last data-in cycle of a write operation. Legend:

- n = CLK cycle number, L = Logic low, H = Logic high, X = Don't care, either logic low or logic high, V = Valid, M = Masked input data, N/A = Not applicable,

- T = Bank T, B = Bank B, actv = Activated, deac = Deactivated, write = Activated and accepting data inputs on cycle n, read = Activated and delivering data outputs on cycle (n + 2)

Table 4 — Serial 4-Word Burst Sequences

|       | INTERNAL COLUMN ADDRESS A1-A0, BA1-BA0 |      |     |       |     |     |     |

|-------|----------------------------------------|------|-----|-------|-----|-----|-----|

|       | DEC                                    | IMAL |     |       | BIN | ARY |     |

| START | 2ND                                    | 3RD  | 4TH | START | 2ND | 3RD | 4TH |

| 0     | 1                                      | 2    | 3   | 00    | 01  | 10  | 11  |

| 1     | 2                                      | 3    | 0   | 01    | 10  | 11  | 00  |

| 2     | 3                                      | 0    | 1   | 10    | 11  | 00  | 01  |

| 3     | 0                                      | 1    | 2   | 11    | 00  | 01  | 10  |

Table 5 - Serial 8-Word Burst Sequences

|       | INTERNAL COLUMN ADDRESS A2-A0, BA2-BA0 |     |     |      |     |     |     |       |     |     |     |     |     |     |     |

|-------|----------------------------------------|-----|-----|------|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|

|       |                                        |     | DEC | IMAL |     |     |     |       |     |     | BIN | ARY |     |     |     |

| START | 2ND                                    | 3RD | 4TH | 5TH  | 6TH | 7TH | 8TH | START | 2ND | 3RD | 4TH | 5TH | 6TH | 7TH | 8TH |

| 0     | 1                                      | 2   | 3   | 4    | 5   | 6   | 7   | 000   | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| 1     | 2                                      | 3   | 4   | 5    | 6   | 7   | 0   | 001   | 010 | 011 | 100 | 101 | 110 | 111 | 000 |

| 2     | 3                                      | 4   | 5   | 6    | 7   | 0   | 1   | 010   | 011 | 100 | 101 | 110 | 111 | 000 | 001 |

| 3     | 4                                      | 5   | 6   | 7    | 0   | 1   | 2   | 011   | 100 | 101 | 110 | 111 | 000 | 001 | 010 |

| 4     | 5                                      | 6   | 7   | 0    | 1   | 2   | 3   | 100   | 101 | 110 | 111 | 000 | 001 | 010 | 011 |

| 5     | 6                                      | 7   | 0   | 1    | 2   | 3   | 4   | 101   | 110 | 111 | 000 | 001 | 010 | 011 | 100 |

| 6     | 7                                      | 0   | 1   | 2    | 3   | 4   | 5   | 110   | 111 | 000 | 001 | 010 | 011 | 100 | 101 |

| 7     | 0                                      | 1   | 2   | 3    | 4   | 5   | 6   | 111   | 000 | 001 | 010 | 011 | 100 | 101 | 110 |

### Absolute Maximum Ratings<sup>1</sup>

| Symbol             | Rating                                                   | Range       | Units |

|--------------------|----------------------------------------------------------|-------------|-------|

| V <sub>CC</sub>    | Supply Voltage                                           | -0.5 to 4.6 | V     |

| $V_{CCQ}$          | Supply Voltage range for output drivers                  | -0.5 to 4.6 | V     |

| $V_{RANGE}$        | Voltage range on any pin with respect to V <sub>SS</sub> | -0.5 to 4.6 | V     |

| T <sub>BIAS</sub>  | Case Temperature under Bias <sup>2</sup>                 | -55 to +125 | °C    |

| $T_{STG}$          | Storage Temperature                                      | -65 to +150 | °C    |

| I <sub>SHORT</sub> | Short-Circuit Output Current                             | 50          | mA    |

| PW                 | Power Dissipation                                        | 4.2         | W     |

<sup>1.</sup> Stresses above those listed under "Absolute Maximums Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

| Symbol           | Parameter                                 | Minimum | Typical | Maximum        | Units |

|------------------|-------------------------------------------|---------|---------|----------------|-------|

| V <sub>CC</sub>  | Supply Voltage                            | 3       | 3.3     | 3.6            | V     |

| V <sub>CCQ</sub> | Supply Voltage range for output drivers   | 3       | 3.3     | 3.6            | V     |

| V <sub>SS</sub>  | Supply Voltage                            |         | 0       |                | V     |

| $V_{SSQ}$        | Supply Voltage range for output drivers   |         | 0       |                | V     |

| $V_{IH}$         | Input High Voltage                        | 2       |         | $V_{CC} + 0.3$ | V     |

| $V_{IL}$         | Input Low Voltage <sup>1</sup>            | -0.3    |         | 0.8            | V     |

| T <sub>C</sub>   | Operating Temperature (Case) <sup>2</sup> | -55     |         | +110           | °C    |

<sup>1.</sup> VIL Minimum = 1.5Vac (Pulsewidth ≤ 5ns)

### **DC Characteristics**

$(VCC = 3.3V \pm 10\%; Tc = -55^{\circ}C \text{ to } +110^{\circ}C, See Notes 1 \& 5)$

| Parameter                      | Symbol          | Conditions                                                     | Min | Max | Units |

|--------------------------------|-----------------|----------------------------------------------------------------|-----|-----|-------|

| Output Low Voltage             | V <sub>OL</sub> | I <sub>OL</sub> = 2mA                                          |     | 0.4 | V     |

| Output High Voltage            | $V_{OH}$        | $I_{OH} = -2mA$                                                | 2.4 |     | V     |

| Input current (Leakage)        | I <sub>I</sub>  | $0V \le VI \le VCC + 0.3V$ , All other pins = $0V$ to $VCC$    | -10 | +10 | μΑ    |

| Output current (Leakage)       | I <sub>O</sub>  | $0V \le VO \le VCC + 0.3V$ , Output disabled                   | -10 | +10 | μΑ    |

| Precharge standby              | Icc2n           | CKE ≥ VIH MIN, tcκ = 20ns (See note 2)                         |     | 180 | mA    |

| current in non-power-down mode | Icc2ns          | CKE $\geq$ VIH MIN, CLK < VIL MAX, tcK = $\infty$ (See note 3) |     | 40  | mA    |

<sup>1.</sup> All specifications apply to the device after power- up initialization. All control and address inputs must be stable and valid.

<sup>2.</sup> The temperature rise of  $\theta_{\text{ic}}$  is negligible due to the low duty cycle during testing.

<sup>2.</sup> The temperature rise of  $\theta_{\text{jc}}$  is negligible due to the low duty cycle during testing.

<sup>2.</sup> Control, DQ, and address inputs change state only once every 40 ns.

<sup>3.</sup> Control, DQ, and address inputs do not change (stable).

<sup>4.</sup> All Icc parameters measured with Vcc, not Vccq.

<sup>5.</sup> The temperature rise of  $\theta_{\text{jc}}$  is negligible due to the low duty cycle during testing.

## Capacitance<sup>†</sup> (f = 1MHz, Tc = 25°C)

| Symbol | Parameter                                                                                                                                                        | Min | Max | Units |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| Ci(S)  | Input Capacitance, CLK Input                                                                                                                                     |     | 50  | pF    |

| Ci(AC) | Input Capacitance, Address and Control Inputs: A0-A11, $\overline{\text{CS}}$ , DQMx, $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ |     | 40  | pF    |

| Ci(E)  | Input Capacitance, CKE Input                                                                                                                                     |     | 50  | pF    |

| Co     | Output Capacitance                                                                                                                                               |     | 20  | pF    |

<sup>†</sup>Parameters Guaranteed but not tested

AC Timing<sup>†‡</sup> (Vcc = 3.3V  $\pm 0.3$ V, Tc = -55°C to +110°C, See Note 4)

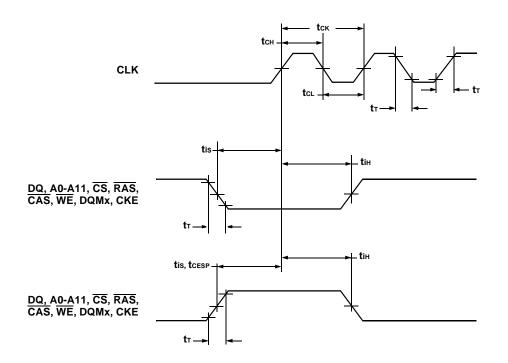

| Parameter                                                                   | Symbol | Test Conditions | Min                              | Max    | Units |

|-----------------------------------------------------------------------------|--------|-----------------|----------------------------------|--------|-------|

| Cycle time, CLK                                                             | tCK2   | CAS latency = 2 | 20                               |        | ns    |

| Pulse duration, CLK high                                                    | tCH    |                 | 6                                |        | ns    |

| Pulse duration, CLK low                                                     | tCL    |                 | 6                                |        | ns    |

| Access time, CLK high to data out (see Note 1)                              | tAC2   | CAS latency = 2 |                                  | 13     | ns    |

| Hold time, CLK high to data out                                             | tОН    |                 | 1                                |        | ns    |

| Setup time, address, control, and data input                                | tıs    |                 | 5                                |        | ns    |

| Hold time, address, control, and data input                                 | tıH    |                 | 3                                |        | ns    |

| Delay time, ACTV command to DEAC or DCAB command                            | tRAS   |                 | 72                               | 100000 | ns    |

| Delay time, ACTV or REFR to ACTV, MRS or REFR command                       | tRC    |                 | 108                              |        | ns    |

| Delay time ACTV command to READ, READ-P, WRT, or WRT-P command (see Note 2) | tRCD   |                 | 30                               |        | ns    |

| Delay time, DEAC or DCAB command to ACTV, MRS or REFR command               | tRP    |                 | 36                               |        | ns    |

| Delay time, ACTV command in one bank to ACTV command in the other bank      | tRRD   |                 | 24                               |        | ns    |

| Delay time, MRS command to ACTV, MRS or REFR command                        | tRSA   |                 | 30                               |        | ns    |

| Final data out of READ-P operation to ACTV, MRS or REFR command             | tapr   |                 | Min<br>t RP - (CL -1<br>(see Not | •      | ns    |

| Final data in of WRT-P operation to ACTV, MRS or REFR command               | tapw   |                 | 60                               |        | ns    |

### AC Timing<sup>†‡</sup> (cont.)

$(Vcc = 3.3V \pm 0.3V, Tc = -55^{\circ}C \text{ to } +110^{\circ}C, See Note 4)$

| Parameter                                                                 | Symbol       | Test Conditions | Min | Max | Units |

|---------------------------------------------------------------------------|--------------|-----------------|-----|-----|-------|

| Delay time, final data in of WRT operation to DEAC or DCAB command        | twr          |                 | 20  |     | ns    |

| Refresh interval                                                          | tREF         |                 |     | 50  | ms    |

| Delay time, CS low or high to input enabled or inhibited                  | <b>n</b> cdd |                 | 0   | 0   | cycle |

| Delay time, CKE high or low to CLK enabled or disabled                    | <b>n</b> cle |                 | 1   | 1   | cycle |

| Delay time, final data in of WRT operation to READ, READ-P, WRT, or WRT-P | <b>n</b> cwl |                 | 1   |     | cycle |

| Delay time, ENBL or MASK command to enabled or masked data in             | <b>n</b> did |                 | 0   | 0   | cycle |

| Delay time, ENBL or MASK command to enabled or masked data out            | ndod         |                 | 2   | 2   | cycle |

| Delay time, DEAC or DCAB, command to DQ in high-impedance state           | NHZP2        | CAS latency = 2 |     | 2   | cycle |

| Delay time, WRT command to first data in                                  | nwcd         |                 | 0   | 0   | cycle |

| Delay time, STOP command to READ or WRT command                           | nbsd         |                 |     | 2   | cycle |

<sup>†</sup> See Figure 2 - LVTTL Load Circuit for load circuits. ‡ All references are made to the rising transition of CLK, unless otherwise noted. NOTES:

<sup>1.</sup> Tac is referenced from the rising transition of CLK that is previous to the data-out cycle. For example, the first data out tac is referenced from the rising transition of CLK within the following cycle: CAS latency minus one cycle after the READ command. An access time is measured at output reference level 1.5 V.

<sup>2.</sup> For read or write operations with automatic deactivate, tRCD must be set to satisfy minimum tRAS .

<sup>3.</sup> CL = CAS Latency. 4. The temperature rise of  $\theta_{jc}$  is negligible due to the low duty cycle during testing.

Figure 3 - Input-Attribute Parameters

Figure 4 - Output Parameters

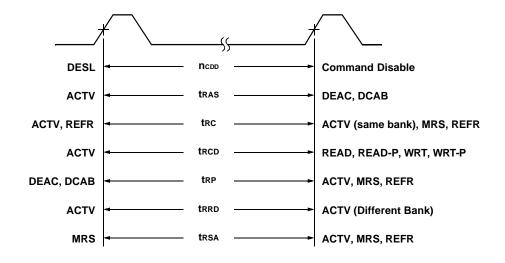

Figure 5 - Command-to-Command Parameters

### Package Information – "F20" – CQFP 200 Leads

Note: 1. All Dimensions in inches (Millimeters)  $\frac{\text{MAX}}{\text{MIN}}$  or Typical where noted.

### **Pin Nomenclature**

| A0-A10<br>BA0-BA10 | Address Inputs<br>A0-A10, BA0-BA10 Row Addresses<br>A0-A7, BA0-BA7 Column Addresses<br>A10, BA10 Automatic-Precharge Select | DQML1,2<br>DQMU1,2 | Data/Input Mask Enables         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------|

| A11,BA11           | Bank Select                                                                                                                 | RAS1,RAS2          | Row-Address Strobe              |

| CAS1,CAS2          | Column-Address Strobe                                                                                                       | vcc                | Power Supply                    |

| CKE1,CKE2          | Clock Enable                                                                                                                | VCCQ               | Power Supply for Output Drivers |

| CLK1,CLK2          | System Clock                                                                                                                | vss                | Ground                          |

| CS1,CS2            | Chip Select                                                                                                                 | VSSQ               | Ground for Output Drivers       |

| DQ0-DQ95           | SDRAM Data Input/Output                                                                                                     | WE1,WE2            | Write Enable                    |

### ACT-D1M96S CQFP Pinouts - "F20"

| PIN<br># | FUNCTION |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 1        | DQ2      | 41       | DQ91     | 81       | DQ67     | 121      | VSSQ     | 161      | DQ30     |

| 2        | DQ3      | 42       | VSSQ     | 82       | DQ66     | 122      | BA1      | 162      | VSSQ     |

| 3        | VSSQ     | 43       | DQ92     | 83       | VSS      | 123      | BA2      | 163      | DQ29     |

| 4        | DQ4      | 44       | DQ93     | 84       | DQ65     | 124      | VCCQ     | 164      | DQ28     |

| 5        | DQ5      | 45       | VCCQ     | 85       | DQ64     | 125      | BA3      | 165      | VCC      |

| 6        | VCCQ     | 46       | DQ94     | 86       | VCC      | 126      | A4       | 166      | DQ27     |

| 7        | DQ6      | 47       | DQ95     | 87       | DQ63     | 127      | VCCQ     | 167      | DQ26     |

| 8        | DQ7      | 48       | VSSQ     | 88       | DQ62     | 128      | A5       | 168      | VSS      |

| 9        | VSSQ     | 49       | DQ87     | 89       | VSSQ     | 129      | A6       | 169      | DQ25     |

| 10       | DQML1    | 50       | DQ86     | 90       | DQ61     | 130      | VSSQ     | 170      | DQ24     |

| 11       | WE1      | 51       | DQ85     | 91       | DQ60     | 131      | A7       | 171      | VSSQ     |

| 12       | VSSQ     | 52       | DQ84     | 92       | VSSQ     | 132      | A8       | 172      | CLK1     |

| 13       | CAS1     | 53       | VSSQ     | 93       | DQ59     | 133      | VSS      | 173      | CKE1     |

| 14       | RAS1     | 54       | DQ83     | 94       | DQ58     | 134      | A9       | 174      | VCCQ     |

| 15       | VCC      | 55       | DQ82     | 95       | VCCQ     | 135      | DQMU1    | 175      | DQ23     |

| 16       | CS1      | 56       | VCCQ     | 96       | DQ57     | 136      | VCC      | 176      | DQ22     |

| 17       | A11      | 57       | DQ81     | 97       | DQ56     | 137      | DQ40     | 177      | VCCQ     |

| 18       | VSS      | 58       | DQ80     | 98       | VSSQ     | 138      | DQ41     | 178      | DQ21     |

| 19       | A10      | 59       | VSSQ     | 99       | DQ48     | 139      | VSSQ     | 179      | DQ20     |

| 20       | A0       | 60       | DQ79     | 100      | DQ49     | 140      | DQ42     | 180      | VSSQ     |

| 21       | VSSQ     | 61       | DQ78     | 101      | DQ50     | 141      | DQ43     | 181      | DQ19     |

| 22       | A1       | 62       | VSSQ     | 102      | DQ51     | 142      | VSSQ     | 182      | DQ18     |

| 23       | A2       | 63       | DQ77     | 103      | VSSQ     | 143      | DQ44     | 183      | VSS      |

| 24       | VCCQ     | 64       | DQ76     | 104      | DQ52     | 144      | DQ45     | 184      | DQ17     |

| 25       | АЗ       | 65       | VCC      | 105      | DQ53     | 145      | VCCQ     | 185      | DQ16     |

| 26       | BA4      | 66       | DQ75     | 106      | VCCQ     | 146      | DQ46     | 186      | VCC      |

| 27       | VCCQ     | 67       | DQ74     | 107      | DQ54     | 147      | DQ47     | 187      | DQ15     |

| 28       | BA5      | 68       | VSS      | 108      | DQ55     | 148      | VSSQ     | 188      | DQ14     |

| 29       | BA6      | 69       | DQ73     | 109      | VSSQ     | 149      | DQ39     | 189      | VSSQ     |

| 30       | VSSQ     | 70       | DQ72     | 110      | DQML2    | 150      | DQ38     | 190      | DQ13     |

| 31       | BA7      | 71       | VSSQ     | 111      | WE2      | 151      | DQ37     | 191      | DQ12     |

| 32       | BA8      | 72       | CLK2     | 112      | VSSQ     | 152      | DQ36     | 192      | VSSQ     |

| 33       | VSS      | 73       | CKE2     | 113      | CAS2     | 153      | VSSQ     | 193      | DQ11     |

| 34       | BA9      | 74       | VCCQ     | 114      | RAS2     | 154      | DQ35     | 194      | DQ10     |

| 35       | DQMU2    | 75       | DQ71     | 115      | VCC      | 155      | DQ34     | 195      | VCCQ     |

| 36       | VCC      | 76       | DQ70     | 116      | CS2      | 156      | VCCQ     | 196      | DQ9      |

| 37       | DQ88     | 77       | VCCQ     | 117      | BA11     | 157      | DQ33     | 197      | DQ8      |

| 38       | DQ89     | 78       | DQ69     | 118      | VSS      | 158      | DQ32     | 198      | VSSQ     |

| 39       | VSSQ     | 79       | DQ68     | 119      | BA10     | 159      | VSSQ     | 199      | DQ0      |

| 40       | DQ90     | 80       | VSSQ     | 120      | BA0      | 160      | DQ31     | 200      | DQ1      |

### **Sample Ordering Information**

| Part Number        | Screening                              | Speed | Package       |  |

|--------------------|----------------------------------------|-------|---------------|--|

| ACT-D1M96S-020F20C | Commercial Temperature                 | 20 ns | 200 Lead CQFP |  |

| ACT-D1M96S-020F20T | CT-D1M96S-020F20T Extended Temperature |       | 200 Lead CQFP |  |

| ACT-D1M96S-020F20M | Extended Temperature Screening         | 20 ns | 200 Lead CQFP |  |

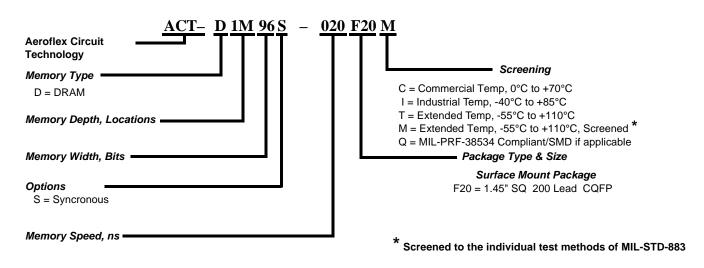

### Part Number Breakdown

Specifications subject to change without notice.

Aeroflex Circuit Technology 35 South Service Road Plainview New York 11803 www.aeroflex.com/act1.htm Telephone: (516) 694-6700 FAX: (516) 694-6715 Toll Free Inquiries: (800) 843-1553 E-Mail: sales-act@aeroflex.com