# H3104A

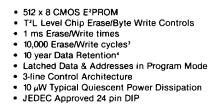

## 512 x 8 CMOS EEPROM

### DESCRIPTION

Hughes H3104A is a CMOS Electrically Erasable Programmable ROM (EEPROM) organized 512 x 8. It is an improved version of the H3104, featuring both lower power dissipation and latched data and addresses during programming. Also, Chip Select (CS) now provides for significantly reduced power to unselected devices in the Program Mode.

Data modification is accomplished by first raising the power voltage, VDD to +VPP and selecting the device with CS high (+5V). Then, erasing or writing is controlled with T²L level signals to appropriate control inputs  $\overline{OE}$  (Erase) and  $\overline{CE}$  (Write).

All read operations are performed with  $V_{DD}$  at 5 volts. With CS at a high level, the falling edge of the Chip Enable signal ( $\overline{CE}$ ) latches a valid address input and initiates the accessing of data. The information is enabled on the bus when Output Enable ( $\overline{OE}$ ) is a low level.

The Chip Select (CS) input for this device is functional in all modes, allowing for chip selection in the Read, Erase, or Write modes independent of  $\overline{OE}$  and  $\overline{CE}$  inputs.

The H3104A is available in a 24 lead dual-in-line ceramic package (D suffix), plastic package (P suffix), or leadless chip carrier (L suffix). Commercial (HC3104A), Industrial (HI3104A), and Military (HB3104A) versions are available.

Leadless Chip Carrier

### **FEATURES**

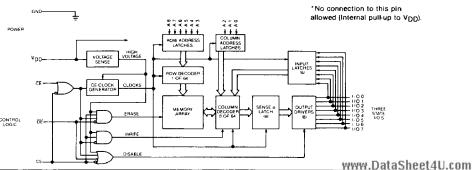

### PIN CONFIGURATION

Dual-In-Line Package

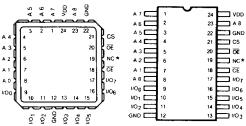

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

DC Supply Voltage Range ..... – 0.3 to + 18 Volts (All voltage referenced to GND terminal)

Input Voltage Range ..... VSS -0.3V to VDD + 0.3V

Storage Temperature Range .... - 65 °C to + 150 °C

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. ErasefWrite functions above 17 V Vpp will adversely affect endurance.

### RECOMMENDED OPERATING CONDITIONS

|                                | <u>-</u>        | Fised Mode      | Write or Erape Mode |

|--------------------------------|-----------------|-----------------|---------------------|

| V <sub>DD</sub> Supply Voltage |                 | 5 ± 1 Volts     | 16 ± 1 Volts        |

| Temperature Range              | Plastic Package | -40°C to +85°C  | - 40 °C to +85 °C   |

| Tomporatore mange              | Ceramic Package | -55°C to +125°C | -55°C to +125°C     |

### DC OPERATING CHARACTERISTICS

Read: VDD = 6 Unless Otherwise Specified

|                 |                                 |      | - <b>- 3</b> *C |      |      | -40°C to +85°C -55°C to 4°125°C |      |      |       |                                                         |

|-----------------|---------------------------------|------|-----------------|------|------|---------------------------------|------|------|-------|---------------------------------------------------------|

| Symbo           | Parameter                       | Min. | Typ.            | Max. | Min. | Mex.                            | Min. | Max. | Unite | Test A<br>Conditions                                    |

| IDDS            | V <sub>DD</sub> Standby Current | _    | 2               | 100  | _    | 100                             | _    | 200  | μA    | $\overline{CE} = \overline{OE} = 6 \text{ V},$ $CS = 0$ |

| IDDA            | V <sub>DD</sub> Active Current  | -    | 2               | 100  |      | 100                             | _    | 200  | μА    | CE = OE = 0,<br>CS = 6 V                                |

| VOL             | Output Low Voltage              | -    | 0.25            | 0.45 | _    | 0.45                            | -    | 0.45 | V     | V <sub>DD</sub> = 4.75 V,<br>I <sub>O</sub> = 2.1mA     |

| ∨он             | Output High Voltage             | 2.4  | 4.5             | -    | 2.4  | _                               | 2.4  | _    | v     | V <sub>DD</sub> = 4.75V,<br>I <sub>O</sub> = -400μA     |

| VIL             | Input Low Voltage               | _    | _               | 8.0  | _    | 0.76                            | -    | 0.76 | v     | V <sub>DD</sub> = 4.75 V                                |

| VIH             | Input High Voltage              | 3.08 | _               | _    | 3.18 | _                               | 3.18 | _    | v     | V <sub>DD</sub> = 5.25 V                                |

| <sup>I</sup> LI | Input Leakage Current           | _    | ±1              | ±5   |      | ± 10                            |      | ± 10 | μА    | V <sub>IN</sub> = 0 or V <sub>DD</sub>                  |

| lo              | Output Leakage Current          |      | ±1              | ±5   |      | ± 10                            | _    | ± 10 | Αц    | VO = 0 or VDD                                           |

Erase or Write: VDD= 17 V Unless Otherwise Specified

|        |                                 | 4-28 °C |      |      | -100°C to +85°C |      | -55°C to + 125°C |      |       |                                        |

|--------|---------------------------------|---------|------|------|-----------------|------|------------------|------|-------|----------------------------------------|

| Symbol | Paramoler 1                     | Main.   | Typ. | Max. | Min.            | Max. | Min,             | Mex  | Units | Test<br>Conditions                     |

| IDPP   | V <sub>DD</sub> Program Current | _       | 1    | 3    | -               | 5    |                  | 5    | mA    | CS = 0 V                               |

| IDPP   | V <sub>DD</sub> Program Current | _       | 2.5  | 5    |                 | 7    | _                | 7    | mA    | CS = 5 V                               |

| VIL    | Input Low Voltage               | _       | _    | 0.8  | -               | 0.76 | -                | 0.76 | ٧     | _                                      |

| VIH    | Input High Voltage              | 3.08    | _    | _    | 3.18            | _    | 3.18             | -    | v     | _                                      |

| ILI    | Input Leakage Current           | _       | ±1   | ±5   | _               | ± 10 | _                | ± 10 | μА    | V <sub>IN</sub> = 0 or V <sub>DD</sub> |

| ILO    | Output Leakage Current          | _       | ±1   | ±5   |                 | ± 10 | Γ –              | ± 10 | μА    | V <sub>O</sub> = 0 or V <sub>DD</sub>  |

### Notes:

- 1. This parameter is only sampled and is not 100% tested.

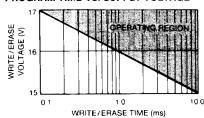

- 2. Erase and Write time is a function of + Vpp. See characteristic curve.

- 3. Endurance is the maximum number of erase/write cycles per byte.

www.DataSheet4U.com

4. Retention is the amount of time the data is retained in memory without power being supplied.

## H3104A

# AC OPERATING CHARACTERISTICS

Read: VDD = 5V ±5% Unless Otherwise Specified

| 1.74             |                                 | L    | . 25 °C |     | ÷ 40°C 1 | 0 +65°C | -   55°C | - 125°C | H.    |                                            |

|------------------|---------------------------------|------|---------|-----|----------|---------|----------|---------|-------|--------------------------------------------|

| Symbol           | Parameter                       | Min. | Typ.    | Max | Min.     | Mex.    | Min.     | Max     | Units | Test<br>Conditions                         |

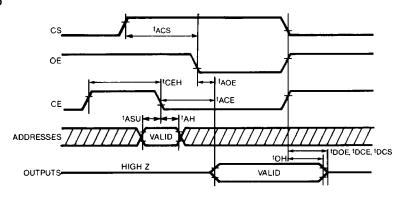

| <sup>t</sup> ASU | Address Set Up Time             | 350  | _       |     | 500      |         | 500      | _       | ns    | CS = V <sub>H</sub>                        |

| t <sub>AH</sub>  | Address Hold Time               | 150  | 50      | -   | 200      |         | 200      | _       | ns    | CS = VH                                    |

| †ACE             | Access Time from ĈĒ             | -    | 500     | 700 | _        | 925     | -        | 925     | ns    | CS = VH. OE = VL                           |

| †OE              | Output Enable Time              | _    | 200     | 325 |          | 475     | -        | 475     | ns    | CS = VH. OE = VL                           |

| †ACS             | Access Time from CS             | -    | -       | 500 | -        | 700     | -        | 700     | ns    | CE = VL, OE = VL                           |

| tDOE             | Time Disable to OE              | -    | _       | 525 | -        | 650     | -        | 650     | ns    | CE = VL. CS = VH                           |

| †DCE             | Time Disable to CE              |      |         | 525 |          | 650     |          | 650     | ns    | $\overline{OE} = V_L, CS = V_H$            |

| tDCS             | Time Disable to CS              | 1    | 1       | 600 |          | 750     |          | 750     | ns    | $\overline{OE} = V_L, \overline{CE} = V_L$ |

| <sup>†</sup> CEH | CE High Time                    | 1.1  | 0.5     | -   | 1,4      | -       | 1.4      | -       | Sىر   | _                                          |

| DYN              | V <sub>DD</sub> Dynamic Current | -    | 0.5     | 1.0 | -        | 12      | _        | 1.2     | mA    | t = 100 KHz                                |

$\begin{array}{ll} \textbf{Read Test Conditions} \\ \textbf{Output Load:} & \textbf{C}_L = 50 \text{pF} \\ \textbf{Input Levels:} & \textbf{V}_H = 3.18 \text{ Volts, V}_L = 0.45 \text{ Volts} \end{array}$

Timing Measurement Reference Levels: Input = Output = 50%

## Erase and Write. VDD = 16V Unless Otherwise Specified

| 4      |                                  | +25°C |      |      | -40°C to +85°C |      | - 55°C to + 125°C |      |       |                     |  |

|--------|----------------------------------|-------|------|------|----------------|------|-------------------|------|-------|---------------------|--|

| Symbol | Parameter                        | Min.  | Typ. | Max. | Min.           | Max. | . Min.            | Mex. | Units | Conditions          |  |

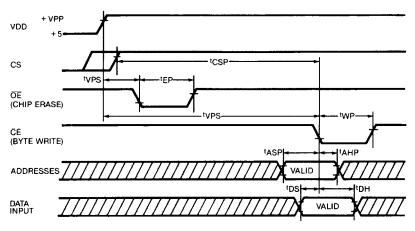

| tvps   | Program Set Up Time <sup>1</sup> | 5     | _    | _    | 5              | _    | 5                 |      | μS    | <del>-</del>        |  |

| tEP    | Erase Pulse Width <sup>2</sup>   | 1     | _    | 10   | 1              | 10   | 1                 | 10   | ms    | CS = VH, CE = VH    |  |

| twp    | Write Pulse Width <sup>2</sup>   | 1     | -    | 10   | 1              | 10   | 1                 | 10   | ms    | CS = VH, OE = VH    |  |

| tDS    | Data Set Up Time'                | 200   | _    | -    | 260            | _    | 260               | _    | ns    | CS = VH, OE = VH    |  |

| tDH    | Data Hold Time'                  | 750   | _    | -    | 900            | -    | 1000              |      | ns    | CS = VH, OE = VH    |  |

| tASP   | Address Set Up Time¹             | 350   | -    | -    | 450            | _    | 500               | _    | ns    | cs = v <sub>H</sub> |  |

| tAHP   | Address Hold Time'               | 200   | -    | -    | 260            |      | 260               | _    | ns    | CS = VH             |  |

| tCSP   | CS Set Up Time Program           | 500   | _    | Ī-   | 625            | -    | 700               | _    | ns    | _                   |  |

## **Programming Test Conditions**

Input Levels: V<sub>H</sub> = 3.18 Volts, V<sub>L</sub> = 0.45 Volts

Timing Measurement Reference Levels: Input = Output = 50%

## **PROGRAM TIME VS. SUPPLY VOLTAGE**

## **TIMING DIAGRAM**

# READ

# **CHIP ERASE / BYTE WRITE**

### **OPERATING MODES**

The H3104A has three modes of operation: Read, Chip Erase and Byte Write, all enabled when the chip is selected (CS = high). In the Read Mode the H3104A functions as a normal CMOS ROM. When the power input ( $V_{DD}$ ) is raised to +Vpp the Erase or Write Mode is enabled. In the Erase Mode, all bytes are reset to a logic low (GND). In the Write Mode, bits of the addressed byte may be programmed to a logic high. An Erase Operation is required before re-writing over previously Programmed data. Detailed procedures for each mode follow:

**READ MODE:** The circuit reads addresses on the falling edge of  $\overline{CE}$  and latches the accessed data until  $\overline{CE}$  goes high again. The latched data will appear at the outputs whenever  $\overline{CE}$  is low, CS is high, and  $\overline{OE}$  is low.

**ERASE MODE:** A Chip Erase (all 0's in memory) is accomplished by setting  $\overline{CE}$  and  $\overline{OE}$  high, raising the positive supply to +Vpp and then pulsing  $\overline{OE}$  low. When the circuit internally senses the +Vpp voltage, it floats the outputs preventing +Vpp level signals from appearing on the data I/O bus.

WRITE MODE: A Write consists of programming 1's into bits that contain a 0. A byte is written by setting CE and OE high, raising the positive supply to +Vpp, and pulsing CE low. The address and data lines must be valid when CE falls. Data and addresses are latched while CE is low. A Write operation can follow an Erase while holding +Vpp at +Vpp, and several or all the bytes can be programmed with +Vpp held at +Vpp.

### SUMMARY OF OPERATING MODES

Logic 1 = High, Logic 0 = Low, X = Do not care

| Standby (unselected)* | X | 0 | X | +5 or + V <sub>PP</sub> | Floating    |

|-----------------------|---|---|---|-------------------------|-------------|

| Standby (selected)*   | 1 | 1 | 1 | +5 or + V <sub>PP</sub> | Floating    |

| Standby (selected)    | 1 | 1 | 0 | +5                      | Floating    |

| Read                  | 0 | 1 | 1 | + 5                     | Floating    |

| Read                  | 0 | 1 | 0 | +5                      | Data Output |

| Erase                 | 1 | 1 | 0 | + V <sub>PP</sub>       | Floating    |

| Write                 | 0 | 1 | 1 | + Vpp                   | Data Input  |

| Prohibited State      | 0 | 1 | 0 | + Vpp                   | Data Input  |

<sup>\*</sup> Recommended modes for V<sub>DD</sub> transition to and from + V<sub>PP</sub> V<sub>DD</sub> should not fall below input levels during transition.

## PIN DESCRIPTIONS

A 0 - A 8: Address inputs which select one of 512 bytes of memory for either Read or Write. The addresses need to be valid during the falling edge of CE.

WOO -WO7: Bidirectional three-state data lines that are Data outputs during a Read operation and Data inputs during a Write operation.

**GND**: Negative supply terminal and V = 0 reference.

VDD: Positive supply terminal. It is raised to +Vpp for Erase and Write operations.

CS: Chip Select. A Logic Low disables all control inputs in all modes.

**OE:** Output Enable. A Logic High disables the Data Output Drivers in normal operation. If V<sub>DD</sub> = + V<sub>PP</sub>, a Logic Low causes a chip erase. This input is active only when CS is high.

CE: Chip Enable. A Logic Low at this input latches the input address during a Read operation and latches both addresses and data inputs during a Write operation. For the Read operation, accessed data is latched and valid as long as CE is held at a Logic Low. If VDD = +VPp., a Logic Low causes a byte Write operation. This input is active only when CS is high.