AUGUST 1994

930 Series Companion Chip

# DATASHEET

2

# FEATURES

- Integrated Interrupt Request Controller, Timer, and Serial Data Transmitter/Receiver

- 930 Series processor interface

- 40 MHz operation

- 15-channel Interrupt Request Controller

- Individual interrupt masks

- Positive and negative level and edge trigger options for each channel

- Four independent 16-bit timers

- Prescalers for two timers

- Five modes of operation for each timer

- Two Serial Data Transmitter and Receiver Units

- Compatible with MB89251

- Synchronous or asynchronous operation

- 5 to 8 bit character length selection

- Parity bit option

- Internal or external synchronous mode options

- One (MONOSYNC) or two (BISYNC) synchronous character options

- 0.8 micron gate CMOS technology.

#### **GENERAL DESCRIPTION**

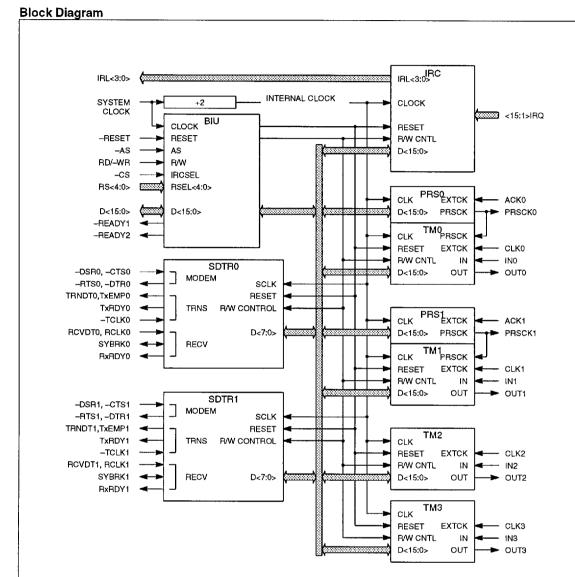

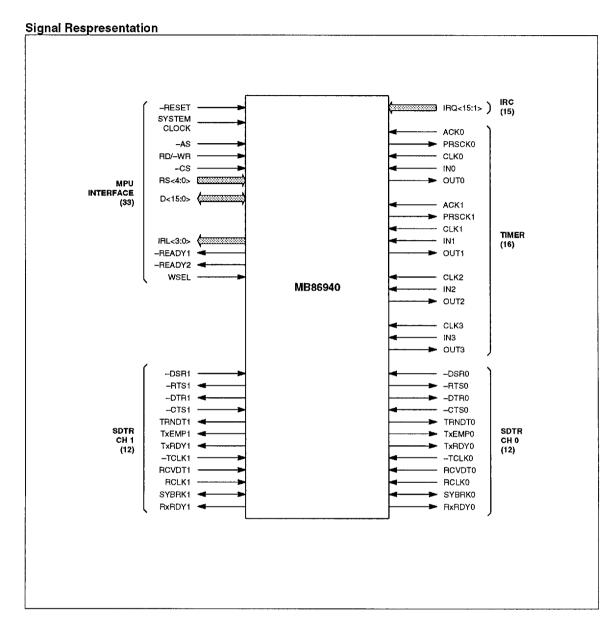

The MB86940 930 Series Companion Chip is a combination interrupt request controller (IRC), timer, and serial data transmitter/receiver (SDTR) that is designed for use with the 930 Series 32-bit RISC embedded processors.

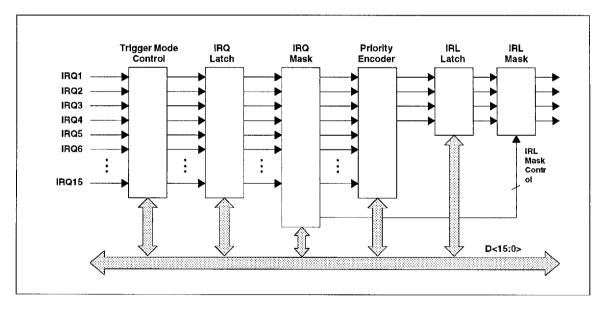

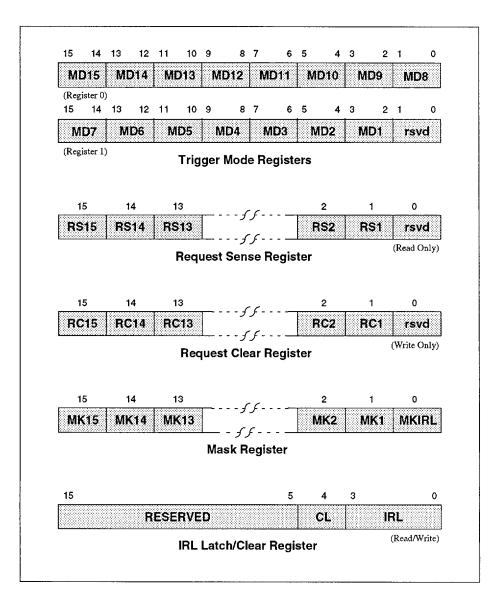

The interrupt controller supports 15 maskable, prioritized interrupts. The system processor can program each interrupt channel to trigger in response to a high level, a low level, arising edge, or a falling edge. The IRC1 atches the interrupt requests and asserts the encoded level number of the highest-priority interrupt on the IRL<3:0> Interrupt Request Bus to interrupt the processor and identify the interrupt.

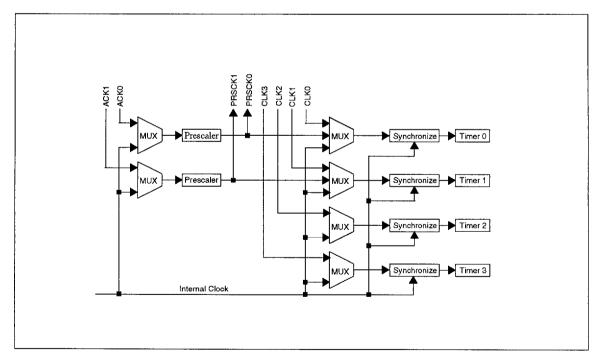

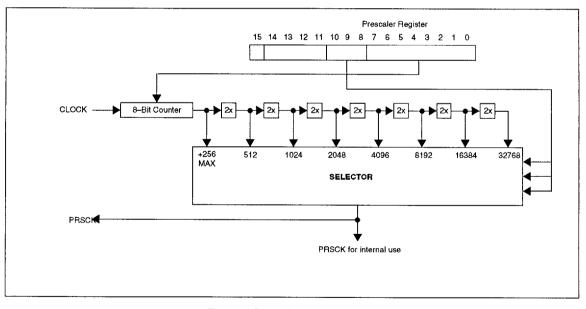

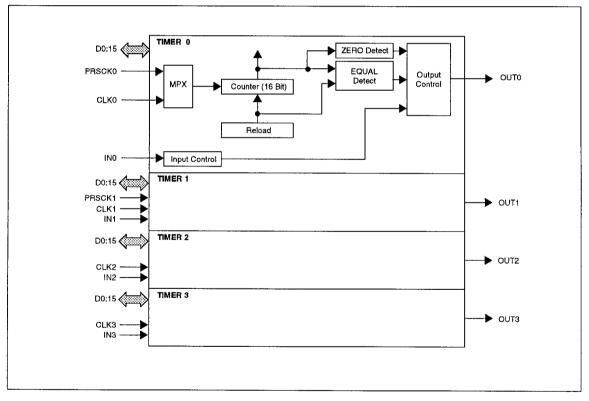

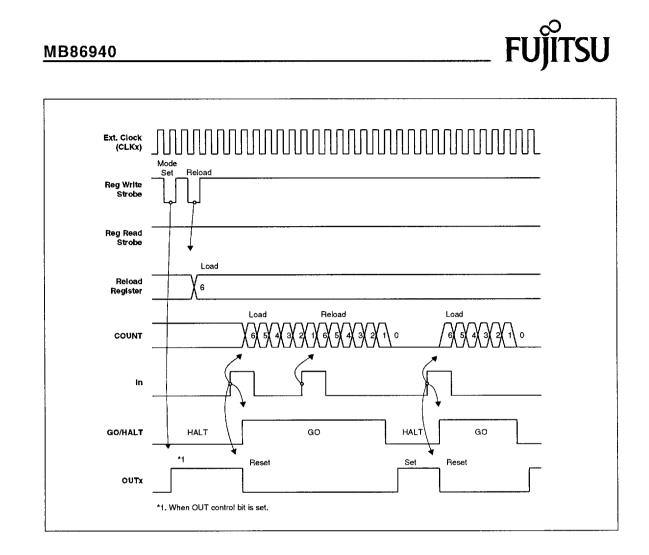

The timers can generate periodic interrupts and square waves, and feature two watchdog modes. They can be clocked by two prescalers, by external clocks, or by the internal MB86940 clock.

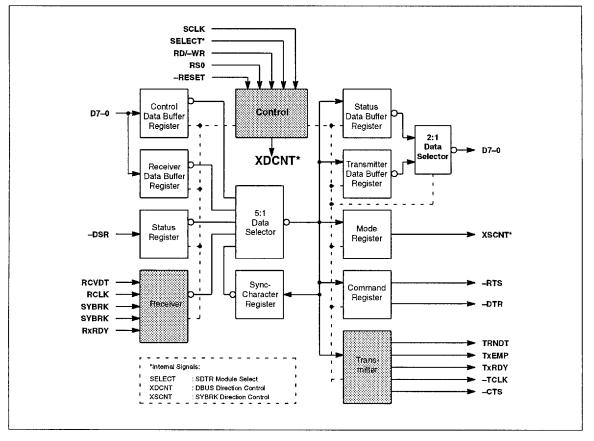

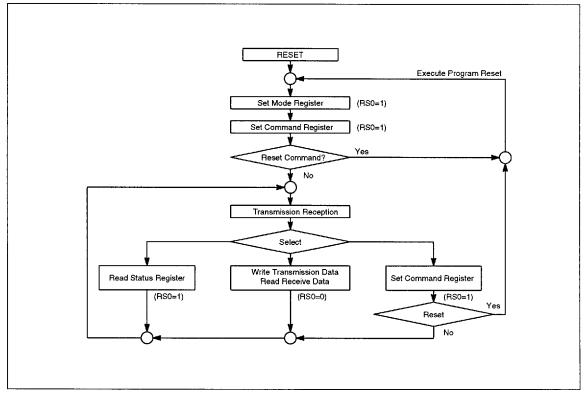

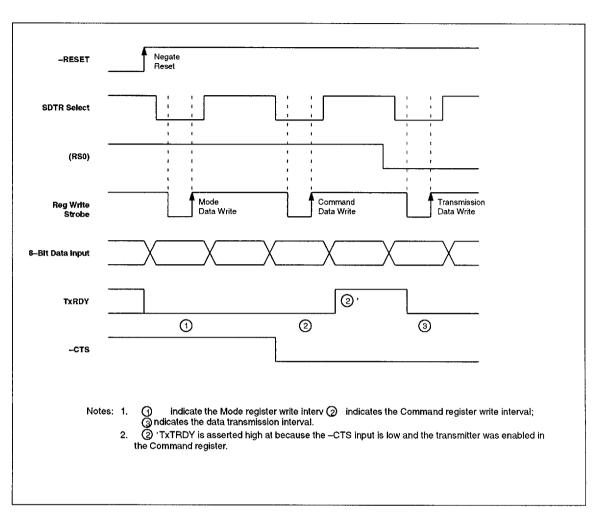

The two Serial Data Transmitter and Receiver (SDTR) units support both synchronous and asynchronous modes, and are program-compatible with standard serial communication devices. They operate independently and can be clocked with the internal MB86940 clock, with external clocks, or with clocks generated by the on-chip timers. Each SDTR supports the communication protocol and handshaking signals necessary for modem interface and control.

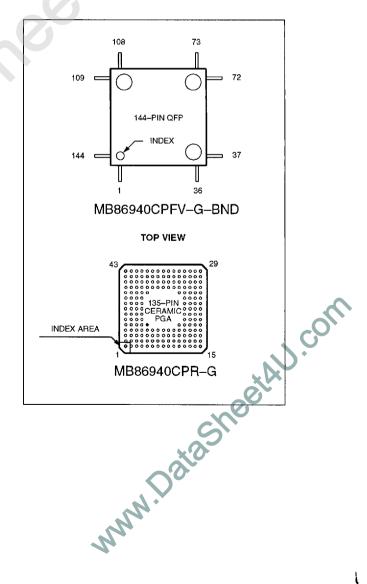

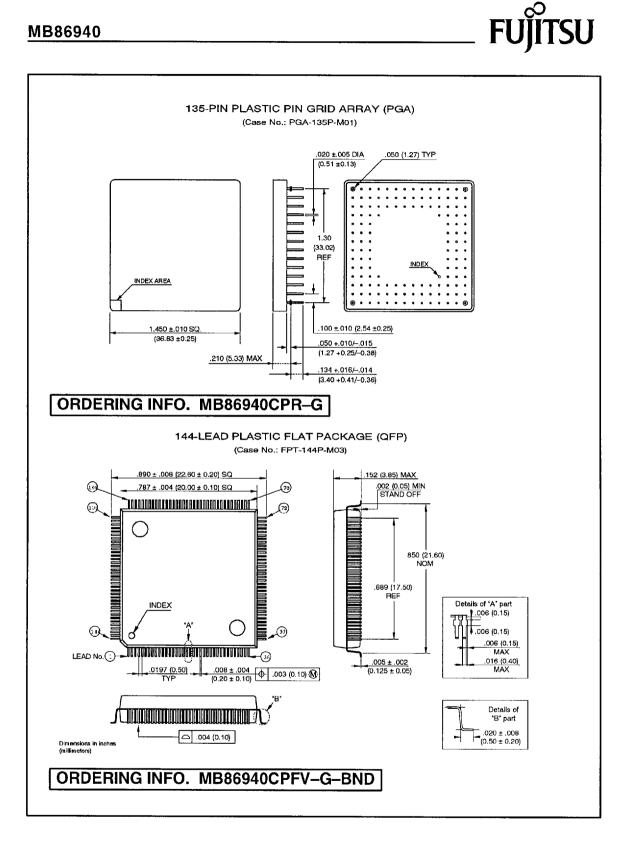

#### **PACKAGE OPTIONS**

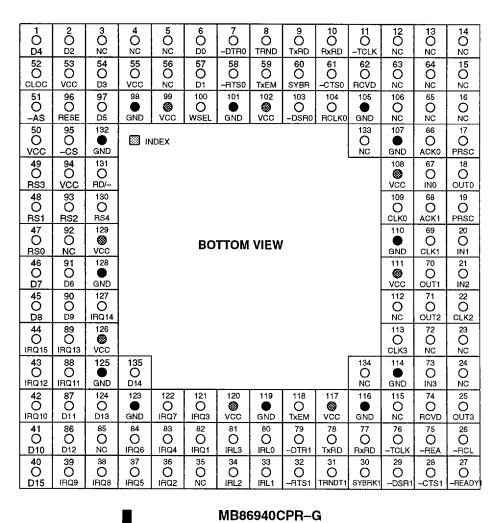

## PIN ASSIGNMENT --- 135-PIN PGA

| PIN<br>NO. | PIN NAME       | TYPE | PIN<br>NO. | PIN NAME       | TYPE | PIN<br>NO. | PIN NAME       | TYPE |

|------------|----------------|------|------------|----------------|------|------------|----------------|------|

| 1          | D4             | I/O  | 46         | D7             | I/O  | 91         | D6             | 1/0  |

| 2          | D2             | I/O  | 47         | RS0            | I    | 92         | NC             | _    |

| 3          | NC             | -    | 48         | RS1            | I    | 93         | RS2            | I    |

| 4          | NC             | -    | 49         | RS3            | I    | 94         | VCC            | -    |

| 5          | NC             | _    | 50         | VCC            | -    | 95         | -CS            | -    |

| 6          | D0             | I/O  | 51         | –AS            | I.   | 96         | -RESET         | 1    |

| 7          | -DTR0          | 0    | 52         | CLOCK          | I.   | 97         | D5             | 1/O  |

| 8          | TRNDT0         | 0    | 53         | VCC            | -    | 98         | GND            | -    |

| 9          | TxRDY0         | 0    | 54         | D3             | I/O  | 99         | VCC            |      |

| 10         | RxRDY0         | 0    | 55         | VCC            | -    | 100        | WSEL           | i i  |

| 11         | TCLK0          | I.   | 56         | NC             | -    | 101        | GND            | -    |

| 12         | NC             |      | 57         | D1             | I/O  | 102        | VCC            | -    |

| 13         | NC             |      | 58         | -RTS0          | 0    | 103        | -DSR0          | 1    |

| 14         | Do Not Connect |      | 59         | TxEMP0         | 0    | 104        | RCLK0          | 1    |

| 15         | Do Not Connect | _    | 60         | SYBRK0         | I/O  | 105        | GND            |      |

| 16         | Do Not Connect | _    | 61         | -CTS0          | i    | 106        | NC             | -    |

| 17         | PRSCK0         | 0    | 62         | RCVDT0         | 1    | 107        | GND            | - 1  |

| 18         | OUTO           | 0    | 63         | NC             | -    | 108        | VCC            | - 1  |

| 19         | PRSCK1         | 0    | 64         | NC             | -    | 109        | CLK0           | 1    |

| 20         | IN1            | I.   | 65         | Do Not Connect | -    | 110        | GND            | -    |

| 21         | IN2            | 1    | 66         | ACK0           | I I  | 111        | VCC            |      |

| 22         | CLK2           | 1    | 67         | IN0            | I I  | 112        | NC             | -    |

| 23         | NC             | _    | 68         | ACK1           | 1    | 113        | CLK3           |      |

| 24         | NC             |      | 69         | CLK1           | 1    | 114        | GND            | _    |

| 25         | OUT3           | 0    | 70         | OUT1           | 0    | 115        | NC             |      |

| 26         | RCLK1          | 1    | 71         | OUT2           | 0    | 116        | GND            | _    |

| 27         | READY1         | 0    | 72         | NC             | -    | 117        | VCC            | -    |

| 28         | -CTS1          | 1    | 73         | IN3            | 1    | 118        | TxEMP1         | 0    |

| 29         | -DSR1          | 1    | 74         | RCVDT1         | 1    | 119        | GND            | _    |

| 30         | SYBRK1         | 1/0  | 75         | -READY2        | 0    | 120        | VCC            | -    |

| 31         | TRNDT1         | 0    | 76         | -TCLK1         | 1    | 121        | IRQ3           |      |

| 32         | -RTS1          | 0    | 77         | RxRDY1         | 0    | 122        | IRQ7           | 1    |

| 33         | IRL1           | 0    | 78         | TxRDY1         | 0    | 123        | GND            | -    |

| 34         | IRL2           | 0    | 79         | -DTR1          | 0    | 124        | D13            | I/O  |

| 35         | NC             |      | 80         | IRL0           | 0    | 125        | GND            | _    |

| 36         | IRQ2           | 1    | 81         | IRL3           | 0    | 126        | VCC            | _    |

| 37         | IRQ5           | 1    | 82         | IRQ1           | 1    | 127        | IRQ14          | I.   |

| 38         | IRQ8           | 1    | 83         | IRQ4           | 1    | 128        | GND            | —    |

| 39         | IRQ9           | 1    | 84         | IRQ6           | I.   | 129        | VCC            | -    |

| 40         | D15            | I/O  | 85         | NC             |      | 130        | RS4            | 1    |

| 41         | D10            | I/O  | 86         | D12            | I/O  | 131        | RD/-WR         | 1    |

| 42         | IRQ10          | I.   | 87         | D11            | I/O  | 132        | GND            | I.   |

| 43         | IRQ12          | I.   | 88         | IRQ11          | 1    | 133        | Do Not Connect |      |

| 44         | IRQ15          | 1    | 89         | IRQ13          | I    | 134        | NC             | —    |

| 45         | D8             | 1/0  | 90         | D9             | I/O  | 135        | D14            | 1/O  |

|            |                |      |            |                |      | I          |                |      |

#### PIN ASSIGNMENT --- 144-PIN QPFT

| 5     IRQ8     I     53     SYBRK1     I/O     101     D7     I/C       6     IRQ7     I     54     VCC      102     GND        7     IRL3     O     55     GND      103     Do Not Connect        9     GND      57     TRNDT1     O     106     Do Not Connect        10     IRL1     O     58     -RTS1     I     107     NC        11     IRL0     O     59     -CTS1     I     108     NC        12     IRQ6     I     61     CLK0     I     110     NC        14     IRQ4     I     62     INO     I     110     NC        15     IRQ3     I     63     ACK0     I     111     NC        16     NC     -     64     PRSCK0     O     112     NC  <                                                                                                                                                                                    | PIN<br>NO. | PIN NAME | TYPE | PIN<br>NO. | PIN NAME       | TYPE | PIN<br>NO. | PIN NAME       | TYPE     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------|------------|----------------|------|------------|----------------|----------|

| 3     IRQ10     I     51     RCLK1     I     99     NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1          | VCC      |      | 49         | NC             |      | 97         | NC             | _        |

| 4     IRQ8     I     52     TXRDY1     0     100     D6     I/C       5     IRQ8     I     53     SYBRK1     I/O     101     D7     I/O       6     IRQ7     I     54     VCC      102     GND        7     IRL3     0     55     GND      103     Do Not Connect        8     IRL2     0     56     -DTR1     0     104     Do Not Connect        10     IRL1     0     58     -RTS1     0     106     Do Not Connect        11     IRL0     0     59     -CTS1     I     107     NC        12     IRQ6     I     610     CLK0     I     109     NC        13     IRQ3     I     63     ACK0     I     1111     NC        14     IRQ4     I     62     OUTO     113     WSEL     I <td>2</td> <td>IRQ11</td> <td>1</td> <td>50</td> <td>RCVDT1</td> <td>1</td> <td>98</td> <td>NC</td> <td>_</td>                                          | 2          | IRQ11    | 1    | 50         | RCVDT1         | 1    | 98         | NC             | _        |

| 5     IRQ8     1     53     SYBRK1     I/O     101     D7     I/O       6     IRQ7     I     54     VCC      102     GND        7     IRL3     O     55     GND      103     Do Not Connect        9     GND      57     TRNDT1     O     105     Do Not Connect        10     IRL1     O     58     -RTS1     O     106     Do Not Connect        11     IRL0     O     59     -CTS1     I     107     NC        12     IRQ6     I     61     CLK0     I     109     NC        13     IRQ3     I     63     ACK0     I     111     NC        16     NC      64     PRSCK0     O     112     NC        17     -READY1     O     68     PRSCK1     O     116     VCC                                                                                                                                                                         | 3          | IRQ10    | i i  | 51         | RCLK1          | 1    | 99         | NC             |          |

| 6     IRQ7     1     54     VCC     —     102     GND     —       7     IRL3     0     55     GND     —     103     Do Not Connect     —       9     GND     —     57     TRNDT1     0     104     Do Not Connect     —       10     IRL1     0     58     -RTS1     0     106     Do Not Connect     —       11     IRL0     0     59     -CTS1     I     107     NC     —       12     IRQ6     I     61     CLK0     I     109     NC     —       13     IRQ3     I     63     ACK0     I     111     NC     —       16     NC     —     64     PRSCK0     0     113     WSEL     I       18     VCC     —     66     GND     —     114     VCC     —       20     -READY1     0     68     PRSCK1     0     116     VCC     —                                                                                                           | 4          | IRQ9     | ł    | 52         | TxRDY1         | 0    | 100        | D6             | I/O      |

| 7   IRL3   0   55   GND   —   103   Do Not Connect   —     8   IRL2   0   56   —DTR1   0   104   Do Not Connect   —     9   GND   —   57   TRNDT1   0   105   Do Not Connect   —     10   IRL1   0   59   —CTS1   I   107   NC   —     11   IRL0   0   59   —CTS1   I   107   NC   —     12   IRQ6   I   60   —DSR1   I   108   NC   —     13   IRQ5   I   61   CLK0   I   109   NC   —     14   IRQ4   I   62   NO   I   111   NC   —     17   —READY2   0   65   OUT0   0   113   WSEL   I     18   VCC   —   66   GND   —   114   VCC   —     19   GND   —   67   OUT1   0   115   VCC <td< td=""><td>5</td><td>IRQ8</td><td>1</td><td>53</td><td>SYBRK1</td><td>I/O</td><td>101</td><td>D7</td><td>I/O</td></td<>                                                                                                                       | 5          | IRQ8     | 1    | 53         | SYBRK1         | I/O  | 101        | D7             | I/O      |

| 8     IRL2     0     56     -DTR1     0     104     Do Not Connect        9     GND      57     TRNDT1     0     105     Do Not Connect        10     IRL1     0     58     -RTS1     0     106     Do Not Connect        11     IRL0     0     59     -CTS1     I     107     NC        12     IRQ6     1     61     CLK0     I     109     NC        13     IRQ3     1     63     ACK0     I     111     NC        16     NC      64     PRSCK0     0     113     WSEL     I       18     VCC      66     GND      114     VCC        19     GND      67     OUT1     0     115     VCC        21     NC      72     NC      120     -AS </td <td>6</td> <td>IRQ7</td> <td>1</td> <td>54</td> <td>VCC</td> <td>-</td> <td>102</td> <td>GND</td> <td>—</td>                                                                                | 6          | IRQ7     | 1    | 54         | VCC            | -    | 102        | GND            | —        |

| 9     GND     —     57     TRNDT1     O     105     Da Not Connect     —       10     IRL1     O     58     -RTS1     O     106     Da Not Connect     —       11     IRL0     O     59     -CTS1     I     107     NC     —       12     IRQ5     I     61     CLK0     I     109     NC     —       13     IRQ5     I     61     CLK0     I     110     NC     —       14     IRQ3     I     63     ACK0     I     111     NC     —       16     NC     —     64     PRSCK0     O     113     WSEL     I       18     VCC     —     66     GND     —     114     VCC     —       20     -READY1     O     68     PRSCK1     O     116     VCC     —       21     NC     —     69     ACK1     I     117     GND     —                                                                                                                     | 7          | IRL3     | 0    | 55         | GND            | —    | 103        | Do Not Connect |          |

| 10   IRL1   0   58   -RTS1   0   106   Do Not Connect   -     11   IRL0   0   59   -CTS1   I   107   NC   -     12   IRQ6   I   60   -DSR1   I   108   NC   -     13   IRQ5   I   61   CLK0   I   109   NC   -     14   IRQ4   I   62   IN0   I   110   NC   -     15   IRQ3   I   63   ACK0   I   111   NC   -     16   NC   -   64   PRSCK0   O   113   WSEL   I     18   VCC   -   66   GND   -   114   VCC   -     20   -READY1   O   68   PRSCK1   O   116   VCC   -     21   NC   -   69   ACK1   I   117   GND   -     22   IRQ2   I   70   IN1   I   118   -RESET   I <td>8</td> <td>IRL2</td> <td>0</td> <td>56</td> <td>-DTR1</td> <td>0</td> <td>104</td> <td>Do Not Connect</td> <td>_</td>                                                                                                                                     | 8          | IRL2     | 0    | 56         | -DTR1          | 0    | 104        | Do Not Connect | _        |

| 11   IRL0   O   59   -CTS1   I   107   NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9          | GND      | _    | 57         | TRNDT1         | 0    | 105        | Do Not Connect | —        |

| 12   IRG6   I   60   -DSR1   I   108   NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10         | IRL1     | 0    | 58         | -RTS1          | 0    | 106        | Do Not Connect | —        |

| 13   IRQ5   I   61   CLK0   I   109   NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11         | IRL0     | 0    | 59         | -CTS1          | 1    | 107        | NC             |          |

| 14   IRQ4   I   62   IN0   I   110   NC   —     15   IRQ3   I   63   ACK0   I   111   NC   —     16   NC   —   64   PRSCK0   O   112   NC   —     17   -READY2   O   65   OUT0   O   113   WSEL   I     18   VCC   —   66   GND   —   114   VCC   —     20   -READY1   O   68   PRSCK1   O   116   VCC   —     21   NC   —   69   ACK1   I   117   GND   —     22   IRQ2   I   70   IN1   I   118   -RESET   I     23   IRQ1   I   71   CLK1   I   119   GLOCK   I     24   NC   —   72   NC   —   120   -AS   I     24   NC   —   73   VCC   —   121   RD/-WR   I                                                                                                                                                                                                                                                                          | 12         | IRQ6     | 1    | 60         | -DSR1          | 1    | 108        | NC             | —        |

| 15   IRQ3   I   63   ACK0   I   111   NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13         | IRQ5     | I    | 61         | CLK0           | 1    | 109        | NC             |          |

| 16     NC     -     64     PRSCK0     O     112     NC     -       17     -READY2     O     65     OUT0     O     113     WSEL     I       18     VCC      66     GND      114     VCC        19     GND      67     OUT1     O     115     VCC        20     -READY1     O     68     PRSCK1     O     116     VCC        21     NC      69     ACK1     I     117     GND        22     IRQ1     I     71     CLK1     I     119     CLOCK     I       24     NC      72     NC      120     -AS     I       25     NC      73     VCC     -     121     RD/-WR     I       26     -DSR0     I     74     CLK3     I     122     -CS     I                                                                                                                                                                                                | 14         | IRQ4     | 1    | 62         | IN0            | 1    | 110        | NC             | —        |

| 17   -READY2   0   65   OUT0   0   113   WSEL   1     18   VCC   -   66   GND   -   114   VCC   -     19   GND   -   67   OUT1   0   115   VCC   -     20   -READY1   0   68   PRSCK1   0   116   VCC   -     21   NC   -   69   ACK1   1   117   GND   -     22   IRQ2   I   70   IN1   I   118   -RESET   I     23   IRQ1   I   71   CLK1   I   119   CLOCK   I     24   NC   -   72   NC   -   120   -AS   I     25   NC   -   73   VCC   -   121   RD/-WR   I     26   -DSR0   I   74   CLK3   I   122   -CS   I     27   -CTS0   I   75   IN3   I   124   D8   I/CO                                                                                                                                                                                                                                                                    | 15         | IRQ3     | I I  | 63         | ACK0           | I    | 111        | NC             |          |

| 18   VCC    66   GND    114   VCC      19   GND    67   OUT1   O   115   VCC      20   -READY1   O   68   PRSCK1   O   116   VCC      21   NC    69   ACK1   I   117   GND      22   IRQ2   I   70   IN1   I   118   -RESET   I     23   IRQ1   I   71   CLK1   I   119   CLOCK   I     24   NC    72   NC    120   -AS   I     25   NC    73   VCC    121   RD/-WR   I     26   -DSR0   I   74   CLK3   I   122   -CS   I     27   -CTS0   I   75   IN3   I   123   VCC      28   -RST0   O   76   CLK2   I   124   D8   I//C                                                                                                                                                                                                                                                                                                              |            |          | _    | 64         | PRSCK0         | 0    | 112        | NC             |          |

| 19   GND   —   67   OUT1   O   115   VCC   —     20   -READY1   O   68   PRSCK1   O   116   VCC   —     21   NC   —   69   ACK1   I   117   GND   —     22   IRQ2   I   70   IN1   I   118   -RESET   I     23   IRQ1   I   71   CLK1   I   119   CLOCK   I     24   NC   —   72   NC   —   120   -AS   I     25   NC   —   73   VCC   —   121   RD/-WR   I     26   -DSR0   I   74   CLK3   I   122   -CS   I     27   -CTS0   I   75   IN3   I   123   VCC   —     28   -RST0   O   76   CLK2   I   124   D8   I/CC     30   GND   —   78   Do Not Connect   —   126   VCC   —                                                                                                                                                                                                                                                            | 17         | -READY2  | 0    | 65         | OUTO           | 0    | 113        | WSEL           | I.       |

| 20   -READY1   0   68   PRSCK1   0   116   VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18         | VCC      |      | 66         | GND            | -    | 114        | VCC            |          |

| 21   NC   —   69   ACK1   I   117   GND   —     22   IRQ2   I   70   IN1   I   118   -RESET   I     23   IRQ1   I   71   CLK1   I   119   CLOCK   I     24   NC   —   72   NC   —   120   -AS   I     25   NC   —   73   VCC   —   121   RD/-WR   I     26   -DSR0   I   74   CLK3   I   122   -CS   I     27   -CTS0   I   75   IN3   I   123   VCC   —     28   -RST0   O   76   CLK2   I   124   D8   I/CC     30   GND   —   78   Do Not Connect   —   125   D9   I/C     31   -DTR0   O   79   OUT2   O   127   GND   —     32   SYBRK0   I/O   80   OUT3   O   128   D10   I/C                                                                                                                                                                                                                                                        | 19         | GND      | —    | 67         | OUT1           | 0    | 115        | VCC            |          |

| 22   IRQ2   I   70   IN1   I   118   -RESET   I     23   IRQ1   I   71   CLK1   I   119   CLOCK   I     24   NC   -   72   NC   -   120   -AS   I     25   NC   -   73   VCC   -   121   RD/-WR   I     26   -DSR0   I   74   CLK3   I   122   -CS   I     27   -CTS0   I   75   IN3   I   123   VCC   -     28   -RST0   O   76   CLK2   I   124   D8   I/C     30   GND    78   Do Not Connect   -   126   VCC   -     31   -DTR0   O   79   OUT2   O   128   D10   I/C     33   TXRDY0   O   81   GND   -   129   D11   I/C     34   RCLK0   I   82   D0   I/O   130   RS4   1                                                                                                                                                                                                                                                           |            |          | 0    | 68         | PRSCK1         | 0    | 116        | VCC            |          |

| 23   IRQ1   I   71   CLK1   I   119   CLOCK   I     24   NC   -   72   NC   -   120   -AS   I     25   NC   -   73   VCC   -   121   RD/-WR   I     26   -DSR0   I   74   CLK3   I   122   -CS   I     27   -CTS0   I   75   IN3   I   123   VCC   -     28   -RST0   O   76   CLK2   I   124   D8   I/C     29   TRNDT0   O   77   IN2   I   125   D9   I/C     30   GND    78   Do Not Connect   -   126   VCC      31   -DTR0   O   79   OUT2   O   127   GND      32   SYBRK0   I/O   80   OUT3   O   128   D10   I/O     34   RCLK0   I   82   D0   I/O   130   RS4   1 </td <td></td> <td></td> <td>-</td> <td>69</td> <td>ACK1</td> <td>I I</td> <td>117</td> <td>GND</td> <td>-</td>                                                                                                                                                |            |          | -    | 69         | ACK1           | I I  | 117        | GND            | -        |

| 24     NC     —     72     NC     —     120     —AS     I       25     NC     —     73     VCC     —     121     RD/–WR     I       26     -DSR0     I     74     CLK3     I     122     -CS     I       27     -CTS0     I     75     IN3     I     123     VCC     —       28     -RST0     O     76     CLK2     I     124     D8     I/O       29     TRNDT0     O     77     IN2     I     125     D9     I/O       30     GND     —     78     Do Not Connect     —     126     VCC     —       31     -DTR0     O     79     OUT2     O     127     GND     —       32     SYBRK0     I/O     80     OUT3     O     128     D10     I/O       34     RCLK0     I     82     D0     I/O     130     RS4     I <t< td=""><td></td><td>IRQ2</td><td>I I</td><td>70</td><td>IN1</td><td>1</td><td>118</td><td>-RESET</td><td>I</td></t<> |            | IRQ2     | I I  | 70         | IN1            | 1    | 118        | -RESET         | I        |

| 25     NC     —     73     VCC     —     121     RD/-WR     I       26     -DSR0     I     74     CLK3     I     122     -CS     I       27     -CTS0     I     75     IN3     I     123     VCC     -       28     -RST0     O     76     CLK2     I     124     D8     I/O       29     TRNDT0     O     77     IN2     I     125     D9     I/O       30     GND      78     Do Not Connect     -     126     VCC     -       31     -DTR0     O     79     OUT2     O     127     GND     -       32     SYBRK0     I/O     80     OUT3     O     128     D10     I/O       33     TxRDY0     O     81     GND     -     129     D11     I/O       34     RCLK0     I     82     D0     I/O     130     RS4     I <td>23</td> <td>IRQ1</td> <td>I.</td> <td>71</td> <td>CLK1</td> <td>1</td> <td>119</td> <td>CLOCK</td> <td>I.</td>    | 23         | IRQ1     | I.   | 71         | CLK1           | 1    | 119        | CLOCK          | I.       |

| 26     -DSR0     I     74     CLK3     I     122     -CS     I       27     -CTS0     I     75     IN3     I     123     VCC     -       28     -RST0     O     76     CLK2     I     124     D8     I/C       29     TRNDT0     O     77     IN2     I     125     D9     I/C       30     GND      78     Do Not Connect     -     126     VCC     -       31     -DTR0     O     79     OUT2     O     127     GND     -       32     SYBRK0     I/O     80     OUT3     O     128     D10     I/O       33     TxRDY0     O     81     GND     -     129     D11     I/O       34     RCLK0     I     82     D0     I/O     130     RS4     1       35     NC     -     83     D1     I/O     131     RS3     I                                                                                                                         |            | NC       | —    | 72         | NC             |      | 120        | -AS            | 1        |

| 27   -CTS0   I   75   IN3   I   123   VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25         | NC       |      |            | VCC            | -    | 121        | RD/-WR         |          |

| 28   -RST0   O   76   CLK2   I   124   D8   I/C     29   TRNDT0   O   77   IN2   I   125   D9   I/C     30   GND    78   Do Not Connect    126   VCC      31   -DTR0   O   79   OUT2   O   127   GND      32   SYBRK0   I/O   80   OUT3   O   128   D10   I/O     33   TxRDY0   O   81   GND    129   D11   I/O     34   RCLK0   I   82   D0   I/O   130   RS4   I     35   NC    83   D1   I/O   131   RS3   I     36   NC    84   NC    132   RS2   I     37   NC    85   NC    133   NC      38   NC    87   NC    135   RS0   I <td></td> <td></td> <td>I I</td> <td>74</td> <td>CLK3</td> <td>I I</td> <td>122</td> <td>-CS</td> <td>1</td>                                                                                                                                                                                            |            |          | I I  | 74         | CLK3           | I I  | 122        | -CS            | 1        |

| 29   TRNDT0   O   77   IN2   I   125   D9   I/O     30   GND    78   Do Not Connect    126   VCC      31   -DTR0   O   79   OUT2   O   127   GND      32   SYBRK0   I/O   80   OUT3   O   128   D10   I/O     33   TxRDY0   O   81   GND    129   D11   I/O     34   RCLK0   I   82   D0   I/O   130   RS4   I     35   NC    83   D1   I/O   131   RS3   I     36   NC    84   NC    132   RS2   I     37   NC    85   NC    133   NC      38   NC    87   NC    134   RS1   I     39   NC    87   NC    135   RS0   I                                                                                                                                                                                                                                                                                                                     | 27         | -CTS0    | I I  | 75         | IN3            | 1    | 123        | VCC            | _        |

| 30   GND    78   Do Not Connect    126   VCC      31   -DTR0   0   79   OUT2   0   127   GND      32   SYBRK0   I/O   80   OUT3   0   128   D10   I/O     33   TxRDY0   0   81   GND    129   D11   I/O     34   RCLK0   I   82   D0   I/O   130   RS4   I     35   NC    83   D1   I/O   131   RS3   I     36   NC    84   NC    132   RS2   I     37   NC    85   NC    133   NC      38   NC    86   NC    134   RS1   I     39   NC    87   NC    135   RS0   I     40   RCVDT0   I   89   D3   I/O   137   D13   I/O<                                                                                                                                                                                                                                                                                                                  |            |          | -    | 76         | CLK2           | I I  | 124        | D8             | I/O      |

| 31     -DTR0     O     79     OUT2     O     127     GND        32     SYBRK0     I/O     80     OUT3     O     128     D10     I/O       33     TXRDY0     O     81     GND      129     D11     I/O       34     RCLK0     I     82     D0     I/O     130     RS4     1       35     NC      83     D1     I/O     131     RS3     I       36     NC      83     D1     I/O     131     RS3     I       37     NC      85     NC      133     NC        38     NC     -     86     NC      134     RS1     I       40     RCVDT0     I     88     D2     I/O     136     D12     I/O       41     -TCLK0     I     89     D3     I/O     137     D13     I/O                                                                                                                                                                             |            |          | 0    |            | IN2            | I I  |            |                | I/O      |

| 32     SYBRK0     I/O     80     OUT3     O     128     D10     I/O       33     TxRDY0     O     81     GND     -     129     D11     I/O       34     RCLK0     I     82     D0     I/O     130     RS4     1       35     NC      83     D1     I/O     131     RS3     I       36     NC      84     NC      132     RS2     I       37     NC      85     NC      133     NC        38     NC      86     NC      134     RS1     I       39     NC      87     NC      135     RS0     I       40     RCVDT0     I     88     D2     I/O     136     D12     I/O       41     -TCLK0     I     89     D3     I/O     137     D13     I/O                                                                                                                                                                                              | 30         |          |      | 78         | Do Not Connect |      | 126        | VCC            | —        |

| 33   TXRDY0   O   81   GND    129   D11   I/O     34   RCLK0   I   82   D0   I/O   130   RS4   I     35   NC    83   D1   I/O   131   RS3   I     36   NC    84   NC    132   RS2   I     37   NC    85   NC    133   NC      38   NC    86   NC    135   RS0   I     40   RCVDT0   I   88   D2   I/O   136   D12   I/O     41   -TCLK0   I   89   D3   I/O   137   D13   I/O     42   TXEMP0   O   90   VCC    138   GND      43   RXRDY0   O   91   GND    139   D14   I/O     44   RXRDY1   O   92   D4   I/O   140   D15   I/O                                                                                                                                                                                                                                                                                                          |            |          |      |            |                |      | 127        | GND            | _        |

| 34   RCLK0   I   82   D0   I/O   130   RS4   I     35   NC    83   D1   I/O   131   RS3   I     36   NC    84   NC    132   RS2   I     37   NC    85   NC    133   NC      38   NC    86   NC    134   RS1   I     39   NC    87   NC    135   RS0   I     40   RCVDT0   I   88   D2   I/O   136   D12   I/O     41   -TCLK0   I   89   D3   I/O   137   D13   I/O     42   TXEMP0   O   90   VCC    138   GND      43   RXRDY0   O   91   GND    139   D14   I/O     44   RXRDY1   O   92   D4   I/O   140   D15   I/O                                                                                                                                                                                                                                                                                                                    | 32         | SYBRK0   | I/O  | 80         | OUT3           | 0    | 128        | D10            | I/O      |

| 35   NC    83   D1   I/O   131   RS3   I     36   NC    84   NC    132   RS2   I     37   NC    85   NC    133   NC      38   NC    86   NC    134   RS1   I     39   NC    87   NC    135   RS0   I     40   RCVDT0   I   88   D2   I/O   136   D12   I/O     41   -TCLK0   I   89   D3   I/O   137   D13   I/O     42   TXEMP0   O   90   VCC    138   GND      43   RxRDY0   O   91   GND    139   D14   I/O     44   RxRDY1   O   92   D4   I/O   140   D15   I/O                                                                                                                                                                                                                                                                                                                                                                       | 33         |          | 0    | 81         | GND            |      | 129        | D11            | I/O      |

| 36   NC    84   NC    132   RS2   1     37   NC    85   NC    133   NC      38   NC    86   NC    134   RS1   1     39   NC    87   NC    135   RS0   1     40   RCVDT0   I   88   D2   I/O   136   D12   I/O     41   -TCLK0   I   89   D3   I/O   137   D13   I/O     42   TXEMP0   O   90   VCC    138   GND      43   RXRDY0   O   91   GND    139   D14   I/O     44   RXRDY1   O   92   D4   I/O   140   D15   I/O                                                                                                                                                                                                                                                                                                                                                                                                                    |            |          | I    |            |                |      | 130        | RS4            | 1        |

| 37 NC  85 NC  133 NC    38 NC  86 NC  134 RS1 1   39 NC  87 NC  135 RS0 1   40 RCVDT0 I 88 D2 I/O 136 D12 I/O   41 -TCLK0 I 89 D3 I/O 137 D13 I/O   42 TXEMP0 O 90 VCC  138 GND    43 RXRDY0 O 91 GND  139 D14 I/O   44 RXRDY1 O 92 D4 I/O 140 D15 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |          |      |            |                | I/O  |            |                | I        |

| 38     NC     —     86     NC     —     134     RS1     I       39     NC     —     87     NC     —     135     RS0     I       40     RCVDT0     I     88     D2     I/O     136     D12     I/O       41     —TCLK0     I     89     D3     I/O     137     D13     I/O       42     TXEMP0     O     90     VCC     —     138     GND     —       43     RXRDY0     O     91     GND     —     139     D14     I/O       44     RXRDY1     O     92     D4     I/O     140     D15     I/O                                                                                                                                                                                                                                                                                                                                               |            |          | -    |            |                | —    | 132        | RS2            | T        |

| 39     NC      135     RS0     I       40     RCVDT0     I     88     D2     I/O     136     D12     I/O       41     -TCLK0     I     89     D3     I/O     137     D13     I/O       42     TXEMP0     O     90     VCC      138     GND        43     RXRDY0     O     91     GND      139     D14     I/O       44     RXRDY1     O     92     D4     I/O     140     D15     I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |          | -    | 85         |                | —    |            |                |          |

| 40     RCVDT0     I     88     D2     I/O     136     D12     I/O       41     -TCLK0     I     89     D3     I/O     137     D13     I/O       42     TXEMP0     O     90     VCC      138     GND        43     RXRDY0     O     91     GND      139     D14     I/O       44     RXRDY1     O     92     D4     I/O     140     D15     I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |          | -    |            |                | -    |            |                | -        |

| 41     -TCLK0     I     89     D3     I/O     137     D13     I/O       42     TXEMP0     O     90     VCC      138     GND        43     RxRDY0     O     91     GND      139     D14     I/O       44     RxRDY1     O     92     D4     I/O     140     D15     I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |          | —    |            |                |      |            |                |          |

| 42     TXEMP0     O     90     VCC     —     138     GND     —       43     RxRDY0     O     91     GND     —     139     D14     I/C       44     RxRDY1     O     92     D4     I/O     140     D15     I/C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |          | I    | 88         |                | I/O  | 136        | D12            | I/O      |

| 43 RxRDY0 O 91 GND 139 D14 1/0<br>44 RxRDY1 O 92 D4 1/0 140 D15 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |          |      | 89         |                | I/O  | 137        | D13            | I/O      |

| 44 RxRDY1 O 92 D4 I/O 140 D15 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |          |      | 90         | VCC            | -    | 138        | GND            | _        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |          |      |            |                |      |            |                | I/O      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |          | 0    |            |                |      |            |                | I/O      |

| 45 GND — 93 D5 1/O 141 IRQ15 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |          | —    |            |                | I/O  |            |                | I        |

| 46 TxEMP1 O 94 NC 142 IRQ14 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |          | 0    |            |                |      |            |                | 1        |

| 47 NC - 95 NC - 143 IRQ13 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |          |      |            |                | -    |            |                |          |

| 48 -TCLK1 I 96 NC - 144 IRQ12 I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48         | -TCLK1   | 1    | 96         | NC             | -    | 144        | IRQ12          | <u> </u> |

FUJITSU

MB86940CPR-G

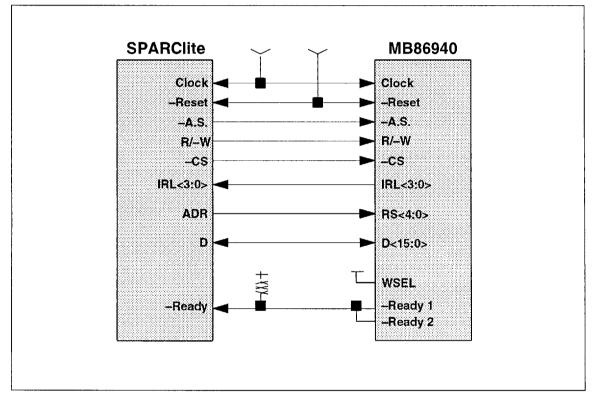

| Name                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

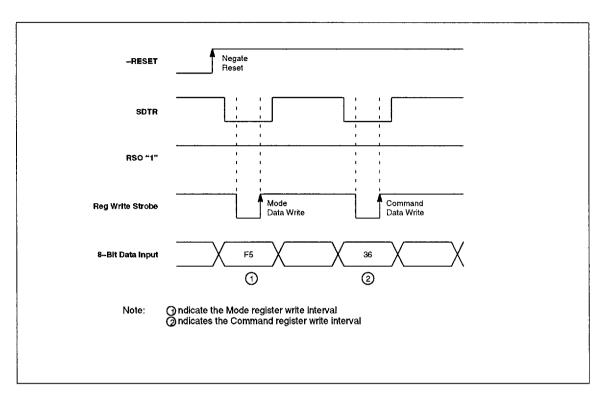

| -RESET               | I    | Reset input signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

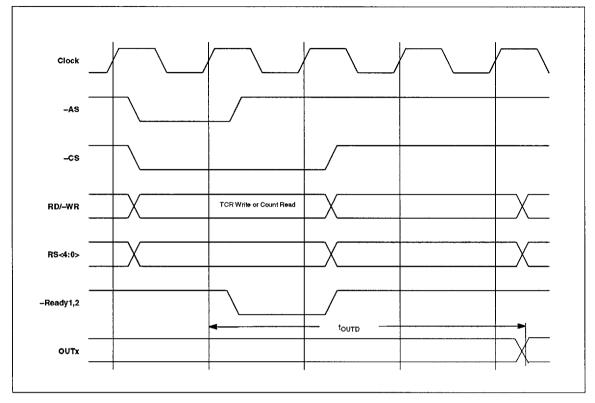

| SYSTEM<br>CLOCK      | I    | System clock signal. Internal logic uses a clock derived from this clock signal, but at half the frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

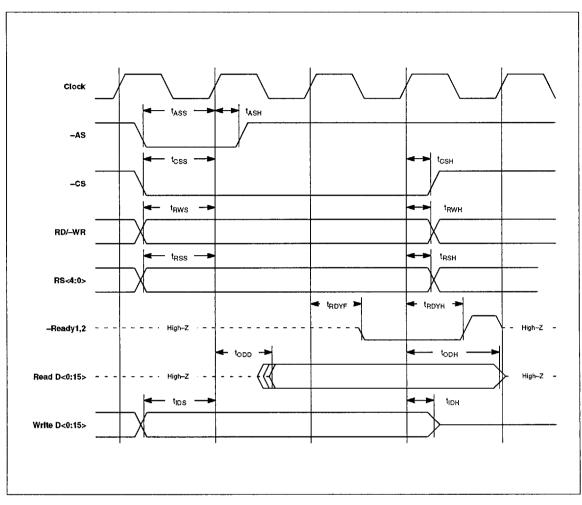

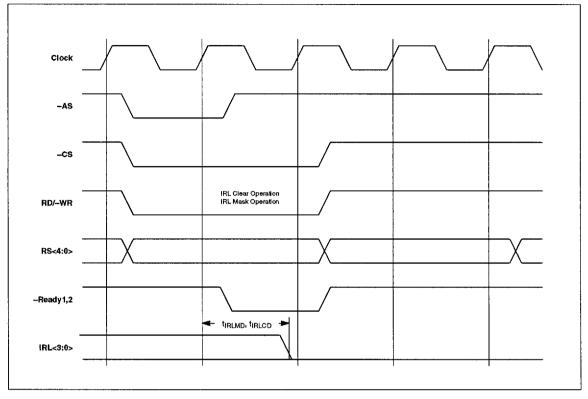

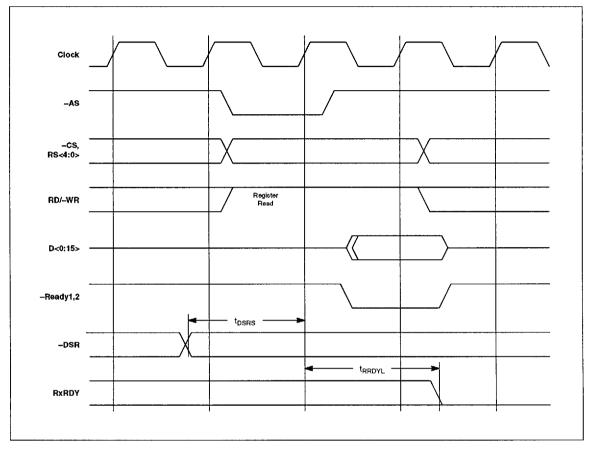

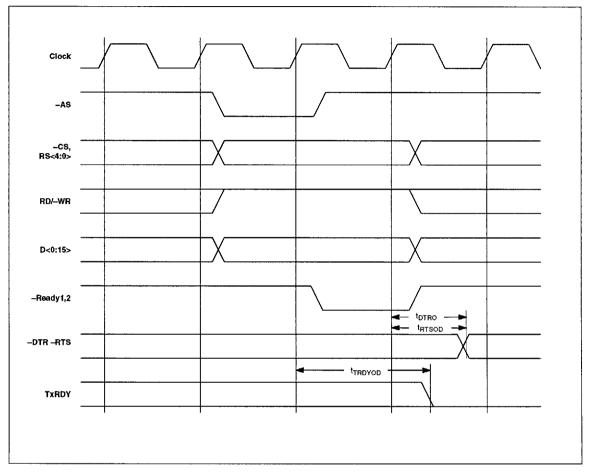

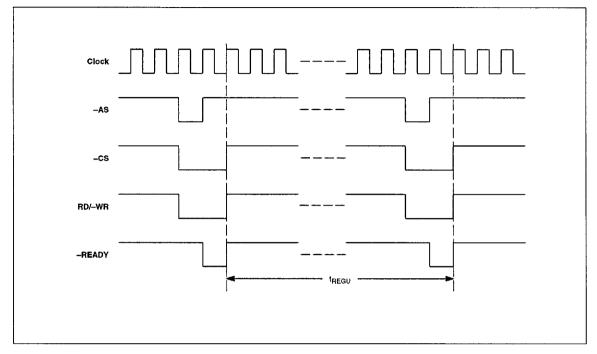

| -AS                  | I    | Address Strobe. The register to be accessed is determined by the states of RS<4:0>, $-CS$ , and $-RD/WR$ while $-AS$ is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RD/WR                | I    | Read/Write. Identifies an operations is a read when high, and as a write when low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -CS                  | I    | Chip select signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

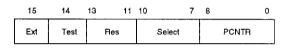

| RS<4:0>              | 1    | Register Select. A bus used to select an MB86940 register that is to be read or written.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -READY 1<br>-READY 2 | 0    | Ready. The READY1 and READY2 signals are identical ready signals that are available on two<br>pins for drive purposes. The MB86940 asserts ready during write operations to indicate that it<br>has received data that is written by the processor, and asserts ready during read operations to<br>indicate that it has asserted data that is to be read by the processor onto the data bus. The<br>signals are not used if the internal ready is used by programming the processor for wait states.<br>Both signals are open drain outputs capable of 12mA low–level drive. The signals are driven<br>high for approximately 3ns before transitioning to high impedance. |

| D<15:0>              | 1/0  | Data Bus. The bus used to transfer data between the MB86940 and the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IRL<3:0>             | 0    | Interrupt Request Level. A bus used to interrupt the processor when an interrupt occurs, and to identify the highest-level pending interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WSEL                 | 1    | Wait Select. Selects two wait states (three-cycle access) when tied low, and one wait state (two-cycle access) when tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### MPU Interface Signal Descriptions

# Interrupt Request Signal Descriptions

| Name      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

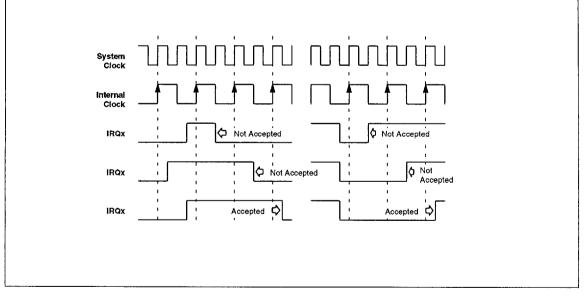

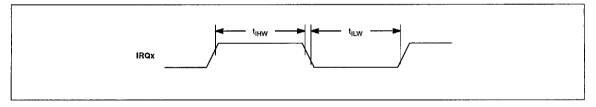

| IRQ<15:1> | I    | Interrupt Request. These are prioritized system interrupt requests. IRQ15 has the highest priority, and IRQ1 the lowest.<br>The triggerfor each interrupt can be programmed for a high level, a low level, a rising edge, or a falling edge. The level-trigger interrupt request signals are sampled during three successive internal clock periods to minimize false interrupts. |

#### **Timer Signal Descriptions**

| Name                                       | Туре | Description                                                                                                                                                                                                                                            |

|--------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

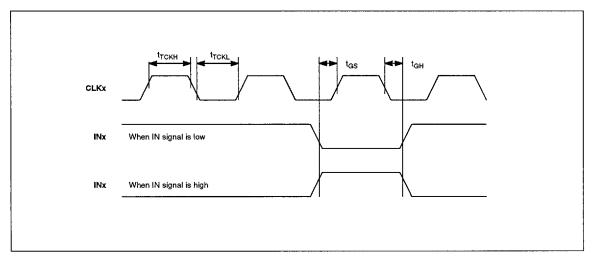

| CLK<3:0>1                                  | 1    | Timer external clock input. In the external clock mode, this signal is synchronized with the internal clock before use.                                                                                                                                |

| OUT<3:0> <sup>2</sup>                      | 0    | Timer output pin. According to the mode, the output wave functions as<br>(1) periodic interrupt signal output;<br>(2) square wave output;<br>(3) one–shot pulse output.                                                                                |

| IN<3:0> <sup>†</sup>                       | I    | Count control input. These inputs are used as gate signals in Modes 0 to 3, and as external triggers in Mode 4.                                                                                                                                        |

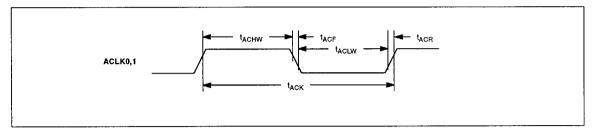

| ACK0<br>ACK1                               | 1    | Asynchronous clock. These are prescaler input clocks that are used when selected in the Prescaler registers. The clocks are synchronized with the internal clock and are divided and output to the PRSCKx pin. When not used, they should be tied low. |

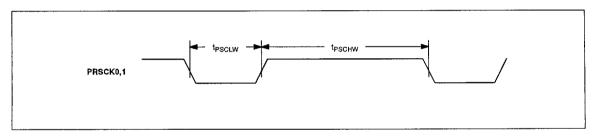

| PRSCK0 <sup>‡</sup><br>PRSCK1 <sup>‡</sup> | 0    | Prescaler output.                                                                                                                                                                                                                                      |

1. When not being used, these pins should tied high or low.

2. These pins will be low during reset.

#### **SDTR Signal Descriptions**

| Name             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSR0<br>DSR1     | 1    | Modem Data Set Ready signal. The status of these pins is loaded into bit 7 of the corresponding SDTR status register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RTS0<br>RTS1     | 0    | Modem Request to Send signal. When bit 5 of the command register is set to 1, these signals are driven low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| –DTR0<br>–DTR1   | 0    | Modem Data Terminal Ready or Rate Select signal. When bit 1 of the command register is set to 1, these signals are driven low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CTS0<br>CTS1     | 1    | Modem Clear to Send signal. A transmitter is enabled only when its corresponding -CTSx signal is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

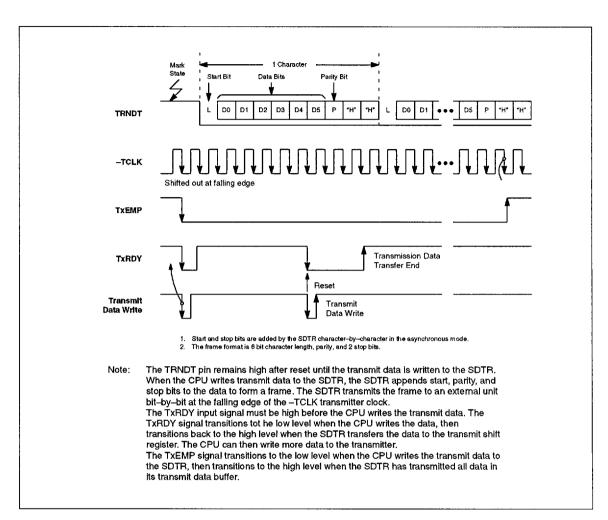

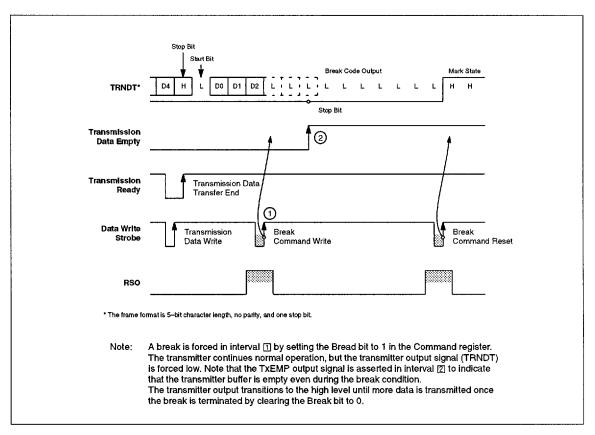

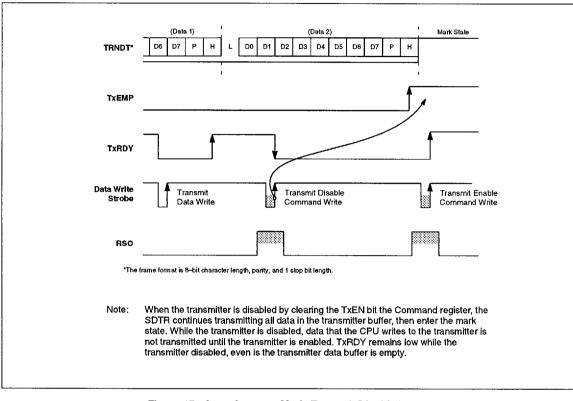

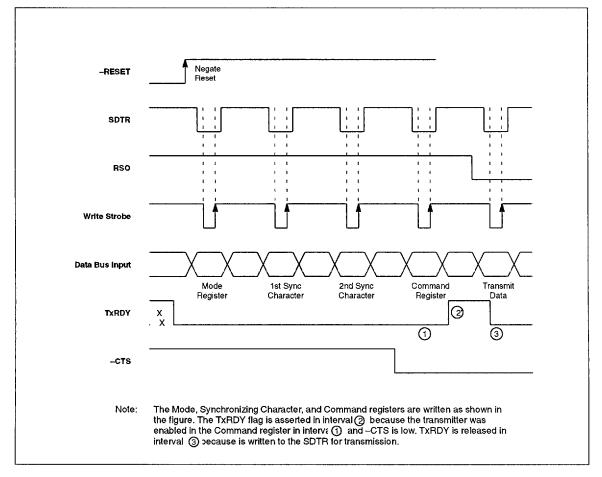

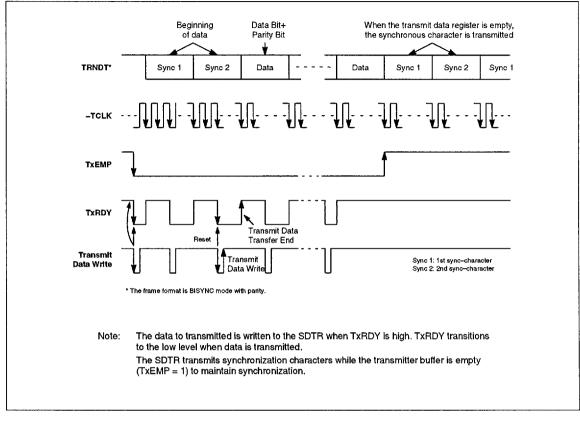

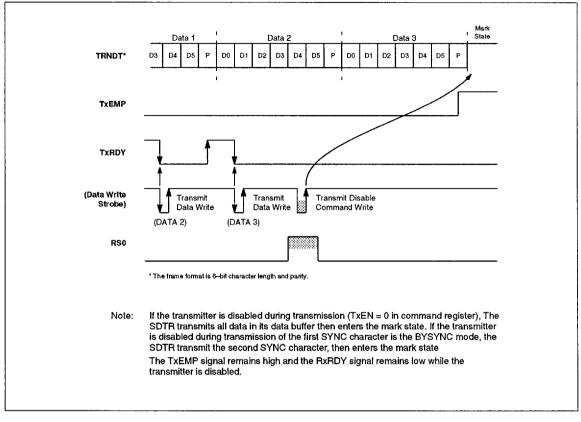

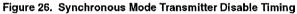

| TRNDT0<br>TRNDT1 | 0    | Serial transmit data. Parallel data written in the data register is converted into serial data, then transmitted through these pins.<br>In the asynchronous mode, start and stop bits are added to data, and a parity bit can be added.<br>If there is no data to be transmitted, the SDTR transmits synchronous characters in the synchronous mode, and enters the mark state in the asynchronous mode. The mark state also occurs after a transmit disable command is specified (bit 0 of the command register is set to 0) or when -CTS is High. Note that the mark state occurs during transmission after:<br>(1) One byte is transmitted if a transmit disable command is specified (bit 0 of the command register) set to 0) or when whether the synchronous character is transmitted if the first synchronous character was transmitted (with the synchronous state held) in the BISYNC mode. |

| TxEMP0<br>TxEMP1 | 0    | These signals are driven high if there is no data to be transmitted in the SDTR. These signals are driven low at the falling edge of the write signal when the processor writes a byte to be transmitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TxRDY0<br>TxRDY1 | 0    | These signals are driven low if the transmit data buffer register becomes empty with the $-CTS$ pin low and the transmitter is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Name             | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

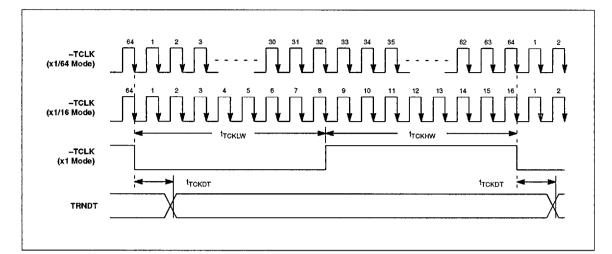

| -TCLK0<br>-TCLK1 | I    | Clock for determining the transmission baud rate.<br>In the synchronous mode, since the baud rate is fixed at transmit clock x 1, the frequency of the clock to be input to the $-TCLK$ pin is the transmission baud rate.<br>In the asynchronous mode, the transmit clock x 1/16 and x 1/64 frequencies will be the transmission baud rate in accordance with the baud rate set in the mode register. For example, if a clock of 19.2 kHz is input to the $-TCLK$ pin, the transmission baud rate is 1200 baud at x 1/16, and 300 baud at x 1/64. The transmit data is synchronized with the falling edge of this transmit clock.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

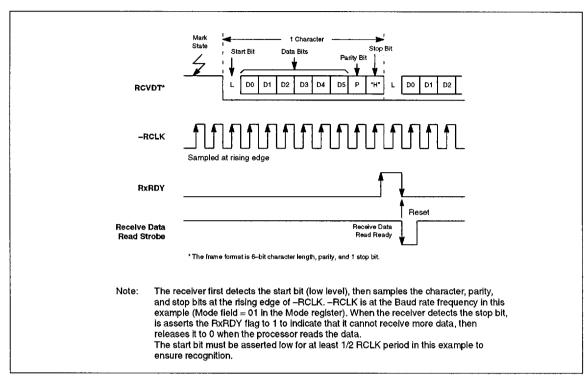

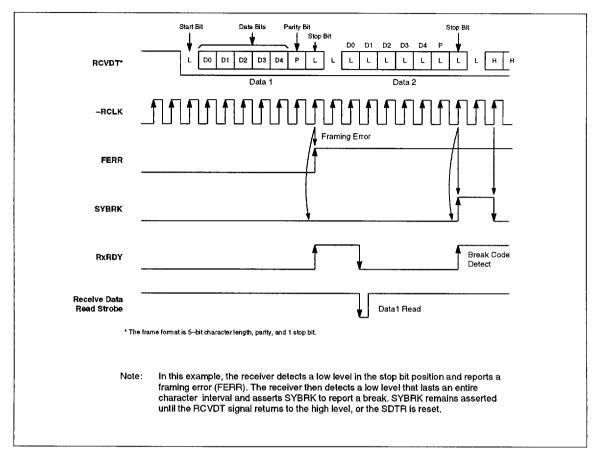

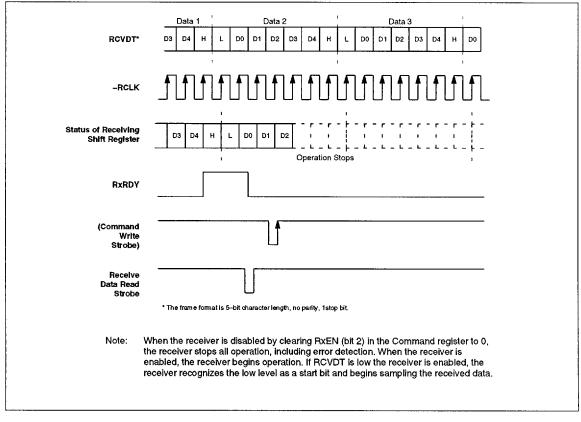

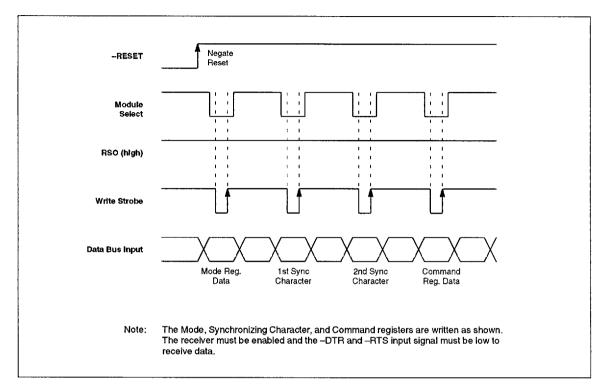

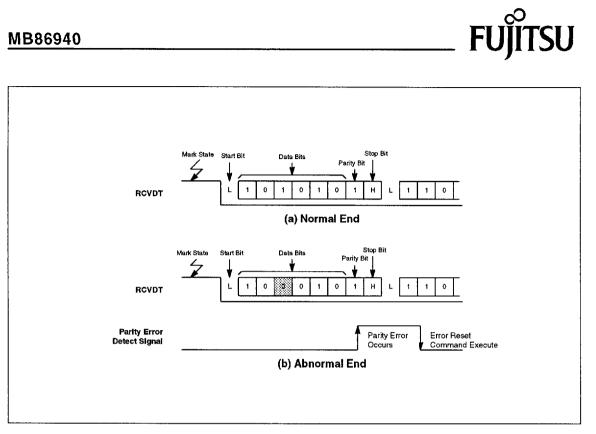

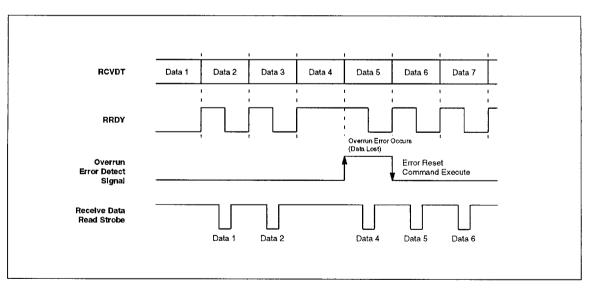

| RCVDT0<br>RCVDT1 | I    | Serial receive data input. The input data is converted to parallel data in the SDTR and can be read via the system data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

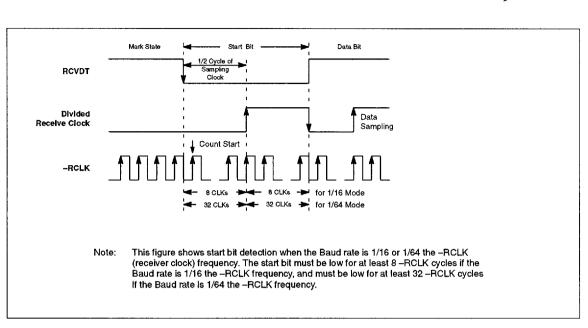

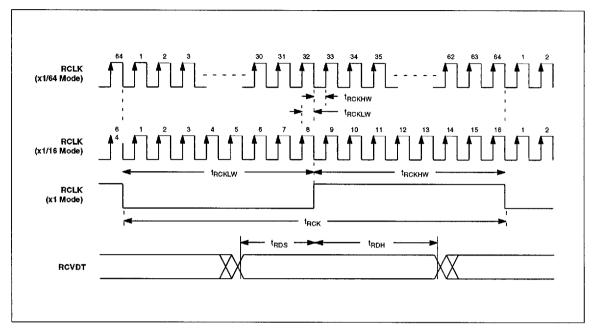

| RCLK0<br>RCLK1   | I    | Clock for determining the receive baud rate. In the synchronous mode, since the baud rate is fixed at receive clock x 1, the frequency of the clock to be input to the RCLK pin is the receive baud rate. In the asynchronous mode, the receive clock x 1/16 and x 1/64 frequencies will be the receive baud rate in accordance with the baud rate set in the mode register. For example, if a clock of 19.2 kHz is input to the RCLK pin, the receive baud rate is 1200 baud at x 1/16, and 300 baud at x 1/64. The receive data is sampled at the falling edge of this receive clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |