# MSP430x1xx Family

# User's Guide

*2000*

**Mixed Signal Products**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

### Preface

### Read This First

#### About This Manual

The MSP430x1xx User's Guide is intended to assist the development of MSP430x1xx family products by assembling together and presenting hardware and software information in a manner that is easy for engineers and programmers to use.

This manual discusses modules and peripherals of the MSP430x1xx family of devices. Each discussion presents the module or peripheral in a general sense. Not all features and functions of all modules or peripherals are present on all devices. In addition, modules or peripherals may differ in their exact implementation between device families, or may not be fully implemented on an individual device or device family. Therefore, a user must always consult the data sheet of any device of interest to determine what peripherals and modules are implemented, and exactly how they are implemented on that particular device.

### How to Use This Manual

This document contains the following chapters:

Chapter 1 – Introduction Chapter 2 – Architectural Overview Chapter 3 – System Resets, Interrupts, and Operating Modes Chapter 4 – Memory Chapter 5 – 16-Bit CPU Chapter 6 – Hardware Multiplier Chapter 7 – Basic Clock Module Chapter 7 – Basic Clock Module Chapter 8 – Digital I/O Configuration Chapter 9 – Watchdog Timer Chapter 10 – Timer\_A Chapter 11 – Timer\_B Chapter 12 – USART Peripheral Interface, UART Mode Chapter 13 – USART Peripheral Interface, SPI Mode Chapter 14 – Comparator\_A Chapter 15 – ADC12 Appendix A – Peripheral File Map Appendix B – Instruction Set Description Appendix C – Flash Memory

#### **Notational Conventions**

This document uses the following conventions.

Program listings, program examples, and interactive displays are shown in a special typeface similar to a typewriter's.

Here is a sample program listing:

| 0011 | 0005 | 0001 | .field | 1, | 2 |

|------|------|------|--------|----|---|

| 0012 | 0005 | 0003 | .field | 3, | 4 |

| 0013 | 0005 | 0006 | .field | б, | 3 |

| 0014 | 0006 |      | .even  |    |   |

### **Related Documentation From Texas Instruments**

For related documentation see the web site http://www.ti.com/sc/msp430.

#### FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

### Contents

| 1 | Intro | duction                                                              | 1-1 |

|---|-------|----------------------------------------------------------------------|-----|

|   | 1.1   | Features and Capabilities                                            | 1-2 |

|   | 1.2   | 11x Devices                                                          | 1-3 |

|   | 1.3   | 11x1 Devices                                                         | 1-3 |

|   | 1.4   | 13x Devices                                                          | 1-4 |

|   | 1.5   | 14x Devices                                                          | 1-4 |

| 2 | Arch  | tectural Overview                                                    |     |

|   | 2.1   | Introduction                                                         | 2-2 |

|   | 2.2   | Central Processing Unit                                              |     |

|   | 2.3   | Program Memory                                                       | 2-3 |

|   | 2.4   | Data Memory                                                          |     |

|   | 2.5   | Operation Control                                                    |     |

|   | 2.6   | Peripherals                                                          | 2-4 |

|   | 2.7   | Oscillator and Clock Generator                                       | 2-4 |

| 3 | Syste | em Resets, Interrupts, and Operating Modes                           | 3-1 |

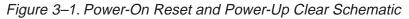

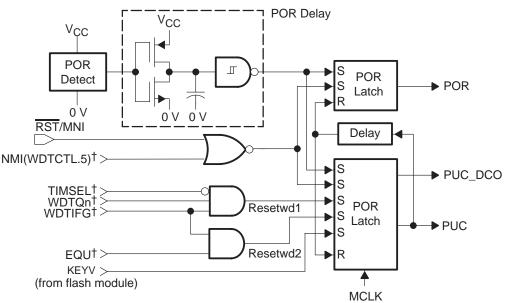

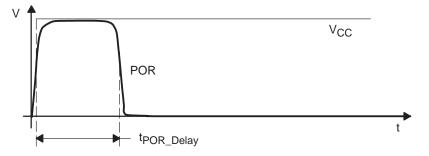

|   | 3.1   | System Reset and Initialization                                      | 3-2 |

|   |       | 3.1.1 Introduction                                                   |     |

|   |       | 3.1.2 Device Initialization After System Reset                       |     |

|   | 3.2   | Global Interrupt Structure                                           |     |

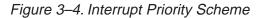

|   | 3.3   | MSP430 Interrupt-Priority Scheme                                     |     |

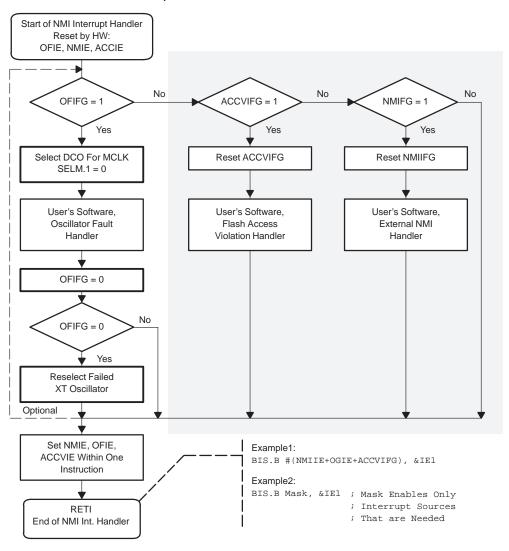

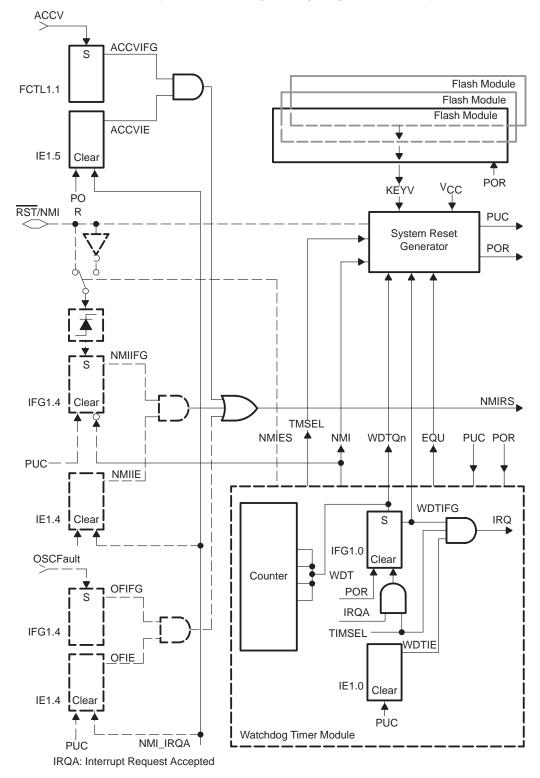

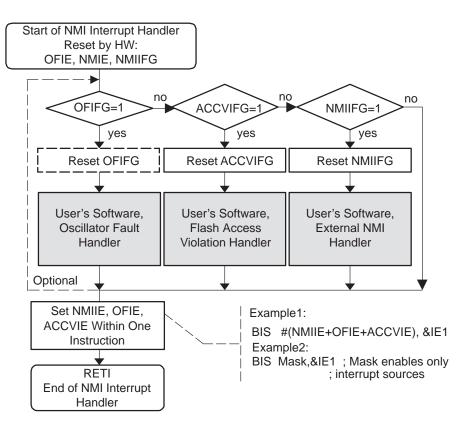

|   |       | 3.3.1 Operation of Global Interrupt—Reset/NMI                        | 3-8 |

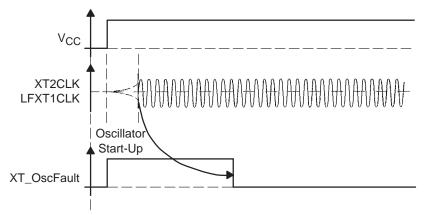

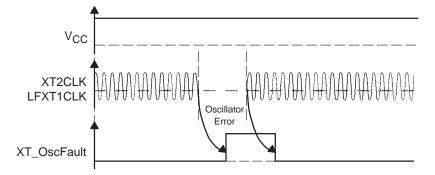

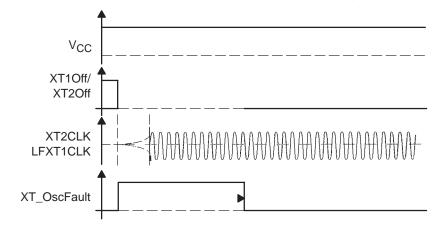

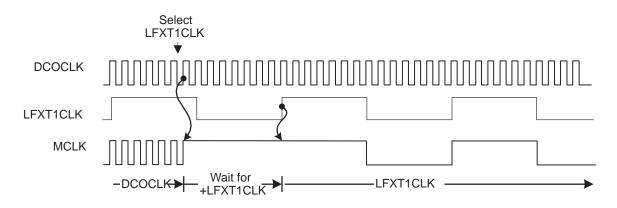

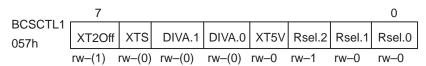

|   |       | 3.3.2 Operation of Global Interrupt—Oscillator Fault Control         | 3-9 |

|   | 3.4   | Interrupt Processing                                                 | 3-9 |

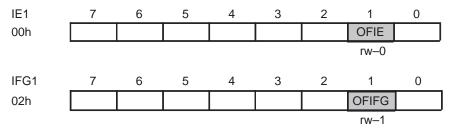

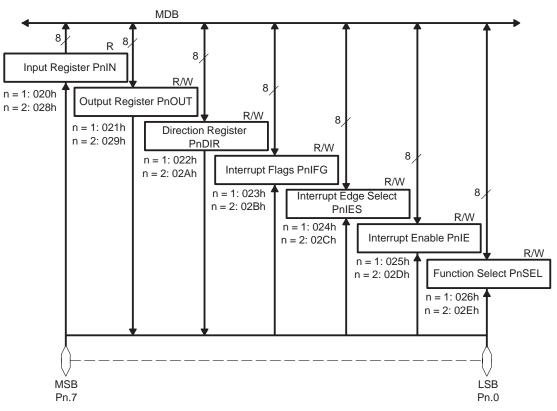

|   |       | 3.4.1 Interrupt Control Bits in Special-Function Registers (SFRs) 3- | -11 |

|   |       | 3.4.2 Interrupt Vector Addresses 3-                                  | ·15 |

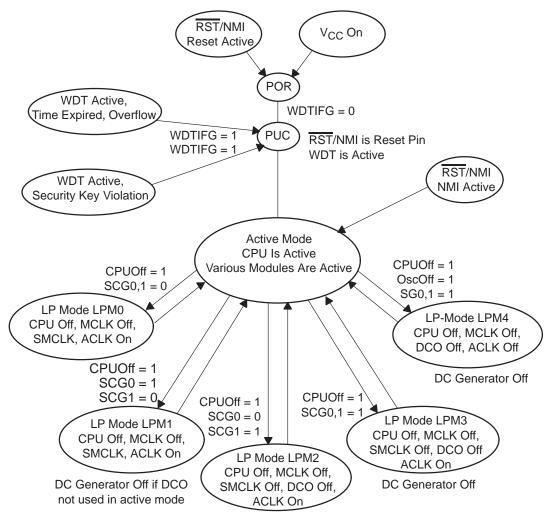

|   | 3.5   | Operating Modes 3-                                                   |     |

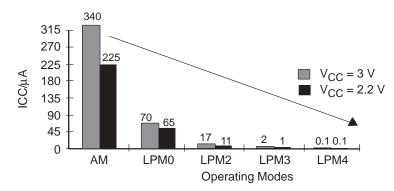

|   |       | 3.5.1 Low-Power Mode 0 and 1 (LPM0 and LPM1) 3-                      |     |

|   |       | 3.5.2 Low-Power Modes 2 and 3 (LPM2 and LPM3) 3-                     |     |

|   |       | 3.5.3 Low-Power Mode 4 (LPM4) 3-                                     |     |

|   | 3.6   | Basic Hints for Low-Power Applications 3-                            | ·22 |

| 4 |       | ory 4                                                                |     |

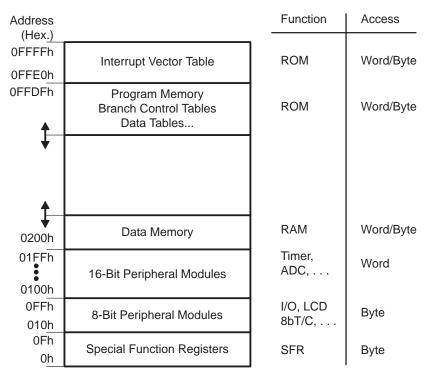

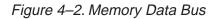

|   | 4.1   | Introduction                                                         |     |

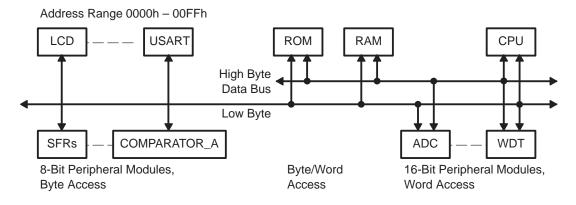

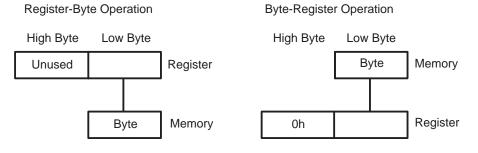

|   | 4.2   | Data in the Memory                                                   |     |

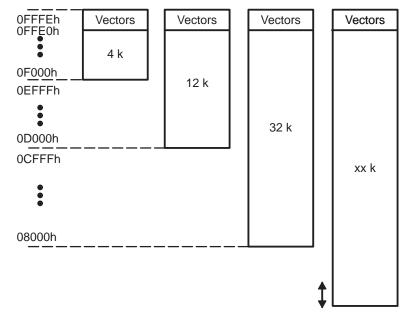

|   | 4.3   | Internal ROM Organization                                            |     |

|   |       | 4.3.1 Processing of ROM Tables 4                                     |     |

|   |       | 4.3.2 Computed Branches and Calls                                    | 4-5 |

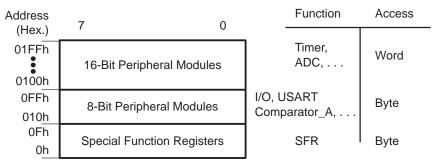

|        | 4.4                                                     | RAM a                                                                                                                                                                              | and Peripheral Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-6                                                                                                                                                                                                                                                                                                                                               |

|--------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                         | 4.4.1                                                                                                                                                                              | Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-6                                                                                                                                                                                                                                                                                                                                               |

|        |                                                         | 4.4.2                                                                                                                                                                              | Peripheral Modules—Address Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-8                                                                                                                                                                                                                                                                                                                                               |

|        |                                                         | 4.4.3                                                                                                                                                                              | Peripheral Modules—Special Function Registers (SFRs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-10                                                                                                                                                                                                                                                                                                                                              |

| 5      | 16-Bi                                                   | t CPU                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-1                                                                                                                                                                                                                                                                                                                                               |

| -      | 5.1                                                     | CPU R                                                                                                                                                                              | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-2                                                                                                                                                                                                                                                                                                                                               |

|        | -                                                       | 5.1.1                                                                                                                                                                              | The Program Counter (PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   |

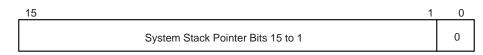

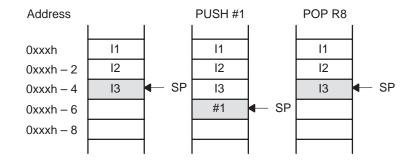

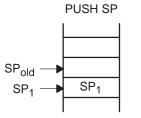

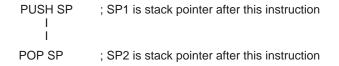

|        |                                                         | 5.1.2                                                                                                                                                                              | The System Stack Pointer (SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                   |

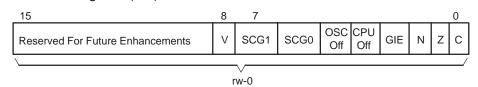

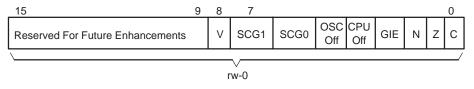

|        |                                                         | 5.1.3                                                                                                                                                                              | The Status Register (SR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   |

|        |                                                         | 5.1.4                                                                                                                                                                              | The Constant Generator Registers CG1 and CG2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                   |

|        | 5.2                                                     | Addres                                                                                                                                                                             | ssing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                   |

|        |                                                         | 5.2.1                                                                                                                                                                              | Register Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                   |

|        |                                                         | 5.2.2                                                                                                                                                                              | Indexed Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                   |

|        |                                                         | 5.2.3                                                                                                                                                                              | Symbolic Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-10                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.2.4                                                                                                                                                                              | Absolute Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-11                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.2.5                                                                                                                                                                              | Indirect Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-12                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.2.6                                                                                                                                                                              | Indirect Autoincrement Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-13                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.2.7                                                                                                                                                                              | Immediate Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-14                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.2.8                                                                                                                                                                              | Clock Cycles, Length of Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-15                                                                                                                                                                                                                                                                                                                                              |

|        | 5.3                                                     | Instruc                                                                                                                                                                            | tion Set Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-17                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.3.1                                                                                                                                                                              | Double-Operand Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-18                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.3.2                                                                                                                                                                              | Single-Operand Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-19                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.3.3                                                                                                                                                                              | Conditional Jumps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-20                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.3.4                                                                                                                                                                              | Short Form of Emulated Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-21                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         | 5.3.5                                                                                                                                                                              | Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-22                                                                                                                                                                                                                                                                                                                                              |

|        |                                                         |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                   |

|        | 5.4                                                     | Instruc                                                                                                                                                                            | tion Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-23                                                                                                                                                                                                                                                                                                                                              |

| 6      |                                                         |                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                   |

| 6      |                                                         | ware Mu                                                                                                                                                                            | ultiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-1                                                                                                                                                                                                                                                                                                                                               |

| 6      | <b>Hard</b><br>6.1                                      | <b>ware M</b> u<br>Hardw                                                                                                                                                           | ultiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>6-1</b><br>6-2                                                                                                                                                                                                                                                                                                                                 |

| 6      | Hard                                                    | <b>ware M</b> u<br>Hardw                                                                                                                                                           | ultiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-1<br>6-2<br>6-3                                                                                                                                                                                                                                                                                                                                 |

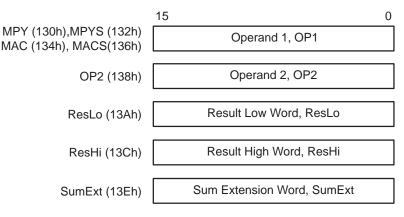

| 6      | <b>Hard</b><br>6.1                                      | <b>ware Mu</b><br>Hardw<br>Hardw                                                                                                                                                   | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-1<br>6-2<br>6-3<br>6-5                                                                                                                                                                                                                                                                                                                          |

| 6      | <b>Hard</b><br>6.1                                      | ware Mu<br>Hardw<br>Hardw<br>6.2.1                                                                                                                                                 | ultipliervare Multiplier Module Supportvare Multiplier OperationMultiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bitMultiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-1<br>6-2<br>6-3<br>6-5<br>6-6                                                                                                                                                                                                                                                                                                                   |

| 6      | <b>Hard</b><br>6.1                                      | ware Mu<br>Hardw<br>Hardw<br>6.2.1<br>6.2.2                                                                                                                                        | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Unsigned and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-1            6-2            6-3            6-5            6-6            6-7                                                                                                                                                                                                                                                                    |

| 6      | <b>Hard</b><br>6.1                                      | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                               | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-1            6-2            6-3            6-5            6-6            6-7            6-8                                                                                                                                                                                                                                                     |

| 6      | <b>Hard</b><br>6.1<br>6.2                               | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw                                                                                                                      | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Unsigned and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-1            6-2            6-3            6-5            6-6            6-6            6-7            6-8            6-9                                                                                                                                                                                                                       |

| 6      | <b>Hard</b><br>6.1<br>6.2<br>6.3                        | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw                                                                                                             | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Unsigned and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits                                                                                                                                                                                                                                                                                                                                                                                                     | 6-1            6-2            6-3            6-5            6-6            6-7            6-8            6-9            6-10                                                                                                                                                                                                                      |

| 6      | Hard<br>6.1<br>6.2<br>6.3<br>6.4                        | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw                                                                                                             | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-1            6-2            6-3            6-5            6-6            6-7            6-8            6-9            6-10            6-10                                                                                                                                                                                                      |

| 6      | Hard<br>6.1<br>6.2<br>6.3<br>6.4                        | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw                                                                                                    | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Unsigned and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions                                                                                                                                                                                                                                                                                           | 6-1            6-2            6-3            6-5            6-6            6-7            6-8            6-9            6-10            6-10            6-10                                                                                                                                                                                      |

| 6      | Hard<br>6.1<br>6.2<br>6.3<br>6.4                        | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw<br>6.5.1                                                                                           | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-1            6-2            6-3            6-5            6-6            6-7            6-8            6-9            6-10            6-10            6-10            6-10                                                                                                                                                                      |

|        | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                 | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3                                                                                  | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—Interrupt Routines         Hardware Multiplier Software Restrictions—MACS                                                                                                                                                    | 6-1            6-2            6-3            6-5            6-6            6-7            6-8            6-9            6-10            6-10            6-11            6-12                                                                                                                                                                      |

| 6<br>7 | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                 | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3<br><b>Clock</b>                                                                  | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—MACS         Multiplier Software Restrictions                                                                                                                                                                                                                                                               | 6-1<br>6-2<br>6-3<br>6-3<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-10<br>6-10<br>6-10<br>6-11<br>6-12<br>6-12<br>7-1                                                                                                                                                                                                                                |

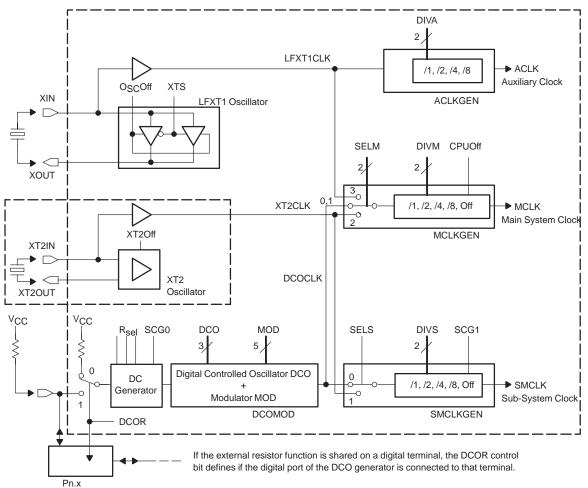

|        | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Basic<br>7.1 | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3<br><b>Clock</b><br>Basic (                                              | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Unsigned and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—MACS         Module                                                                                                                                                                                                        | 6-1            6-3            6-5            6-6            6-7            6-7            6-7            6-7            6-7            6-7            6-7            6-7            6-10            6-10            6-10            6-11            6-12            7-1                                                                           |

|        | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Basic        | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3<br><b>Clock</b><br>Basic (                                              | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—MACS         Module         Clock Module         and XT2 Oscillators                                                                                                                                                         | 6-1            6-2            6-3            6-5            6-6            6-7            6-7            6-7            6-7            6-7            6-7            6-9            6-10            6-10            6-10            6-11            6-12            7-12            7-2            7-4                                            |

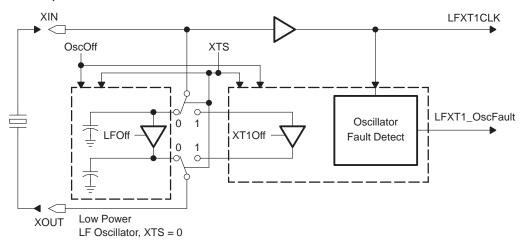

|        | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Basic<br>7.1 | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3<br><b>Clock</b><br>Basic 0<br>LFXT1                                     | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—MACS         Module         Clock Module         and XT2 Oscillators         LFXT1 Oscillator                                                                                                                                | 6-1            6-2            6-3            6-5            6-6            6-7            6-7            6-7            6-7            6-7            6-7            6-10            6-10            6-11            6-12            7-1            7-2            7-4                                                                            |

|        | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Basic<br>7.1 | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3<br><b>Clock</b><br>Basic 0<br>LFXT1<br>7.2.1                            | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—Interrupt Routines         Hardware Multiplier Software Restrictions—MACS         Module         Clock Module         and XT2 Oscillators         LFXT1 Oscillator         XT2 Oscillator                                    | 6-1            6-3            6-5            6-6            6-7            6-8            6-9            6-10            6-10            6-11            6-12            7-1            7-2            7-4            7-5                                                                                                                         |

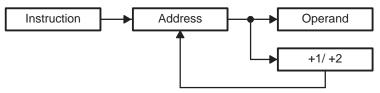

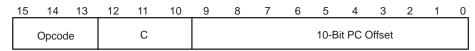

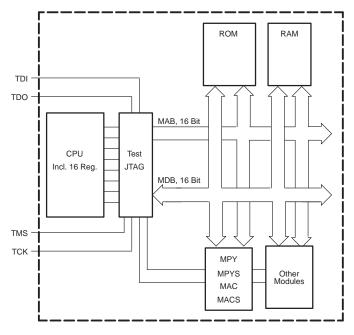

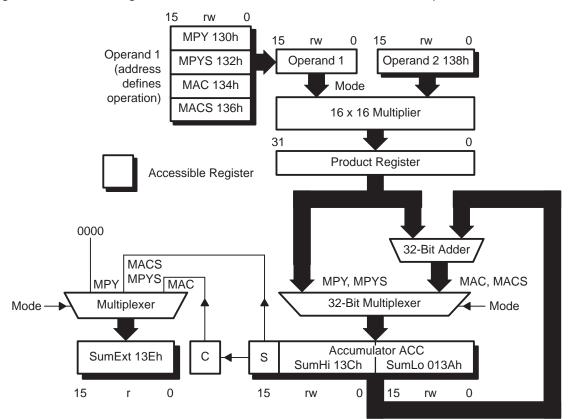

|        | Hard<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>Basic<br>7.1 | ware Mu<br>Hardw<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Hardw<br>Hardw<br>Hardw<br>6.5.1<br>6.5.2<br>6.5.3<br><b>Clock</b><br>Basic (<br>LFXT1<br>7.2.1<br>7.2.1                   | ultiplier         are Multiplier Module Support         are Multiplier Operation         Multiply Unsigned, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed, 16×16 bit, 16×8 bit, 8×16 bit, 8×8 bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         Multiply Signed and Accumulate, 16x16bit, 16x8bit, 8x16bit, 8x8bit         are Multiplier Registers         are Multiplier Special Function Bits         are Multiplier Software Restrictions         Hardware Multiplier Software Restrictions—Address Mode         Hardware Multiplier Software Restrictions—MACS         Module         Clock Module         and XT2 Oscillators         LFXT1 Oscillator                                                                                                                                | 6-1            6-3            6-5            6-6            6-7            6-7            6-7            6-7            6-7            6-7            6-7            6-7            6-7            6-10            6-10            6-11            6-12            7-1            7-2            7-4            7-5            7-6                |