MT92210

Carrier Class VoIP Processor Advance Datasheet

### Introduction

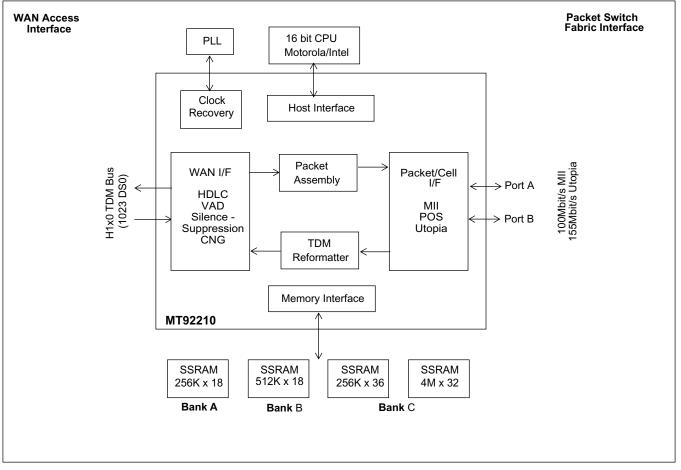

The MT92210 is an assembly and disassembly engine that can convert up to 1023 full-duplex TDM voice channels to IP packets and back, according to the H.225 standard. The device communicates via an H.1x0 TDM bus on the WAN Access side, carrying voice in plain PCM format, ADPCM or HDLCencapsulated mini-packets.

On the Packet Switch Fabric side, the MT92210 can carry IP packets over Ethernet, ATM (using AAL5 cells) or Packet over SONET. A 16 bit Intel/Motorola CPU interface is used to access and configure the device. Finally, up to 12 SRAMs and 2 SDRAMs can be used as external memory configuration and storage space.

The MT92210 offers significant savings in systems cost and system simplicity through reduced component count and simplified software.

DS5660

ISSUE 1.0

December 2001

### Features

#### General

- Up to 1023 Full-duplex PCM or ADPCM Voice Channels over IP/UDP/RTP connections

- Up to 4096 HDLC channels carrying UDP payload converted to IP/UDP connections

- Simultaneous support of PCM, ADPCM and HDLC Connections

- 16-bit Intel/Motorola CPU Interface

- Fully H.1x0 compliant TDM interface

- Network Interface A: UTOPIA Level 1/2, POS-PHY Level 2 or MII

- Network Interface B: UTOPIA Level 1

- Two to eight 18 bit data bus ZBT SSRAMs, each ranging in size from 128K to 1M bytes

- One to four 36 bit data bus ZBT SSRAMs, each ranging in size from 128K to 1M bytes

- Two 16 bit data bus SDRAMs, each ranging in size from 8M to 16M bytes

# **Data Formats**

- Simultaneous Support of IP versions 4 and 6

- Support for RTP, UDP and IP to support H.225

- IP packets can be sent over 3 different types of physical links (Ethernet, Utopia, Packet over SONET)

- RTP packaging is optional per connection

- IP over AAL5 can be performed using Classical IP over ATM with SNAP/LLC headers or Ethernet LAN Emulation (LANE)

- Support of MPLS & MPOA on reception

- Quality of service can de determined using Ethernet user priority or IP Type Of Service (TOS)

# **SAR Functions**

- Up to 4096 connections using HDCC minipackets

- Up to 1023 PCM/ADPCM channels

- HDLC packets containing UDP payload converted to IP/UDP datagrams

- Packets sizes up to 1500 bytes

- Jitter Absorption Buffer size up to 8192 bytes allows absorption of ±512 ms of PDV

- Injection of CPU-generated RTP packets

- Reception of CPU-destined RTP packets in buffers of up to 64K bytes

- Packet loss & miss-insertion compensation for PCM and ADPCM packets

- Network jitter monitoring allows support of RTCP for PCM, ADPCM, HDLC and CPU connections

#### **Network Functions**

- Off-the-shelf AAL5 SAR can be used to terminate data connections on a PCI bus

- Look-up can be performed on a priority basis: for example, a packet can be looked-up using only IP and UDP headers, then the look-up result can request a second lookup using IP, UDP and RTP headers

- IP, UDP and RTP header verification performed

- Payload type & Marker bit routing allows different compression formats as well as signaling packets to be transported on the same connection

#### Silence Suppression and Padding

- Proprietary Adaptive Silence Suppression

- Supported in both PCM and ADPCM formats

- Built-in detection of energy level

- Padding with matched energy "comfort noise"

- 32 large "comfort noise" buffers (16Kb to 64Kb)

- Suppression indication can be generated by chip or fed externally to synchronize with offchip compression codecs

#### H.1x0 Interface

- Fully H.110/H.100 compatible

- H.1x0 Master and Slave capability

- Support of message channel

- Low Latency Loop-back, H.1x0 to H.1x0, of 128 channels (delay <= 375 us)</li>

- Redundant Adaptive Clock Recovery Circuit

- Support of 2/4/8 MHz bus speed in groups of 4 streams (8 separate groups)

- Generation of H.1x0 compatibility signals

#### **TDM** data formats

- Support of plain PCM in u-law and A-law

- Translation between u-law and A-law on a per connection basis

- Support of ADPCM at 40, 32, 24 or 16 kbps

- Support of HDLC encapsulated mini-packets with asynchronous timing

- Support of HDLC streams ranging from 1 to 1023 time slots

- Support of HDLC packets up to 1500 bytes in length

#### Link Interface

- Ethernet: support of MII interface

- ATM: twin UTOPIA interfaces allow secondary data SAR to be daisy-chained with device for data connections

- Packet over SONET: support of 16-bit POS-PHY bus allowing interoperation with PHYs at speeds up to 155 Mbps

- Secondary UTOPIA port can be used in all modes, allowing the same data support architecture to be used independently of the link layer with minimal changes

- Transmission of voice to secondary port allows H.1x0/PCM bridging when coupled with AAL5 SAR

- Chip's pin-out allows designs that support Ethernet, ATM and Packet over SONET with only software configuration deciding on the link layer used

http://www.zarlink.com

World Headquarters - Canada Tel: +1 (613) 592 0200 Fax: +1 (613) 592 1010

North America - West Coast Tel: (858) 675-3400 Fax: (858) 675-3450

> **Asia/Pacific** Tel: +65 333 6193

Fax: +65 333 6192

North America - East Coast Tel: (978) 322-4800 Fax: (978) 322-4888

Europe, Middle East, and Africa (EMEA) Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products escincerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products end subject to Zarlink Semiconductor's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in an I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2001, Zarlink Semiconductor Inc. All rights reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE