# OKI Semiconductor ML9070-02/03

## DIRECT BUS CONNECTED CMOS REAL TIME CLOCK/CALENDAR

# DESCRIPTION

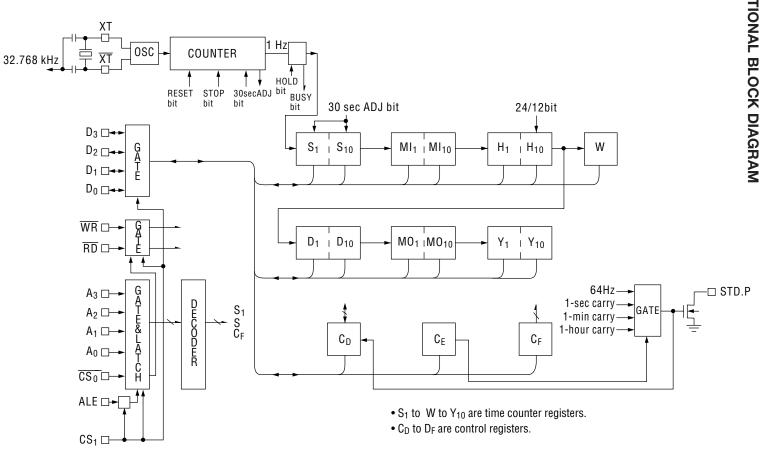

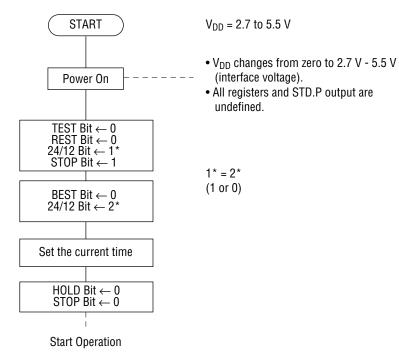

The ML9070-02/03 is a silicon gate CMOS Real Time Clock/Calendar for use in direct busconnection Microcontroller/Microprocessor applications. An on-chip 32.768 kHz crystal oscillator time base is divided to provide addressable 4-bit I/O data for SECONDS, MINUTES, HOURS, DAY OF WEEK, DATE, MONTH and YEAR. Data access is controlled by 4-bit address, chip selects ( $\overline{CS}_0$ ,  $CS_1$ ), WRITE, READ, and ALE. The ML9070-03 is not provided with the ALE pin. Control Registers D, E and F provide 30 SECOND error adjustment, INTERRUPT REQUEST (IRQ FLAG) and BUSY status bits, clock STOP, HOLD, and RESET FLAG bits, 4 selectable INTERRUPTS rates are available at the STD.P (STANDARD PULSE) output utilizing Control Register inputs T0, T1 and the INT/STND (INTERRUPT/STANDARD). Masking of the interrupt output (STD.P) can be accomplished via the MASK bit. The ML9070-02/03 can operate in a 12/24 hour format and Leap Year timing is automatic.

The interface supply voltage is 2.7 V to 5.5 V and the clock supply voltage during battery backup is 2.0 V to 5.5 V. A low current consumption has been realized.

## FEATURES

- Real time clock/calendar of SECONDS, MINUTES, HOURS, DAY OF WEEK, DATE, MONTH and YEAR

- 4-bit data bus

- 4-bit address bus

- READ, WRITE ALE, and CHIP SELECT INPUTS

- Auto leap year

- ±30 second error correction by software

- Selectable interrupt outputs 1/64 second, 1second, 1minute, 1hour

- Stop and restart of clock

- 12/24 hour format

- The ML9070-02 can input ALE from a microcontroller. (In case there is no ALE input from a microcontroller, fix ALE to "H" or use ML9070-03.)

- Wide range of interface power supply : 2.7 V to 5.5 V

- Wide range of clock power supply : 2.0 V to 5.5 V

- Low current consumption

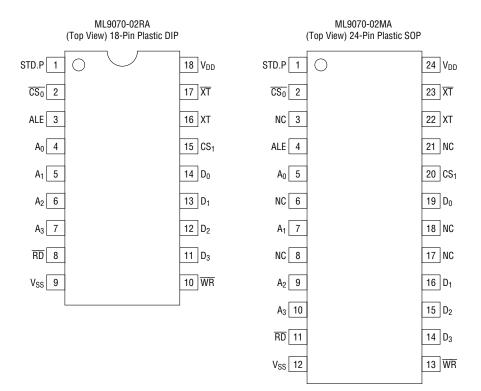

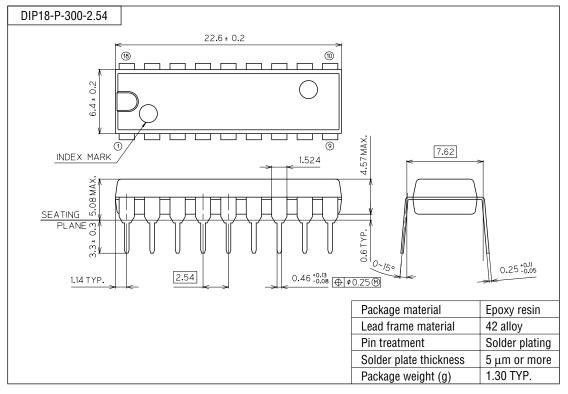

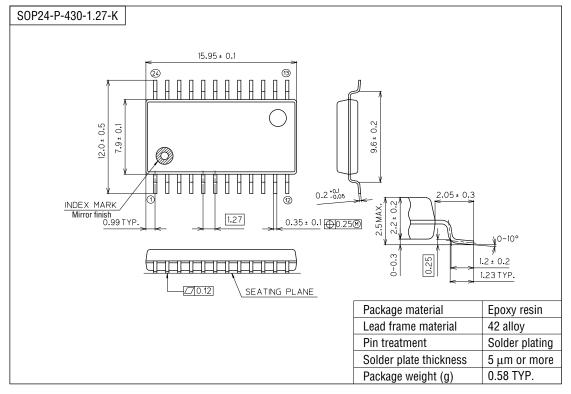

#### ML9070-02

- 18-pin plastic DIP (DIP18-P-300-2.54)

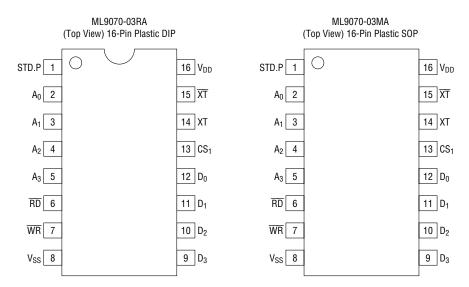

- 24-pin plastic SOP (SOP24-P-430-1.27-K) ML9070-03

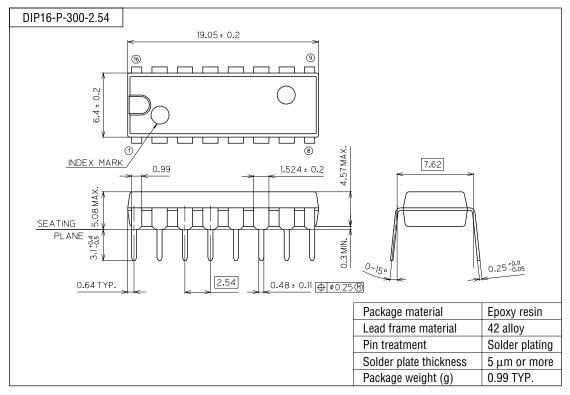

- 16-pin plastic DIP (DIP16-P-300-2.54)

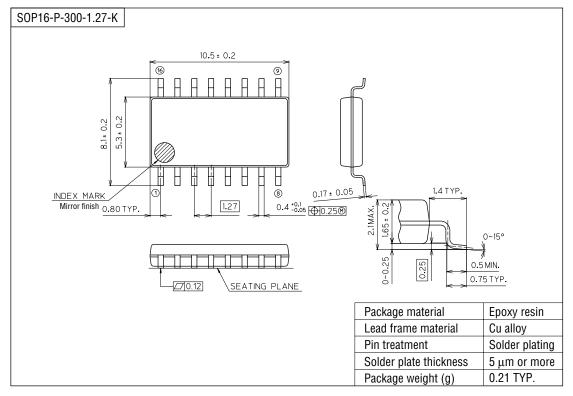

- 16-Pin plastic SOP (SOP16-P-300-1.27-K)

# **PIN CONFIGURATIONS**

NC : NO CONNECTION (Unused pin)

#### Note) "M9070-02" is marked on actual devices.

Note) "M9070-03" is marked on actual devices.

## **PIN DESCRIPTION**

•  $D_0$  to  $D_3$  (Data bus 0 to 3)

Data bus Input/output pins to be directly connected to a microcontroller bus for reading and writing of the clock/calendar's registers and control registers.

The interface is logically positive. When  $\overline{CS}_0 = "L"$ ,  $CS_1 = "H"$ ,  $\overline{RD} = "L"$  and  $\overline{WR} = "H"$ , these pins are in the output mode. Otherwise these pins are in the high impedance state.

The ML9070-03 has no  $\overline{CS}_0$  pin and operates similarly as when  $\overline{CS}_0$  is fixed to "L". In the ML9070-03, input/output of these pins are determined by the same settings as those in the ML9070-02 except setting of the  $\overline{CS}_0$  pin.

•  $A_0$  to  $A_3$  (Address bus 0 to 3)

Address input pin for use by a microcontroller to select internal clock/calendar's registers and control registers for Read/Write operations. Address input pins  $A_0 - A_3$  are used in combination with ALE for addressing registers.

• ALE (Address Latch Enable)

Address Latch Enable pin. This pin enables writing of address data when ALE = "H" and  $\overline{CS}_0$  = "L"; address data is latched when ALE = "L". Microcontroller having an ALE output should connect to this pin; otherwise it should be connected at V<sub>DD</sub>. CS<sub>1</sub> works independently of ALE. When a 4-bit microcontroller and other peripheral ICs share A<sub>0</sub> to A<sub>3</sub>, ALE is also used to specify this IC. The ML9070-03 has no ALE pin and operates similarly as when ALE is fixed to "H".

•  $\overline{\mathrm{WR}}$  (WRite)

Writing of data is performed by this pin.

When  $CS_1 = "H"$  and  $\overline{CS}_0 = "L"$ ,  $D_0 - D_3$  data is written into the register specified by  $A_0$  to  $A_3$  and ALE at the rising edge of  $\overline{WR}$ .

• RD (ReaD)

Reading of register data is accomplished using this pin. When  $CS_1 = "H"$ ,  $\overline{CS}_0 = "L"$  and  $\overline{RD} = "L"$ , the data of this register is output to  $D_0 - D_3$ .

It is inhibited to set both  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  to "L" simultaneously because this setting causes a malfunction.

•  $\overline{\text{CS}}_{0}$ ,  $\text{CS}_{1}$  (Chip Select 0, 1)

Chip Select pins. These pins enable or disable ALE,  $\overline{RD}$  and  $\overline{WR}$  operations.  $\overline{CS}_0$  and ALE work in combination with one another.

When  $\overline{CS}_0 = "L"$  and  $CS_1 = "H"$ , ALE,  $\overline{RD}$  and  $\overline{WR}$  are enabled. Otherwise, the device is unconditionally equivalent to ALE = "L",  $\overline{WR} = \overline{RD} = "H"$ .

For details, refer to "CS1 (Chip Select)" in "APPLICATION NOTE".

The ML 9070-03 has no  $\overline{CS}_0$  pin and operates similarly as when ALE is fixed to "H" and  $\overline{CS}_0$  to "L".

• STD.P (STanDard Pulse)

Output pin of N-CH OPEN DRAIN type. The output data is controlled by the D<sub>1</sub> data (INT/STD bit) content of C<sub>E</sub> register. This pin has a priority to  $\overline{CS}_0$  and CS<sub>1</sub>. Refer to "C<sub>E</sub> Register" in "FUNCTIONAL DESCRIPTION OF REGISTERS".

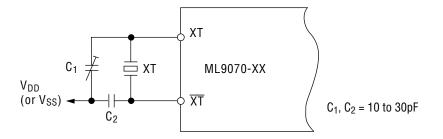

#### • XT, $\overline{\text{XT}}$ (X'Tal OSC)

32.768kHz crystals are connected to these pins. The connection diagram is shown below.

The impedance of the crystal should be less than  $30k\Omega$ .

When an external clock is used, it is to be input to XT, while XT should be left open. The oscillation crystal and capacitors should be placed as close to the IC as possible. The oscillation circuit and other signal lines on any side of the substrate should be distant from each other.

• V<sub>DD</sub>, V<sub>SS</sub>

Power supply pins.  $V_{DD}$  is used for positive supply and  $V_{SS}$  is for negative supply.

# **ABSOLUTE MAXIMUM RATING**

| Parameter            | Symbol           | Condition | Rating                                       | Unit |

|----------------------|------------------|-----------|----------------------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  |           | -0.3 to +7.0                                 |      |

| Input Voltage        | VI               | Ta = 25°C | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output Voltage       | V <sub>0</sub>   |           | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 |      |

| Storage Temperature  | T <sub>STG</sub> | —         | -55 to +150                                  | °C   |

# **OPERATING CONDITIONS**

| Parameter             | Symbol            | Condition | Rating     | Unit |

|-----------------------|-------------------|-----------|------------|------|

| Power Supply Voltage  | V <sub>DD</sub>   | —         | 2.7 to 5.5 | V    |

| Clock Supply Voltage  | V <sub>CLK</sub>  | —         | 2.0 to 5.5 | V    |

| Crystal Frequency     | f <sub>(XT)</sub> | _         | 32.768     | kHz  |

| Operating Temperature | T <sub>op</sub>   | _         | -40 to +85 | °C   |

(Note) The clock supply voltage assures crystal oscillation and clock.

# **DC CHARACTERISTICS**

$(V_{DD} = 2.7 \text{ to } 5.5 \text{V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter               | Symbol           | Condition                                          | Min.               | Тур. | Max.               | Unit | Applicable Terminal              |

|-------------------------|------------------|----------------------------------------------------|--------------------|------|--------------------|------|----------------------------------|

| "H" Input Voltage (1)   | V <sub>IH1</sub> | V <sub>DD</sub> = 2.7 to 4.0 V                     | 4/5V <sub>DD</sub> |      | V <sub>DD</sub>    | V    |                                  |

|                         | VIH1             | $V_{DD}$ = 4.0 to 5.5 V                            | 2.2                |      | V <sub>DD</sub>    | V    | All input terminals              |

| "I " Input Voltage (1)  | V                | $V_{DD}$ = 2.7 to 4.0 V                            | V <sub>SS</sub>    | _    | 1/5V <sub>DD</sub> | V    | except CS <sub>1</sub> ,XT       |

| "L" Input Voltage (1)   | V <sub>IL1</sub> | $V_{DD}$ = 4.0 to 5.5 V                            | V <sub>SS</sub>    | _    | 0.8                | V    |                                  |

| "H" Input Current (1)   | l <sub>IH1</sub> | $V_I = V_{DD}$                                     | —                  |      | 1                  | μA   | Input terminals other            |

| "L" Input Current (1)   | l <sub>IL1</sub> | $V_I = 0 V$                                        | _                  |      | -1                 | μA   | than $D_0$ to $D_3$ , XT         |

| "H" Input Voltage (2)   | V <sub>IH2</sub> | $V_{DD}$ = 2.0 to 5.5 V                            | 4/5V <sub>DD</sub> |      | V <sub>DD</sub>    | V    | CS <sub>1</sub>                  |

| "L" Input Voltage (2)   | V <sub>IL2</sub> | $V_{DD}$ = 2.0 to 5.5 V                            | V <sub>SS</sub>    | _    | 1/5V <sub>DD</sub> | V    |                                  |

| "H" Input Current (2)   | I <sub>IH2</sub> | $V_I = V_{DD}$                                     |                    |      | 10                 | μA   | D <sub>0</sub> to D <sub>3</sub> |

| "L" Input Current (2)   | I <sub>IL2</sub> | $V_I = 0 V$                                        | —                  |      | -10                | μA   |                                  |

| "L" Output Voltage (1)  | V <sub>OL1</sub> | l <sub>0</sub> = 2.5 mA                            | _                  | _    | 0.4                | V    | D <sub>0</sub> to D <sub>3</sub> |

| "H" Output Voltage      | V <sub>OH</sub>  | I <sub>0</sub> = -400 μA                           | 2.4                | _    | —                  | V    |                                  |

| "L" Onput Voltage (2)   | V <sub>0L2</sub> | l <sub>0</sub> = 2.5 mA                            | _                  | _    | 0.4                | V    | STD. P                           |

| OFF Leak Current        | I <sub>OFF</sub> | $V_I = V_{DD}$ or 0 V, $V_0 = V_D$                 | D —                | _    | 10                 | μA   |                                  |

| Current Consumption (1) | I <sub>DD1</sub> | f <sub>(XT)</sub> = 32.768 kHz V <sub>DD</sub> = 5 | /                  |      | 20                 | μA   | V <sub>DD</sub>                  |

| Current Consumption (2) | I <sub>DD2</sub> | $V_{I(CS1)} = 0 V$ $V_{DD} = 2 V$                  | /                  | _    | 5                  | μA   |                                  |

# SWITCHING CHARACTERISTICS

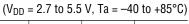

#### • ML9070-02/03

## • WRITE mode (ALE = "H")

|                             |                  | (VDD)     | - 2.7 10 5.5 | v, ia – –40 | 0 10 +03 0) |

|-----------------------------|------------------|-----------|--------------|-------------|-------------|

| Parameter                   | Symbol           | Condition | Min.         | Max.        | Unit        |

| CS1 Setup Time              | t <sub>C1S</sub> | —         | 100          |             |             |

| CS <sub>1</sub> Hold Time   | t <sub>C1H</sub> | _         | 100          |             |             |

| Address Stable Before WRITE | t <sub>AW</sub>  | —         | 20           |             |             |

| Address Stable After WRITE  | t <sub>WA</sub>  | —         | 10           |             | ns          |

| WR Pulse Width              | t <sub>WW</sub>  | —         | 120          |             | 115         |

| Data Setup Time             | t <sub>DS</sub>  | —         | 100          |             |             |

| Data Hold Time              | t <sub>DH</sub>  | —         | 10           |             |             |

| RD / WR Recovery Time       | t <sub>RCV</sub> | —         | 60           | _           |             |

The ML9070-03 has no  $\overline{\text{CS}}_0$  input. (Note)

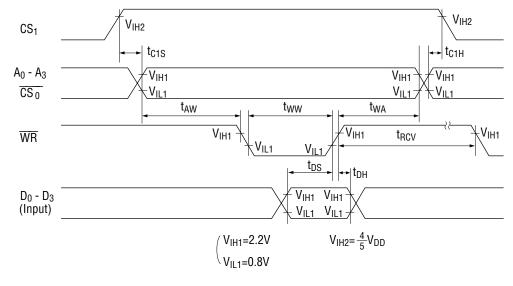

#### • ML9070-02

• WRITE mode (with use of ALE)

$(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                  | Symbol           | Condition | Min. | Max. | Unit |

|----------------------------|------------------|-----------|------|------|------|

| CS <sub>1</sub> Setup Time | t <sub>C1S</sub> | _         | 100  | —    |      |

| Address Setup Time         | t <sub>AS</sub>  | _         | 25   | —    |      |

| Address Hold Time          | t <sub>AH</sub>  | _         | 25   | —    |      |

| ALE Pulse Width            | t <sub>AA</sub>  | _         | 40   | —    |      |

| ALE Before WRITE           | t <sub>ALW</sub> | _         | 10   | —    |      |

| WRITE Pulse Width          | t <sub>WW</sub>  | _         | 120  | —    | ns   |

| ALE After WRITE            | t <sub>WAL</sub> | _         | 20   | —    |      |

| DATA Setup Time            | t <sub>DS</sub>  | —         | 100  | —    |      |

| DATA Hold Time             | t <sub>DH</sub>  | —         | 10   | —    |      |

| CS <sub>1</sub> Hold Time  | t <sub>C1H</sub> | —         | 100  | —    |      |

| RD / WR Recovery Time      | t <sub>RCV</sub> | _         | 60   | —    |      |

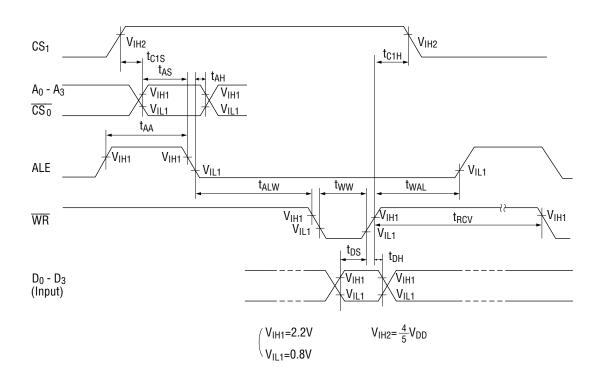

#### ML9070-02/03

• READ mode (ALE = "H")

|                            |                  | (V <sub>DD</sub>       | = 2.7 to 5.5 | 5 V, Ta = -4 | 0 to +85°C |

|----------------------------|------------------|------------------------|--------------|--------------|------------|

| Parameter                  | Symbol           | Condition              | Min.         | Max.         | Unit       |

| CS <sub>1</sub> Setup Time | t <sub>C1S</sub> | —                      | 100          | —            |            |

| CS <sub>1</sub> Hold Time  | t <sub>C1H</sub> | —                      | 100          | —            |            |

| Address Stable Before READ | t <sub>AR</sub>  | —                      | -10          | —            |            |

| Address Stable After READ  | t <sub>RA</sub>  | —                      | 0            | —            | ns         |

| RD to Data                 | t <sub>RD</sub>  | C <sub>L</sub> = 150pF |              | 120          |            |

| Data Hold                  | t <sub>DR</sub>  | —                      | 0            | —            | ]          |

| RD / WR Recovery Time      | t <sub>RCV</sub> | —                      | 60           | —            |            |

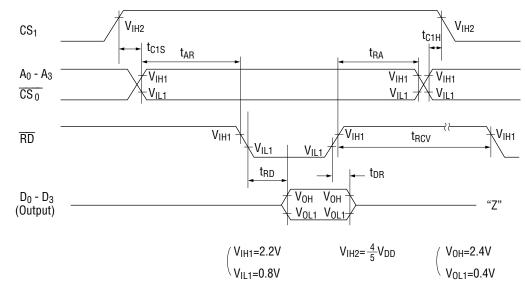

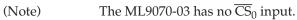

#### • ML9070-02

• READ mode (with use of ALE)

| Parameter                  | Symbol           | Condition              | Min. | Max. | Unit  |

|----------------------------|------------------|------------------------|------|------|-------|

| CS <sub>1</sub> Setup Time | t <sub>C1S</sub> | _                      | 100  | _    |       |

| Address Setup Time         | t <sub>AS</sub>  | _                      | 25   | _    |       |

| Address Hold Time          | t <sub>AH</sub>  | _                      | 25   | _    |       |

| ALE Pulse Width            | t <sub>AA</sub>  | —                      | 40   | _    |       |

| ALE Before READ            | t <sub>ALR</sub> | _                      | 10   | _    | ns    |

| ALE After READ             | t <sub>RAL</sub> | _                      | 10   | _    | 1 113 |

| RD to Data                 | t <sub>RD</sub>  | C <sub>L</sub> = 150pF | _    | 120  |       |

| DATA Hold                  | t <sub>DR</sub>  | _                      | 0    | —    |       |

| CS <sub>1</sub> Hold Time  | t <sub>C1H</sub> | _                      | 100  | _    |       |

| RD / WR Recovery Time      | t <sub>RCV</sub> | _                      | 60   | _    | 1     |

# (V<sub>DD</sub> = 2.7 to 5.5 V, Ta = -40 to +85°C)

## **REGISTER TABLE**

| Add-<br>ress | Ac             | Address Input Register |            |                | Data             |                         |                  |                  | Count                   |                     |                               |

|--------------|----------------|------------------------|------------|----------------|------------------|-------------------------|------------------|------------------|-------------------------|---------------------|-------------------------------|

| Input        | A <sub>3</sub> | <b>A</b> 2             | <b>A</b> 1 | A <sub>0</sub> | Name             | D <sub>3</sub><br>(MSB) | D <sub>2</sub>   | D <sub>1</sub>   | D <sub>0</sub><br>(LSB) | value               | Description                   |

| 0            | 0              | 0                      | 0          | 0              | S <sub>1</sub>   | S8                      | \$4              | \$2              | \$1                     | 0 to 9              | 1-second digit register       |

| 1            | 0              | 0                      | 0          | 1              | S <sub>10</sub>  | f <sub>0</sub>          | \$40             | \$ <sub>20</sub> | \$ <sub>10</sub>        | 0 to 5              | 10-second digit register      |

| 2            | 0              | 0                      | 1          | 0              | MI <sub>1</sub>  | mi <sub>8</sub>         | mi <sub>4</sub>  | mi <sub>2</sub>  | mi <sub>1</sub>         | 0 to 9              | 1-minute digit register       |

| 3            | 0              | 0                      | 1          | 1              | MI <sub>10</sub> | *                       | mi <sub>40</sub> | mi <sub>20</sub> | mi <sub>10</sub>        | 0 to 5              | 10-minute digit register      |

| 4            | 0              | 1                      | 0          | 0              | H <sub>1</sub>   | h <sub>8</sub>          | h <sub>4</sub>   | h <sub>2</sub>   | h <sub>1</sub>          | 0 to 9              | 1-hour digit register         |

| 5            | 0              | 1                      | 0          | 1              | H <sub>10</sub>  | *                       | PM/AM            | h <sub>20</sub>  | h <sub>10</sub>         | 0 to 2<br>or 0 to 1 | PM/AM, 10-hour digit register |

| 6            | 0              | 1                      | 1          | 0              | D <sub>1</sub>   | d <sub>8</sub>          | d4               | d <sub>2</sub>   | d <sub>1</sub>          | 0 to 9              | 1-day digit register          |

| 7            | 0              | 1                      | 1          | 1              | D <sub>10</sub>  | *                       | *                | $d_{20}$         | d <sub>10</sub>         | 0 to 3              | 10-day digit register         |

| 8            | 1              | 0                      | 0          | 0              | MO <sub>1</sub>  | mo <sub>8</sub>         | mo <sub>4</sub>  | m0 <sub>2</sub>  | m0 <sub>1</sub>         | 0 to 9              | 1-month digit register        |

| 9            | 1              | 0                      | 0          | 1              | MO <sub>10</sub> | *                       | *                | *                | mo <sub>10</sub>        | 0 to 1              | 10-month digit register       |

| Α            | 1              | 0                      | 1          | 0              | Y <sub>1</sub>   | У8                      | У4               | У2               | У1                      | 0 to 9              | 1-year digit register         |

| В            | 1              | 0                      | 1          | 1              | Y <sub>10</sub>  | У80                     | У40              | У20              | У10                     | 0 to 9              | 10-year digit register        |

| С            | 1              | 1                      | 0          | 0              | W                | *                       | W4               | W <sub>2</sub>   | W <sub>1</sub>          | 0 to 6              | Week register                 |

| D            | 1              | 1                      | 0          | 1              | CD               | 30 sec.<br>ADJ          | IRQ-F            | BUSY             | HOLD                    | —                   | Control Register D            |

| E            | 1              | 1                      | 1          | 0              | CE               | t <sub>1</sub>          | t <sub>0</sub>   | INT<br>/STND     | MASK                    |                     | Control Register E            |

| F            | 1              | 1                      | 1          | 1              | CF               | TEST                    | 24/12            | STOP             | REST                    | —                   | Control Register F            |

REST = RESET

INT/STND = INTERRUPT/STANDARD

- Note 1) Bit\* does not exist (unrecognized during a write and held at "0" during a read).

- Note 2) Be sure to mask the AM/PM bit when processing 10's of hour's data.

- Note 3) BUSY bit is read only. The IRQ-F bit can only be set to a "0". Setting the IRQ-F to a "1" is done by hardware.

- Note 4) PM at 1 and AM at 0 for PM/AM bit.

- Note 5) "1" or "0" may be written to bit \*.

- Note 6) The bit fo (OSC FLAG) memorizes that oscillation stops. This bit is used to monitor the battery. This bit is cleared by writing a "0". A "1" cannot be written into this bit.

# FUNCTIONAL DESCRIPTION OF REGISTERS

## $S_1, S_{10}, MI_1, MI_{10}, H_1, H_{10}, D_1, D_{10}, MO_1, MO_{10}, Y_1, Y_{10}, W$

- a) These are abbreviations for SECOND1, SECOND10, MINUTE1, MINUTE10, HOUR1, HOUR10, DAY1, DAY10, MONTH1, MONTH10, YEAR1, YEAR10, and WEEK. These values are in BCD notation.

- b) All registers are logically positive. For example,  $(s_8, s_4, s_2, s_1) = 1001$  which means 9 seconds.

- c) "1" or "0" may be written to bit\* in the Register Table. The bit\* automatically reads "0".

- d) If data is written which is out of the clock register data limits, it can result in erroneous clock data being read back.

- PM/AM, h<sub>20</sub>, h<sub>10</sub>

- a) In 12-hour mode

The existent time is AM12 : 00 through AM11 : 00 and PM12 : 00 through PM11 : 00. It is impossible to write data into the  $h_{20}$ , bit which is fixed to "0" unconditionally. The  $h_{20}$  bit is not set by clocking.

- b) In 24-hour modeThe existent time is 0 : 00 clock through 23 : 00 clock.The PM/AM bit written is ignored and read out as "0" unconditionally.

- Y<sub>1</sub>, Y<sub>10</sub>, and leap year

The ML9070 automatically recognizes leap years in either Christian Era calendar or Heisei Era (Japanese) calendar.

80, 84, 88... Leap year

When invalid month and day values are set (for instance, February 29, 1983 or November 31), the month and day values will be carried to the next month and day values when the carry pulse to the day digit is generated (for instance, the above dates become March 1, 1983 and December 1).

The ML9070 recognizes a year whose last two digits can be divided evenly by 4 as leap year. Therefore, year 2100, which does not include a leap day, is excluded from automatic leap year correction. Year 2000 will be corrected automatically since the year contains a leap day. The user must check whether the year is year 2000 or 2100 when  $Y_{10}$ ,  $Y_1 = "0, 0"$ .

| <b>W</b> 4 | W2 | <b>W</b> 1 | Day of Week |

|------------|----|------------|-------------|

| 0          | 0  | 0          | Sunday      |

| 0          | 0  | 1          | Monday      |

| 0          | 1  | 0          | Tuesday     |

| 0          | 1  | 1          | Wednesday   |

| 1          | 0  | 0          | Thursday    |

| 1          | 0  | 1          | Friday      |

| 1          | 1  | 0          | Saturday    |

The Register W data limits are 0 - 6 (The table below shows a possible bit data definition).

f<sub>0</sub> Flag

The  $f_0$  flag bit memorizes that oscillation stops and is used to monitor the output of the battery. The "1" of this bit indicates stop of oscillation. This bit is cleared by writing "0". It is not permitted to write "1" into this bit.

"0" cannot be written in this bit during stop of oscillation.

## C<sub>D</sub> REGISTER (Control D Register)

• 30-sec ADJ (D<sub>3</sub>) (30-second adjustment bit)

When a "1" is written to this bit, if the second digits are smaller than 30, the second digits are reset to 00, and if it is larger than 30, the second digits are reset to 00 and a carry into the minute digit is executed. Data cannot be written into the  $S_1$  - W registers and a "1" can not be written into the REST bit of the  $C_F$  register 125µs after writing into this bit because internal processing is being executed. This bit holds "1" 125µs after writing, and returns to "0" automatically. Therefore, data should be written into the  $S_1$  - W registers after checking that this bit has returned to "0".

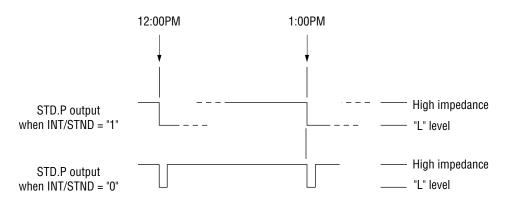

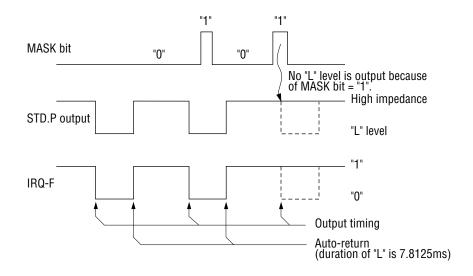

• IRQ-F (D<sub>2</sub>) (Interrupt ReQuest Flag)

This status bit corresponds to the output level of the STD.P output. When STD.P = "L", then IRQ-F = "1", when STD.P = high impedance, then IRQ-F = "0". The IRQ-F indicates that an interrupt has occurred in the microcomputer if IRQ-F = "1". When D<sub>0</sub> of register C<sub>E</sub> (MASK) = "0", then the STD.P output changes from high impedance to "L" and IRQ-F changes from "0" to "1" according to the timing set by D<sub>3</sub> (t<sub>1</sub>) and D<sub>2</sub> (t<sub>0</sub>) of register C<sub>E</sub>. When D<sub>1</sub> of register C<sub>E</sub> (INT/STND) = "1" (interrupt mode), the STD.P output remains "L" until the IRQ-F is written to a "0". When IRQ-F = "1" and timing for a new interrupt occurs, the new interrupt is ignored. When D<sub>1</sub> (INT/STND) = "0" (Standard Pulse Output mode) the STD.P output remains "L" until either "0" is written to the IRQ-F or the IRQ-F automatically goes to "0" after 7.8125ms.

#### • BUSY (D<sub>1</sub>)

Internal status bit that indicates whether interface with a microcontroller is enabled or disabled. To write data in registers  $S_1$  to W (addresses 0 to C), the HOLD bit must be set to "1" and the BUSY bit must be set to "0". To read data, the BUSY bit must be set to "0" when the HOLD bit is used. The BUSY bit is kept to "0" while the HOLD bit is "1". When the HOLD bit is set to "0", the BUSY bit is set to "1". The IRQ-F of register  $C_D$ ,  $C_E$  and  $C_F$  operations can be performed regardless of the settings of the HOLD bit and the BUSY bit.

When the HOLD bit is set to "0", the BUSY bit is set to "1" unconditionally and BUSY/non-BUSY can be checked by writing "1" to the HOLD bit. When BUSY = "1" (BUSY status) is read, check BUSY = "0" as follows :

Repeat the BUSY checking routine by writing "0" and then "1" to the HOLD bit (HOLD  $\leftarrow$  0, HOLD  $\leftarrow$  1, BUSY check) or write "1" to the HOLD bit again 190 micro seconds after writing "0" to the HOLD bit.

The BUSY status lasts 190 micro seconds per one second.

Data cannot be written to the BUSY bit.

#### • HOLD (D<sub>0</sub>)

Bit used for reading and writing registers  $S_1$  to W (addresses 0 to C), When "1" is written to this bit and the BUSY bit is "0", the clock of one second digit or more is stopped, enabling Read/Write operations. When BUSY is "1" or Read/Write is completed, "0" is written to the HOLD bit. If the writing of "0" is omitted, data may be corrupted.

By setting this bit to "1", the carry of one-second digit is prohibited inside the IC. However, the carry to the second digit that was generated during the "1" interval will be corrected automatically (+1 second) once only when "0" is written to this bit. However, next and subsequent carry will be ignored and data will not be corrected. (Loss of second).

When CS<sub>1</sub> is set to "L", the HOLD bit will become "0" like that "0" is written to the HOLD bit.

## C<sub>E</sub> REGISTER (Control E Register)

• t<sub>1</sub> (D<sub>3</sub>), T<sub>0</sub> (D<sub>2</sub>) (Time 0, 1) INT/STND bit = "1" : Setting of interrupt period INT/STND bit = "0" : Setting of periodic waveform

| t <sub>1</sub> | t <sub>0</sub> | Period      |

|----------------|----------------|-------------|

| 0              | 0              | 1-64 second |

| 0              | 1              | 1 second    |

| 1              | 0              | 1 minute    |

| 1              | 1              | 1 hour      |

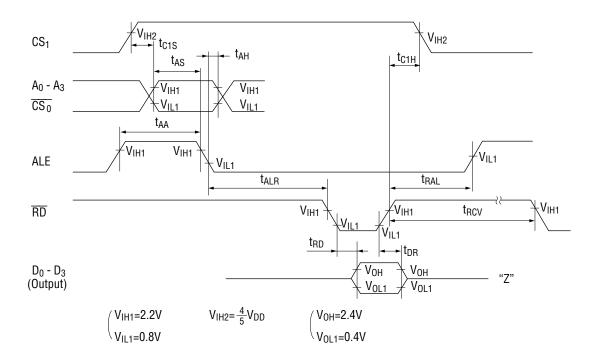

The duration that the periodic waveform output is at "L" level is about 7.8125ms.  $t_1$  and  $t_0$  determine the output timing of the STD.P output.

e.g.) When t<sub>1</sub> = "1", t<sub>0</sub> = "1", MASK = "0"

When a "1" is written to the 30-sec ADJ bit, a carry can occur.

Therfore, if  $(t_1, t_0) = (1, 0)$ , (1, 1), the STD.P output may sometime be at "L" level. When INT/STND = "0", this "L" level is kept for a maximum of 9.8ms after under-second digits in 30-sec ADJ is cleared (the 30-sec ADJ flag returns to "0").

If the selected interrupt period is 1 second, 1 minute, or 1 hour, a carry occurs during the time the  $S_1$ ,  $S_{10}$ ,  $MI_1$ ,  $MI_{10}$  registers are overwritten using the HOLD bit, and data written in these registers determines the interrupt timing set by the carry, the STD.P output will go to "L" level after HOLD = "0". (IRQ-F will is set to "1")

In other cases, writing to the S<sub>1</sub>, S<sub>10</sub>, MI<sub>1</sub>, MI<sub>10</sub>, H<sub>1</sub> registers do not change the STD.P output.

- INT/STND (D<sub>1</sub>) (interrupt-to-Standard waveform switching bit)

- INT/STND = "1" : "1" of the IRQ-F bit and "L" level on the STD.P output are kept until IRQ-F (C<sub>D</sub> register) is read out.

- INT/STND = "0" : "1" of the IRQ-F bit returns to "0" after a certain time elapses (after about 7.8ms) or when IRQ-F is read out.

"L" level on the STD.P output returns to high impedance after a certain time elapses.

#### • MASK (D<sub>0</sub>)

"1" of the MASK bit inhibits the setting of "1" to the IRQ-F flag and sets the STD.P output to the high impedance state.

Interrupt mode (INT/STND = "1")

Periodic timing waveform output mode (INT/STND = "0")

When the IRQ-F bit is read out before auto-return, the IRQ-F bit goes to "0", and the STD.P output keeps "L" level for 7.8125 ms, then goes into the high impedance state.

## **C<sub>F</sub> REGISTER (Control F Register)**

- TEST (D<sub>3</sub>) The TEST bit is used for testing by OKI and should be set to "0".

- 24/12 (D<sub>2</sub>) (24/12 hour format) This bit is used to switch between 24-hour format and 12-hour format. 24/12 = "1" : 24-hour format without PM/AM 24/12 = "0" : 12-hour format with PM/AM When the 24/12 bit is changed, data in the H<sub>1</sub> - W registers may become undefined. Therefore, it is required to set those registers again.

- STOP (D<sub>1</sub>)

"1" of this bit stops clocking and "0" restarts clocking.

• REST (D<sub>0</sub>)

"1" of this bit clears under-second-time to zero and at the same time stops clocking. "0" of this bit restarts clocking.

When  $CS_1$  is set to "L", this bet goes to "0" automatically.

## **APPLICATION NOTE**

#### **Power Supply**

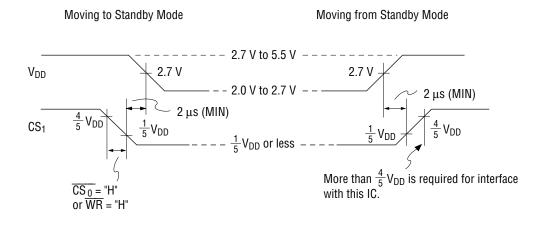

## CS<sub>1</sub> (Chip Select)

$V_{IH}$  and  $V_{IL}$  of  $CS_1$  has 3 functions.

- a) To accomplish the interface with a microcontroller/microprocessor.

- b) To inhibit the control bus, data bus and address bus and to reduce input gate pass current in the stand-by mode.

- c) To protect internal data when the mode is moved to and from standby mode.

To realize the above functions:

- a) More than  $\frac{4}{5}$  V<sub>DD</sub> should be applied to the ML9070 for the interface with a microcontroller/microprocessor.

- b) In moving to the standby mode, less than  $\frac{1}{5}$  V<sub>DD</sub> should be applied so that all data buses should be disabled. In the standby mode, approx. 0V should be applied.

- c) When moving to and from the standby mode, obey the following timing chart.

# PACKAGE DIMENSIONS

(Unit : mm)

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit : mm)

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1998 Oki Electric Industry Co., Ltd.