Data Sheet

# **JTAG Test Sequencer**

### **Description**

The AS91L1002 device provides a solution to perform stand alone IEEE1149.1 tests with out any third party test hardware.

The device executes tests that have been translated from the Serial Vector Format (SVF) to the compact binary format, BVI which is stored in a Flash memory. Upon completion of the test run the user is presented with PASS/FAIL information, thus enabling a high degree of confidence in the operation of the PCB.

The AS91L1002 can be controlled by using one of two different sources: a power-on

### **Key Features**

- Performs IEEE1149.1 tests in standalone mode without any 3<sup>rd</sup> Party test hardware

- Eliminates the need for firmware development, thereby speeding up time to market

- AS91L1002 can be used to perform self tests on multiple PCBs on a system in parallel

reset circuit or a front panel switch. Any one of these can cause the AS91L1002 to execute tests that have been loaded into the Flash memory. When the AS91L1002 is running and performing the tests, status lines are fed off chip to enable the user to hold the PCB in a safe state until completion of the tests.

When the tests have completed, the status of the execution is presented off chip through a status line to indicate the PASS/FAIL condition.

- Pinout and feature set compatible (complete second source) with the Firecron JTS02 device

- Available in a 100-pin LQFP or a 100-pin FPBGA lead free package

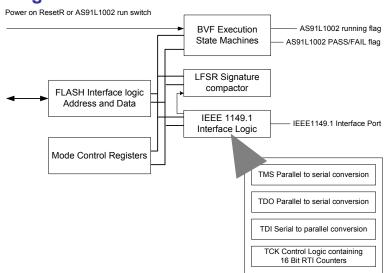

### **Device Block Diagram**

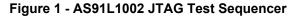

### **BIST Sequencer Power On Operation**

The AS91L1002 does not require a microprocessor to operate and run IEEE1149.1 tests. It can be used to perform diagnostics on the PCB. In systems with multiple cards, all cards can simultaneously execute self tests without processor intervention, thereby significantly reducing test time. AS91L1002 utilizes IEEE1149.1 tests generated by industry standard ATPG tools, thereby eliminating the need for custom firmware development resulting in faster time to market.

In the AS91L1002, the IEEE1149.1 test preparation is a two-step process. The first step is to convert the industry standard SVF format into the compact Alliance binary BVF file. One or more IEEE1149.1 tests represented as Alliance BVF files can then be further compressed into an Alliance BVI file which is then exported to a binary file for programming into the flash device, and then used by the AS91L1002 for test execution.

The user is able to specify the TCK rate for each individual test execution based on a programmable divider within the AS91L1002, along with a programmable test start delay time based upon the number of TCKs.

These features enable multiple tests to be stored, in the AS91L1002 test flash. It allows each test to operate at different TCK rate, and allows for sufficient settling time before each test starts to ensure that the PCB is in a stable condition.

# **Signal Description**

| PIN NAME       | PIN NUMBER<br>LQFP                                                                                                | PIN NUMBER<br>FPBGA                                     | DESCRIPTION                                                                                                                                                                                                                       |

|----------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOE            | 88                                                                                                                | B6                                                      | Test Output Enable: When this signal is taken to logic '0', all I/O on the device is placed in HighZ.                                                                                                                             |

| POR            | 14                                                                                                                |                                                         | Power on Reset: This signal when taken to logic<br>'0' causes the AS91L1002 to reset. When the<br>signal returns to logic '1' the AS91L1002 starts<br>test execution.                                                             |

| SW_RUN         | 10                                                                                                                |                                                         | Switch AS91L1002 Run: This signal when taken<br>to logic '0' causes the AS91L1002 to reset. When<br>the signal returns to logic '1' the AS91L1002 starts<br>test execution.                                                       |

| OSC_IN         | 16                                                                                                                | F1                                                      | Oscillator Input: Provides the master clock into the AS91L1002, Max freq 66 MHz.                                                                                                                                                  |

| BUSY_IDLE      | 25                                                                                                                |                                                         | BUSY IDLE: This output indicates the state of the AS91L1002. When High, it indicates that the AS91L1002 is active.                                                                                                                |

| PASS_FAIL      | 24                                                                                                                |                                                         | PASS FAIL: This output provides status of the test<br>execution. When at logic'1' after test execution the<br>stored IEEE1149.1 test has failed due to data<br>errors.                                                            |

| FLASH_ADD[023] | 70, 69, 67, 65,<br>64, 63, ,61,<br>60, 57, 28, 29,<br>30, 31, 32, 35,<br>36, 37, 40, 41,<br>42, 45, 46, 47,<br>48 | E10, E9, F7,<br>F10, F9,<br>G10, J2, K3,<br>J3, H4, J4, | FLASH ADD: These outputs provide the address<br>pins to the flash device that is used to store the<br>IEEE1149.1 tests.                                                                                                           |

| FLASH_DB[015]  |                                                                                                                   | A9, A8, B8,<br>A7, B7, C7,                              | FLASH DB: These inputs provide the stored<br>IEEE1149.1 test data within the flash device to the<br>AS91L1002 sequencer.                                                                                                          |

| FLASH_RD       | 50                                                                                                                |                                                         | FLASH READ: This output provides an active '0'<br>signal to indicate that the AS91L1002 wishes to<br>read data from the flash device.                                                                                             |

| TRST           | 22                                                                                                                | H2                                                      | TRST: This output signal provides the IEEE1149.1<br>TRST signal for the devices to be tested.                                                                                                                                     |

| TMS            | 21                                                                                                                | G2                                                      | TMS: This output signal provides the IEEE1149.1<br>TMS signal for the devices to be tested.                                                                                                                                       |

| тск            | 87                                                                                                                |                                                         | TCK: This output signal provides the IEEE1149.1<br>TCK signal for the devices to be tested. The clock<br>frequency is based upon the frequency of<br>oscillator to the AS91L1002 and is programmable<br>for each tests execution. |

| PIN NAME      | PIN NUMBER<br>LQFP                                            | PIN NUMBER<br>FPBGA | DESCRIPTION                                                                                                                                                           |

|---------------|---------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDO           | 20                                                            | G1                  | TDO: This output signal provides the IEEE1149.1 data for the devices to be tested. It should be connected to the TDI pin on the first device in the IEEE1149.1 chain. |

| TDI           | 19                                                            | G3                  | TDI: This input signal receives the IEEE1149.1 data from the devices to be tested. It should be connected to the TDO pin on the last device in the IEEE1149.1 chain.  |

| DEVICE_TCK    | 62                                                            | F8                  | Silicon TAP Port Signal                                                                                                                                               |

| DEVICE_TDI    | 4                                                             | A1                  | Silicon TAP Port Signal                                                                                                                                               |

| DEVICE_TDO    | 73                                                            | A10                 | Silicon TAP Port Signal                                                                                                                                               |

| DEVICE_TMS    | 15                                                            | F3                  | Silicon TAP Port Signal                                                                                                                                               |

| Signal Ground | 55,56, 89, 38,<br>86, 11, 26, 43,<br>59, 74, 95, 2,<br>17, 90 |                     |                                                                                                                                                                       |

| 3.3 V Supply  | 39, 91,23, 3,<br>18, 34, 51, 66,<br>82,54                     |                     |                                                                                                                                                                       |

Table 1 - Signal Description

www.alsc.com

# **Signal Functions**

| Signal Name    | Signal Function                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRST           | TRST: This output signal provides the IEEE1149.1 TRST signal for the devices to be tested.                                                                                                                            |

| TOE            | Test Output Enable: When this signal is taken to logic '0' all I/O on the device is<br>placed in HighZ.                                                                                                               |

| TMS            | TMS: This output signal provides the IEEE1149.1 TMS signal for the devices to be tested.                                                                                                                              |

| TDO            | TDO: This output signal provides the IEEE1149.1 data for the devices to be tested. It should be connected to the TDI pin on the first device in the IEEE1149.1 chain.                                                 |

| TDI            | TDI: This input signal receives the IEEE1149.1 data from the devices to be tested. It should be connected to the TDO pin on the last device in the IEEE1149.1 chain.                                                  |

| тск            | TCK: This output signal provides the IEEE1149.1 TCK signal for the devices to be tested. The clock frequency is based upon the frequency of oscillator to the AS91L1002 and is programmable for each tests execution. |

| SW_RUN         | Switch AS91L1002 Run: This signal when taken to logic '0' causes the AS91L1002 to reset. When the signal returns to logic '1' the AS91L1002 starts test execution.                                                    |

| RST_OUT        | RESET OUT: This output signal pulses low before the start of each test execution. It is<br>used to reset the Flash device to ensure that they are in a stable state before the<br>AS91L1002 access the stored data.   |

| POR            | Power on Reset: This signal when taken to logic '0' causes the AS91L1002 to reset.<br>When the signal returns to logic '1' the AS91L1002 starts test execution.                                                       |

| PASS_FAIL      | PASS FAIL: This output provides status of the test execution. When at logic'1' after test execution, the stored IEEE1149.1 test has failed due to data errors.                                                        |

| OSC_IN         | Oscillator Input: Provides the master clock into the AS91L1002, Max freq 66 MHz.                                                                                                                                      |

| FLASH_RD       | FLASH READ: This output provides an active '0' signal to indicate that the AS91L1002 wishes to read data from the flash device.                                                                                       |

| FLASH_DB[015]  | FLASH DB: These inputs provide the stored IEEE1149.1 test data within the flash.                                                                                                                                      |

| FLASH_ADD[023] | FLASH ADD: These outputs provide the address pins to the flash device that is used to store the IEEE1149.1 tests.                                                                                                     |

| BUSY_IDLE      | BUSY IDLE: This output indicates the state of the AS91L1002. When High, it indicates the AS91L1002 is active.                                                                                                         |

Table 2 - Signal Functions

## **Absolute Maximum Ratings**

| Parameter                                      | Maximum Range        |

|------------------------------------------------|----------------------|

| Supply Voltage (Vcc)                           | -0.3V to 5.5V        |

| DC Input Voltage (Vi)                          | -0.5V to Vcc +0.5V   |

| Max sink current when Vi = -0.5V               | -20mA                |

| Max source current when Vi = Vcc + 0.5V        | +20mA                |

| Max Junction Temperature with power applied Tj | +125 degrees C       |

| Max Storage temperature                        | -55 to +150 degree C |

Table 3 - Absolute Maximum Ratings

Note: Stress above the stated maximum values may cause irreparable damage to the device, correct operation of the device at these values is not guaranteed.

## **Recommended Operating Conditions**

| Parameter                                | Operating Range                       |  |

|------------------------------------------|---------------------------------------|--|

| Supply Voltage (Vcc)                     | 3.0V to 3.6V                          |  |

| Input Voltage (Vi)                       | 0V to Vcc                             |  |

| Output Voltage (Vo)                      | 0V to Vcc                             |  |

| Operating Temperature (Ta)<br>Commercial | 0 C to 70 C                           |  |

| Industrial (Ta)                          | -40 deg C to +85 deg C, 3.00V to 3.6V |  |

#### **Table 4 - Recommended Operating Conditions**

### **DC Electrical Characteristics**

| Symbol          | Parameter                      | Min   | Max          | Condition                            |

|-----------------|--------------------------------|-------|--------------|--------------------------------------|

| V <sub>IH</sub> | Minimum High Input<br>Voltage  | 2.0   | 5.25         |                                      |

| V <sub>IL</sub> | Maximum Low Input<br>Voltage   | -0.3V | 0.8V         |                                      |

|                 |                                |       |              |                                      |

| Symbol          | Parameter                      | _     | Value        | Condition                            |

| V <sub>OH</sub> | Minimum High Output<br>Voltage |       |              | loh=24mA or 8mA as<br>defined by pin |

| V <sub>OL</sub> | Minimum Low Output<br>Voltage  |       |              | lol=24mA or 8mA as<br>defined by pin |

| l <sub>oz</sub> | Tristate output leakage        |       | -10 or 10 mA |                                      |

| Symbol           | Parameter                           | Min | Max  | Condition                |

|------------------|-------------------------------------|-----|------|--------------------------|

| I <sub>cc</sub>  | Maximum quiescent<br>supply current |     | 2mA  |                          |

| I <sub>ccd</sub> | Maximum dynamic<br>supply current   |     | 80mA | TCK freq equal to 10 MHz |

| Table 5 - AS91L1002 | 2 DC Electrical | Characteristics |

|---------------------|-----------------|-----------------|

|---------------------|-----------------|-----------------|

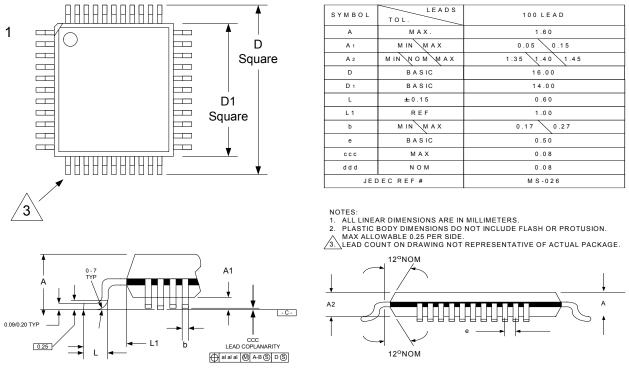

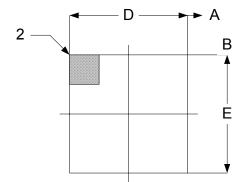

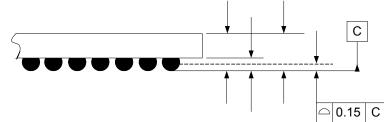

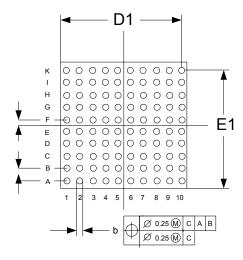

## **Packaging Information**

The AS91L1002 is available in a 100-pin LQFP or a 100-pin FPBGA lead free package.

Figure 4 - LQFP-100

| Revisions |                                                           |       |          |  |  |

|-----------|-----------------------------------------------------------|-------|----------|--|--|

| REV.      | DESCRIPTION                                               | ECN   | DATE     |  |  |

| А         | Initial document release.                                 | 91253 | 12-04-01 |  |  |

| В         | Updated ball coplanarity limits from<br>0.20mm to 0.15mm. |       |          |  |  |

|           |                                                           |       |          |  |  |

|           |                                                           |       |          |  |  |

| DIMENSIONS     |                   |      |      |  |

|----------------|-------------------|------|------|--|

| SYMBOL         | MIN.              | NOM. | MAX. |  |

| A              |                   |      | 1.70 |  |

| A1             | 0.30              |      |      |  |

| A2             | 0.25              |      | 1.10 |  |

| b              | 0.50              | 0.60 | 0.70 |  |

| D              | 11.00 BSC         |      |      |  |

| D1             | 9.00 BSC          |      |      |  |

| E              | 11.00 BSC         |      |      |  |

| E1             | 9.00 BSC          |      |      |  |

| е              | 1.00              |      |      |  |

| PACKAGE NUMBER | FBGA0100-11F      |      |      |  |

| JEDEC REF #    | MO-192 VAR. AAC-1 |      |      |  |

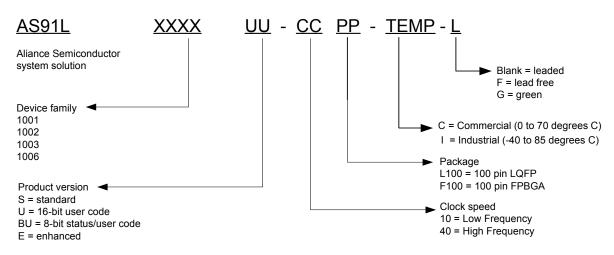

### **Device Selector Guide and Ordering Information**

#### www.alsc.com

| Part Number           | Description                                           | Availability                                |

|-----------------------|-------------------------------------------------------|---------------------------------------------|

| AS91L1002S – 10L100-C | JTAG Test Sequencer, 100-pin LQFP package, commercial | now                                         |

| AS91L1002S – 10L100-I | JTAG Test Sequencer, 100-pin LQFP package, industrial | now                                         |

| AS91L1002S – 10F100-C | JTAG Test Sequencer 100-pin FPBGA package, commercial | Please Contact<br>Alliance<br>Semiconductor |

| AS91L1002S – 10F100-I | JTAG Test Sequencer 100-pin FPBGA package, industrial | Please Contact<br>Alliance<br>Semiconductor |

Table 6 - Valid Part Number Combination

| Device<br>Master | Description          | Package                  | e Options |

|------------------|----------------------|--------------------------|-----------|

|                  |                      | FPBGA-100<br>(1mm pitch) | LQFP-100  |

| AS91L1001        | JTAG Test Controller | х                        | х         |

| AS91L1002        | JTAG Test Sequencer  | х                        | х         |

| AS91L1003U       | 3-Port Gateway       | х                        | х         |

| AS91L1006BU      | 6-Port Gateway       | х                        | х         |

Table 7 - JTAG Controller Product Family

www.alsc.com