## Satellite Tuner Front End LNA with AGC Preliminary Information

#### **Features**

- Single chip solution for satellite tuner LNA and AGC

- Provides for 30 dB minimum AGC

- Low DSB NF at maximum gain

- High signal handling at minimum gain

- Provides differential output drive

- ESD protection (Normal ESD handling procedures should be observed)

#### **Applications**

- Satellite receiver systems

- Data communications systems

- Master Antennae Distribution Systems

#### **Description**

The SL1914 is a wideband LNA with AGC designed primarily for application in satellite tuner front ends, offering high signal handling capability with low noise figure compatible with most common tuner input requirements.

The SL1914 is optimised to complement the SL1925, ZIF quadrature downconverter, integrating all the active RF circuitry within the tuner, in a highly compact, efficient solution, and offering a full 1-45 MS/s tuner capability.

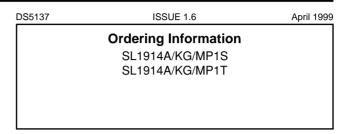

Figure 1 Block Diagram

### **SP1914** Preliminary Information

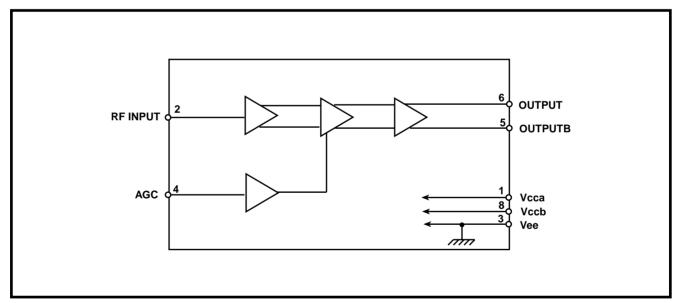

Figure 2 Pin Connections

#### **Quick Reference Data**

| Characteristic           |            | Units |

|--------------------------|------------|-------|

| Operating frequency      | 950 - 2150 | MHz   |

| Input DSB NF at max gain | 9          | dB    |

| Maximum conversion gain  | 20         | dB    |

| Minimum conversion gain  | -10        | dB    |

| IPIP3 <sub>2T</sub>      | 117        | dΒμV  |

| IPIP2 <sub>2T</sub>      | 127        | dBμV  |

Table 1

#### **Functional Description**

The SL1914 is a bipolar, low noise AGC amplifier designed primarily for application in satellite tuner front ends. It contains a low noise input amplifier, an AGC stage with a minimum of 30dB of gain control and a 75 Ohm output drive. It replaces all active circuitry in conventional architectures.

The typical key performance numbers under nominal load ambient and supply conditions are contained in table headed Quick Reference Data.

#### **Electrical Characteristics**

$T_{amb}$ = -20 $^{\circ}$ C to +70 $^{\circ}$ C,  $V_{ee}$ = 0V,  $V_{cc}$  = 5V±5%. These characteristics are guaranteed by either production test or design. They apply within the specified ambient temperature and supply voltage unless otherwise stated.

| Characteristic                                         | Pin  | Value |     | Units | Conditions |                                         |

|--------------------------------------------------------|------|-------|-----|-------|------------|-----------------------------------------|

|                                                        |      | Min   | Тур | Max   |            |                                         |

|                                                        |      |       |     |       |            |                                         |

| Supply current                                         | 1, 8 |       | 110 | 150   | mA         | AGC = 4V                                |

| Operating range                                        |      | 950   |     | 2150  | MHz        |                                         |

| Input impedance                                        | 2    |       | 75  |       | Ω          |                                         |

| IF input return loss                                   | 2    | 8     |     |       | dB         |                                         |

| Input DSB NF                                           | 2    |       | 9   | 11    | dB         | Maximum gain, AGC = 0.75V               |

| Variation in NF with gain                              |      |       |     | -1    | dB/dB      |                                         |

| setting                                                |      |       |     |       |            |                                         |

| Conversion gain                                        |      |       |     |       |            | Differential power gain into $75\Omega$ |

| minimum                                                |      |       |     | -10   | dB         | Vagc = 4V See note 1.                   |

| maximum                                                |      | 21    |     |       | dB         | Vagc = 0.75V                            |

|                                                        |      |       |     |       | dB         | AGC monotonic from Vee to Vcc           |

| Gain variation within                                  |      |       |     | +0.5  | dB         | Maximum channel bandwidth of            |

| channel                                                |      |       |     |       |            | 54MHz, within range 950 -<br>2150MHz    |

| Input referred 1 dB gain                               | 2    | 107   |     |       | dΒμV       | Minimum specified gain setting          |

| compression                                            |      |       |     |       |            |                                         |

| Input referred IP3                                     | 2    | 117   |     |       | dΒμV       | Minimum specified gain setting,         |

|                                                        |      |       |     |       |            | two tones at 99dBμV                     |

| Input referred IP2                                     | 2    | 125   |     |       | dΒμV       | Minimum specified gain setting,         |

|                                                        |      |       |     |       |            | two tones at 99dBμV                     |

| Variation in second and                                |      |       |     | -1    | dB/dB      |                                         |

| third order intermodulation intercept points with gain |      |       |     |       |            |                                         |

| setting                                                |      |       |     |       |            |                                         |

| AGC control slope                                      | 4    |       |     | 4:1   |            |                                         |

| variation                                              |      |       |     |       |            |                                         |

| AGC control input current                              | 4    |       |     | ±350  | μΑ         |                                         |

| Output impedance                                       | 5, 6 |       | 75  |       | Ω          |                                         |

| Output return loss                                     | 5, 6 | 6     |     |       | dB         |                                         |

Note 1: The AGC voltage should not exceed 4V.

3

#### **Absolute Maximum Ratings**

All voltages referred to Vee at 0V.

| Characteristics              | Min  | Max     | Unit | Conditions                  |

|------------------------------|------|---------|------|-----------------------------|

| Supply voltage               | -0.3 | 7       | V    |                             |

| IFIN and IFINB input voltage |      | 117     | dΒμV | Transient condition only    |

| All I/O port DC offset       | -0.3 | VCC+0.3 | V    | Except AGC (pin 4)          |

| AGC input DC offset          | -0.3 | 4       | V    |                             |

| Storage temperature          | -55  | 150     | °C   |                             |

| Junction temperature         |      | 150     | °C   |                             |

| Package thermal resistance,  |      | 39.8    | °C/W |                             |

| chip to case                 |      |         |      |                             |

| Package thermal resistance,  |      | 120     | °C/W |                             |

| chip to ambient              |      |         |      |                             |

| Power consumption at 5.25V   |      | 790     | mW   |                             |

| ESD protection               | 2    |         | kV   | Mil std-883 latest revision |

|                              |      |         |      | method 3015 class 1         |

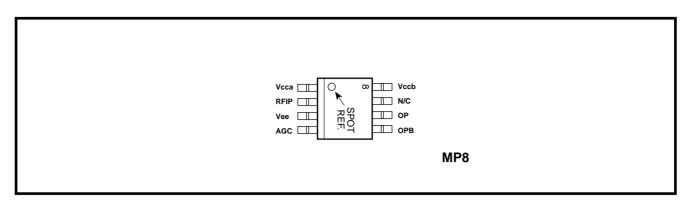

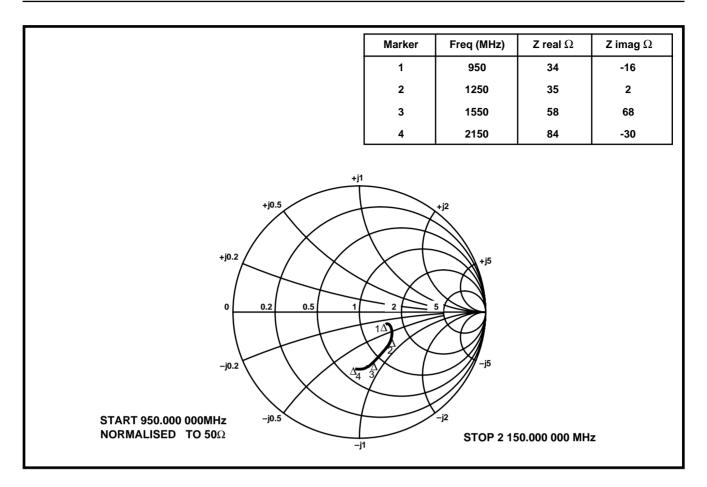

Figure 3 Input impedance (typical)

**Figure 4 Output impedance (typical)**

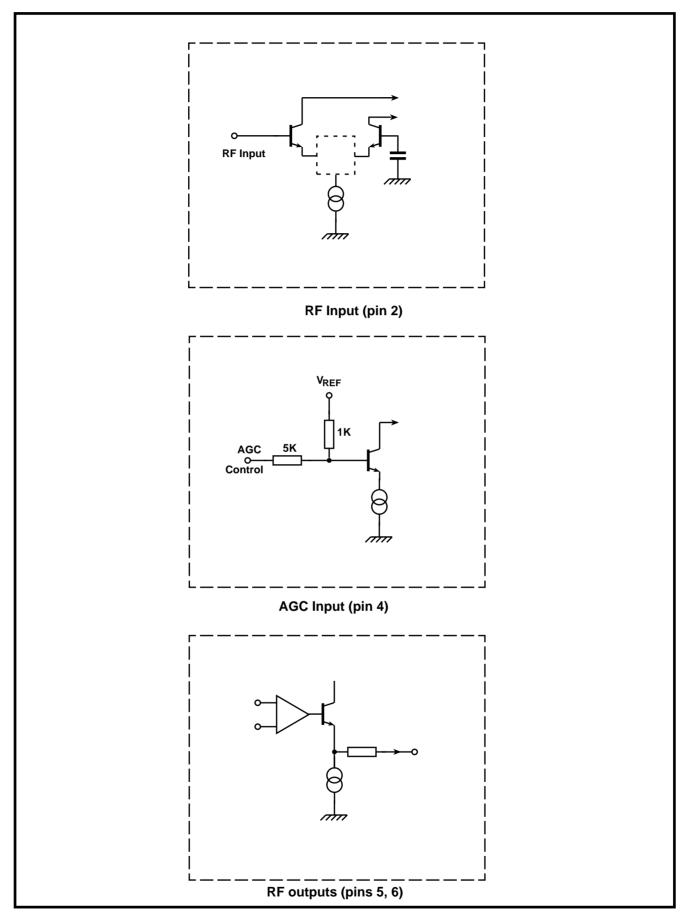

Figure 6 Input/Output interface circuit

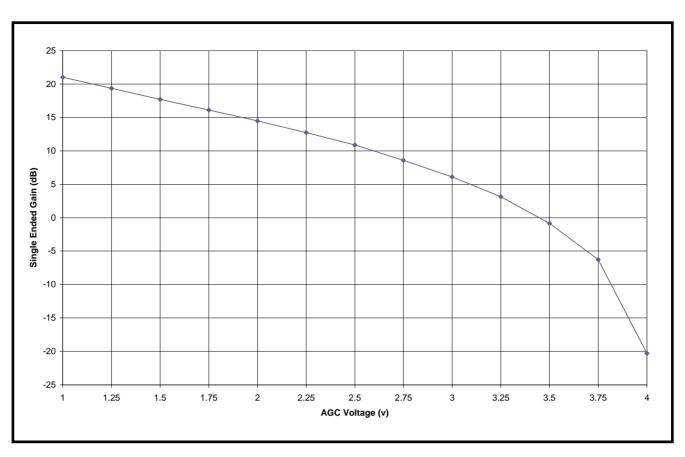

Figure 5 gain variation with AGC voltage (typical)

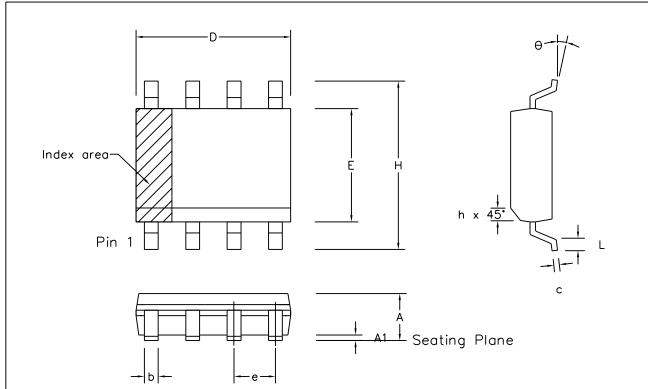

|                                   | Min          | Max        | Min       | Max   |  |  |

|-----------------------------------|--------------|------------|-----------|-------|--|--|

|                                   | mm           | mm         | inch      | inch  |  |  |

| Α                                 | 1.35         | 1.75       | 0.053     | 0.069 |  |  |

| A1                                | 0.10         | 0.25       | 0.004     | 0.010 |  |  |

| D                                 | 4.80         | 5.00       | 0.189     | 0.197 |  |  |

| Н                                 | 5.80         | 6.20       | 0.228     | 0.244 |  |  |

| E                                 | 3.80         | 4.00       | 0.150     | 0.157 |  |  |

| L                                 | 0.40         | 1.27       | 0.016     | 0.050 |  |  |

| е                                 | 1.27         | BSC        | 0.050 BSC |       |  |  |

| b                                 | 0.33         | 0.51       | 0.013     | 0.020 |  |  |

| С                                 | 0.19         | 0.25       | 0.008     | 0.010 |  |  |

| 0                                 | O°           | 8 <b>°</b> | 0°        | 8°    |  |  |

| h                                 | 0.25         | 0.50       | 0.010     | 0.020 |  |  |

|                                   | Pin Features |            |           |       |  |  |

| N                                 | 3            | 3          | 8         |       |  |  |

| Conforms to JEDEC MS-012AA Iss. C |              |            |           |       |  |  |

#### Notes:

- 1. The chamfer on the body is optional. If not present, a visual index feature, e.g. a dot, must be located within the cross—hatched area.

- 2. Controlling dimensions are in inches.

- 3. Dimension D do not include mould flash, protusion or gate burrs. These shall not exceed 0.006" per side.

- 4. Dimension E1 do not include inter-lead flash or protusion. These shall not exceed 0.010" per side.

- 5. Dimension b does not include dambar protusion / intrusion. Allowable dambar protusion shall be 0.004" total in excess of b dimension.

| © Zarlinl | k Semiconduc | ctor 2002 All ri | ghts reserved. |        |         |                          |   | Package Code                       |                     |

|-----------|--------------|------------------|----------------|--------|---------|--------------------------|---|------------------------------------|---------------------|

| ISSUE     | 1            | 2                | 3              | 4      | 5       |                          |   | Previous package codes             | Package Outline for |

| ACN       | 6745         | 201936           | 202595         | 203705 | 212424  | ZARLINK<br>SEMICONDUCTOR |   | 8 lead SOIC<br>(0.150" Body width) |                     |

| DATE      | 5Apr95       | 27Feb97          | 12Jun97        | 9Dec97 | 22Mar02 |                          | , | ,                                  |                     |

| APPRD.    |              |                  |                |        |         |                          |   | GPD00010                           |                     |

# For more information about all Zarlink products visit our Web Site at

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's  $I^2C$  components conveys a licence under the Philips  $I^2C$  Patent rights to use these components in an  $I^2C$  System, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2002, Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE