ISSUE 3

PM73121 AAL1GATOR II

AAL1GATOR II REFERENCE DESIGN

# PM73121

# AAL1GATOR II

# **REFERENCE DESIGN**

**ISSUE 3**

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

# **CONTENTS**

| 1 | FEAT | URES.  |                                         | 1  |

|---|------|--------|-----------------------------------------|----|

| 2 | OVER | VIEW.  |                                         | 2  |

| 3 | DEVE | LOPM   | ENT DESCRIPTION                         | 4  |

|   | 3.1  | COM    | ET VERSION OF REFERENCE DESIGN          | 4  |

|   | 3.2  | TQUA   | D/EQUAD VERSION OF REFERENCE DESIGN     | 6  |

| 4 | HIGH | LEVEI  | L DESIGN                                | 8  |

|   | 4.1  | AAL1   | GATOR II PLUS COMET DESIGN              | 8  |

|   |      | 4.1.1  | MICROPROCESSOR AND MEMORY SYSTEM        | 11 |

|   |      | 4.1.2  | FIELD PROGRAMMABLE GATE ARRAY (FPGA)    | 18 |

|   |      | 4.1.3  | CLOCK AND POWER SUPPLY CIRCUITRY        | 22 |

|   |      | 4.1.4  | UTOPIA INTERFACE                        | 22 |

|   |      | 4.1.5  | ADDITIONAL CONNECTIONS                  | 24 |

|   |      | 4.1.6  | LINE INTERFACE                          | 26 |

|   |      | 4.1.7  | ADDITIONAL COMET CONNECTIONS            | 26 |

|   |      | 4.1.8  | COMET CONFIGURATION                     | 29 |

|   |      | 4.1.9  | AAL1GATOR II CONFIGURATION              | 29 |

|   |      | 4.1.10 | ) THE JTAG PORT                         | 29 |

|   | 4.2  | AAL1   | GATOR II PLUS TQUAD/EQUAD DESIGN        |    |

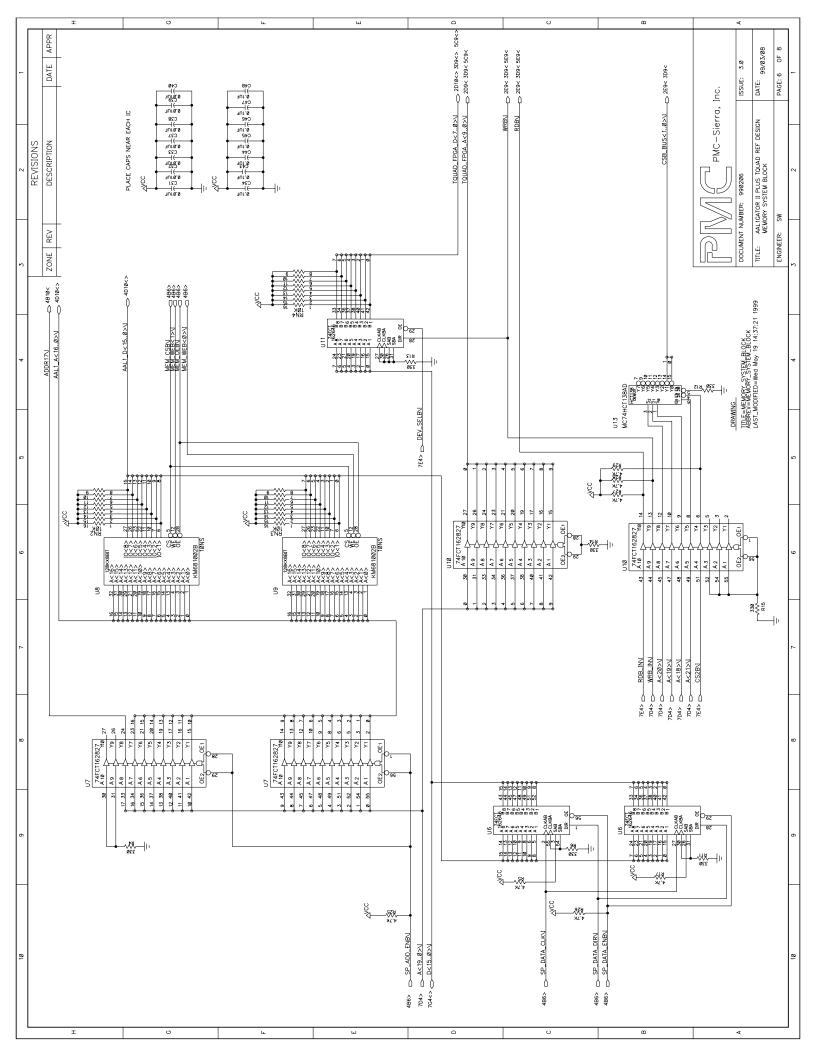

|   |      | 4.2.1  | MICROPROCESSOR AND MEMORY SYSTEM        | 30 |

|   |      | 4.2.2  | LINE SIDE INTERFACE TO THE AAL1GATOR II | 30 |

|   |      | 4.2.3  | LINE INTERFACE                          |    |

ISSUE 3

|   |       | 4.2.4 ADDITIONAL CONNECTIONS FOR THE TQUAD DEVICE |

|---|-------|---------------------------------------------------|

|   |       | 4.2.5 TQUAD/EQUAD CONFIGURATION                   |

| 5 | MEMO  | ORY MAP AND REGISTER DEFINITIONS                  |

| 6 | SOFT  | WARE CONFIGURATION                                |

|   | 6.1   | AAL1GATOR II CONFIGURATION                        |

|   | 6.2   | COMET CONFIGURATION43                             |

|   | 6.3   | TQUAD/EQUAD CONFIGURATION45                       |

|   | 6.4   | FPGA CONFIGURATION45                              |

| 7 | IMPLE | EMENTATION DESCRIPTION46                          |

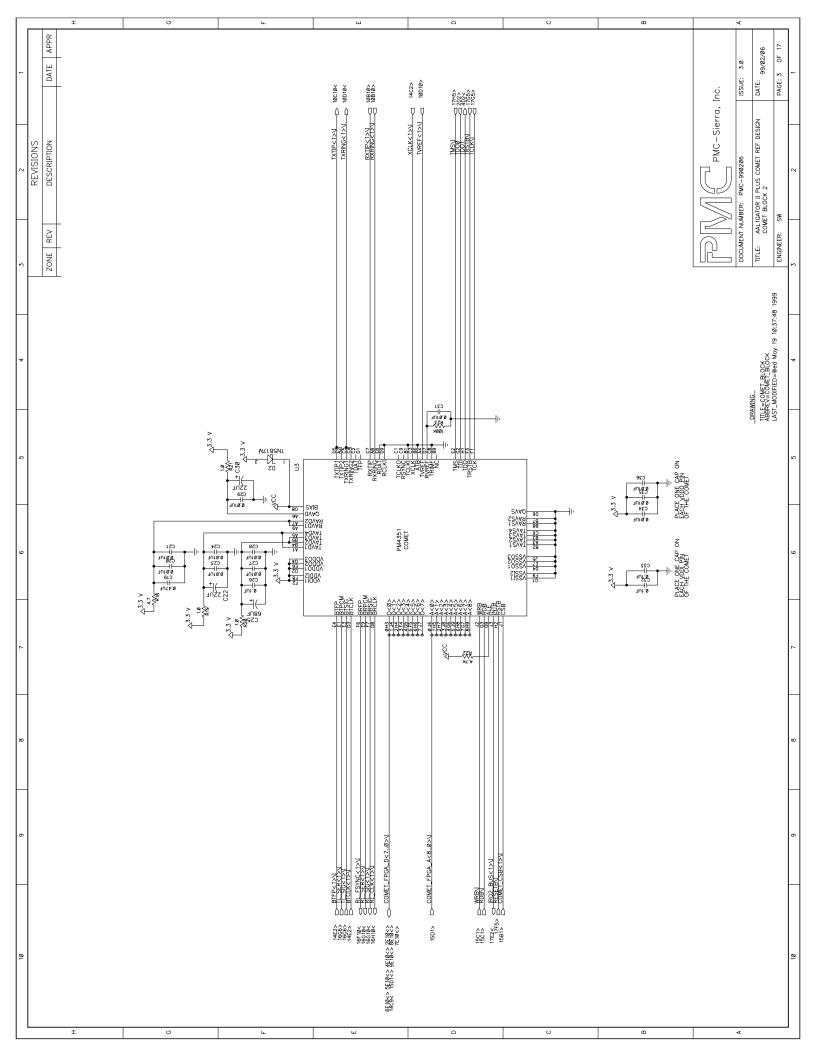

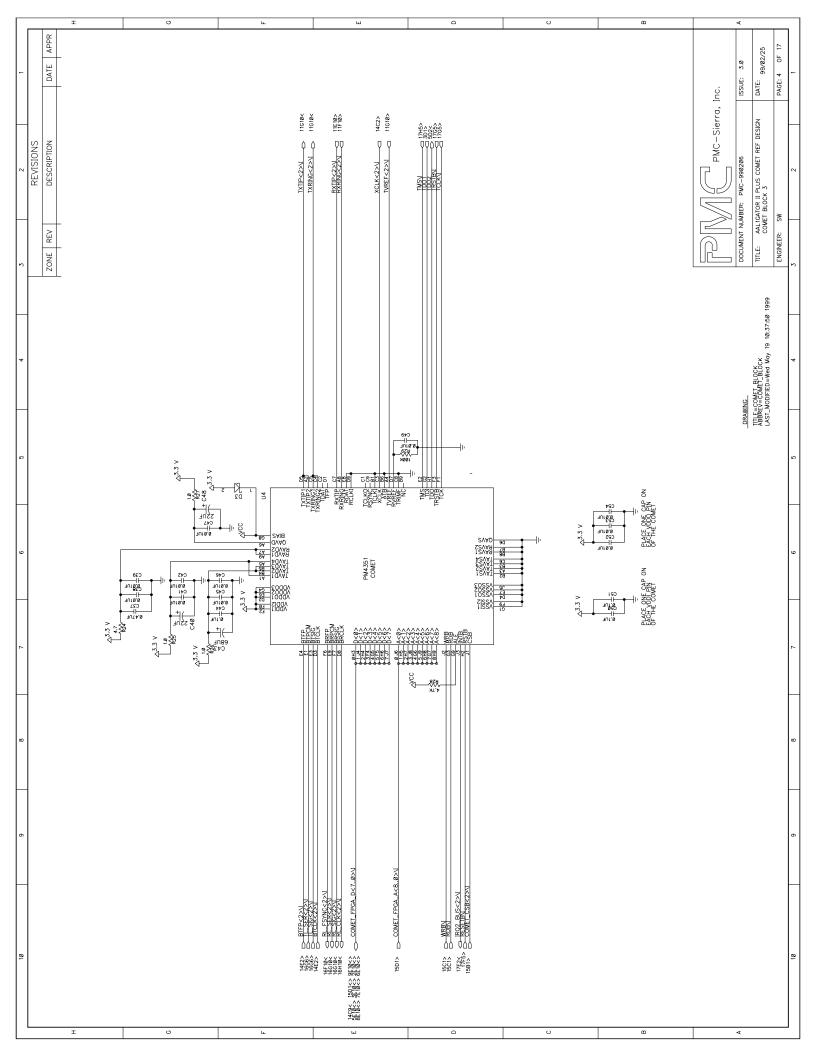

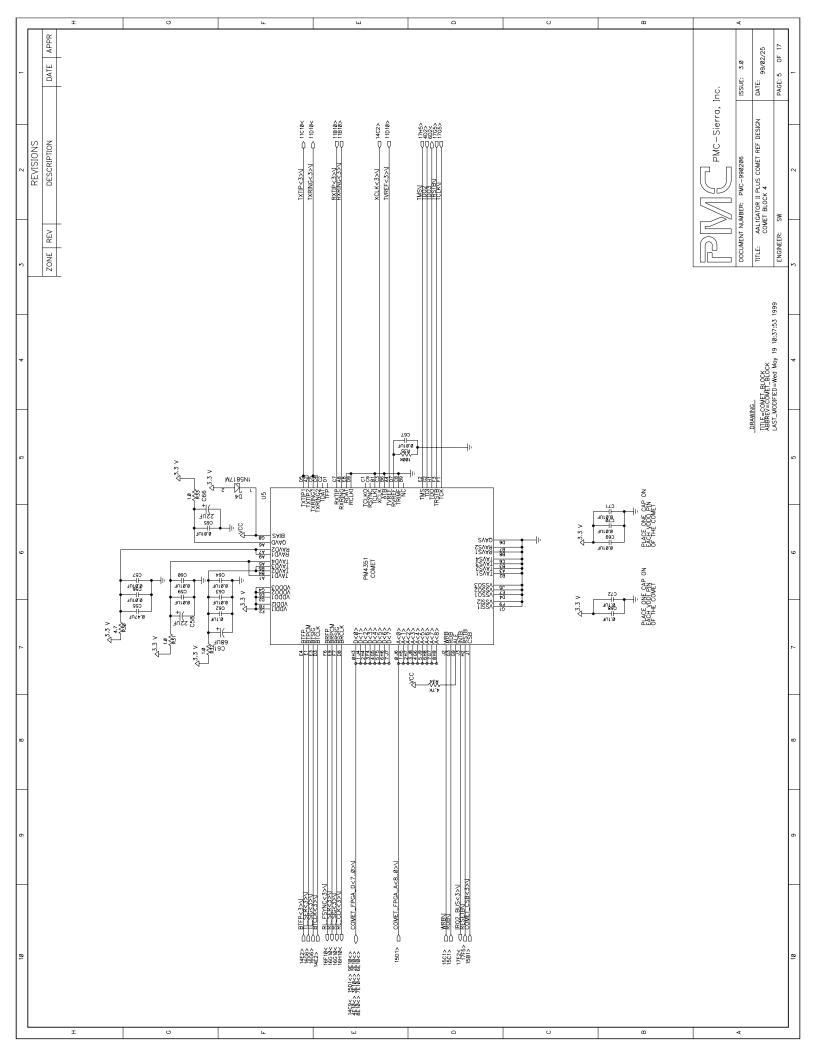

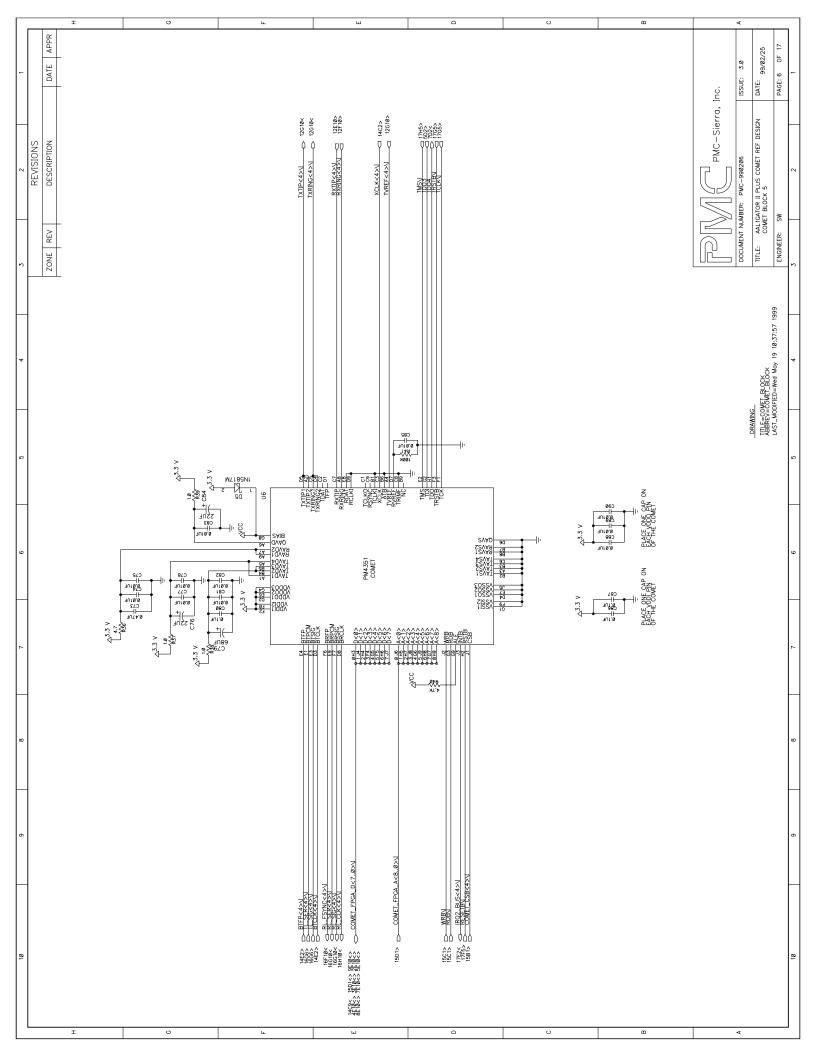

|   | 7.1   | COMET VERSION SCHEMATICS                          |

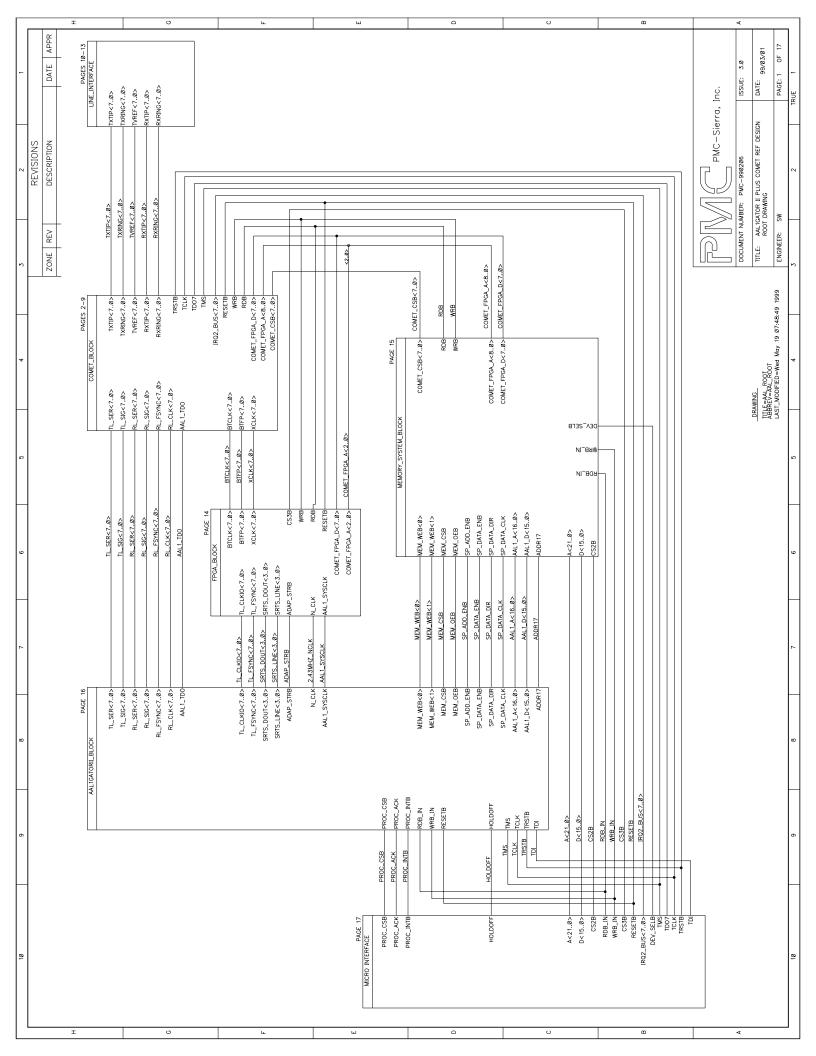

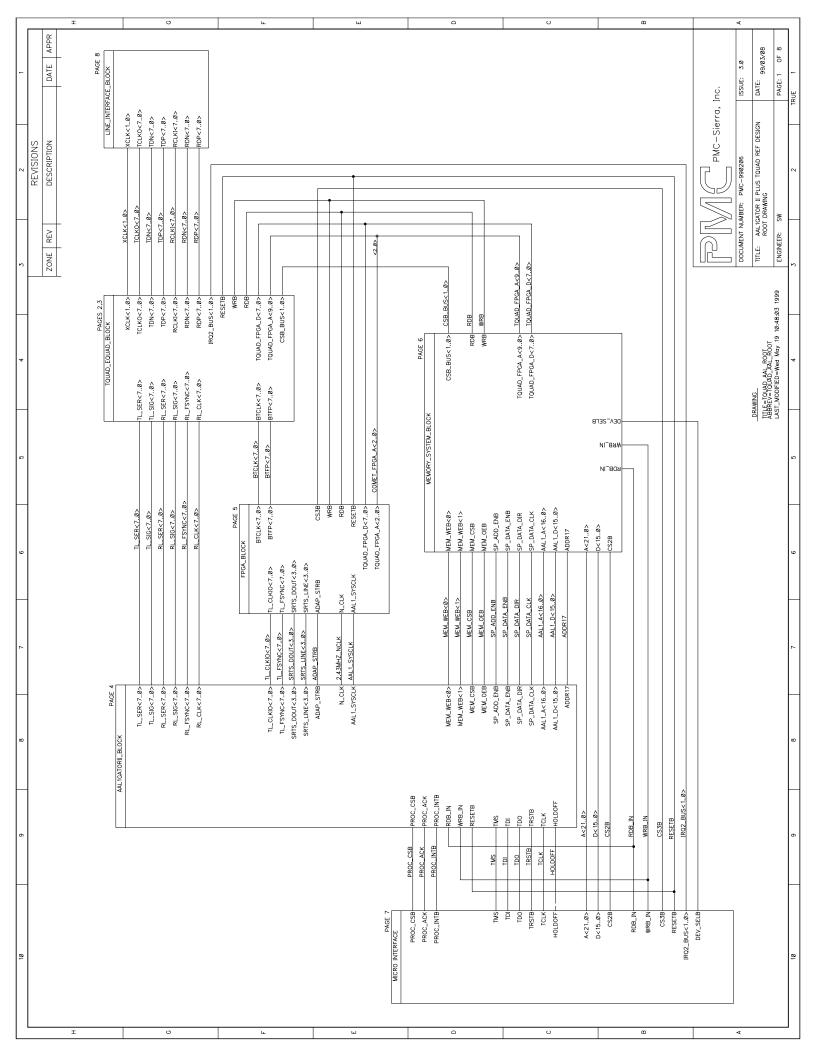

|   |       | 7.1.1 ROOT DRAWING, SHEET 1                       |

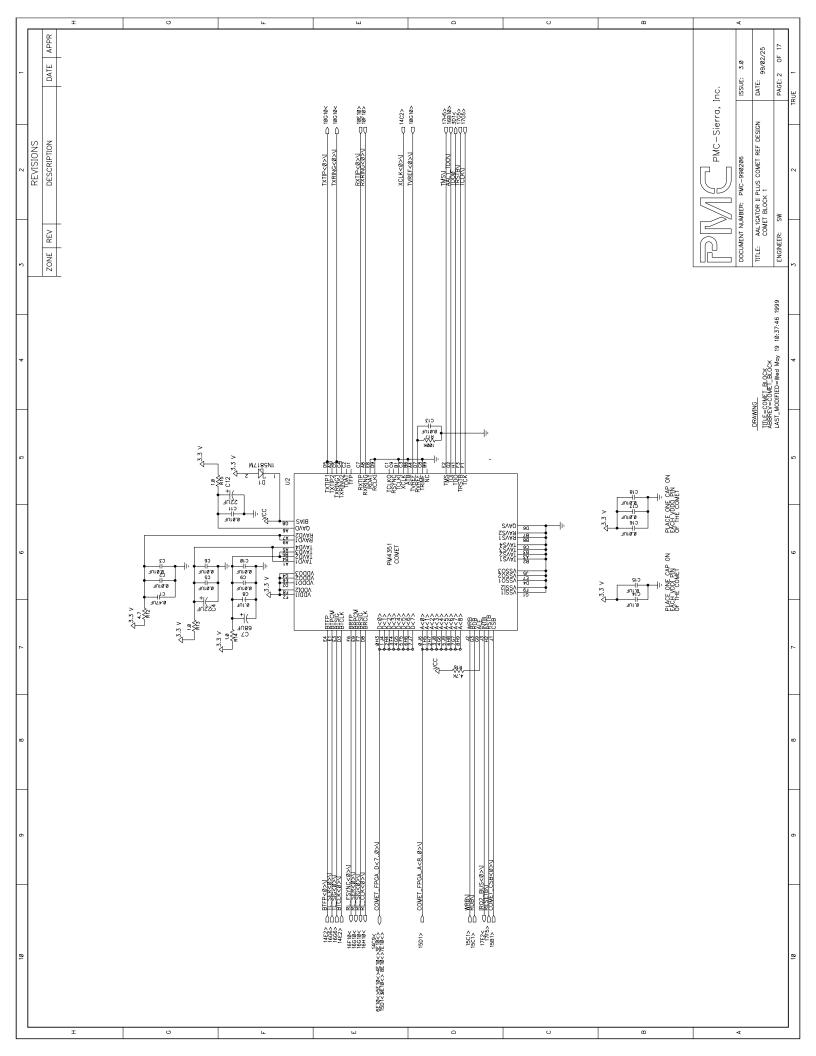

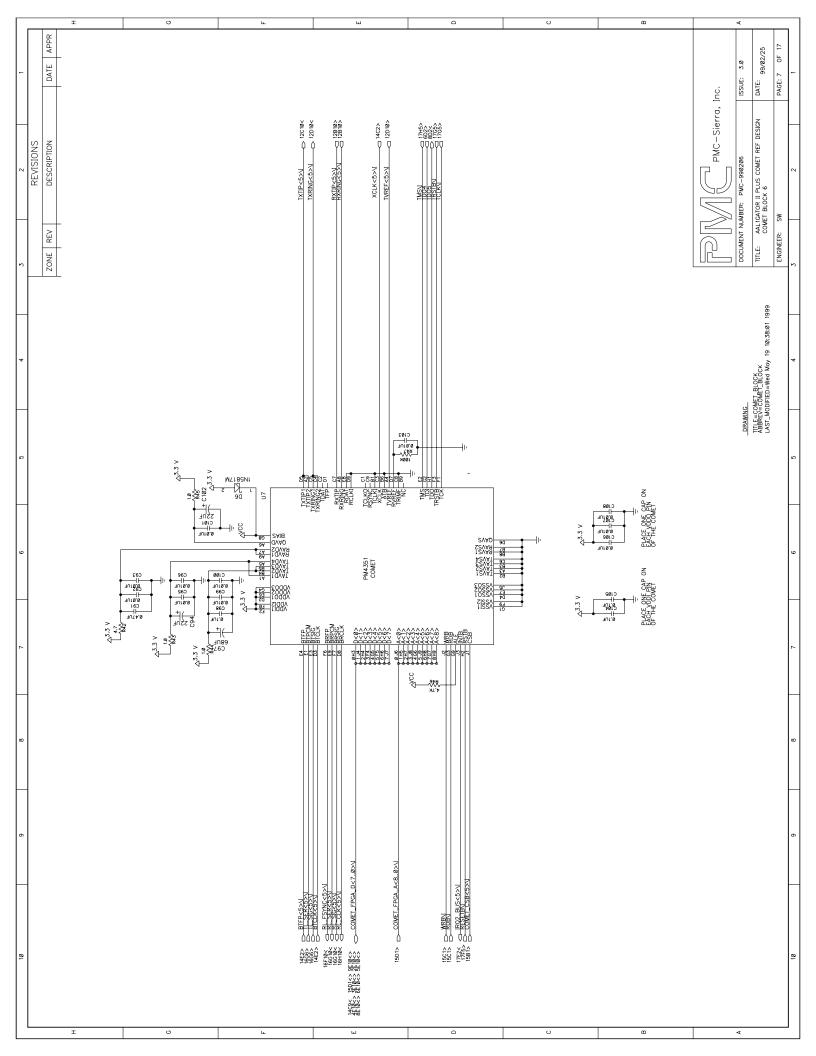

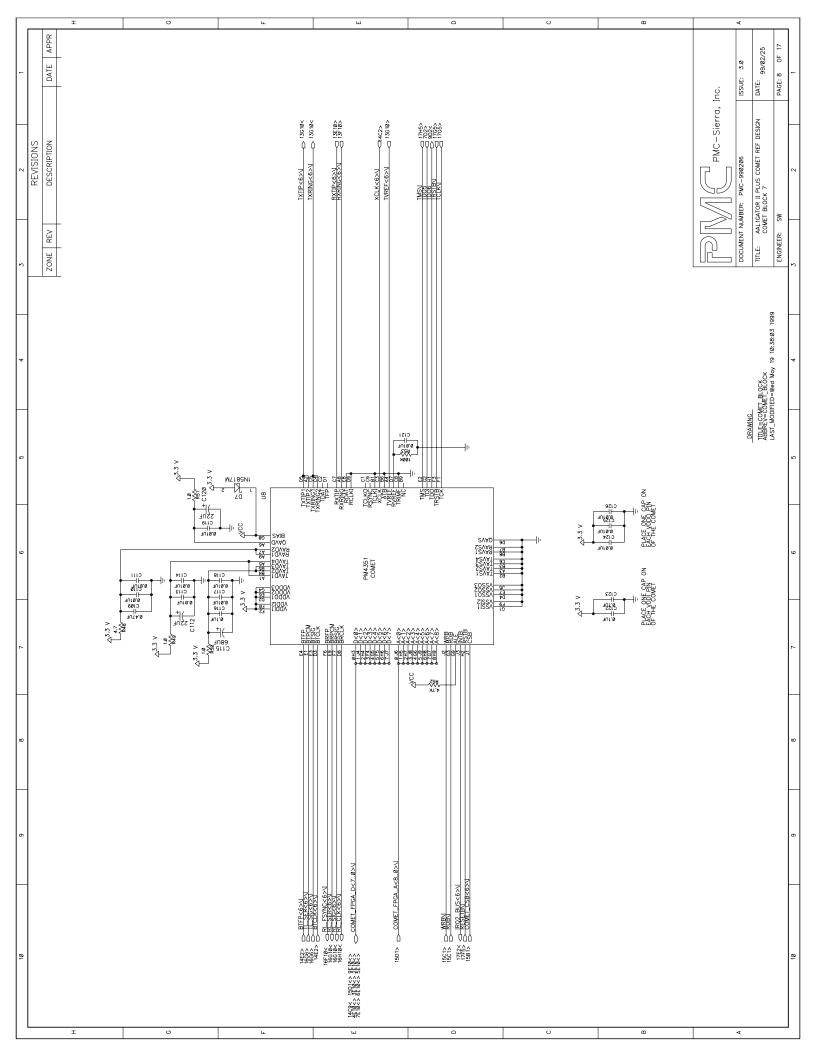

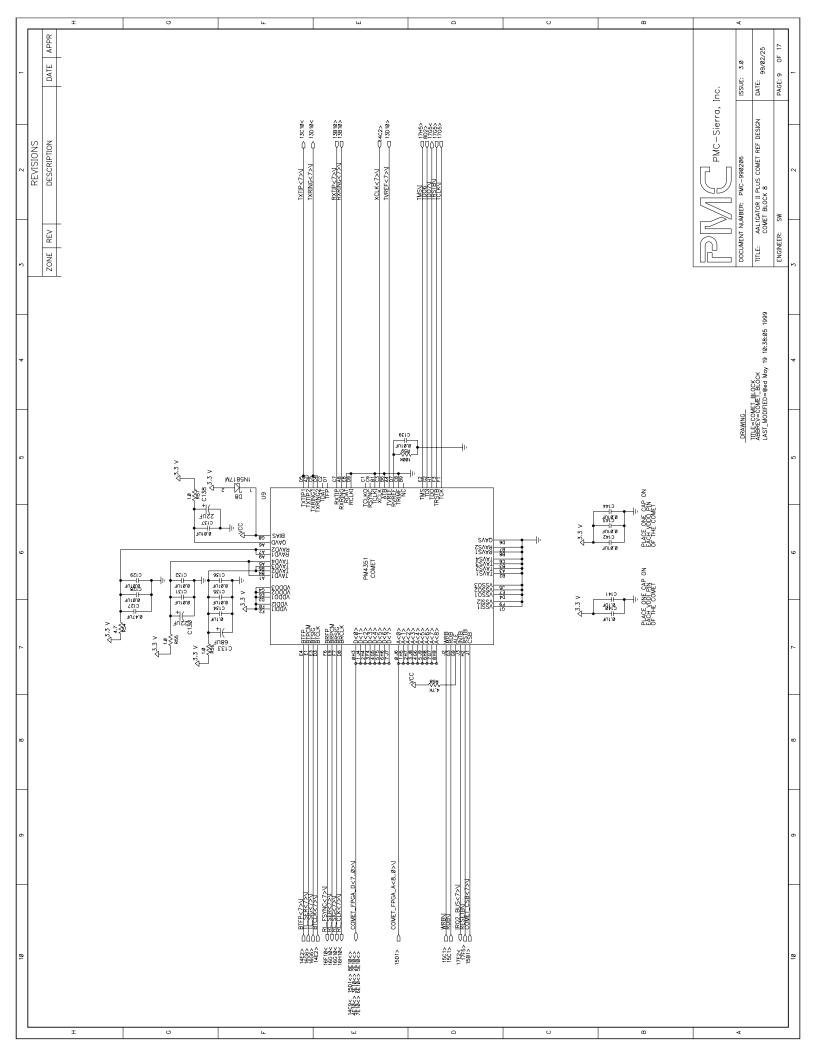

|   |       | 7.1.2 COMET BLOCK, SHEETS 2-9                     |

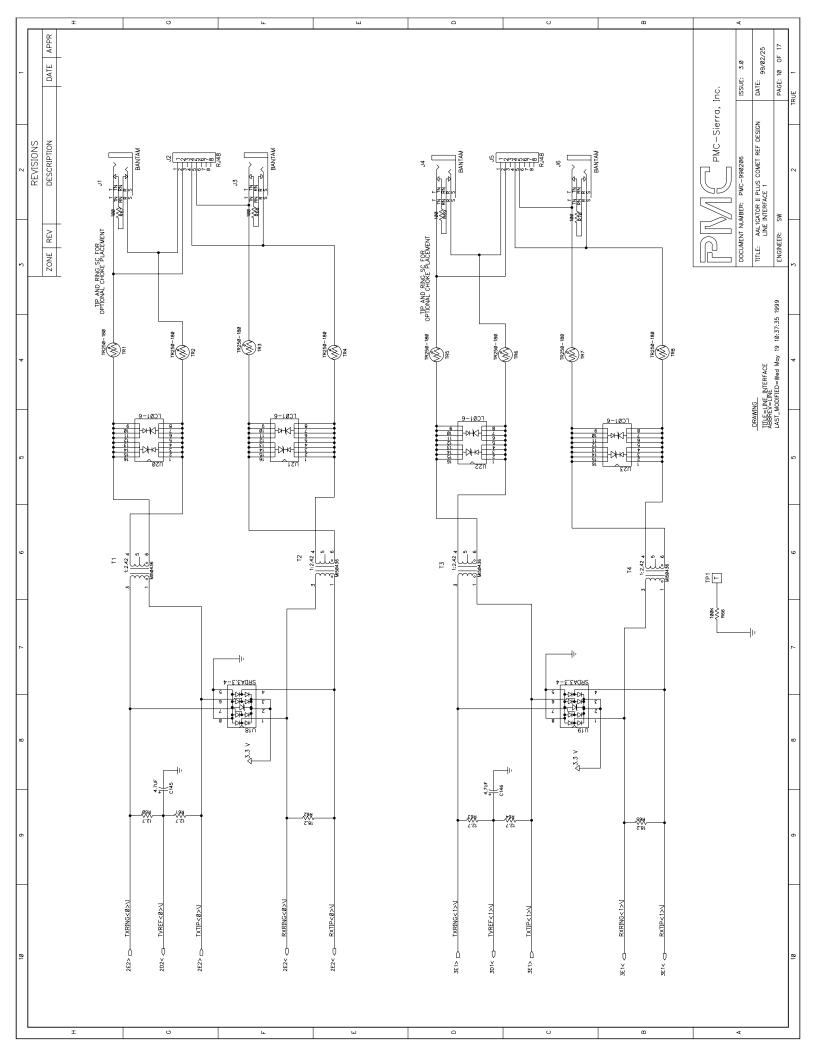

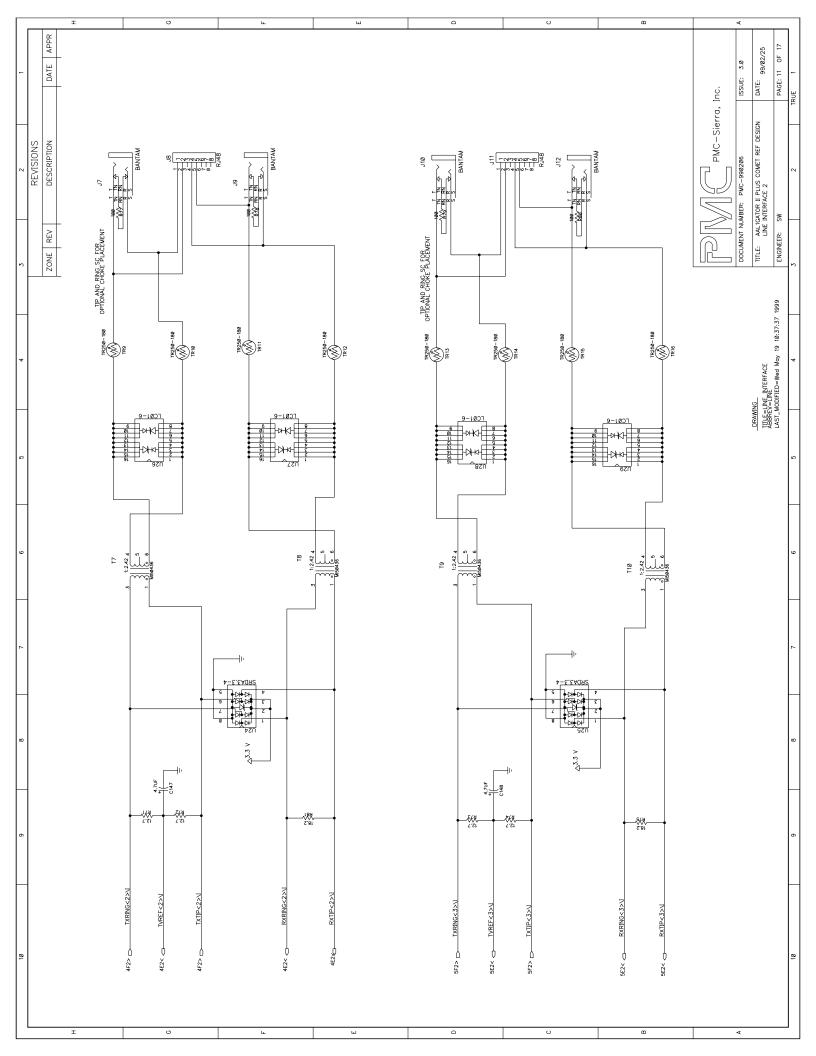

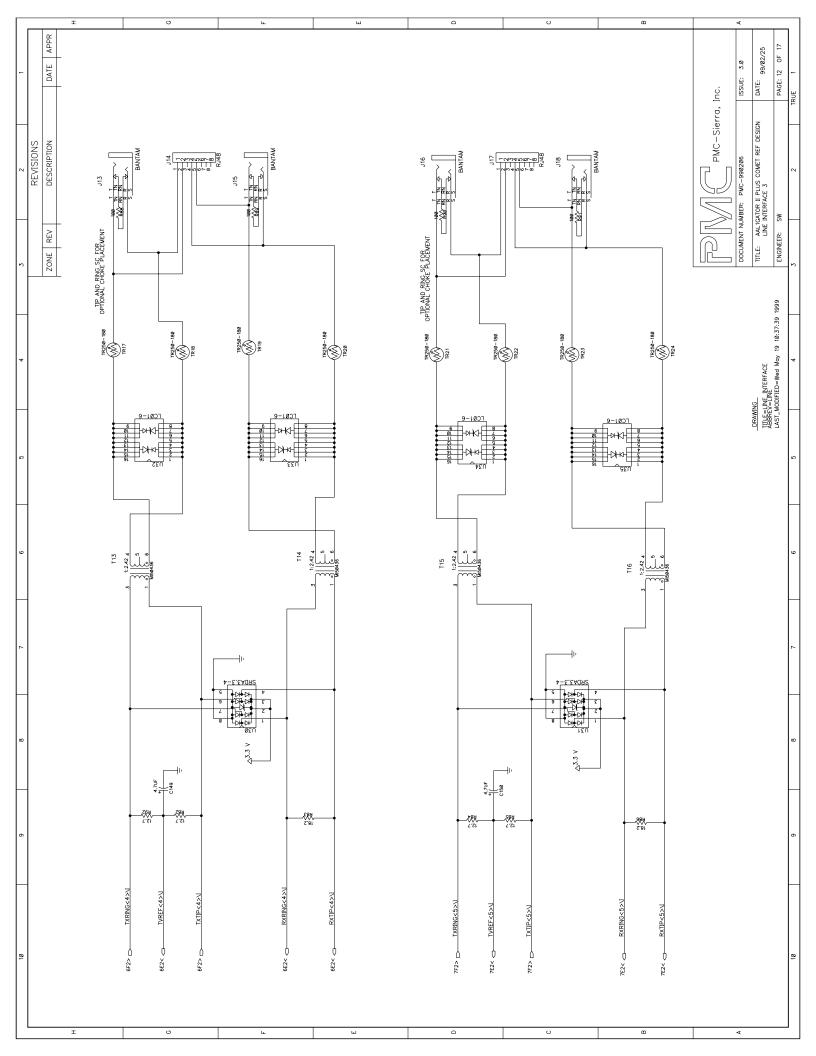

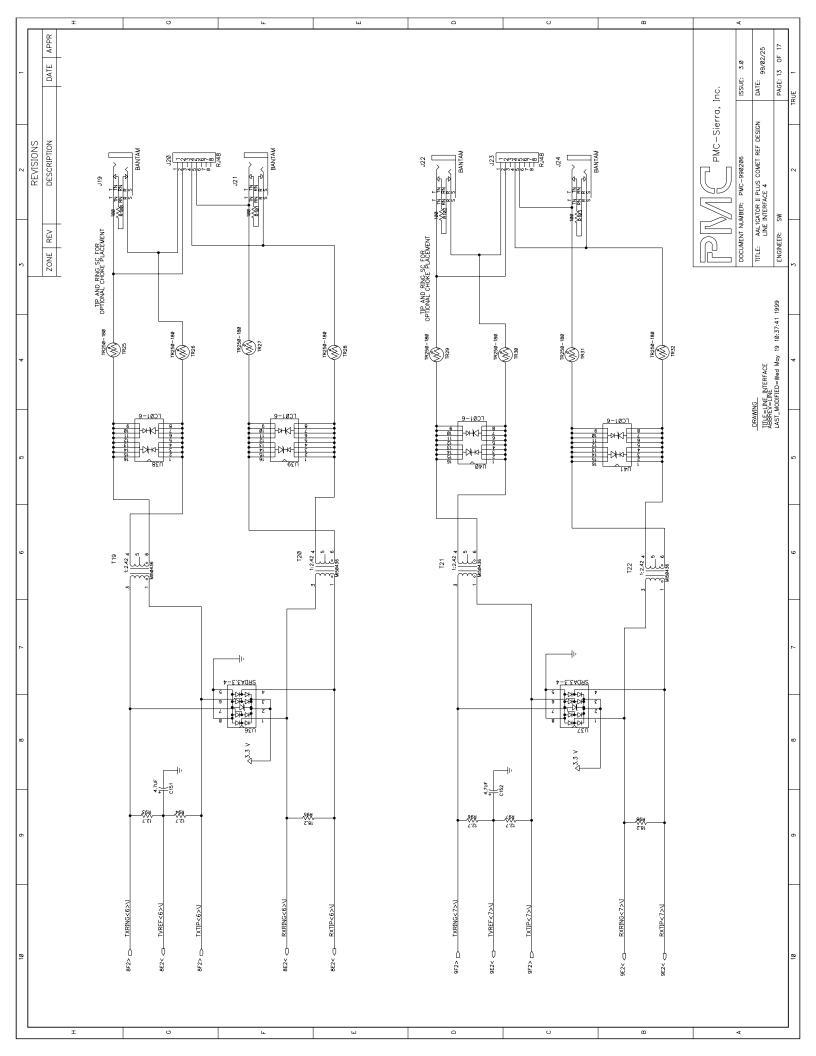

|   |       | 7.1.3 LINE INTERFACE, SHEETS 10-1346              |

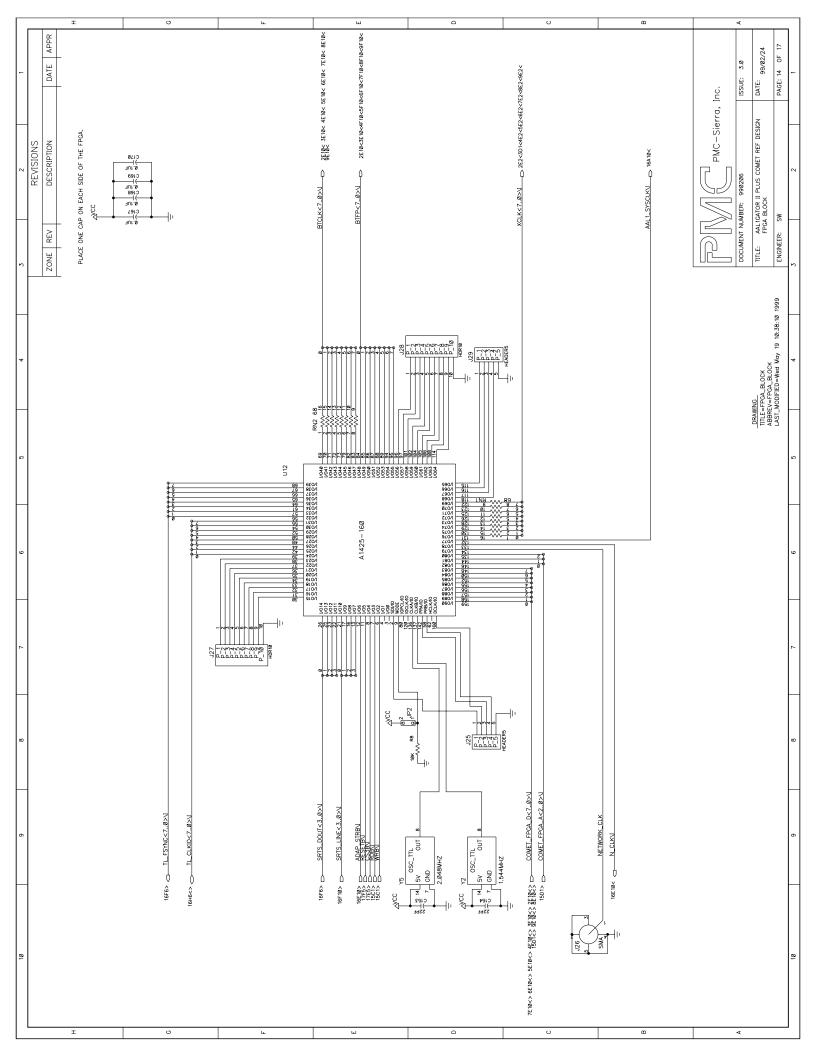

|   |       | 7.1.4 FPGA BLOCK, SHEET 14                        |

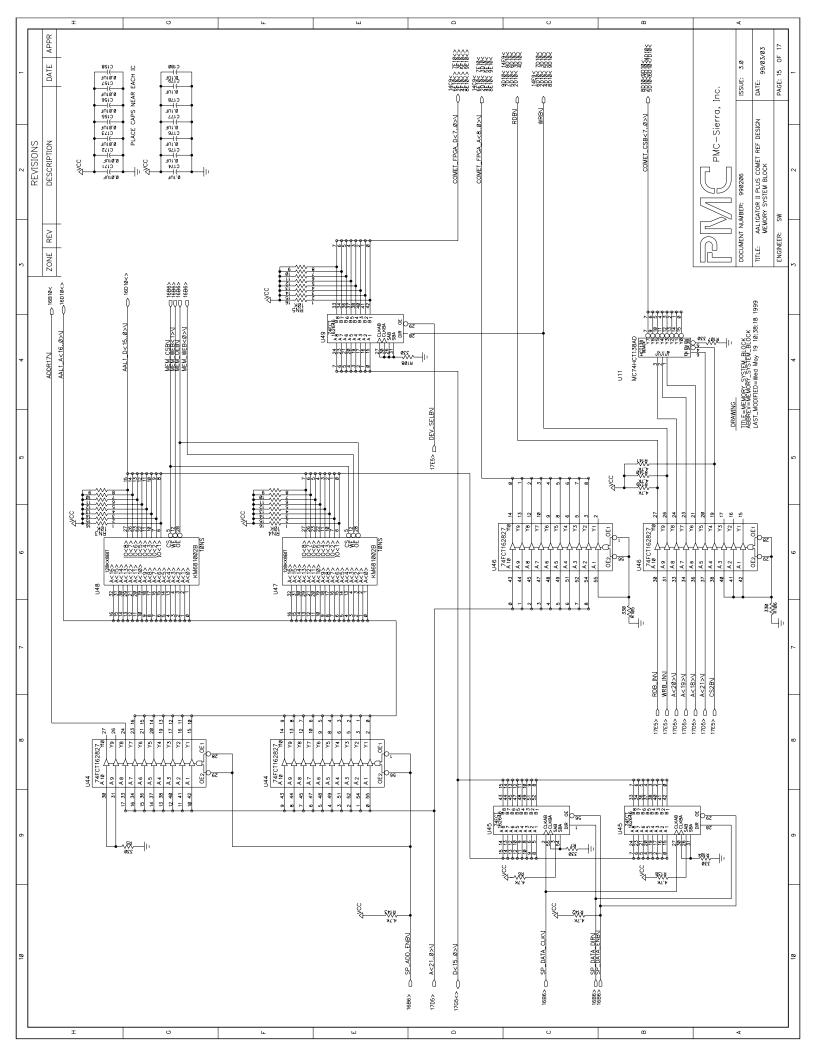

|   |       | 7.1.5 MEMORY SYSTEM BLOCK, SHEET 1546             |

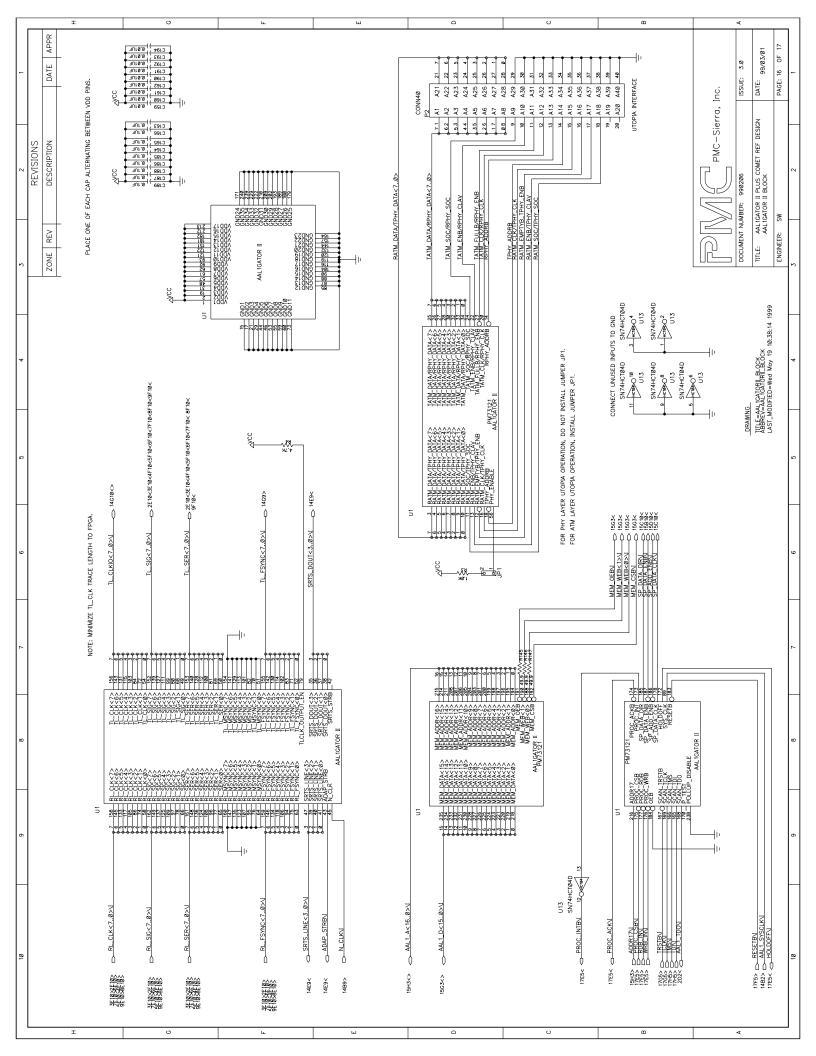

|   |       | 7.1.6 AAL1GATOR II BLOCK, SHEET 16                |

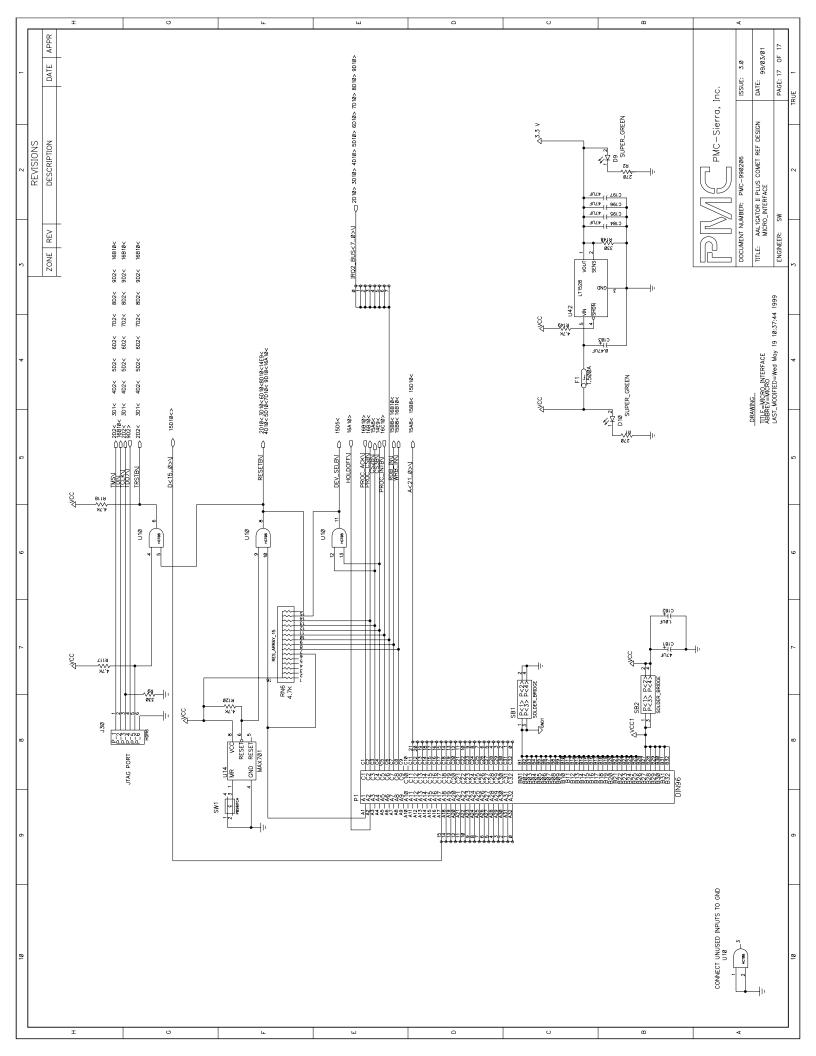

|   |       | 7.1.7 MICRO INTERFACE, SHEET 1747                 |

|   | 7.2   | TQUAD VERSION SCHEMATICS                          |

|   |       | 7.2.1 ROOT DRAWING, SHEET 1                       |

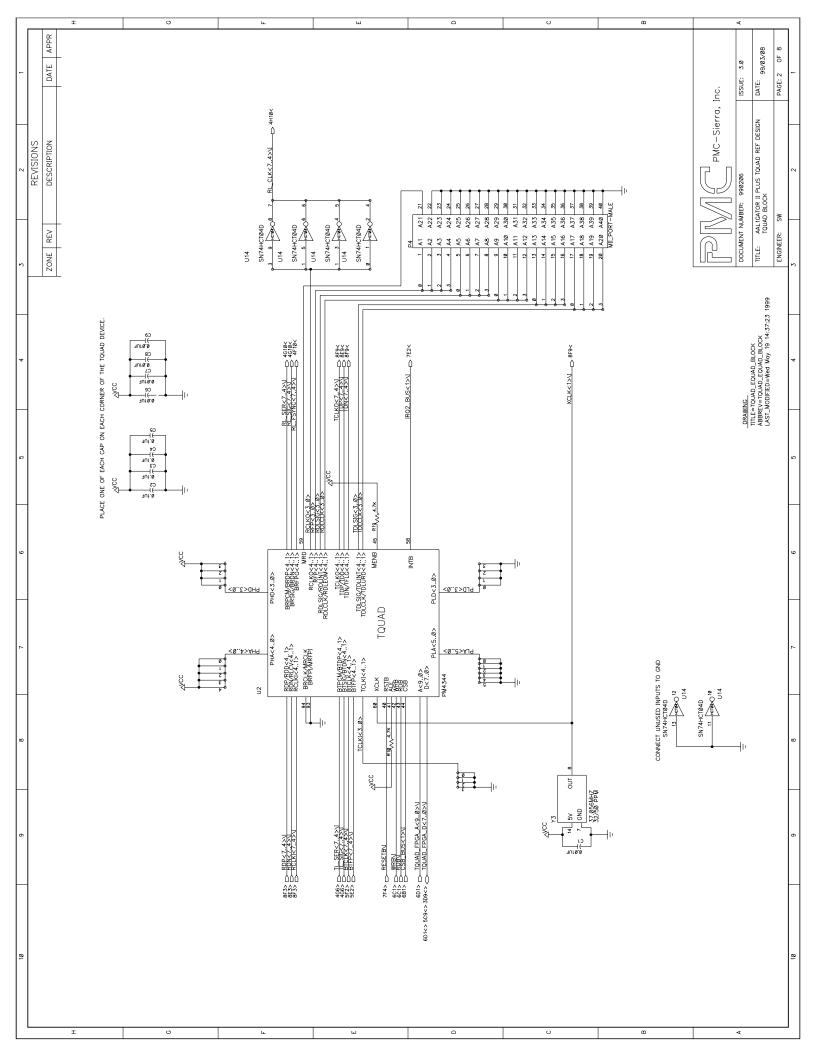

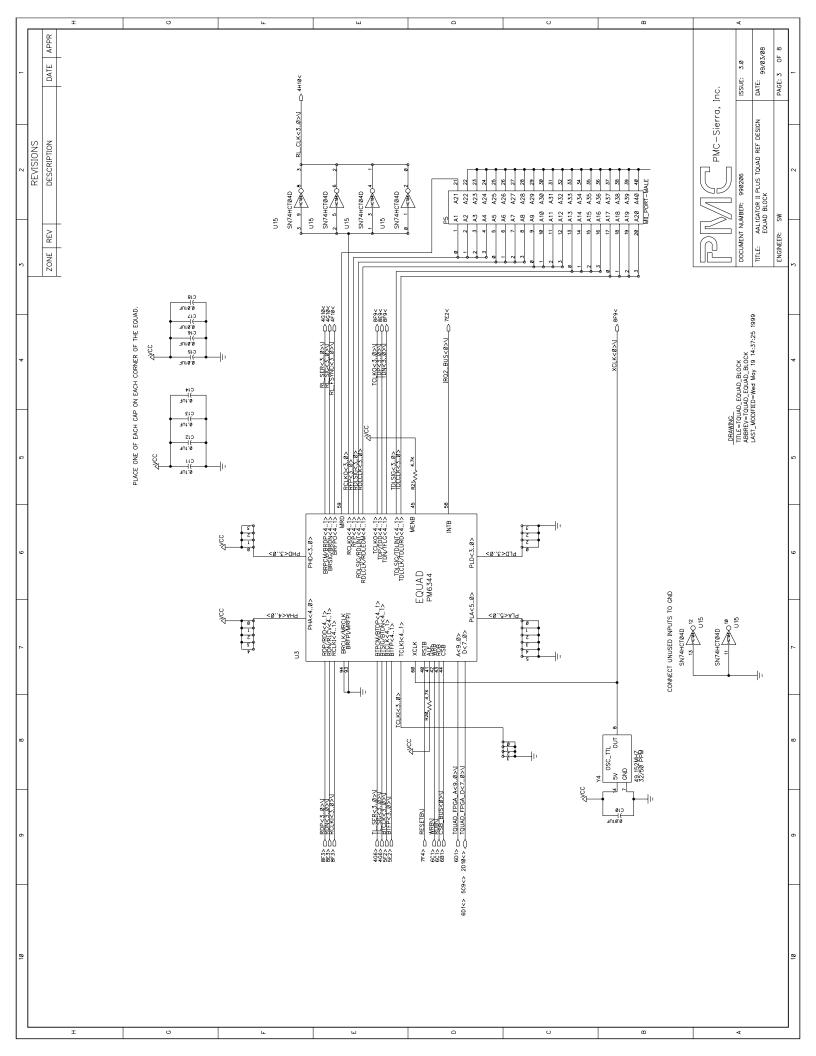

|   |       | 7.2.2 TQUAD/EQUAD BLOCK, SHEETS 2,347             |

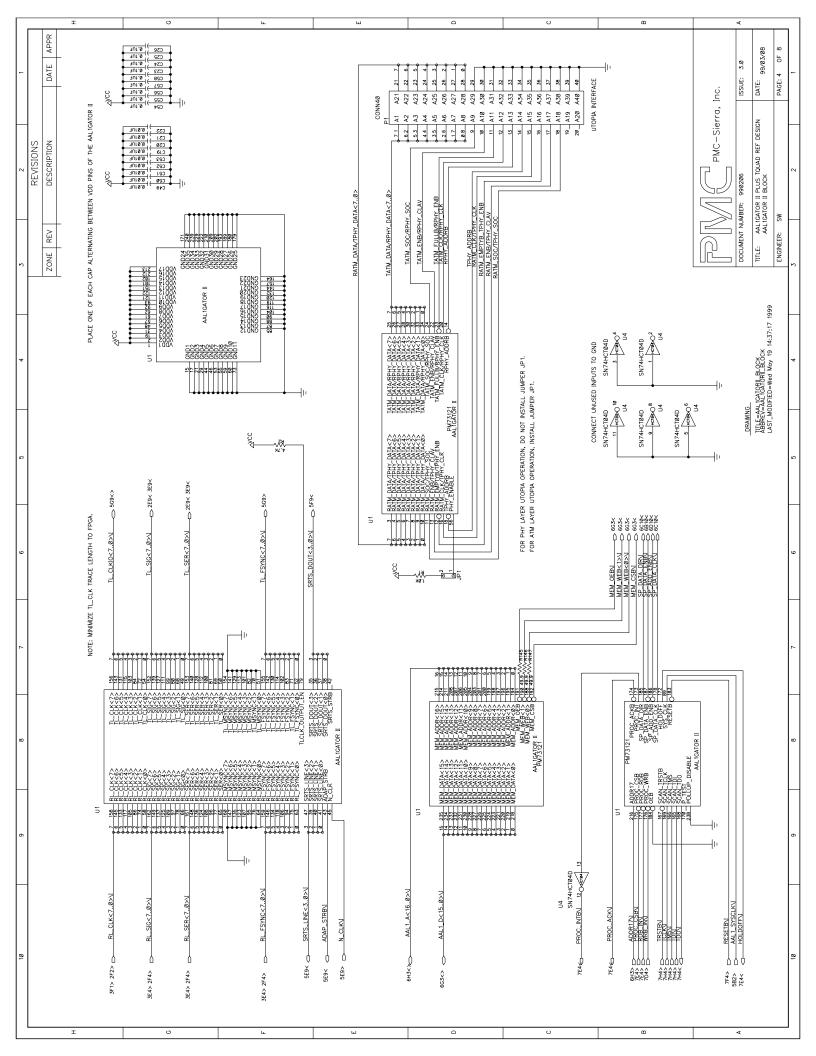

|   |       | 7.2.3 AAL1GATOR II BLOCK, SHEET 4                 |

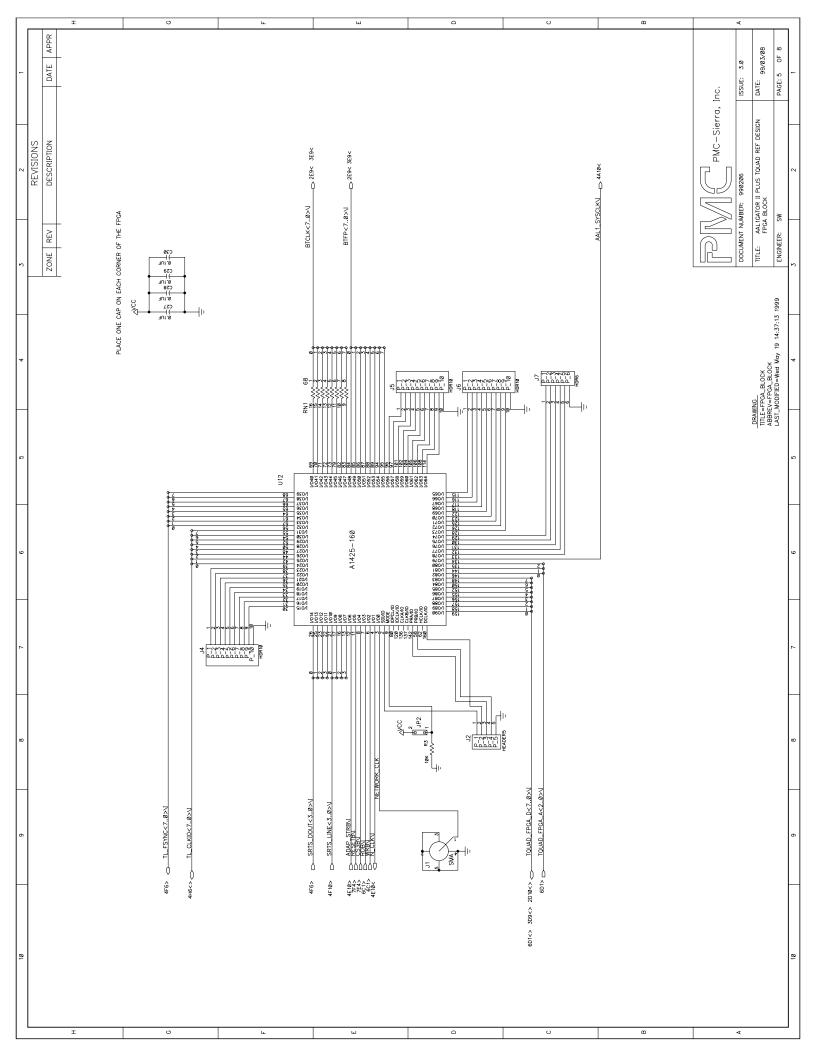

|   |       | 7.2.4 FPGA BLOCK, SHEET 5                         |

|   |       | 7.2.5 MEMORY SYSTEM BLOCK, SHEET 6                |

REFERENCE DESIGN

14

15

16

| PMC-990206 | ISSUE 3                            | AAL1GATOR II REFERENCE DESIGN |

|------------|------------------------------------|-------------------------------|

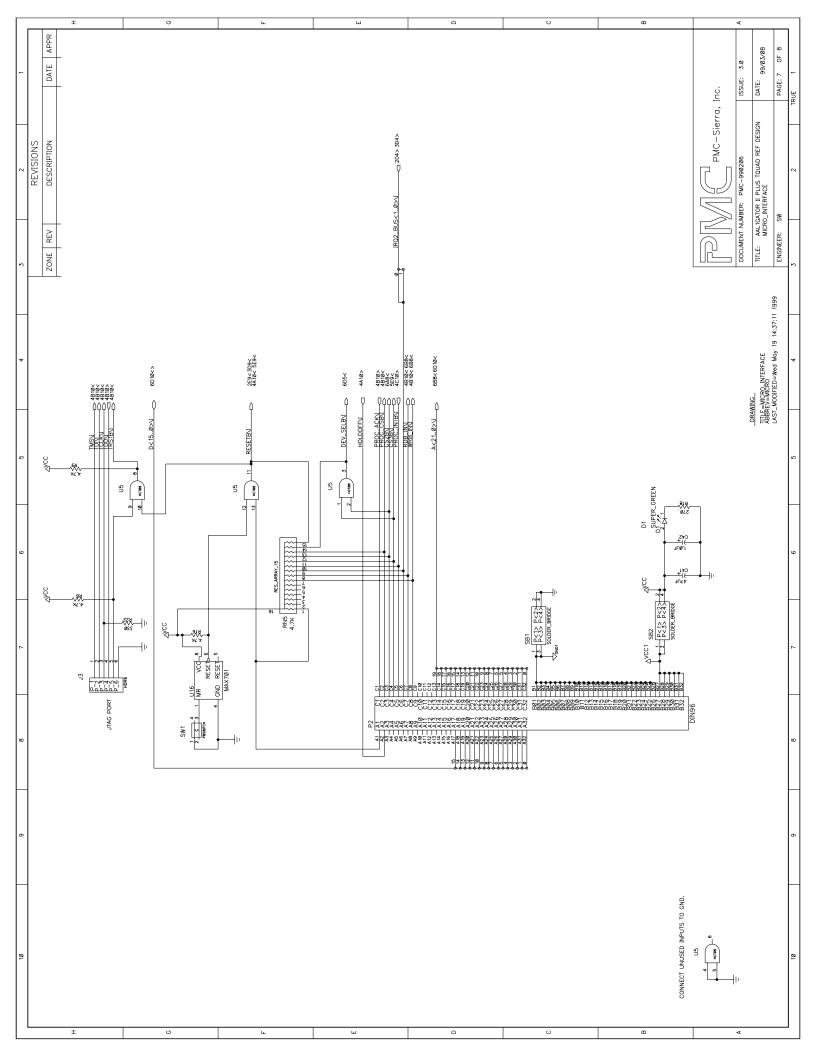

|            | 7.2.6 MICRO INTERFACE BLOCK        | C, SHEET 748                  |

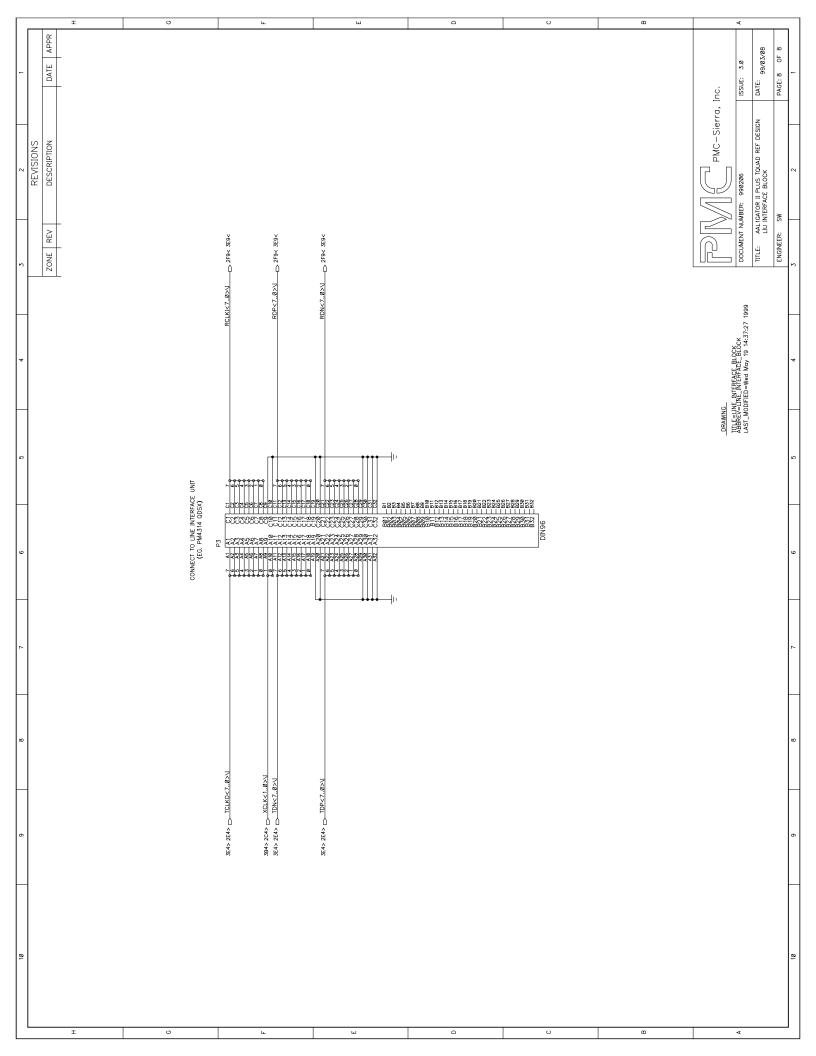

|            | 7.2.7 LIU INTERFACE BLOCK, SH      | IEET 848                      |

| 8          | MODULARIZATION ISSUES              |                               |

| 9          | REFERENCES                         | 55                            |

| 10         | APPENDIX A: BILL OF MATERIALS (CON | IET VERSION)56                |

| 11         | APPENDIX B: BILL OF MATERIALS (TQU | AD/EQUAD VERSION)60           |

| 12         | APPENDIX C: AAL1GATOR II PLUS COM  | ET SCHEMATIC DIAGRAM.62       |

| 13         | APPENDIX D: SCHEMATIC DIAGRAM (T   | QUAD/EQUAD VERSION)63         |

ISSUE 3

## LIST OF FIGURES

| FIGURE 1. SYSTEM CONFIGURATION OPTIONS WITH AAL1GATOR II2     |

|---------------------------------------------------------------|

| FIGURE 2. COMET/AAL1GATOR II BLOCK DIAGRAM4                   |

| FIGURE 3. THE COVERAGE OF THE COMET REFERENCE DESIGN. 5       |

| FIGURE 4. TQUAD/EQUAD TO AAL1GATOR II BLOCK DIAGRAM6          |

| FIGURE 5. COVERAGE OF THE TQUAD/EQUAD REFERENCE DESIGN7       |

| FIGURE 6. AAL1GATOR II TO COMET HIGH LEVEL DESIGN9            |

| FIGURE 7. GLUELESS AAL1GATOR II TO COMET INTERCONNECTION 10   |

| FIGURE 8. BLOCK DIAGRAM OF MICROPROCESSOR INTERFACE           |

| FIGURE 9. AAL1GATOR II CONNECTIONS TO MICROPROCESSOR          |

| FIGURE 10.COMET INTERFACE TO MICROPROCESSOR                   |

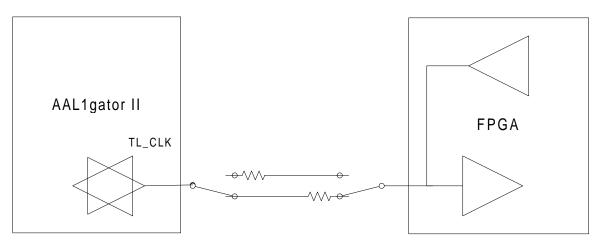

| FIGURE 11.TERMINATION OF TL_CLK SIGNAL19                      |

| FIGURE 12.TL_CLK SWITCHING TERMINATION OPTION                 |

| FIGURE 13.INTERNAL FPGA CIRCUITRY23                           |

| FIGURE 14. AAL1GATOR II PLUS TQUAD/EQUAD HIGH LEVEL DESIGN 33 |

| FIGURE 15.FLOWCHART FOR CONFIGURING THE AAL1GATOR II40        |

| FIGURE 16.AAL1GATOR II BOARD50                                |

|                                                               |

| FIGURE 17.COMET BOARD                                         |

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

## LIST OF TABLES

| TABLE 1.  | AAL1GATOR II TO COMET INTERCONNECTIONS                |    |

|-----------|-------------------------------------------------------|----|

| TABLE 2.  | MICROPROCESSOR INTERFACE PIN ASSIGNMENT12             |    |

|           | ADDITIONAL AAL1GATOR II TO MICROPROCESSOR<br>IONS     |    |

| TABLE 4.  | ADDRESS RANGES OF THE COMET DEVICES17                 |    |

| TABLE 5.  | TL_CLK OPTIONS                                        |    |

| TABLE 6.  | ADDITIONAL CONNECTIONS TO AAL1GATOR II                |    |

| TABLE 7.  | ADDITIONAL CONNECTIONS TO THE COMET DEVICE26          |    |

| TABLE 8.  | LINE INTERFACE UNIT CONNECTIONS                       |    |

| TABLE 9.  | ADDITIONAL TQUAD DEVICE CONNECTIONS                   |    |

| TABLE 10. | AAL1GATOR II REFERENCE DESIGN MEMORY MAP              |    |

| TABLE 11. | SOURCE_SELECT REGISTER (400000H)                      |    |

| TABLE 12. | N_CLK_SOURCE REGISTER (400001H)                       |    |

| TABLE 13. | XCLK_SELECT REGISTER (400002H)                        |    |

| TABLE 14. | TL_CLK OPTIONS FOR THE AAL1GATOR II41                 |    |

| TABLE 15. | SUMMARY OF MINIMUM AAL1GATOR II LINE CONFIGURATIONS.4 | 12 |

|           | SUMMARY OF THE MINIMUM COMET DEVICE<br>RATIONS        |    |

| TABLE 17. | SUMMARY OF FPGA CONFIGURATIONS45                      |    |

| TABLE 18. | AAL1GATOR II TO FRAMER INTERFACE                      |    |

| TABLE 19. | COMET VERSION BILL OF MATERIALS                       |    |

| TABLE 20. | TQUAD/EQUAD VERSION BILL OF MATERIALS                 |    |

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

## 1 FEATURES

- Implementation strategy for AAL1gator II in a Multi Service Access Concentrator environment using the PM4351 COMET.

- Implementation strategy for AAL1gator II in a Multi Service Access Concentrator environment using the PM4344 TQUAD or PM6344 EQUAD.

- Implementation strategy for AAL1gator II in a DS3 system.

- Complete implementation of 8 link Circuit Emulation Service.

- Supports structured and unstructured (both with and without CAS) CES for T1/E1 links.

- Supports independently clocked links.

- Microprocessor interface for configuration and monitoring.

- Allows 8 T1/E1 lines (1.544 Mbit/s/2.048 Mbit/s) to be serviced.

- Supports enabling/disabling of Synchronous Residual Time Stamp (SRTS) clocking.

- Modular design

- Includes a software driven clock multiplexer to allow customers to select one of several possible TL\_CLK sources.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

#### 2 OVERVIEW

This document describes the hardware and software configuration required for the PM73121 AAL1gator II Reference Design. This will be a paper only reference design, intended to assist customers in their efforts to build a Circuit Emulation Service (CES) card. The purpose of a CES card is to emulate circuit oriented transmission technology characteristics in order to support Constant Bit Rate (CBR) traffic. One example of CBR traffic is time sensitive voice applications.

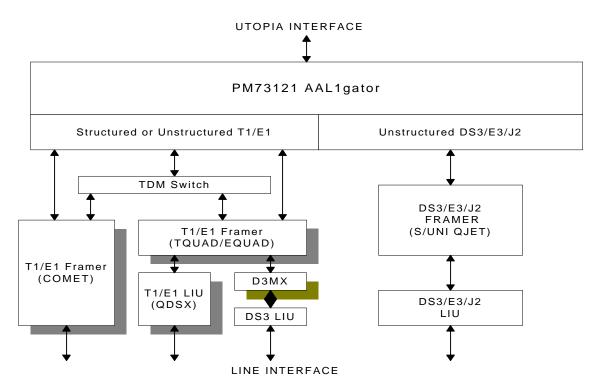

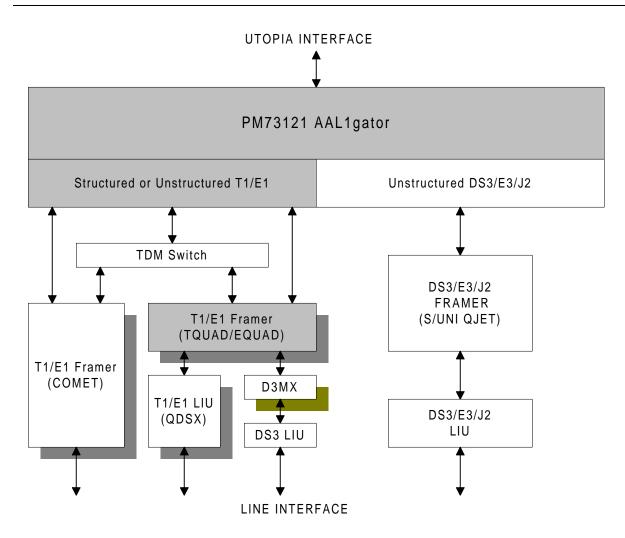

The purpose of the AAL1gator II is to provide T1/E1, or DS3/E3/J2 line interfaces access to an AAL1 CBR ATM network. Figure 1 below indicates the ways in which an AAL1gator II can be used to connect to T1/E1 or DS3/E3/J2 line interfaces. Not shown is the interface to the UTOPIA bus, and associated routing tables, and switching elements.

#### Figure 1. System Configuration options with AAL1gator II.

AAL1GATOR II REFERENCE DESIGN

The AAL1gator II is capable of supporting eight data streams, where a single data stream cannot exceed 15 Mbit/s and the aggregate total cannot exceed 20 Mbit/s, or one data stream which can support up to 45 Mbit/s.

The reference design will consist of two separate AAL1gator II implementations:

1. AAL1gator II with 8 COMET'S

**ISSUE 3**

2. AAL1gator II with 2 TQUAD's or EQUAD's

The first implementation will target the Multi Service Access Concentrator market, while the second will provide a building block for using the AAL1gator II in a DS3 application.

The reference design will further support a modularized implementation, should the need arise in the future to build prototypes based on the design. A modular implementation was chosen to allow either a board consisting of 8 COMET devices or 2 TQUAD/EQUAD devices to be connected over a common interface to a main board consisting of a single AAL1gator II along with associated memory and microprocessor interface.

PM73121 AAL1GATOR II

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

## 3 DEVELOPMENT DESCRIPTION

#### 3.1 COMET Version of Reference Design

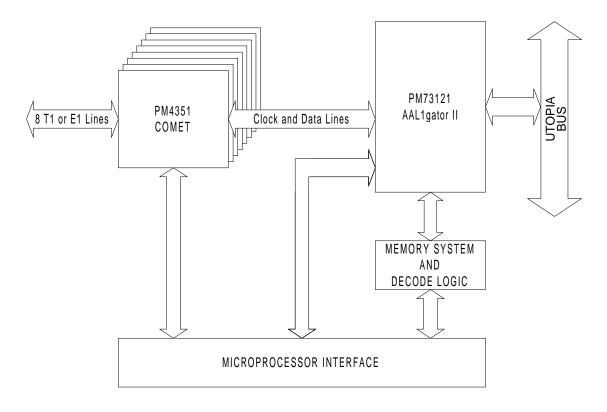

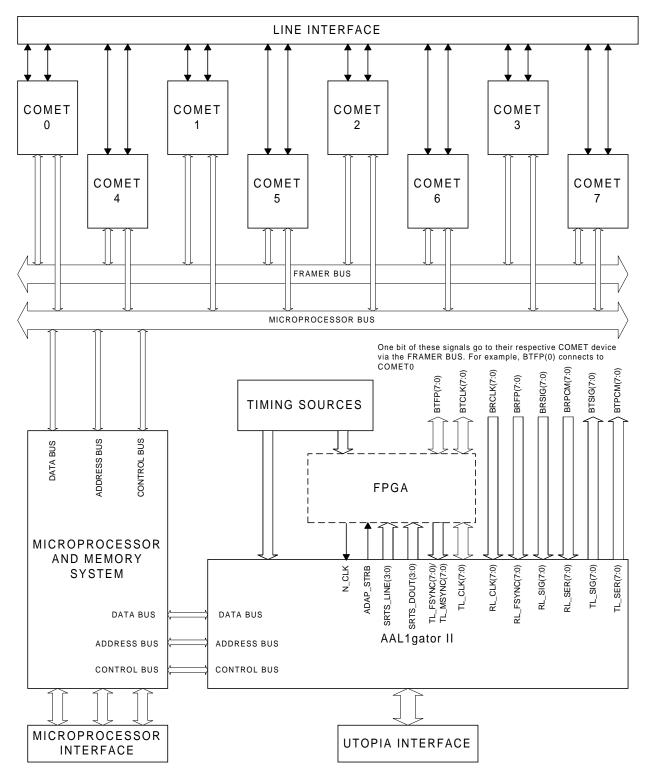

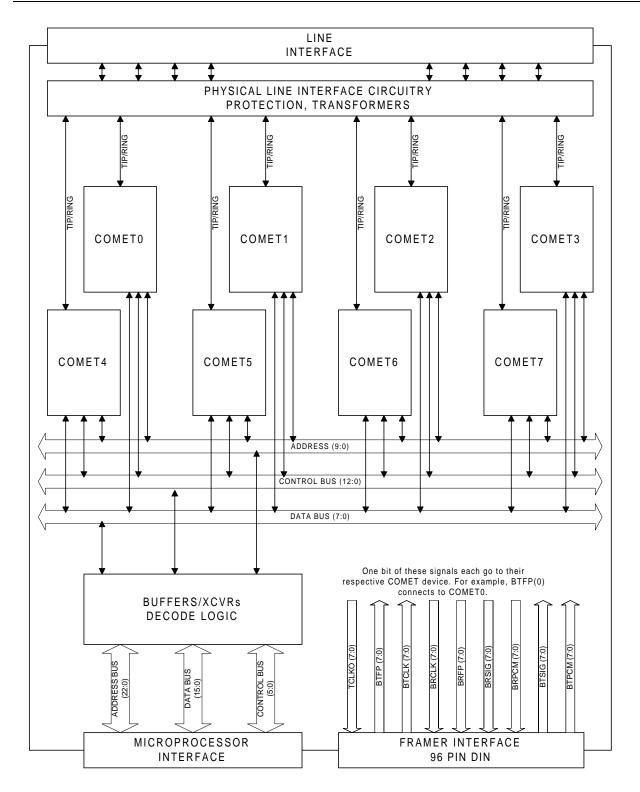

Figure 2 illustrates the block diagram of the PM73121 Reference Design using 8 COMET devices. The hardware allows full access to the AAL1gator II device via the microprocessor interface. Each COMET device acts as a line interface unit with an integrated long haul LIU, and T1/E1 framer/deframer. In the receive path (from T1 or E1 line), the COMET converts the incoming line data (in the form of channels) to a serial bit stream. The AAL1gator II then receives this data (and clocking information) from the COMET, and builds ATM cells to be sent to the UTOPIA bus.

In the transmit path (to T1 or E1 line), the AAL1gator II receives ATM cells from the UTOPIA bus. The AAL1gator II retrieves the data and signaling information, and places the data to be transmitted over the T1 (or E1) line (via the COMET) in the appropriate port and time slot.

## Figure 2. COMET/AAL1gator II Block Diagram.

REFERENCE DESIGN PMC-990206

ISSUE 3

Figure 3. The coverage of the COMET reference design.

With reference to Figure 1, Figure 3 shows how a T1 or E1 line can be interfaced to an ATM network via the UTOPIA bus by using the COMET and AAL1gator II devices.

ISSUE 3

### 3.2 TQUAD/EQUAD Version of Reference Design

REFERENCE DESIGN PMC-990206

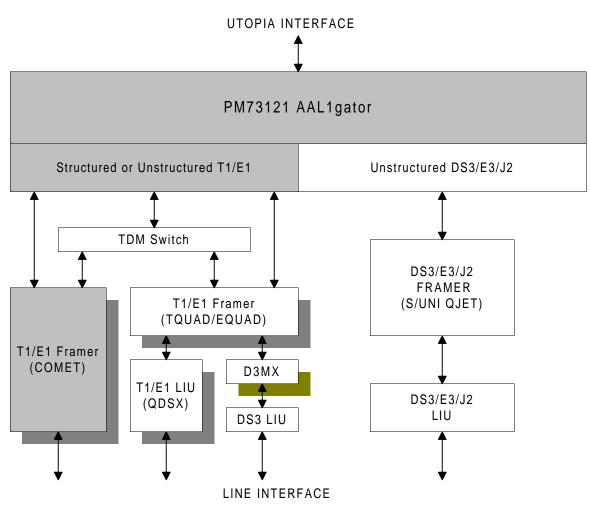

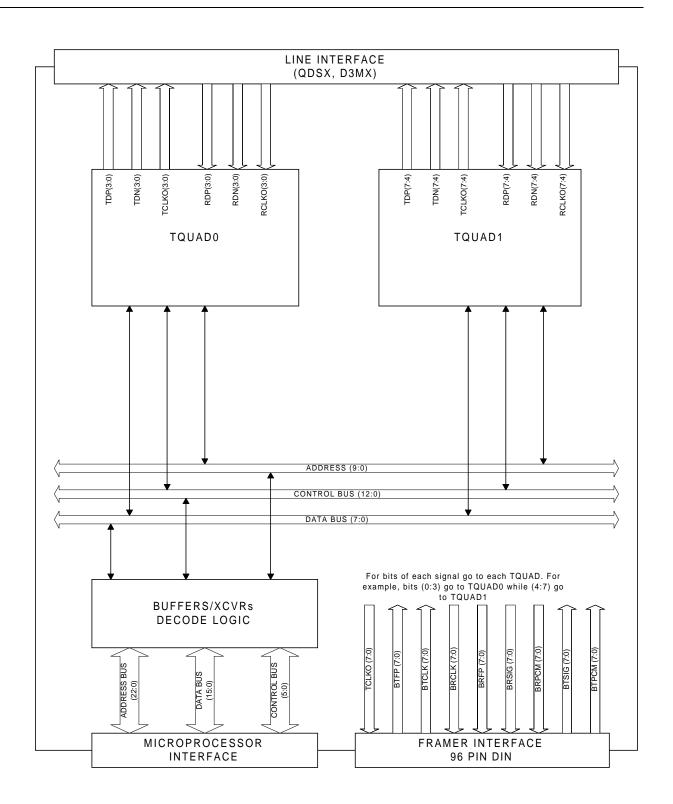

Figure 4 illustrates the AAL1gator II in an application involving the use of 2 TQUAD (or the pin compatible EQUAD) devices. This design could form a building block for the use of AAL1gator II in a DS3 system. The operation is similar to that of Figure 2.

## Figure 4. TQUAD/EQUAD to AAL1gator II Block Diagram.

With reference to Figure 1, Figure 5 illustrates the coverage of the TQUAD/EQUAD design.

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

Figure 5. Coverage of the TQUAD/EQUAD reference design.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

## 4 HIGH LEVEL DESIGN

### 4.1 AAL1gator II plus COMET Design

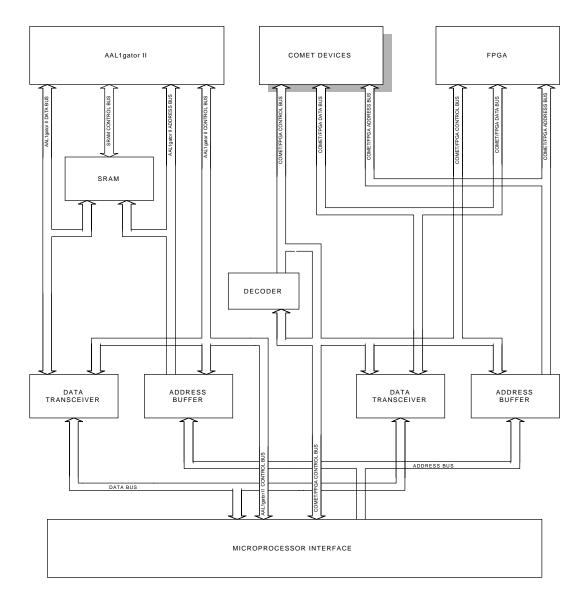

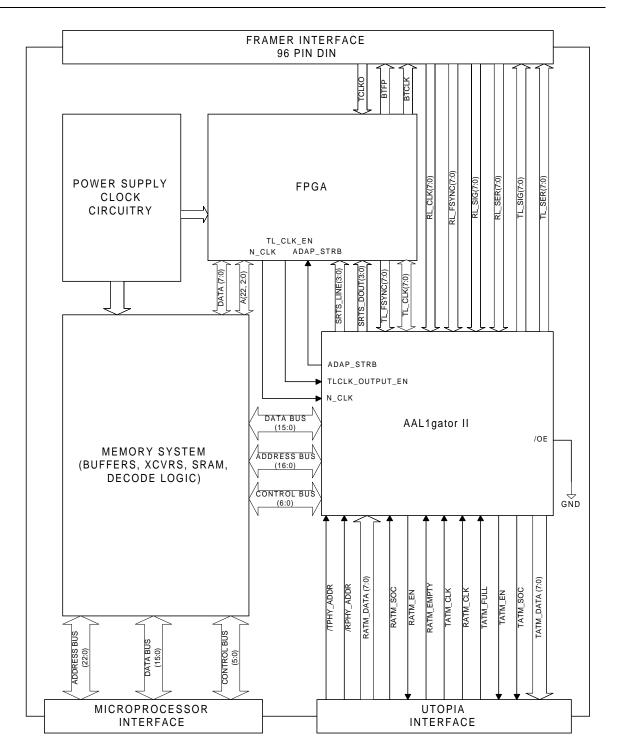

Figure 6 on the following page represents the high level design of the AAL1gator II plus COMET reference design. As can be seen, the design contains the following functional blocks:

- 1. AAL1gator II Integrated Circuit

- 2. 8 COMET Devices

- 3. Microprocessor and Memory System Interface

- 4. Field Programmable Gate Array

- 5. Clock Sources

- 6. UTOPIA Interface

- 7. Line Interface

The AAL1gator II communicates with the COMET devices via the framer bus signals listed in Table 1. As noted in Figure 9, one bit of each signal group connects to its associated COMET device. For instance, TL\_FSYNC(0) connects to COMET0, while TL\_FSYNC(1) connects to COMET1.

| SIGNAL       | DESCRIPTION                                                       |  |  |

|--------------|-------------------------------------------------------------------|--|--|

| TL_FSYNC(70) | The FPGA generates this signal for both the AAL1gator II and      |  |  |

|              | COMET. In T1 mode, this signal consists of a pulse once every 193 |  |  |

|              | bit periods.                                                      |  |  |

| TL_CLK(70)   | This is a clock signal at the transmit line rate. Its source is   |  |  |

|              | determined by the configuration of the FPGA.                      |  |  |

| RL_CLK(70)   | Receive line clock at either 1.544 MHz or 2.048 MHz, derived from |  |  |

|              | the recovered line rate timing.                                   |  |  |

| RL_FSYNC(70) | Carries receive frame synchronization from the COMET devices.     |  |  |

| RL_SIG(70)   | Carries the CAS signaling information from the COMET devices.     |  |  |

| RL_SER(70)   | Carries the receive data from the COMET devices.                  |  |  |

| TL_SIG(70)   | Carries the CAS signaling outputs to the COMET devices.           |  |  |

| TL_SER(70)   | Carries the serial data to the COMET devices.                     |  |  |

**REFERENCE DESIGN** PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

AAL1gator II to COMET High Level Design. Figure 6.

REFERENCE DESIGN PMC-990206

AAL1GATOR II REFERENCE DESIGN

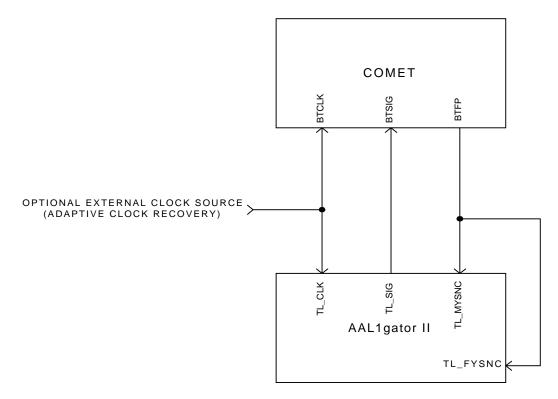

In Figure 6, the FPGA is shown with a dotted line. This is because it is possible to directly connect the AAL1gator II to the COMET device as illustrated in Figure 7. In this way, it is possible to align signaling bits to the multiframe boundary.

**ISSUE 3**

## Figure 7. Glueless AAL1gator II to COMET interconnection.

Using the approach of Figure 7, the FPGA depicted in Figure 6 is no longer necessary. The main purpose of the FPGA is to provide maximum clock distribution flexibility by allowing for independently clocked links. Using the FPGA , it is possible to use Adaptive Clock Recovery for the generation of TL\_CLK (AAL1gator II) and BTCLK (COMET). In addition, the FPGA generates an appropriate signal for N\_CLK (at 2.43 MHz), and also distributes XCLK signals to the 8 COMET devices from only two clock oscillators (1.544 MHz and 2.048 MHz). Therefore, without the FPGA, some other method will have to be found to generate a 2.42 MHz signal for N\_CLK (if SRTS is in use) and to distribute XCLK signals to the COMET devices. Please see section 4.1.2 for further discussion of the FPGA.

The other difference between the two drawings is that in Figure 7, both TL\_FSYNC and TL\_MSYNC of the AAL1gator II connects to the COMET BTFP pin (configured as an output), rather than just TL\_FSYNC. As mentioned above, this allows for alignment of signaling bits on multiframe boundaries.

The interface between the system microprocessor can be divided into two sections. The first section interfaces the system microprocessor to the AAL1gator II, while the second section interfaces the system microprocessor to the COMET devices and the FPGA. The following figure (Figure 8) represents a high level view the microprocessor interface.

# Figure 8. Block Diagram of microprocessor interface.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

In order to provide maximum system implementation flexibility, a particular microprocessor has not been specified. However, in order to implement the microprocessor and memory system as shown in this document, the system microprocessor must have the following capabilities:

- 1. Minimum 22 bit address bus

- 2. Minimum 16 bit data bus

- 3. Minimum 3 programmable chip selects

- 4. Minimum 2 independent interrupt request lines

An example of a device that meets these minimum requirements is the Motorola MC68330 microprocessor. Another scenario would see the design implemented in a PCI or compact PCI system.

Table 2 lists the pin assignment of a potential microprocessor interface (96 pin DIN). Note that this interface includes all connections from the microprocessor to the AAL1gator II, COMET devices, and FPGA.

| PIN   | PIN       | PIN    | FUNCTION           |

|-------|-----------|--------|--------------------|

| NAME  | TYPE      | NUMBER |                    |

| D(15) | I/O       | A17    | 16 bit data bus    |

| D(14) |           | A18    |                    |

| D(13) |           | A19    |                    |

| D(12) |           | A20    |                    |

| D(11) |           | A21    |                    |

| D(10) |           | A22    |                    |

| D(9)  |           | A23    |                    |

| D(8)  |           | A24    |                    |

| D(7)  |           | A25    |                    |

| D(6)  |           | A26    |                    |

| D(5)  |           | A27    |                    |

| D(4)  |           | A28    |                    |

| D(3)  |           | A29    |                    |

| D(2)  |           | A30    |                    |

| D(1)  |           | A31    |                    |

| D(0)  |           | A32    |                    |

| A(21) | Input     | C11    | 22 bit address bus |

| A(20) | (from uP) | C12    |                    |

| A(19) | . ,       | C13    |                    |

| A(18) |           | C14    |                    |

| A(17) |           | C15    |                    |

Table 2.

Microprocessor Interface Pin Assignment.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

| PIN      | PIN     | PIN      | FUNCTION                                       |

|----------|---------|----------|------------------------------------------------|

| NAME     | TYPE    | NUMBER   |                                                |

| A(16)    |         | C16      |                                                |

| A(15)    |         | C17      |                                                |

| A(14)    |         | C18      |                                                |

| A(13)    |         | C19      |                                                |

| A(12)    |         | C20      |                                                |

| A(11)    |         | C21      |                                                |

| A(10)    |         | C22      |                                                |

| A(9)     |         | C23      |                                                |

| A(8)     |         | C24      |                                                |

| A(7)     |         | C25      |                                                |

| A(6)     |         | C26      |                                                |

| A(5)     |         | C27      |                                                |

| A(4)     |         | C28      |                                                |

| A(3)     |         | C29      |                                                |

| A(2)     |         | C30      |                                                |

| A(1)     |         | C31      |                                                |

| A(0)     |         | C32      |                                                |

| RDB      | Input   | C7       | Active Low read signal                         |

| WRB      | Input   | C8       | Active Low write signal.                       |

| PROC_ACK | Input   | C1       | Active Low acknowledge signal to uP.           |

| IRQ1B    | Output  | C5       | Active low interrupt request to uP. from       |

|          | (to uP) |          | AAL1gator II                                   |

| IRQ2B    | Output  | C7       | Active low interrupt request to uP from Framer |

| RESETB   | Input   | A1       | Active low global reset.                       |

| CS1B     | Input   | C2       | Active low chip select. When asserted, the     |

|          |         |          | AAL1gator II is selected.                      |

| CS2B     | Input   | C3       | Active low chip select. When asserted, the     |

|          | -       |          | COMET or TQUAD/EQUAD is selected.              |

| CS3B     | Input   | C4       | Active low chip select. When asserted, the     |

|          | -       |          | FPGA is selected.                              |

| HOLDOFF  | Output  | A2       | Prevents uP from gaining too many cycles.      |

| GND      | n/a     | B1 – B26 | GND. Ground Reference                          |

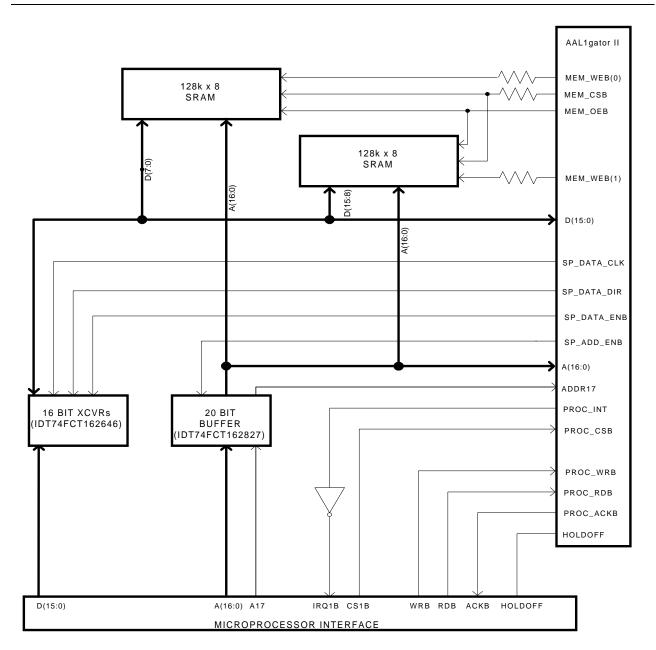

Figure 9 on the following page represents the design of the interface from the AAL1gator II to its associated memory system and the system microprocessor. As can be noted, the interface consists of 2 128K x 8 static ram devices. In the transmit direction (from the line via RL\_SER and RL\_SIG, to the ATM network), the devices store queued data while cells for transmission are built. In the receive direction (from the ATM network via the UTOPIA bus to the line side interface) the SRAM holds data while frames are built for transmission on the T1 or E1 line. The selected SRAM must be 12 ns or faster, with a write setup time of 7 ns or faster.

REFERENCE DESIGN PMC-990206

AAL1GATOR II REFERENCE DESIGN

Figure 9. AAL1gator II Connections to Microprocessor.

PMC PMC-Sierra, Inc.

PM73121 AAL1GATOR II

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

Figure 9 also indicates the usage of external address buffers and data transceivers. In order for the system to operate at the maximum frequency of 40.00 MHz, the address buffers must have a worst case propagation delay of 8ns, while the data transceivers must have a worst case delay of 10ns. For these reasons the IDT74FCT162827CT was chosen as the address buffer. This 20 bit device has a maximum propagation delay of 4.4ns (50pF, 500 $\Omega$  load). The IDT74FCT162646 was chosen as the data transceiver. This 16 bit device has a worst case propagation delay of 5.4ns under the same loading conditions. As can be seen, serial termination resistors are placed on the MEM\_WEB(x) and MEM\_CSB signals. The resistor value was chosen in accordance with the discussion in section 8.6 of the AAL1gator II data sheet. Please refer to that section for additional information.

Table 3 below describes additional connections between the AAL1gator II, the microprocessor and the memory system.

| SIGNAL NAME | DESCRIPTION                                                                                                                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM_WEB(0)  | Active low write enable for low order byte SRAM                                                                                                                                                   |

| MEM_WEB(1)  | Active low write enable for high order byte SRAM                                                                                                                                                  |

| MEM_CSB     | Active low chip select for SRAM devices                                                                                                                                                           |

| MEM_OEB     | Active low output enable of SRAM devices                                                                                                                                                          |

| SP_DATA_CLK | Memory or register read data is written into the FCT162646 data transceiver on the rising edge of this signal. The microprocessor may then access the data. Signal is driven by the AAL1gator II. |

| SP_DATA_DIR | Controls the direction of data movement in the FCT162646. When high, data flows toward the microprocessor, when low, towards the AAL1gator II. Signal is driven by the AAL1gator II.              |

| SP_DATA_ENB | AAL1gator II driven signal that enables the FCT162646 data transceiver.                                                                                                                           |

| SP_ADD_ENB  | AAL1gator II driven signal that enables the FCT162827 address buffer.                                                                                                                             |

| PROC_INT    | Active high interrupt from the AAL1gator II to the microprocessor.                                                                                                                                |

| PROC_CSB    | Active low chip select from the microprocessor (via CS1B).                                                                                                                                        |

| ADDR17      | When high, the CMD_REG of the AAL1gator II is selected.                                                                                                                                           |

| PROC_WRB    | Active low write signal for the AAL1gator II from the microprocessor.                                                                                                                             |

| PROC_RDB    | Active low read signal for the AAL1gator II from the microprocessor.                                                                                                                              |

| PROC_ACKB   | Active low acknowledge signal from the AAL1gator II.                                                                                                                                              |

| HOLDOFF     | When high, prevents the microprocessor from additional accesses until 20 SYS_CLK cycles from the last processor access.                                                                           |

| Table 3. | Additional AAL1gator II to Microprocessor Connections. |

|----------|--------------------------------------------------------|

|----------|--------------------------------------------------------|

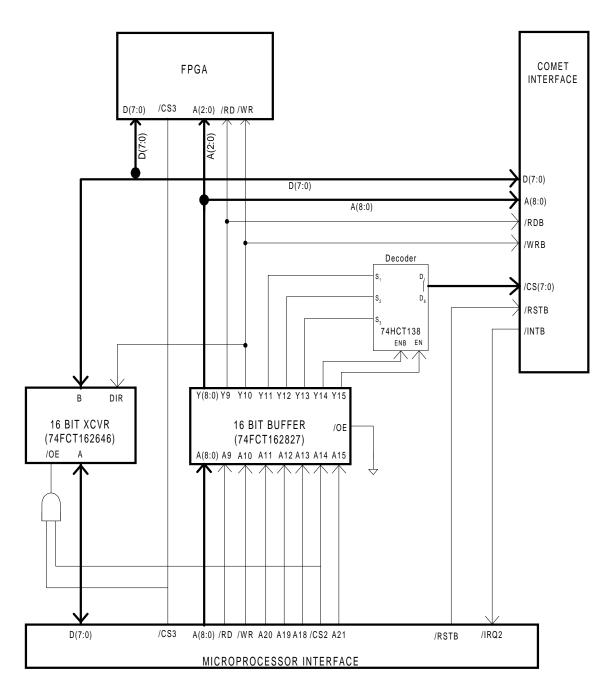

Figure 10 on the following page illustrates the connections between the microprocessor, and the 8 COMET devices plus the FPGA.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

### Figure 10. COMET Interface to Microprocessor.

When the microprocessor wishes to communicate with a COMET device, it asserts an address as listed in the following table (Table 4). When an appropriate address is driven onto the bus, the microprocessor simultaneously asserts CS2B. Since A21 is high, the decoder is then active. Address bits A(20..18) determine which output of the decoder is

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

driven low. One decoder output connects to the CSB input of each COMET device. For example, if A(20..18) are 000, then decoder output Y0 is driven low, which also asserts CSB of COMET0. No other COMET device is selected at this time. Address bits A(8..0) determine which register of the COMET the microprocessor is communicating with.

In order to meet the timing requirements of the COMET devices (see PM4351 COMET data sheet), the 3-8 decoder (74HCT138) must have a minimum propagation delay of 10ns. With a 15pF load, the device has a typical delay of 13ns. At 50pf (VCC = 4.5), the delay increases to 27ns, and therefore will meet the specifications.

| COMET  | BASE ADDRESS | ADDRESS RANGE    |

|--------|--------------|------------------|

| COMET0 | 200000h      | 200000 – 2001FFh |

| COMET1 | 240000h      | 240000 – 2401FFh |

| COMET2 | 280000h      | 280000 – 2801FFh |

| COMET3 | 2C0000h      | 2C0000 – 2C01FFh |

| COMET4 | 300000h      | 300000 – 3001FFh |

| COMET5 | 340000h      | 340000 – 3401FFh |

| COMET6 | 380000h      | 380000 – 3801FFh |

| COMET7 | 3C0000h      | 3C0000 – 3C01FFh |

Table 4.

Address Ranges of the COMET devices.

Since the address and data buses are shared among many devices, a 20 bit buffer and transceiver is used. This insures that clean signals are present on the inputs of the devices, and that no data collisions occur. The buffer (FCT162827) is not only placed on the address lines, but the various control signals such as WRB and RDB as well. The 16 bit transceiver (FCT162646) is used in flow through mode to control data bus access. The transceivers output enable is controlled by the result of a logical AND of CS2 and CS3. In this way, whenever the microprocessor needs to communicate with either a COMET or the FPGA, either the CS2, or CS3 signal must be driven low, which drives the active low output enable signal of the transceiver low. The transceivers direction is controlled by the WRB signal.

AAL1GATOR II REFERENCE DESIGN

ISSUE 3

# 4.1.2 Field Programmable Gate Array (FPGA)

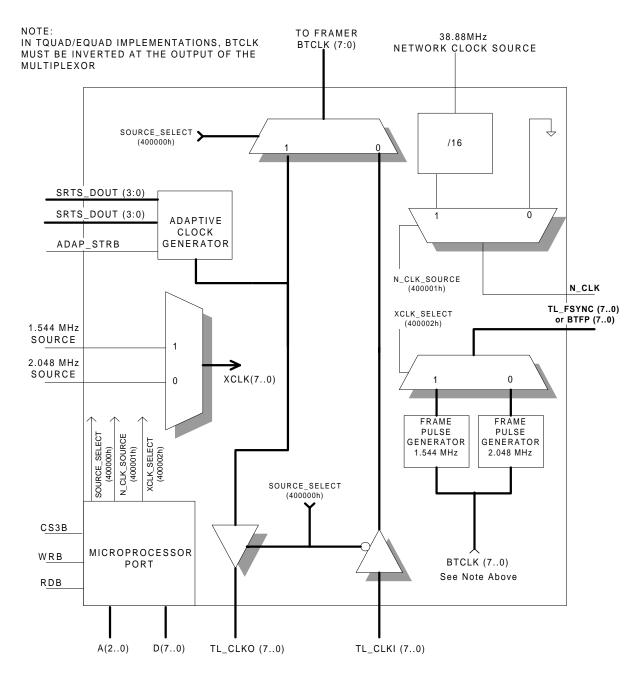

The FPGA (see Figure 13 page 23) performs the following functions on a per line basis:

- 1. Allows fully software selectable TL\_CLK source.

- 2. Allows a fully selectable COMET XCLK source (1.544 or 2.048 MHz).

3. Generates framing pulses at the 8 kHz rate for the TL\_FSYNC (AAL1gator II) and BTFP (TQUAD or COMET) signals.

4. Produces a software selected N\_CLK signal (gnd, or 2.43 MHz).

In order to provide maximum system flexibility, the AAL1gator II provides several options for the TL\_CLK signal. Table 5 lists the options that the user may select. As can be seen, the FPGA permits the use of all options on a per line basis. The options must also be set in the LIN\_STR\_MODE register (CLK\_SOURCE bits) of the AAL11gator II.

| CLK_SOURCE(54) | FUNCTION                            | TL_CLK I/O | SUPPORTED |

|----------------|-------------------------------------|------------|-----------|

| 00             | External Clock Source               | input      | YES       |

| 01             | Recovered: based on RL_CLK          | output     | YES       |

| 10             | Nominal T1 or E1 Clock<br>Synthesis | output     | YES       |

| 11             | SRTS                                | output     | YES       |

When the CLK\_SOURCE(5..4) bits are set to 00, TL\_CLK is configured as an input. In this mode, the FPGA will allow a 1.544 MHz, 2.048 MHz, or adaptive clock source to be supplied to the TL\_CLK input (and also to the BTCLK input of the COMET or TQUAD device). In adaptive clock mode, an adaptive clock generator block provides a queue depth difference for control of an external clock. If the queue depth is low, the clock frequency is reduced, while if the queue depth is high, the clock frequency is increased. Adaptive clock data from the AAL1gator II appears on the SRTS port when the ADAP\_STRB signal is asserted by the AAL1gator II.

In recovered mode, (CLK\_SOURCE set to 01), the clock signal output on TL\_CLK is based on the received RL\_CLK.

When the CLK\_SOURCE(5..4) bits are set to 10, the AAL1gator II is configured to generate a nominal T1 or E1 clock derived from a 38.88 MHz SYS\_CLK. SYS\_CLK must be network derived in order to lock the synthesized clock to the network clock.

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

When CLK\_SOURCE(5..4) are set to 11, the AAL1gator II is configured to use the Synchronous Residual Time Stamp (SRTS) option. In this mode, the AAL1gator II compares locally generated SRTS values with received SRTS values. A 4 bit difference code is then generated. If the code value is higher than that previously generated, the remote clock is running faster than the local clock. Alternatively, if the code is lower, the remote clock is running slower than the local clock. The AAL1gator II uses this information to synthesize TL\_CLK.

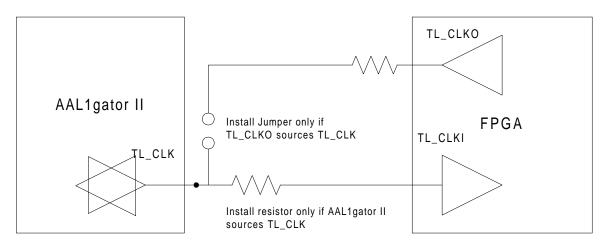

In this implementation, the interconnection between the AAL1gator II TL\_CLK pin and the FPGA is bidirectional. There are many possible ways to alleviate the complexity of terminating a bidirectional signal. The first method, illustrated below in Figure 11, utilizes two separate FPGA ports for TL\_CLK. The TL\_CLKI port is an input port from the AAL1gator II, while the TL\_CLKO port is an output port to the AAL1gator II. In additon two series terminating resistors (value between 33 and 50 $\Omega$ ) and one jumper per line are required. When the AAL1gator II is sourcing TL\_CLK (to the TL\_CLKI input of the FPGA), the jumper is not installed, and the resistor nearest the AAL1gator II is installed. Likewise, when the TL\_CLKO port of the FPGA is sourcing TL\_CLK, the jumper is installed, and the resistor nearest he AAL1gator II is not installed. This, in essence, creates a unidirectional transmission path for each direction.

Figure 11. Termination of TL\_CLK signal.

However, there is a disadvantage to the above method. It is no longer possible to interactively switch between having the AAL1gator II source TL\_CLK, or have an external source provide TL\_CLK to the AAL1gator II. Therefore, an alternative approach would be to combine the TL\_CLKI and TL\_CLKO ports of the FPGA into one bidirectional port (for each line). The signal path distance between the AAL1gator II and the FPGA must then be kept as short as possible. If this is not possible, both ends of the signal path may be serially terminated with an appropriate value resistor.

AAL1GATOR II REFERENCE DESIGN

One last alternative is a hybrid between the previous two approaches. As illustrated in Figure 12 for one of the eight TL\_CLK lines, this method utilizes a switching arrangement to change between having the AAL1gator II source TL\_CLK, to having the FPGA source TL\_CLK to the AAL1gator II.

Figure 12. TL\_CLK switching termination option.

**ISSUE 3**

REFERENCE DESIGN PMC-990206

The switches could take the form of dip switches, requiring manual interchange, or could be digitally controlled analog swiches. In addition, the switches could be replaced by jumpers.

PMC-Sierra Inc. has secured an agreement with Bellcore (patent holders for SRTS clock recovery technique). Please refer to the AAL1gator II data sheet for important information regarding this agreement.

In a typical application employing SRTS, N\_CLK must be a 2.43 MHz signal derived from the ATM network (for example, from the 155.52 MHz SONET clock). To disable SRTS, N\_CLK is connected to GND, whereas to enable SRTS, N\_CLK must be connected to a 2.43 MHz signal. This is accomplished via a divide by 16 block in the FPGA whose input is the 38.88 MHz network clock signal.

Another function of the FPGA is to generate the 8 kHz framing pulse from the transmit line clock output (BTCLK) to the framer. This 8 kHz signal connects to the AAL1gator II TL\_FSYNC input, and the framer's BTFP input. In T1 mode, a pulse one BTCLK period wide is generated every 193 bits, while in E1 mode, the pulse is generated every 256 bits.

In an implementation involving the AAL1gator II and TQUAD or EQUAD device, each BTCLK output from the FPGA must be inverted. Whereas if the design involves AAL1gator II to COMET devices, the BTCLK output must not be inverted with respect to TL\_CLK. The reason for this is the timing requirements of the line side interface of the

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

AAL1gator II. In the receive direction (from the ATM network to the line), the AAL1gator II updates signals (TL\_SIG, TL\_SER) on the rising edge of TL\_CLK. In addition, the TQUAD samples the corresponding signals on the rising edge of its BTCLK (analogous to TL\_CLK) signal. If the output of the FPGA is not inverted, this would cause the TQUAD or EQUAD device to sample the TL\_SIG and TL\_SER (BTSIG and BTPCM) signals at the same time that they are in transition. Inverters shift the sample point to a time in which all signals are stable.

The COMET version does not require inverters because it allows users to select the active edge (on which it samples BTSIG and BTPCM) of its BTCLK signal.

Please see sections 5 and 6 for FPGA register and programming information.

AAL1GATOR II REFERENCE DESIGN

# 4.1.3 Clock and Power Supply Circuitry

**ISSUE 3**

This is a relatively simple block. It consists of two crystal oscillators: One at 2.048 MHz (50 ppm), and one at 1.544 MHz (50 ppm). These crystals provide the XCLK signal via the FPGA to the individual COMET devices on a per line basis. For instance, if COMET 0 is configured to interface to a T1 line, a 1.544 MHz clock is applied to its XCLK input. Alternatively, if it is to interface to an E1 line, a 2.048 MHz clock signal is applied to its XCLK input.

The AAL1gator II requires a 38.88 MHz clock signal on its SYS\_CLK input. Ideally, this is a network derived signal (for example, the 155.52 MHz SONET clock divided by four) with a duty cycle variance of  $\pm$  2.5 %. In applications employing SRTS, SYS\_CLK need not be network derived, provided N\_CLK is network derived.

In applications that do not employ SRTS (for example, synthesizing a nominal T1 or E1 clock), the accuracy of the synthesized clock is dependent on the accuracy of SYS\_CLK. For example, to generate a T1 clock with 50 ppm accuracy, SYS\_CLK must have 50 ppm accuracy. To lock this synthesized clock to a network clock, SYS\_CLK must be derived from the network clock.

To accomplish these requirements in this reference design, the network clock signal (ideally, the 155.52 MHz SONET clock) is input to the FPGA via an SMA connector. The FPGA then provides a 38.88 MHz SYS\_CLK signal for the AAL1gator II. As mentioned previously, the FPGA also generates the 2.43 MHz N\_CLK signal from this same source.

In addition to the clock circuitry, this block also generates the required +5V/+3.3V supply for the board.

## 4.1.4 UTOPIA Interface

The AAL1gator II communicates with various ATM devices, such as the ATLAS or the QRT/QSE via the UTOPIA interface. Please refer to section 4.3 of the AAL1gator II data sheet for a discussion of the individual signals.

There are two possible UTOPIA modes of operation for the AAL1gator II: ATM mode and PHY mode. In ATM mode, the AAL1gator II is configured with an ATM layer UTOPIA interface. In PHY mode, it is configured with a PHY layer UTOPIA interface.

When PHY\_ENABLE is high, PHY mode is enabled, while if low, the device is in ATM mode. To allow for application specific implementations, an optional jumper will be specified in the schematic diagram. If a PHY mode application is required, the jumper

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

may be installed, otherwise it may be left unconnected, due to the internal pulldown resistor within the device (device defaults to ATM mode).

## Figure 13. Internal FPGA Circuitry.

REFERENCE DESIGN PMC-990206

-

ISSUE 3

## 4.1.5 Additional Connections

The following table (Table 6) lists the remaining connections to the AAL1gator II not already discussed.

| PIN         |                   | DESCRIPTION                               |  |

|-------------|-------------------|-------------------------------------------|--|

| NAME        | PIN NUMBER        |                                           |  |

| PHY_ENABLE  | 56                | Determines which UTOPIA mode the          |  |

|             |                   | UTOPIA interface is configured for.       |  |

|             |                   |                                           |  |

|             |                   | Connect optional resistor to VCC for PHY  |  |

|             |                   | mode, otherwise leave unconnected for ATM |  |

|             |                   | mode operation.                           |  |

| TL_MSYNC(x) | 154, 141, 129,    | Transmit Line Multiframe Synchronization  |  |

|             | 113, 101, 82, 70, | (TL_MSYNC). An edge an these signals      |  |

|             | 51                | indicate the start of a multiframe.       |  |

|             |                   |                                           |  |

|             |                   | Connect to GND if unused.                 |  |

| RL_MSYNC(x) | 160, 147, 135,    | Receive Line Multiframe Synchronization   |  |

|             | 123, 107, 95, 76, | (RL_MSYNC). RL_MSYNC carries the          |  |

|             | 64                | signaling information from the framer.    |  |

|             |                   | Indicates the start of a multiframe.      |  |

|             |                   |                                           |  |

|             |                   | Connect to GND if unused                  |  |

| /OE         | 184               | Output Enable (/OE). Active low signal to |  |

|             |                   | enable outputs of the device.             |  |

|             |                   |                                           |  |

|             |                   | Connect to GND.                           |  |

| /SCAN_TRST  | 167               | Scan Test Reset (/SCAN_TRST). Reset       |  |

|             |                   | signal for boundary scan logic.           |  |

|             |                   |                                           |  |

|             |                   | Connect to GND (if JTAG port unused) or   |  |

|             |                   | header.                                   |  |

| SCAN_TMS    | 166               | Scan Test Mode Select (SCAN_TMS). Mode    |  |

|             |                   | select signal for boundary scan logic.    |  |

|             |                   |                                           |  |

|             |                   | Connect to header.                        |  |

| SCAN_TDI    | 165               | Scan Test Data Input (SCAN_TDI). Serial   |  |

|             |                   | data input for boundary scan.             |  |

|             |                   |                                           |  |

| Table 6. | Additional Connections to AAL1gator II. |

|----------|-----------------------------------------|

|----------|-----------------------------------------|

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

| PIN            | AAL1GATOR II | DESCRIPTION                                     |

|----------------|--------------|-------------------------------------------------|

| NAME           | PIN NUMBER   |                                                 |

|                |              | Connact to booder                               |

|                |              | Connect to header.                              |

| SCAN_TDO       | 168          | Scan Test Data Output (SCAN_TDO). Serial        |

|                |              | data output from boundary scan.                 |

|                |              | Connect to header                               |

| SCAN_TCLK      | 169          | Scan Test Clock (SCAN_TCLK). Clock for          |

| _              |              | boundary scan logic.                            |

|                |              | Connect to $330\Omega$ resistor to GND (if JTAG |

|                |              | port unused) or to header.                      |

| P_TEST         | 170          | Process Test (P_TEST). Used to measure          |

|                |              | process test parameters.                        |

|                |              | N.C.                                            |

|                | 000          |                                                 |

| PULLUP_DISABLE | 238          | Pullup Disable. Used to disable pullup          |

|                |              | resistors during manufacturing tests.           |

|                |              | Connect to GND                                  |

| VDD            | multiplo     |                                                 |

|                | multiple     | +5V supply                                      |

| GND            | multiple     | Ground Reference                                |

#### N.C. = No Connection

Note: The JTAG port signals (eg. SCAN\_TDO) will connect to a header to allow for connection to other devices that have a JTAG port to allow for comprehensive boundary scan testing. On the schematic diagram, the SCAN\_TRST pin is connected to a header and pulled up via a 4.7K resistor to VCC, to allow for external connection to a JTAG controller. If the JTAG port is not being used, the SCAN\_TRST pin should be connected to ground via a  $330\Omega$  resistor.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

## 4.1.6 Line Interface

Although the COMET device has an integral Line Interface Unit, additional circuitry is required before connecting to the T1 or E1 line. Transformers must be placed between the tip and ring lines. In addition, transient voltage suppressors must be placed in series with each line. Each set of tip and ring lines connect to the T1 or E1 line via a bantam connector.

## 4.1.7 Additional COMET Connections

The following table (Table 7) lists additional connections to the COMET device not previously discussed.

| PIN NAME | DESCRIPTION                                                                                                                                         |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| TDAT     | Transmit Digital PCM Data (TDAT). Provides the line side NRZ PCM data (when transmit digital interface is enabled).                                 |

|          | N.C.                                                                                                                                                |

| TFP      | Transmit Digital Frame Pulse (TFP). When enabled, indicates the frame alignment of the line side transmitted PCM stream.                            |

| RDAT     | Receive Digital Line Data (RDAT). When enabled, samples the line side recovered NRZ PCM data.                                                       |

| RCLKI    | Receive Digital Line Clock (RCLK). When the transmit digital interface is enable, the externally recovered line rate clock is provided on this pin. |

| RSYNC    | Recovered Clock Synchronization Signal (RSYNC). Provides a 8 kHz timing reference signal for T1 and E1 applications.<br>N.C.                        |

| TCLKI    | Transmit Clock Reference (TCLKI). May be used a reference for transmit line rate generation. May be any multiple of 8 kHz. Connect to GND.          |

| XCLK     | Crystal Clock Input (XCLK). Jitter free, 50% duty cycle clock at 1.544                                                                              |

Table 7.

Additional Connections to the COMET Device.

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

| PIN NAME | DESCRIPTION                                                                          |

|----------|--------------------------------------------------------------------------------------|

|          | MHz (if T1) or 2.048 MHz if E1. 50 ppm.                                              |

| ATB      | Analog Test Bus (ATB). Reserved for production test.                                 |

|          | Connect to GND.                                                                      |

| TRIMF    | Trim Fuse. Reserved for production purposes.                                         |

|          | Connect to GND                                                                       |

| ТСК      | Test Clock (TCK) Boundary scan clock.                                                |

|          | Connect via $330\Omega$ resistor to GND (if JTAG port unused) or header.             |

| TMS      | Test Mode Select (TMS). Boundary scan test select signal.                            |

|          | Connect to header.                                                                   |

| TDI      | Test Data Input (TDI). Boundary scan input serial data.                              |

|          | Connect to header.                                                                   |

| TDO      | Test Data Output (TDO). Boundary scan serial test data output.<br>Connect to header. |

| /TRSTB   | Test Reset (TRSTB). Boundary scan test reset.                                        |

|          | Connect to header and VCC via 4.7K resistor, or to RSTB (if JTAG port unused).       |

| VDDOx    | Output Power Pins                                                                    |

| N/000    | Connect to well decoupled +3.3V supply (in common with VDDI.                         |

| VSSOx    | Output Ground Pins.                                                                  |

|          | Connect to GND in common with VSSI.                                                  |

| VDDIx    | Internal Power Pins                                                                  |

|          | Connect to well decoupled +3.3V supply in common with VDDOx                          |

| VSSIx    | Internal Ground Pins                                                                 |

|          | Connect to GND in common with VSSOx                                                  |

| BIAS     | +5 V Bias. Facilitates 5 V tolerance on inputs.                                      |

|          | Connect to well decoupled +5 V rail.                                                 |

| TAVD1    | Transmit Analog Power.                                                               |

|          | Power for transmit LIU reference circuitry.                                          |

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

| PIN NAME     | DESCRIPTION                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

|              |                                                                                             |

|              | Connect to analog +3.3V                                                                     |

| TAVD2,       | Transmit Analog Power. Transmit power for transmit LIU output drivers.                      |

| TAVD3        |                                                                                             |

|              | Connect to analog +3.3V.                                                                    |

| TAVD4        | Transmit Analog Power. Supplies power for transmit clock synthesis.                         |

|              | Connect to analog +3.3 V.                                                                   |

| TAVS1        | Transmit Analog Ground                                                                      |

|              |                                                                                             |

|              | Connect to analog GND.                                                                      |

| TAVS2, TAVS3 | Transmit Analog Ground.                                                                     |

|              | Connect to analog GND.                                                                      |

| TAVS4        | Transmit Analog Ground.                                                                     |

| 17.004       |                                                                                             |

|              | Connect to analog GND.                                                                      |

| RAVD1        | Receive Analog Power.                                                                       |

|              | Supplies power for receive LIU input equalizer.                                             |

|              |                                                                                             |

| RAVD2        | Connect to analog +3.3V.<br>Receive Analog Power. Supplies power for analog peak detect and |

| RAV DZ       | slicer.                                                                                     |

|              |                                                                                             |

|              | Connect to analog +3.3 V.                                                                   |

| RAVS1,       | Receive Analog Ground.                                                                      |

| RAVS2        |                                                                                             |

|              | Connect to analog GND.                                                                      |

| QAVD         | Quiet Analog Power. Supplies power for core analog circuitry.                               |

|              | Connect to analog +3.3 V                                                                    |

| QAVS         | Quiet Analog Ground.                                                                        |

|              |                                                                                             |

|              | Connect to analog GND.                                                                      |

#### N.C. = No Connection

Note: The JTAG port signals (eg. TCK) will connect to a header to allow for connection to other devices that have a JTAG port to allow for comprehensive boundary scan testing.

ISSUE 3

## 4.1.8 COMET Configuration

Soon after power up, a hardware reset should be performed.

The following minimum additional COMET software configurations are required:

- 1. Set active edge of BTCLK to falling edge.

- 2. Set active edge of BRCLK to rising edge.

- 3. Set BRCLK as output.

- 4. Set BRFP as output.

For additional information, including COMET configuration data, please refer to Section 6 and the COMET data sheet (PMC-970624).

## 4.1.9 AAL1gator II Configuration

Please refer to Section 6 and the AAL1gator II data sheet (PMC-980620) for additional information regarding configuration of the AAL1gator II.

#### 4.1.10 The JTAG Port

The JTAG port is connected among all devices to allow for boundary scan testing. The signals are connected in the following way:

1. TMS The Test Mode Select signal is connected in parallel among all COMET devices and the AAL1gator II.

2. TCK The Test Clock signal is connected in parallel among all COMET devices and the AAL1gator II.

3. TRSTB The Test Reset Select signal is connected in parallel among all COMET devices and the AAL1gator II. The source of this signal may either be the JTAG controller, or from a pushbutton activation

4. TDI/TDO The Test Data Input/Test Data Output signal is connected serially among all COMET devices and the AAL1gator II, beginning with the AAL1gator II, and ending with the last COMET device.

The JTAG port signals connect to an externally accessible header.

ISSUE 3

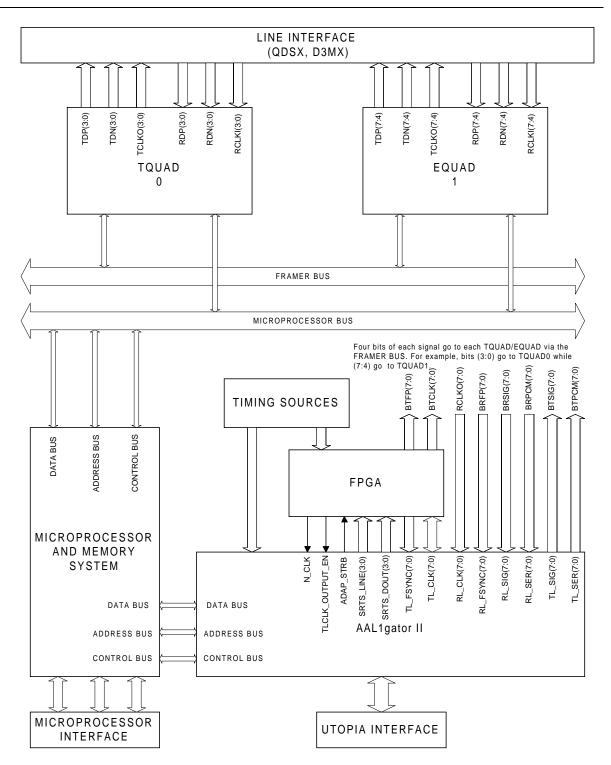

## 4.2 AAL1gator II Plus TQUAD/EQUAD Design

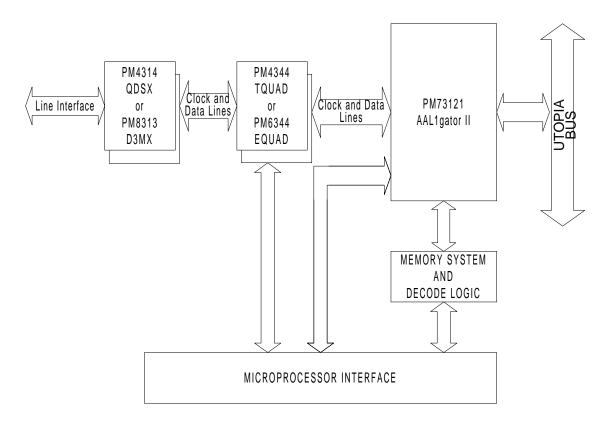

The high level design of the AAL1gator II plus TQUAD/EQUAD is illustrated in Figure 14 on page 33. As can be seen, the COMET design and the TQUAD/EQUAD design are nearly identical. However, they do have the following differences:

1. Only 2 TQUAD/EQUAD are devices used in the TQUAD/EQUAD design.

2. The address bus connecting to each individual TQUAD/EQUAD is 10, rather than 9 bits wide.

3. The TQUAD/EQUAD device does not contain an integral Line Interface Unit, therefore a separate LIU such as the QDSX or D3MX must be used.

4. The TQUAD or EQUAD does not require a 1.544 or 2.048 MHz oscillator. Instead, a 37.56 MHz 32/50 ppm (49.152 MHz 32/50 ppm) if EQUAD) oscillator is used.

## 4.2.1 Microprocessor and Memory System Interface

The same microprocessor and memory system interface as that used in the AAL1gator II plus COMET reference design is used in the AAL1gator II plus TQUAD reference design.

## 4.2.2 Line Side Interface to the AAL1gator II

As discussed in section 4.1.2, the AAL1gator II plus TQUAD requires additional inverters on the line side interface. This is because the AAL1gator II samples RL\_SER and RL\_SIG on the falling edge of RL\_CLK while the TQUAD asserts the corresponding signals on the falling edge of RCLKO. Therefore, inverters are placed on the RCLKO output to the AAL1gator II device.

## 4.2.3 Line Interface

Also mentioned previously, the TQUAD does not contain an integral Line Interface Unit. Therefore, an LIU such as the QDSX or D3MX (if used in a channelized DS3 application) must be used. Table 8 lists the pin information for the connections to the line interface unit.

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

#### Table 8.Line Interface Unit Connections.

| SIGNAL                                                                                       | EUNCTION                                                                                                             |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| SIGNAL<br>NAME                                                                               | FUNCTION                                                                                                             |

| XCLK                                                                                         | XCLK. Crystal Clock signal. Nominally 37.056 MHz if T1, 49.152 MHz if E1.                                            |

| TDP(7)<br>TDP(6)<br>TDP(5)<br>TDP(4)<br>TDP(3)<br>TDP(2)<br>TDP(1)<br>TDP(0)                 | Transmit Digital Positive Line Pulse (TDP). Available when the TQUAD/EQUAD is configured to transmit dual rail data. |

| TDN(7)<br>TDN(6)<br>TDN(5)<br>TDN(4)<br>TDN(3)<br>TDN(2)<br>TDN(1)<br>TDN(0)                 | Transmit Digital Negative Line Pulse (TDN). Available when the TQUAD/EQUAD is configured to transmit dual rail data. |

| TCLKO(7)<br>TCLKO(6)<br>TCLKO(5)<br>TCLKO(4)<br>TCLKO(3)<br>TCLKO(2)<br>TCLKO(1)<br>TCLKO(0) | Transmit Clock Output (TCLKO) Signals TDN and TDP are updated on the active edge of this signal.                     |

| RDP(7)<br>RDP(6)<br>RDP(5)<br>RDP(4)<br>RDP(3)<br>RDP(2)<br>RDP(1)<br>RDP(0)                 | Receive Digital Positive Line Pulse (RDP). Available when the TQUAD/EQUAD is configured to receive dual rail data.   |

| RDN(7)<br>RDN(6)<br>RDN(5)<br>RDN(4)<br>RDN(3)                                               | Receive Digital Negative Line Pulse (RDN). Available when the TQUAD/EQUAD is configured to receive dual rail data.   |

ISSUE 3

| SIGNAL<br>NAME | FUNCTION                                                                |

|----------------|-------------------------------------------------------------------------|

| RDN(2)         |                                                                         |

| RDN(1)         |                                                                         |

| RDN(0)         |                                                                         |

| RCLKI(7)       | Receive Line Clock Input (RCLKI). Each input is an externally recovered |

| RCLKI(6)       | 1.544 MHz (or 2.048 MHz) line clock that may be enabled to sample the   |

| RCLKI(5)       | RDN and RDP inputs, when the device is configured to receive dual rail  |

| RCLKI(4)       | data.                                                                   |

| RCLKI(3)       |                                                                         |

| RCLKI(2)       |                                                                         |

| RCLKI(1)       |                                                                         |

| RCLKI(0)       |                                                                         |

| GND            | GND. Ground Reference.                                                  |

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

Figure 14. AAL1gator II plus TQUAD/EQUAD High Level Design.

REFERENCE DESIGN PMC-990206

AAL1GATOR II REFERENCE DESIGN

# 4.2.4 Additional Connections for the TQUAD Device

ISSUE 3

The following table (Table 9) lists the additional connections for the TQUAD/EQUAD device not previously discussed.

| PIN NAME | TQUAD PIN<br>NUMBER   | DESCRIPTION                                                                                                                                                                        |

|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRCLKx   | 94                    | Backplane Receive Clock. Either a 1.544 or 2.048<br>MHz clock signal. This signal is common to all framers<br>within the TQUAD/EQUAD device.<br>Connect to GND.                    |

| MENB     | 45                    | Multiplex Enable. When asserted low, the four sets of data per TQUAD are combined into a single bit interleaved 12.352 MHz stream.                                                 |

| RDLSIGx  | 125, 126, 127,<br>128 | Receive Data Link Signal. Signals are available when<br>the HDLC receiver is enabled.<br>Connect to header.                                                                        |

| RDLCLKx  | 119, 120, 123,<br>124 | Receive Data Line Clock. Clock signals are available<br>on these pins when the HDLC receiver is enabled.<br>Connect to header.                                                     |

| MRD      | 59                    | Multiplexed Receive Data (MRD). When MENB is low,<br>four sets of data and signaling information is bit<br>interleaved into a single 12.352 MHz data stream.<br>Connect to header. |

| TDLSIGx  | 113, 114, 117,<br>118 | Transmit Data Link Signal. When the associated<br>HDLC transmitter is enabled, signaling data is<br>available on these pins.<br>Connect to header.                                 |

| TDLCLKx  | 109, 110, 111,<br>112 | Transmit Data Link Clock. When HDLC is enabled,<br>used to sample the TDLSIG signal.                                                                                               |

| XCLK     | 60                    | Connect to header.<br>XCLK. Crystal Clock Input.                                                                                                                                   |

#### Table 9. Additional TQUAD Device Connections.

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

| PIN NAME | TQUAD PIN<br>NUMBER        | DESCRIPTION                                              |

|----------|----------------------------|----------------------------------------------------------|

|          | NOMBER                     |                                                          |

|          |                            | If TQUAD, connect to 37.056 MHz crystal.                 |

|          |                            | If EQUAD, connect to 49.152 MHz crystal. 32/50 ppm       |

| ALE      | 41                         | Address Latch Enable. Allows TQUAD to be                 |

|          |                            | connected to a multiplexed address data bus.             |

|          |                            | Connect to VCC via 4.7K resistor.                        |

| PHAx     | 18, 52, 89, 105,<br>121    | AC Power Pins.                                           |

|          |                            | Connect to well decoupled +5 V supply together with PHD. |

| PHDx     | 20, 50, 85, 115            | DC Power Pins.                                           |

|          |                            | Connect to well decoupled +5 V supply together with PHA. |

| PLAx     | 19, 53, 90, 106,<br>122, 1 | AC Ground Pins                                           |

|          | ,                          | Connect to common ground with PLD                        |

| PLDx     | 21, 51, 86, 116            | DC Ground Pins                                           |

|          |                            | Connect to common ground with PLA.                       |

N.C. = No Connection

# 4.2.5 TQUAD/EQUAD Configuration

A software reset should occur soon after power up to restore the TQUAD or EQUAD to its default configuration state. Please refer to Section 6 and the TQUAD or EQUAD data sheet (PMC-940910, PMC-951013) for additional configuration information.

ISSUE 3

## 5 MEMORY MAP AND REGISTER DEFINITIONS

The memory map for the AAL1gator II reference design is as indicated in Table 10.

| •                      | •            | •                 |

|------------------------|--------------|-------------------|

| DEVICE                 | BASE ADDRESS | RANGE             |

| AAL1gator II           | 000000h      | 000000h – 01FFFFh |

| AAL1gator II CMD_REG   | 02000h       | 020000h – 03FFFFh |

| COMET0                 | 20000h       | 200000h – 2001FFh |

| TQUAD0                 | 20000h       | 200000h – 2003FFh |

| COMET1                 | 240000h      | 240000h – 2401FFh |

| TQUAD1                 | 240000h      | 240000h – 2403FFh |

| COMET2                 | 280000h      | 280000h – 2801FFh |

| COMET3                 | 2C0000h      | 2C0000h – 2C01FFh |

| COMET4                 | 30000h       | 300000h – 3001FFh |

| COMET5                 | 340000h      | 340000h – 3401FFh |

| COMET6                 | 380000h      | 380000h – 3801FFh |

| COMET7                 | 3C0000h      | 3C0000h – 3C01FFh |

| FPGA                   | 400000h      | 40000h            |

| SOURCE_SELECT Register |              |                   |

| FPGA                   | 400001h      | 400001h           |

| N_CLK_SOURCE Register  |              |                   |

| FPGA                   | 400002h      | 400002h           |

| XCLK_SELECT Register   |              |                   |

#### Table 10. AAL1gator II Reference Design Memory Map.

To communicate with the FPGA and its internal registers, a programmable chip select on the system microprocessor should be configured to be asserted when an address in the range 400000h – 400002h is driven onto the address bus. The VHDL code within the FPGA will then examine the WRB and RDB to determine if a register read or write is being performed. The FPGA then either drives the data bus with the selected registers contents, or updates one of the following registers with the data driven on the data bus by the system microprocessor.

As mentioned previously, the FPGA allows the support of several configurable options. This is accomplished through the use of the following registers within the FPGA:

| Table 11. | SOURCE_SELECT Register (400000h). |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

| bit 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| ss7   | ss6 | ss5 | ss4 | ss3 | ss2 | ss1 | ss0 |

REFERENCE DESIGN PMC-990206

ISSUE 3

The SOURCE\_SELECT determines whether the signal transmitted to the COMET or TQUAD device via the BTCLK pin is from the AAL1gator II TL\_CLK pin or from an external source. If an external source is selected, adaptive clock mode is enabled, and the FPGA synthesizes an external clock at the line rate. The synthesized clock appears at the TL\_CLKIO<7..0> and BTCLK<7..0> pins

ssX:

- 0 = AAL1gator II internal clock (nominal, recovered, or SRTS) sources clock signal via the FPGA to the COMET or TQUAD BTCLK<X> pin.

- 1 = External Clock mode is selected. Adaptive clock recovery mode is in use. The FPGA provides a line rate clock to both the AAL1gator II and the COMET or TQUAD device.

| Bit 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|---|---|---|---|---|---|

| srts_enable | Х | х | Х | Х | Х | Х | Х |

Table 12 presents the structure of the N\_CLK\_SOURCE Register. If the srts\_enable bit is set to 0, N\_CLK is connected to GND. Otherwise, if the bit is set to 1, a 2.43MHz (38.88 MHz divided by 16) signal is presented on N\_CLK. The affect of this register is to allow for disabling of Synchronous Residual Time Stamp (SRTS) on the AAL1gator II. If the N\_CLK signal is connected to GND, SRTS is disabled. Bits 6 through 0 are unused.

srts\_enable:

1 = 2.43MHz signal presented on N\_CLK. SRTS is enabled.

$0 = N_CLK$  is set to a logic 0. SRTS is disabled.

| Table 13. | XCLK_SELECT Register (400002h). |

|-----------|---------------------------------|

|-----------|---------------------------------|

| Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| xclk7 | xclk6 | xclk5 | xclk4 | xclk3 | xclk2 | xclk1 | xclk0 |

Table 13 lists the details of the XCLK\_SELECT register. The purpose of this register to allow support of both T1 and E1 lines. If a T1 line is used, that lines bit (for example xclk7) must be set to 1. Otherwise, if an E1 line is in use, the associated lines bit must be set to 0. This feature is available on a per line basis.

AAL1GATOR II REFERENCE DESIGN

The effect of this register is seen in two places on a per line basis:

- 1. The register determines which clock signal (1.544 MHz or 2.048 MHz) is output from the FPGA to each individual COMETs XCLK pin.

- 2. The register determines which framing pulse format (T1 or E1) is used. The effect is seen on the outputs the AAL1gator II's TL\_FSYNC<7..0> pins and the COMET or TQUAD/EQUAD's BTFP pins.

xclk:

- 1 = Line is T1. If using a COMET device, the COMET receives a 1.544MHz clock signal on its XCLK pin. In addition, a pulse one BTCLK period wide is generated every 193 bits, and output to the AAL1gator II and COMET or TQUAD device.

- 0 = Line is E1. If using a COMET device, the COMET receives a 2.048MHz clock signal on its XCLK pin. In addition, a pulse one BTCLK period wide is generated every 256 bits, and output to the AAL1gator II and COMET or EQUAD device.

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

# 6 SOFTWARE CONFIGURATION

This section describes how to configure the AAL1gator II to work with T1 and E1 lines. A hypothetical scenario consisting of the AAL1gator II interfacing to 4 T1 and 4 E1 lines will be explored. Lines 0 through 3 will be T1, while lines 4 through 7 will be E1.

#### 6.1 AAL1gator II Configuration

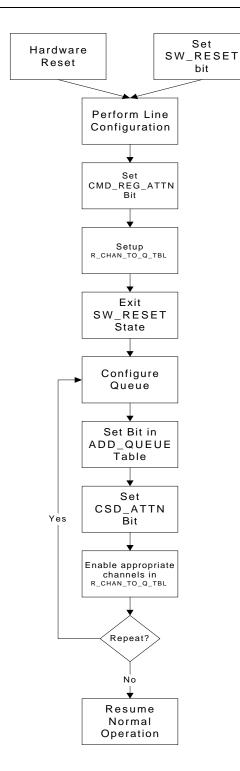

The basic configuration steps for the AAL1gator II are as outlined in Figure 15 (next page). As can be seen, the first step is to enter a SW\_RESET state. There are two possible ways to enter the SW\_RESET state:

- 1. By performing a hardware reset. Once the hardware reset is removed, the AAL1gator II enters the SW\_RESET state.

- 2. By asserting bit 5 (SW\_RESET) of the CMD\_REG (base address 20000h).

Once in the SW\_RESET state, various configurable options are set by writing to the data structures in memory. Among many others, these options include:

- 1. Type of line (T1 or E1).

- 2. Source of the TL\_CLK signal.

- 3. The value of empty bytes in partially filled cells.

- 4. OAM cell format.

When the AAL1gator II has been set up in the desired format, the CMD\_REG\_ATTN bit (bit 3 in the CMD\_REG) should be set to 1. Finally, to complete the configuration, the SW\_RESET bit in the CMD\_REG should be deasserted.

REFERENCE DESIGN PMC-990206

ISSUE 3

AAL1GATOR II REFERENCE DESIGN

## Figure 15. Flowchart for configuring the AAL1gator II.

To configure the AAL1gator II to operate with the conditions given above, the following operations should be performed:

- 1. Enter the SW\_RESET state

- Write a 1 to bit 6 (MIXED\_MODE\_EN) of the COMP\_LIN\_REG (base address 1h). This permits the device to operate with a mix of T1 and E1 lines.

- 3. Write to the remaining bits of the COMP\_LIN\_REG as necessary for each individual implementation.

- 4. Write to the LINE\_STR\_MODE\_X registers. These eight registers store the per line configuration. In these registers, users may set each line in T1 or E1, and determine the source of TL\_CLK.

To set lines 0 through 3 for T1 mode, write a 1 to bit 13 (T1\_MODE) of LINE\_STR\_MODE\_0 through LINE\_STR\_MODE\_3 (addresses 10h through 13h).

To set lines 4 through 7 for E1 mode, write a 0 to bit 13 of LINE\_STR\_MODE\_4 through LINE\_STR\_MODE\_7.

The TL\_CLK source for each line may be set at the same time that the line mode is set.

The remaining bits may be set as required, and as indicated in the AAL1gator II data sheet.

| CLK_SOURCE(5:4) | DESCRIPTION                                                                     |

|-----------------|---------------------------------------------------------------------------------|

| 00              | Use external clock (TL_CLK is an input)                                         |

| 01              | Looped: Loop the recovered RL_CLK as the source.                                |

| 10              | Nominal: Generate a clock of the nominal T1 or E1 frequency<br>based on SYS_CLK |

| 11              | SRTS: Generate a clock based on the received SRTS values.                       |

Table 14. TL\_CLK options for the AAL1gator II.

- 5. Set CMD\_REG\_ATTN (bit 3) in the CMD\_REG (20000h)

- 6. Configure the R\_CHAN\_TO\_Q\_TBL data structure (base address 08200h) as required. See the AAL1gator II data sheet, section 7.8.6 for further details.

- 7. Exit the SW\_RESET state.

- 8. Configure a queue via the T\_QUEUE\_TBL (base address 2000h) as required. See the AAL1gator II data sheet, section 7.6.8 for further details.

- 9. Set corresponding bit for the queue just added in the ADD\_QUEUE table (base address 30h). See the AAL1gator II data sheet, section 7.6.8 for further details.

- 10. Set CSD\_ATTN (bit 4) in the CMD\_REG (base address 20000h).

- 11. Perform steps 8 through 10 as necessary, adding only queue at a time (helps minimize CDV due to clumping).

| REGISTER        | BASE<br>ADDRESS | VALUE | FUNCTIONAL DESCRIPTION                                                                     |

|-----------------|-----------------|-------|--------------------------------------------------------------------------------------------|

| COMP_LIN_REG    | 1h              | 0040h | AAL1gator II is set to operate with mixed lines.                                           |

| LINE_STR_MODE_0 | 10h             | 2000h | Line 0 is in T1 mode, using adaptive clock recovery (external TL_CLK source).              |

| LINE_STR_MODE_1 | 11h             | 2010h | Line 1 is in T1 mode. TL_CLK outputs a looped RL_CLK.                                      |

| LINE_STR_MODE_2 | 12h             | 2020h | Line 2 is in T1 mode. AAL1gator II generates a nominal T1 clock, and outputs it on TL_CLK. |

| LINE_STR_MODE_3 | 13h             | 2030h | Line 3 is in T1 mode. AAL1gator II is using SRTS clock recovery on this line.              |

| LINE_STR_MODE_4 | 14h             | 0000h | Line 0 is in E1 mode, using adaptive clock recovery (external TL_CLK source).              |

| LINE_STR_MODE_5 | 15h             | 0010h | Line 1 is in E1 mode. TL_CLK outputs a looped RL_CLK.                                      |

| LINE_STR_MODE_6 | 16h             | 0020h | Line 2 is in E1 mode. AAL1gator II generates a nominal T1 clock, and outputs it on TL_CLK. |

| LINE_STR_MODE_7 | 17h             | 0030h | Line 3 is in E1 mode. AAL1gator II<br>is using SRTS clock recovery on<br>this line.        |

#### Table 15. Summary of minimum AAL1gator II line configurations.

ISSUE 3