# ISO-CMOS ST-BUS™ FAMILY MT8910 **Digital Subscriber Line Interface Circuit**

たフケーノノーノフ

**Preliminary Information**

#### **Features**

- Compatible with ISDN U-Interface standard.

- Over 5.5 km (18 kft.) loop range.

- Full duplex transmission over single twisted pair.

- Advanced echo cancelling technology.

- High performance 2B1Q line code.

- Frame and superframe synchronization.

- Mitel ST-BUS compatible.

- Single 5V power supply.

- Full activation/deactivation state machine.

- Low power consumption (typically, 250 mW).

- QSNR and line attenuation diagnostics.

- On-chip 15 second timer.

- Insertion loss measurement test signal & quiet

### **Applications**

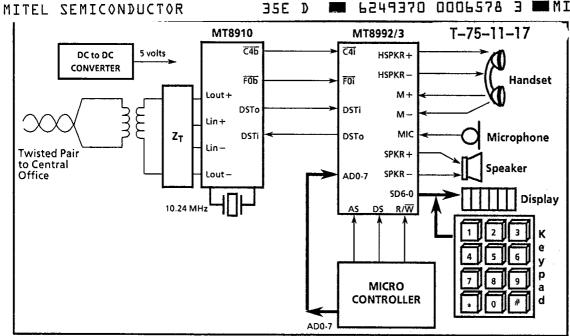

- ISDN NT1 and NT2 DSL interface.

- Digital PABX line cards and telephone sets.

- Digital multiplexers and concentrators.

- Pair gain system.

# Description

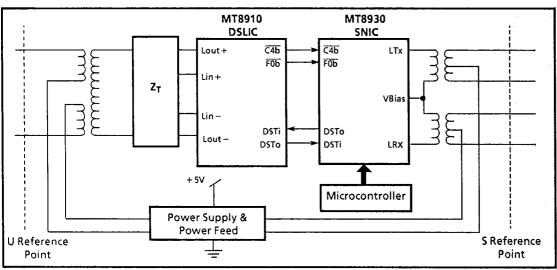

The MT8910 Digital Subscriber Line Interface Circuit (DSLIC) is designed to provide ISDN basic rate access (2B+D) at the U-interface. Full duplex digital

transmission at 160 kbit/s on a single twisted pair is achieved using echo cancelling hybrid (ECH) technology. This, in conjunction with the high performance 2B1Q line code, allows the DSLIC to meet the loop length requirements of the digital subscriber loops at the U-interface over the entire non-loaded telephone loop plant. The DSLIC is compatible with the complete range of Mitel Semiconductor ISDN components through the use of the ST-BUS interface.

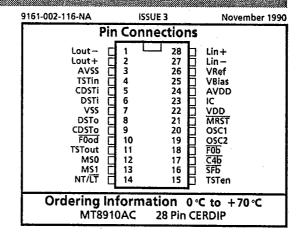

Figure 1 - Functional Block Diagram

# **Preliminary Information**

MITEL SEMICONDUCTOR

35E D ■ 6249370 0006555 2 ■MITC

# **Absolute Maximum Ratings\***

|   | Parameters                | Symbol            | Min  | Max                  | Units |

|---|---------------------------|-------------------|------|----------------------|-------|

| 1 | Supply Voltage            | . V <sub>DD</sub> | -0.3 | 7.0                  | V     |

| 2 | Voltage on any I/O pin    | V <sub>I/O</sub>  | -0.3 | V <sub>DD</sub> +0.3 | ٧     |

| 3 | Current on any I/O pin    | 11/0              |      | 20                   | mA    |

| 4 | Storage Temperature       | T <sub>ST</sub>   | -55  | 125                  | °C    |

| 5 | Package Power Dissipation | P <sub>D</sub>    |      | 1000                 | mW    |

<sup>\*</sup>Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

T-75-11-17

# Recommended Operating Conditions - Voltages are with respect to ground (Vss) unless otherwise stated.

|   | Characteristics                                         | Sym              | Min  | Typt | Max  | Units | Test Conditions                       |

|---|---------------------------------------------------------|------------------|------|------|------|-------|---------------------------------------|

| 1 | Supply Voltage                                          | V <sub>DD</sub>  | 4.75 | 5.0  | 5.25 | V     | (see Note 1)                          |

| 2 | Analog Supply Voltage                                   | AV <sub>DD</sub> | 4.75 | 5.0  | 5.25 | ٧     | Relative to AV <sub>SS</sub> (Note 1) |

| 3 | Input Low Voltage (except OSC1, MRST, MS0, MS1, NT/LT)  | V <sub>IL</sub>  |      |      | 0.4  |       | for 400mV noise margin                |

| 4 | Input High Voltage (except OSC1, MRST, MS0, MS1, NT/LT) | V <sub>IH</sub>  | 2.4  |      |      | V     | for 400mV noise margin                |

| 5 | Input Low Voltage for OSC1/2, MRST, MS0, MS1, NT/LT     | V <sub>IL</sub>  |      | 1.0  | 1.5  |       |                                       |

| 6 | Input High Voltage for OSC1/2, MRST, MS0, MS1, NT/LT    | V <sub>IH</sub>  | 3.5  | 3.0  |      | V_    |                                       |

| 7 | Operating Temperature                                   | TA               | 0    |      | 70   | °C    |                                       |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Note 1: To obtain optimum line performance, noise level on supply must be less than 25 mVpp.

### DC Electrical Characteristics - Voltages are with respect to ground (Vss) unless otherwise stated.

|   |        | Characteristics                                         | Sym             | Min | Тур‡ | Max | Units | Test Conditions |

|---|--------|---------------------------------------------------------|-----------------|-----|------|-----|-------|-----------------|

| 1 |        | Input High Voltage (except OSC1, MRST, MS0, MS1, NT/LT) | V <sub>IH</sub> | 2.0 |      |     | ٧     |                 |

| 2 | I<br>N | Input Low Voltage (except OSC1, MRST, MS0, MS1, NT/LT)  | V <sub>IL</sub> |     |      | 0.8 | ٧     |                 |

| 3 | P<br>U | Input High Voltage for OSC1/2, MRST, MS0, MS1, NT/LT    | V <sub>IH</sub> | 3.0 | 3.5  |     | V     |                 |

| 4 | T<br>S | Input Low Voltage for OSC1/2, MRST, MS0, MS1, NT/LT     | V <sub>IL</sub> |     | 1.5  | 2.0 | V     |                 |

| 5 |        | Input Leakage Current                                   | ارر             |     | 10   |     | μΑ    |                 |

| 6 | 1      | Input Impedance (Lin-to Lin+)                           | Z <sub>in</sub> |     | 100  |     | kΩ    | @40 kHz         |

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

DC Electrical Characteristics (continued) - Voltages are with respect to ground (Vss) unless otherwise stated.

|    |   | Characteristics                                                          | Sym               | Min | Typ                 | Max | Units            | Test Conditions                                                            |

|----|---|--------------------------------------------------------------------------|-------------------|-----|---------------------|-----|------------------|----------------------------------------------------------------------------|

| 7  |   | V <sub>Bias</sub> Voltage                                                | V <sub>8ias</sub> |     | 0.5AV <sub>DD</sub> |     | ٧                | Relative to AV <sub>SS</sub> , $C_L = 1 \mu F$ minimum to AV <sub>SS</sub> |

| 8  |   | V <sub>Ref</sub> Voltage                                                 | V <sub>Ref</sub>  |     | -1.8                |     | ٧                | Relative to $V_{Bias}$<br>$C_L = 1 \mu F$ minimum to $AV_{SS}$             |

| 9  | 0 | V <sub>Bias</sub> and/or V <sub>Ref</sub> load                           | V <sub>BL</sub>   | 1   |                     |     | MΩ               |                                                                            |

| 10 | Ü | Output High Voltage(1)                                                   | V <sub>OH</sub>   | 2.4 |                     |     | V                | I <sub>OH</sub> =10mA                                                      |

| 11 | Т | Output Low Voltage (1)                                                   | V <sub>OL</sub>   |     |                     | 0.4 | V                | I <sub>OL</sub> = 5.0mA                                                    |

| 12 | P | OSC2 Output High Voltage                                                 | V <sub>OH</sub>   |     | 3.5                 |     | V                | I <sub>OH</sub> = 10μA                                                     |

| 13 | T | OSC2 Output Low Voltage                                                  | V <sub>OL</sub>   |     | 1.5                 |     | V                | I <sub>OL</sub> =10μA                                                      |

| 14 | S | Differential Output Voltage<br>(L <sub>out+</sub> to L <sub>out-</sub> ) | V <sub>out</sub>  |     | 6.2                 |     | V <sub>p-p</sub> | R <sub>L</sub> =80Ω                                                        |

| 15 |   | Output Impedance<br>(L <sub>out+</sub> , L <sub>out-</sub> )             | Z <sub>out</sub>  |     | 0.5                 |     | Ω                | Measured by sourcing and sinking 10 mA.                                    |

| 16 |   | Output Capacitance<br>(L <sub>out+</sub> , L <sub>out-</sub> )           | c <sub>o</sub>    |     |                     | 50  | pF               | (see Note 1)                                                               |

| 17 |   | High Impedance Leakage                                                   | loz               |     | 10                  |     | μΑ               |                                                                            |

| 18 |   | Supply Current                                                           | I <sub>DD</sub>   |     | 50<br>10            |     | mA<br>mA         | Line Drivers Active<br>Low Power Mode                                      |

<sup>&</sup>lt;sup>1</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing. (1) except OSC2

T-75-11-17

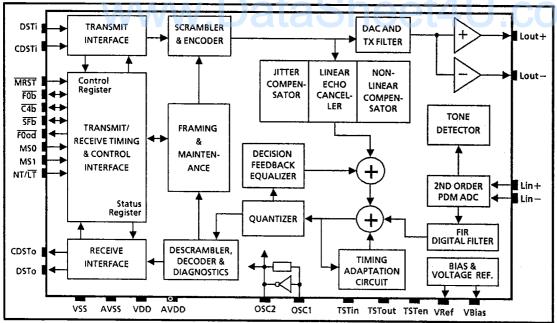

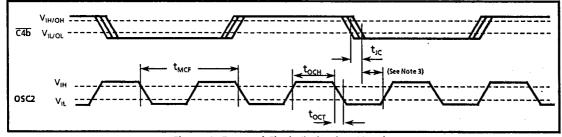

AC Electrical Characteristics' - ST-BUS Timing LT Mode (Ref. Figure 2)

|    | Characteristics                                                  | Sym                                                      | Min | Тур               | Max | Units | Test Conditions                                                                      |

|----|------------------------------------------------------------------|----------------------------------------------------------|-----|-------------------|-----|-------|--------------------------------------------------------------------------------------|

| 1  | F0b Input Pulse Width                                            | t <sub>FPW</sub>                                         |     | 244               |     | ns    |                                                                                      |

| 2  | Frame Pulse (FOb) Setup Time                                     | t <sub>FPS</sub>                                         | 50  | 1                 |     | ns    |                                                                                      |

| 3  | Frame Pulse (FOb) Hold Time                                      | t <sub>FPH</sub>                                         | 50  |                   |     | ns    |                                                                                      |

| 4  | C4b Input Clock Period                                           | t <sub>P40</sub>                                         |     | 244               |     | ns    |                                                                                      |

| 5  | C4b Pulse Width High or Low                                      | t <sub>C4W</sub>                                         |     | 122               |     | ns    |                                                                                      |

| 6  | Superframe Setup Time                                            | t <sub>SFS</sub>                                         |     | 50                |     | ns    |                                                                                      |

| 7  | Superframe Hold Time                                             | t <sub>SFH</sub>                                         |     | 50                |     | ns    |                                                                                      |

| 8  | FOod Delay                                                       | t <sub>DFD</sub>                                         |     | 45                |     | ns    | 150 pF Load (see Note 2)                                                             |

| 9  | FOod Pulse Width                                                 | t <sub>DFW</sub>                                         |     | 244               |     | ns    | 150 pF Load (see Note 2)                                                             |

| 10 | Serial Input Setup Time                                          | tsis                                                     |     | 30                |     | ns    | (see Note 2)                                                                         |

| 11 | Serial Input Hold Time                                           | t <sub>SIH</sub>                                         |     | 50                |     | ns    | (see Note 2)                                                                         |

| 12 | Serial Output Delay Act to Act<br>High Z to Act<br>Act to High Z | t <sub>DAA</sub><br>t <sub>DZA</sub><br>t <sub>DAZ</sub> |     | 125<br>125<br>125 |     | ns    | 150 pF Load (see Note 2)<br>150 pF Load (see Note 2)<br>150 pF Load (see Notes 2 & 3 |

<sup>†</sup> Timing is over recommended temperature & power supply voltages.

Note 1) Note that this is a specification on the maximum parallel capacitance to AC ground, connected directly to the pins. Higher capacitance is acceptable when placed in series with resistor networks such as the line termination impedance.

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

Note 2) These timing parameters are mode independent (NT or LT).

<sup>3)</sup> High impedance is measured by pulling to the appropriate rail with  $R_L = 1k\Omega$ , with timing corrected to cancel time taken to discharge C<sub>L</sub>

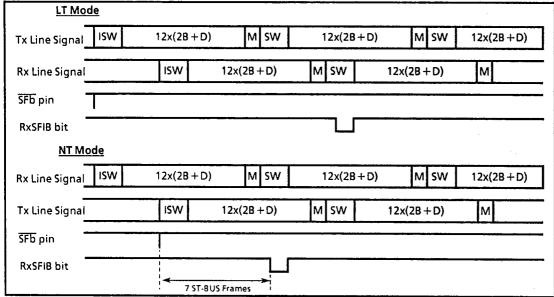

Figure 2. ST-BUS Timing LT Mode

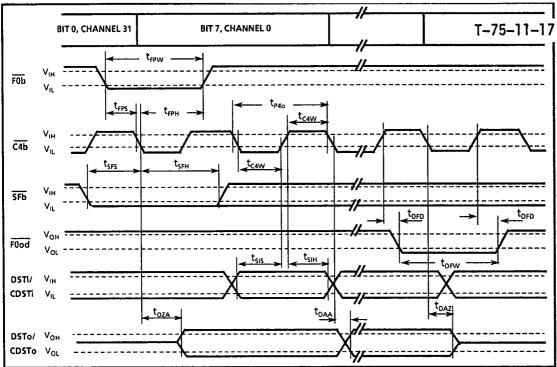

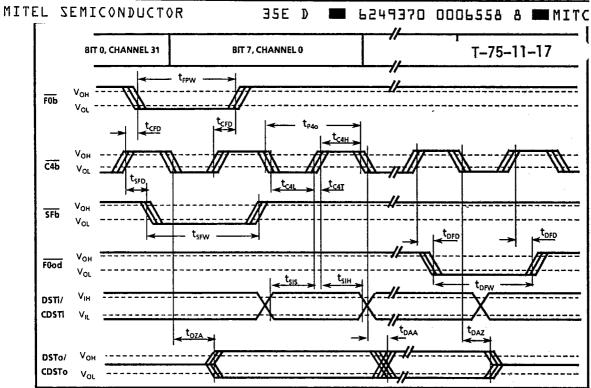

AC Electrical Characteristics' - ST-BUS Timing NT Mode (Ref. Figure 3)

|    | Characteristics                                                  | Sym                                                      | Min | Typ:              | Max | Units          | Test Conditions                                                                       |

|----|------------------------------------------------------------------|----------------------------------------------------------|-----|-------------------|-----|----------------|---------------------------------------------------------------------------------------|

| 1  | F0b Output Pulse Width                                           | t <sub>FPW</sub>                                         |     | 1                 |     | cycles         | $C_L = 150 \text{ pF}, \overline{C4b} \text{ cycles}$                                 |

| 2  | F0b Output Delay                                                 | t <sub>CFD</sub>                                         |     | 45                |     | ns             | 150 pF                                                                                |

| 3  | C4b Output Clock Period                                          | t <sub>P40</sub>                                         |     | 244               |     | ns             | 150 pF                                                                                |

| 4  | C4b Pulse Width High                                             | t <sub>C4H</sub>                                         |     | 88                |     | ns             | 150 pF                                                                                |

| 5  | C4b Pulse Width Low                                              | t <sub>C4L</sub>                                         |     | 137               |     | ns             | 150 pF (See Note 1)                                                                   |

| 6  | C4b Transition Time                                              | t <sub>C4T</sub>                                         |     | 15                |     | ns             | 150 pF                                                                                |

| 7  | SFb Output Delay                                                 | t <sub>SFD</sub>                                         |     | 45                |     | ns             | $C_L = 150  pF$                                                                       |

| 8  | SFb Output Pulse Width                                           | t <sub>SFW</sub>                                         |     | 1                 |     | cycles         | $C_L = 150 \text{ pF}, \overline{C4b} \text{ cycles}$                                 |

| 9  | FOod Delay                                                       | t <sub>DFD</sub>                                         |     | 45                |     | ns             | C <sub>L</sub> = 150 pF (see Note 2)                                                  |

| 10 | F0od Pulse Width                                                 | t <sub>DFW</sub>                                         |     | 1                 |     | cycles         | C <sub>L</sub> = 150 pF, C4b cycles (see Note 2)                                      |

| 11 | Serial Input Setup Time                                          | tsis                                                     |     | 30                |     | ns             | C <sub>L</sub> = 150 pF (see Note 2)                                                  |

| 12 | Serial Input Hold Time                                           | t <sub>SiH</sub>                                         |     | 50                |     | ns             | C <sub>L</sub> = 150 pF (see Note 2)                                                  |

| 13 | Serial Output Delay Act to Act<br>High Z to Act<br>Act to High Z | t <sub>DAA</sub><br>t <sub>DZA</sub><br>t <sub>DAZ</sub> |     | 125<br>125<br>125 |     | ns<br>ns<br>ns | 150 pF load (see Note 2)<br>150 pF load (see Note 2)<br>150 pF load (see Notes 2 & 3) |

<sup>†</sup> Timing is over recommended temperature & power supply voltages.

<sup>\*</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

The  $\overline{C4b}$  pulse width low will vary by  $\pm$  48ns during a phase-correction cycle. These timing parameters are mode independent (NT or LT).

High impedance is measured by pulling to the appropriate rail with  $R_L = 1k\Omega$ , with timing corrected to cancel time taken to discharge C

Figure 3. ST-BUS Timing NT Mode

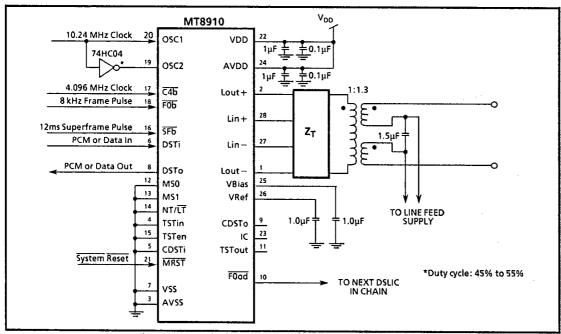

AC Electrical Characteristics'- External Clock Timing (Ref. Figure 4)

|   | Characteristics            | Sym                       | Min | Тур   | Max | Units | Test Conditions      |

|---|----------------------------|---------------------------|-----|-------|-----|-------|----------------------|

| 1 | OSC2 Clock Frequency       | 1/t <sub>MCF</sub>        |     | 10.24 |     | MHz   | (see Notes 1, 2 & 3) |

| 2 | OSC2 Clock Duty Cycle      | toch/<br>t <sub>MCF</sub> | 45  | 50    | 55  | %     |                      |

| 3 | OSC2 Clock Transition Time | tост                      |     |       | 10  | ns    |                      |

| 4 | C4b Jitter (wrt OSC2)      | t <sub>JC</sub>           | -15 |       | +15 | ns    | (see Note 3)         |

<sup>†</sup> Timing is over recommended temperature & power supply voltages.

- \* Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

- Notes: 1) External clock tolerance of ±5 PPM in LT mode or ±50 PPM in NT mode is required to meet ANSI specifications.

- 2) Absolute jitter on OSC2 must be less than 2.0 ns RMS in order to meet the full line length specifications.

- 3) In LT mode the C4b and OSC2 clocks must be externally frequency locked (i.e., f<sub>OSC2</sub> = 2.5 x f<sub>C4b</sub>). The relative phase between the clocks is not critical.

Figure 4. External Clock Timing in LT Mode

35E D ■ 6249370 0006559 T ■ MITC

| in Desci<br>Pin # | Name   | Description T-75-11-17                                                                                                                                                                                                                                                                           |

|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | Lout - | Line Out Minus. One of a pair of differential analog outputs for the 80 kbaud/s 2B1Q signal, biased at VBias.                                                                                                                                                                                    |

| 2                 | Lout+  | Line Out Plus. One of a pair of differential analog outputs for the 80 kbaud/s 2B1Q signal, biased at VBias.                                                                                                                                                                                     |

| 3                 | AVSS   | Analog Ground. Tie to VSS.                                                                                                                                                                                                                                                                       |

| 4                 | TSTin  | I/O Structure Test Input. When TSTen is high, TSTin is used as a source to all output drivers. Refer to "I/O Structure Test" in functional description for more details. Tie to VSS for normal operation.                                                                                        |

| 5                 | CDSTi  | Control/Data ST-BUS Input. A 2048 kbit/s serial PCM/data input for the D- and C-channels in Dual mode. Unused in Single mode and should be connected to VSS.                                                                                                                                     |

| 6                 | DSTi   | Data ST-BUS Input. A 2048 kbit/s serial PCM/data input for the D-, C-, B1- and B2-channels in Single mode. In Dual mode, only the B-channels are input.                                                                                                                                          |

| 7                 | VSS    | Ground.                                                                                                                                                                                                                                                                                          |

| 8                 | DSTo   | Data ST-BUS Output. A 2048 kbit/s serial PCM/data output for the D-, C-, B1- and B2-channels in Single mode. In Dual mode, only the B-channels are output. This output is placed in high impedance during the unused channel times.                                                              |

| 9                 | CDSTo  | Control/Data ST-BUS Output. A 2048 kbit/s serial PCM/data output for the D- and C- channels in Dual mode. It is placed in high impedance in Single mode, and during the unused channel times in Dual mode.                                                                                       |

| 10                | FOod   | Delayed Frame Pulse Output. A 244 ns wide negative going pulse indicating the end of the active ST-BUS channel times of the device to allow for daisy-chaining of othe ST-BUS devices. Active after channel 0 in Dual Port mode and Channel 3 in Single Por Mode.                                |

| 11                | TSTout | I/O Structure Test Output. When TSTen is high, the TSTout provides the output of ar XOR chain which is sourced from all digital inputs. Refer to "I/O Structure Test" in functional description for more details. Leave unconnected for normal operation.                                        |

| 12                | MS0    | Mode Select 0. CMOS input. Refer to Table 1.                                                                                                                                                                                                                                                     |

| 13                | MS1    | Mode Select 1. CMOS input. Refer to Table 1.                                                                                                                                                                                                                                                     |

| 14                | NT/LT  | NT/LT Mode Select. CMOS Input. When high the DSLIC is set up in NT mode. Whe low, the LT mode is selected.                                                                                                                                                                                       |

| 15                | TSTen  | I/O Structure Test Enable Input. This active high input enables the built-in test of a digital input and output structures. Refer to "I/O Structure Test" in functional description for more details. Tie to VSS for normal operation.                                                           |

| 16                | SFb    | Superframe Pulse. In LT mode, an input pulse once every superframe (12 ms) which when low during a falling edge of C4b within an F0b low pulse, sets the transm superframe boundary.                                                                                                             |

|                   | į      | In NT mode, a 244 ns wide output pulse once every 12 ms indicating the boundary of the transmit superframe. In NT mode, the superframe timing is generated from the line signal time base and, as such, \$\overline{5Fb}\$ will only be valid once the transceiver has achieved full activation. |

| 17                | C4b    | 4096 kHz Data Clock. In LT mode, a 4096 kHz ST-BUS clock input. In NT mode, a 409 kHz ST-BUS clock output frequency locked to the line signal.                                                                                                                                                   |

| 18                | FOB    | Frame Pulse. In LT mode, an 8 kHz input pulse indicating the start of the active ST-BU channel times. In NT mode, an 8 kHz output pulse extracted from the line sign indicating the start of the active ST-BUS channel times.                                                                    |

#### Pin Description (continued)

| Pin# | Name  | Description T-75-11-17                                                                                                                                                                                                                                                                                                                                                              |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

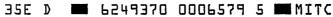

| 19   | OSC2  | Oscillator Output. When the DSLIC operates with an External Clock (typically LT mode) connect OSC2 to the output of an external inverter providing a 10.24 MHz ±5ppm clock (see "10.24 MHz Clock Interface" section).  When operating with a crystal (typically NT mode) connect one lead of the fundamental mode parallel resonator crystal (10.24 MHz ±50ppm in case of NT mode). |

| 20   | OSC1  | Oscillator Input. When the DSLIC operates with an External Clock (typically LT mode) connect OSC1 to the input of an external inverter (see Fig.18). When operating with a crystal (typically NT mode) connect the other lead of the fundamental mode parallel resonator crystal (10.24 MHz ±50ppm in case of NT mode).                                                             |

| 21   | MRST  | Master Reset. Active low CMOS input performs a master reset of the DSLIC.                                                                                                                                                                                                                                                                                                           |

| 22   | VDD   | Power Supply Input.                                                                                                                                                                                                                                                                                                                                                                 |

| 23   | 1C    | Internal Connection. Leave unconnected.                                                                                                                                                                                                                                                                                                                                             |

| 24   | AVDD  | Analog Power Supply. Connect to VDD.                                                                                                                                                                                                                                                                                                                                                |

| 25   | VBias | Bias Voltage. Decouple to AVSS through a 1.0μF ceramic capacitor.                                                                                                                                                                                                                                                                                                                   |

| 26   | VRef  | Reference Voltage. Decouple to AVSS through a 1.0µF ceramic capacitor.                                                                                                                                                                                                                                                                                                              |

| 27   | Lin - | Line Signal Input Minus. Internally biased at VBias.                                                                                                                                                                                                                                                                                                                                |

| 28   | Lin+  | Line Signal Input Plus. Internally biased at VBias.                                                                                                                                                                                                                                                                                                                                 |

#### **Functional Description**

The MT8910 Digital Subscriber Line Interface Circuit (DSLIC) is a high performance, full duplex transceiver which provides a complete interface to the U-reference point as specified in ANSI T1.601-1988. Operating in either master Line Terminator (LT) mode or slave Network Terminator (NT) mode, the DSLIC can be configured to operate at either end of the Digital Subscriber Line (DSL). The DSLIC supports full duplex transmission of a 2B + Dchannel format at 160 kbit/s over a single twisted pair with about 42 dB of loop attenuation at 40 kHz. To achieve this transmission performance, the DSLIC uses a 2B1O line code which is a four level pulse amplitude modulated (PAM) signal with no redundancy. This line code was approved by the American National Standards Institute technical subcommittee T1D1.3/T1E1.4. Using this line code, two binary bits are converted into one four level quaternary symbol. This results in an effective baud rate reduction from 160 to 80 kbaud/s allowing the transmission to benefit from reduced line attenuation and improved immunity to near end crosstalk (NEXT).

To complement the performance of the 2B1Q line code, the DSLIC uses an advanced echo cancelling hybrid (ECH) technique, by means of a transversal filter, that provides greater than 60 dB of echo cancellation. This cancellation, along with all equalization, is performed in the digital domain using dedicated DSP hardware. Since a digital

transversal echo canceller gives a linear representation of the echo, the MT8910 also has a non-linear echo canceller which works in parallel with the transversal filter to compensate for nonlinearities in the transmit path and the passive line termination. In addition, a jitter compensator is used to correct errors in the echo estimates which are sourced from corrections in the received timebase. The jitter compensator will interact directly with the echo taps in the transversal filter.

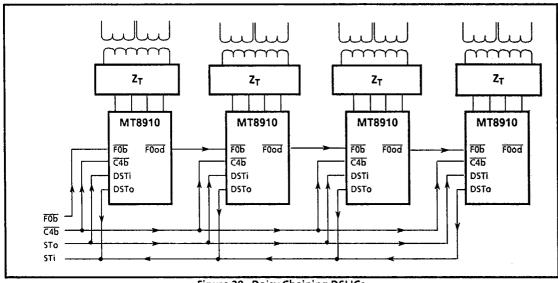

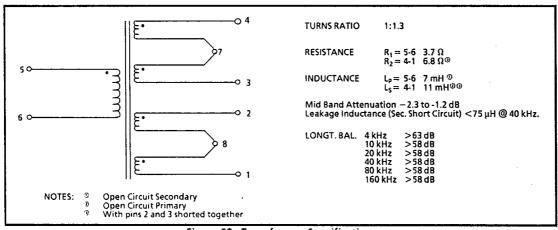

A block diagram of the DSLIC is shown in Figure 1. The DSLIC has two ports consisting of a serial system interface (Mitel's standard ST-BUS), and a line port which interfaces directly to the single twisted pair via a passive termination hybrid and a line pulse transformer.

The two B-channels and the D-channel to be transmitted on the line are input to the DSLIC (on the ST-BUS) into the transmit interface block. The sync word and maintenance bits are added to the data which is then formatted, scrambled and digitally encoded into 2B1Q symbols. This digital representation is passed through a finite impulse response filter which converts the digital representation into an analog waveform. The transmitted pulse is then passed through a smoothing filter whose output is passed to a differential line driver which is capable of driving the line directly through a passive hybrid and line pulse transformer.

35E D == 6249370 0006561 8 == MITC

On the receive side, the pre-cancelled signal drives a balanced receiver which feeds the input to an oversampled second-order delta sigma A/D converter. The digital representation of the received signal yields a Pulse Density Modulated (PDM) stream which is digitally filtered and decimated to the 80 kHz baseband. Intersymbol interference (ISI) introduced by the loop is cancelled by a decision feedback equalizer. This is achieved by taking a convolution of the received pulse with the estimated impulse response of the loop. The cancellation of ISI is performed in parallel with the echo cancellation. Estimated received echo is obtained by taking the convolution of the transmit signal with the estimated impulse response of the loop. Feedback from the jitter compensator and the non-linear corrector interact with the coefficients of the echo canceller to reduce the error introduced by jitter and non-linearities in the analog circuitry. The output of all these blocks is summed together and the result is the received data which is passed through a decoder and descrambler before being sent out in TDM bursts on the ST-BUS.

#### Line Port

The DSLIC interfaces to the U-reference point as defined in the ISDN Basic Access Reference model. As such, the transceiver transfers full duplex, time division multiplexed data at 160 kbit/s. This includes two 64 kbit/s PCM voice or data channels (B-channels), a 16 kbit/s signalling channel (D-channel) and 16 kbit/s for synchronization and overhead.

The two 64 kbit/s channels are defined as the B1-and B2-channels and they carry subscriber information such as digitally encoded voice, circuit switched data or packet switched data. The DSLIC will transfer both B-channels transparently from the ST-BUS port to the line port and vice versa once the device has acquired superframe synchronization<sup>®</sup>.

The 16 kbit/s D-channel is primarily intended to carry signalling information for circuit switching the

B-channels through the ISDN network. The D-channel can optionally carry packetized information and telemetry services. The D-channel is transmitted transparently through the DSLIC from the ST-BUS port to the line port and vice versa once the device has acquired superframe synchronization<sup>®</sup>. It is to be noted that the system interface has dedicated a full 64 kbit/s for the D-channel of which only the two first bits (D0 and D1) are actually carrying information. The other bits of the ST-BUS D-channel are reserved for future use.

Note <sup>9</sup>: Before superframe synchronization, data is not valid.

A third type of channel, the C-channel, is a nonbearer channel which provides a means for the system to control and monitor the functionality of the DSLIC. This control/status channel is accessed by the system through the ST-BUS. The C-channel provides access to three control registers and four status registers which provide complete control or status of all built-in features. Access to the control register is provided by two bits in the Control Register itself (CRSO and CRS1). Selection of the desired status register is performed using two bits in Control Register 1 (SRSO and SRS1). The C-channel also carries a control and status register for the 4 kbit/s M-channel which can be used as an additional maintenance channel. A detailed description of these registers is discussed in the ST-BUS port interface section.

T-75-11-17

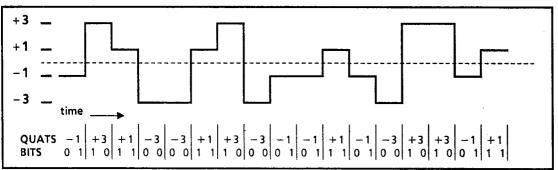

#### Line Code

The DSLIC transceiver uses the 2B1Q line code which is a four level Pulse Amplitude Modulated (PAM) code with no redundancy. The generation of the 2B1Q signal is achieved by grouping two consecutive bits into a bit field of which the first bit represents the sign bit and the second represents the magnitude. This yields four possible output codes as shown in Figure 5 (note that +3, +1, -1 and -3 are only symbols and they do not reflect the voltage on the line).

Figure 5. Example of 281Q Quaternary Symbols

The bit fields are grouped relative to the borders of the defined channels where the first bit field consists of bit 1 and bit 2 of the B1-channel, the second bit field consists of bit 3 and bit 4 of the B1-channel and so on.

Before converting the bit fields into output symbols, all bits except the framing pattern are scrambled with polynomials:

$$1 \oplus x^{-5} \oplus x^{-23}$$

for LT  $1 \oplus x^{-18} \oplus x^{-23}$  for NT

(where ⊕ is modulo two summation)

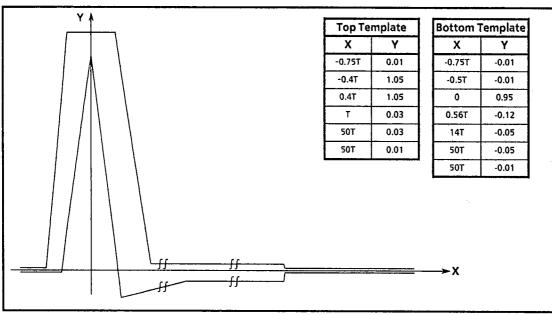

After encoding and scrambling, the bit fields are then converted into a quaternary symbol which conforms to the pulse template shown in Figure 6 below. With a random signal on the output, the DSLIC will transfer a nominal average power of about 11.5 dBm to the line with the recommended line circuit.

T-75-11-17

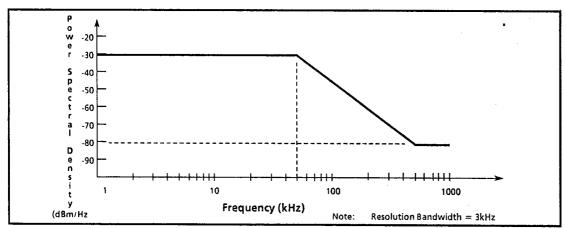

The upper bound of the Power Spectral Density (PSD) of the DSLIC transmitted signal falls below the PSD plot shown in Figure 7.

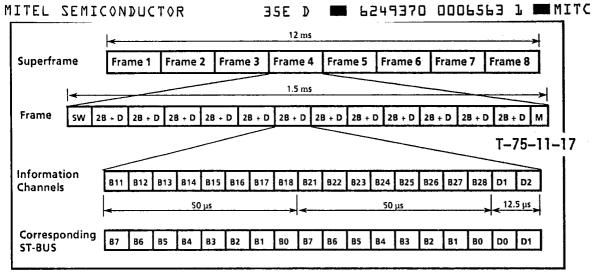

#### Framing

The frame structure in the DSLIC is 1.5 ms long and consists of twelve 2B+D-channels delimited by the

Figure 6. Normalized Pulse Template

Figure 7. Power Spectral DensityTemplate

Figure 8. Frame Structure

framing pattern at the start of the frame and the maintenance channel at the end. Framing for both the LT and the NT is performed using a 9 symbol synchronization word. This sync word (SW) has the following structure:

Sync Word:

$$+3$$

,  $+3$ ,  $-3$ ,  $-3$ ,  $+3$ ,  $-3$ ,  $+3$ ,  $+3$

Eight DSLIC frames are grouped into a superframe delimited by inverting the sync word (ISW): -3, -3, +3, +3, +3, -3, +3, -3, -3. This second level of framing is used to assign the M-channel bits as defined in the ANSI T1.601-1988. The framing structure is shown in Figure 8.

Transmission between the LT and NT is fully synchronous. As such, the frame/superframe boundaries between the NT receive frame and the NT transmit frame have a fixed phase relationship.

The transmitted frame/superframe from the NT is delayed by 60  $\pm$  2 quaternary symbols (quats) with respect to its received frame/superframe. Since the NT extracts all its timing from the line, the DSLIC will maintain the required phase relationship between the frames and superframes and will insert the SW and ISW during the proper time interval.

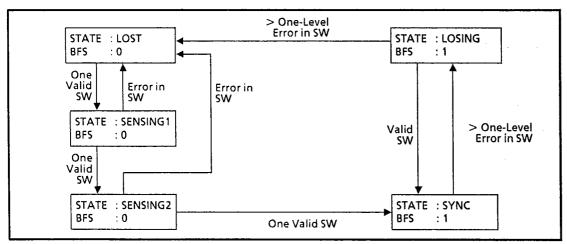

Basic Frame Synchronization (BFS) is achieved using the algorithm shown in Figure 9. The DSLIC searches for the sync word or the inverted sync word within the received data stream. After detecting three consecutive synchronization patterns spaced exactly 120 quats apart, the DSLIC declares terminal synchronization by setting the bits of the Internal State Indicator to 111 in Status Register 1. A loss of synchronization is declared by the DSLIC when at least one of the nine quats at the

Figure 9. Frame Synchronization State Diagram

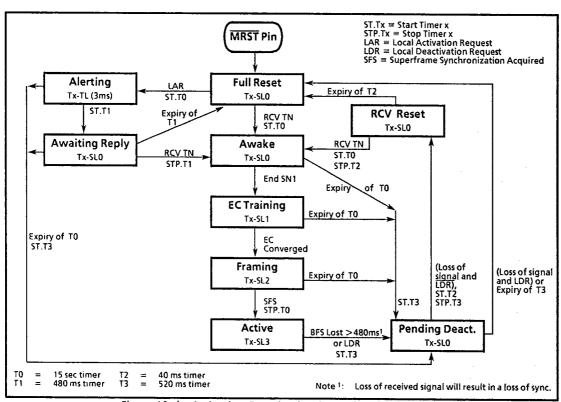

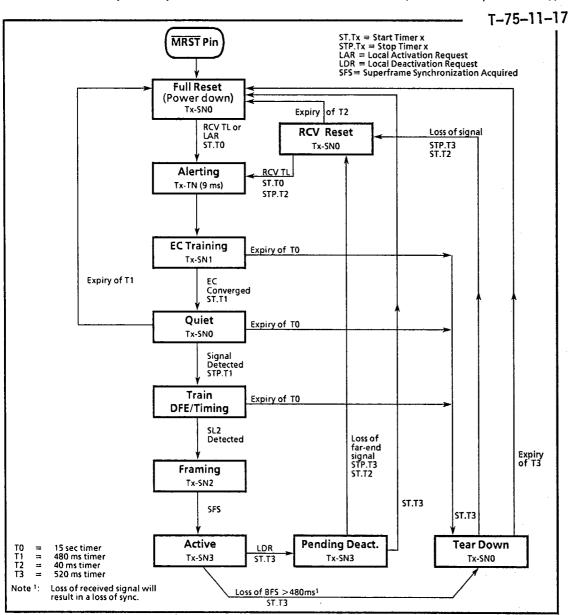

T1.601-1988 standards. The activation sequence for the DSLIC is mode dependent and is outlined in Figures 10a) and b).

T-75-11-17

beginning of each Basic Frame differs by more than one quantization level for two consecutive frames.

A search for superframe synchronization will begin only after Basic Frame sync has been found. The DSLIC will declare superframe sync (SFS) on the first occurrence of the properly spaced Inverted Sync Word (ISW) once Basic Frame sync has been acquired. The synchronized state is identified by the status of internal state bits ISO, IS1 and IS2 found in Status Register 1.

The DSLIC will lose superframe sync under three conditions;

- 1) if the DSLIC loses basic frame sync,

- if the ISW does not occur exactly eight basic frames apart,

- 3) if the ISW is received when it is not expected.

#### Activation/Deactivation

The DSLIC has a complete activation/deactivation state machine which allows the user to activate or deactivate the link as per the requirements in the

in the LT mode, the request for activation can be initiated in two ways. Setting the start/stop bit in the Control Register 1 will result in the generation of a repeated pattern of four +3 symbols followed by four -3 symbols producing a 10 kHz activation tone (TL) for 3 milliseconds. The DSLIC can also be activated by receiving a 10 kHz activation tone from the NT (TN). Once the NT has generated a tone, progression through the state machine follows the algorithm as shown in Figure 10 (a).

In the NT mode, the request for activation can be initiated in two ways. Setting the start/stop bit in the Control Register 1 will result in the generation of a repeated pattern of four +3 symbols followed by four -3 symbols resulting in the transmission of the NT activation tone (TN). The DSLIC can also be activated by receiving TL from the LT to which the NT will respond with its own activation tone (TN). Progression through the state machine will follow the algorithm as shown in Figure 10 (b).

Figure 10 a) - Activation/Deactivation State Diagram - LT Mode

# 35E D ■ 6249370 0006565 5 ■MITC

During the activation sequence, there is an extensive exchange of signals between the LT and the NT. This handshaking of information is required to allow individual transceivers to train both their echo cancellers and decision feedback equalizers. All possible signals are described below.

- TN: A 10 kHz activation tone sourced by the NT which is generated by sending a continuous pattern of four +3 symbols followed by four -3 symbols.

- SNO: SNO is a no signal condition which is used to indicate to the LT that the NT has finished training its echo canceller.

- SN1: An NT generated signal consisting of a framed (but not superframed), scrambled 2B1Q signal which carries all 1s in the B-, D- and M-channels. This signal is used to train the NT's echo canceller.

- SN2: An NT generated signal consisting of a framed (but not superframed),

Figure 10 b) - Activation/Deactivation State Diagram - NT Mode

scrambled 2B1Q signal which carries all 1s in the B-, D- and M-channels. This signal is used to train the LT's DFE.

- SN3: An NT generated signal consisting of a fully framed and superframed scrambled 2B1Q signal which carries information in all the B-, D- and Mchannels.

- TL: A 10 kHz activation tone sourced by the LT which is generated by sending a continuous pattern of four +3 symbols followed by four -3 symbols.

- SLO: SLO is a no signal condition generated from the LT.

- SL1: An LT generated signal consisting of a framed (but not superframed), scrambled 2B1Q signal which carries all 1s in the B-, D- and M-channels. This signal is used to train the LT's echo canceller.

- SL2: An LT generated signal consisting of a fully framed and superframed scrambled 2B1Q signal which carries all Os in the B- and D-channels with information in the M-channel. This signal is used to train the NT's DFE.

- SL3: An LT generated signal consisting of a fully framed and superframed scrambled 2B1Q signal which carries information in all the B-, D- and Mchannels

The reset state consists of two substates, the receive reset state and full reset state. The full reset state is entered following a power-up or after the expiry of the receive reset timer (40 ms). The receive reset state is a transient state which is entered once the DSLIC has detected a loss of received signal while the transceiver is not transmitting. In this state, the transceiver will not initiate the start-up sequence but is capable of responding to the appropriate activation tone. When the timer in the receive reset state has timed out (40 ms), the transceiver enters the full reset state.

All timers surrounding the reset states are included in the DSLIC and have been set as per the ANSI-T1.601-1988:

- Failure to complete a start-up sequence timer is set at 15 seconds.

- Loss of received signal timer is set at 480 ms as is the loss of synchronization.

- The receive reset state timer is set to 40

- A fourth timer (not specified in ANSI T1.601-1988) has been included which will restrict the time to 520 ms for a deactivation sequence.

The DSLIC will enter a deactivated state on the assertion of a deactivation request (setting the Start/Stop bit to 0 in Control Register 1, and the subsequent loss of the received signal). Once the deactivation process has been completed, the request for activation can follow a warm start process as defined in ANSI T1.601-1988.

#### **Loop Performance**

T-75-11-17

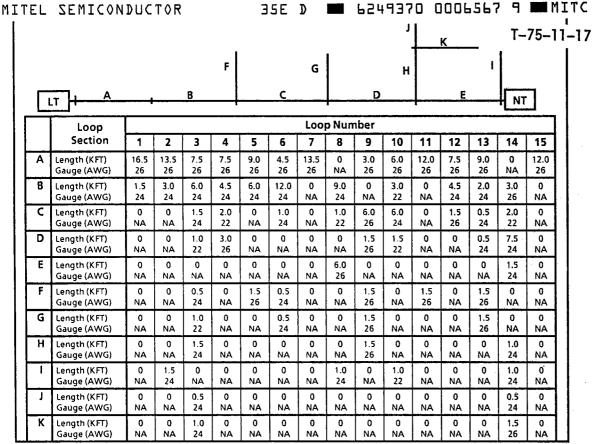

The DSLIC operates on a digital subscriber line (DSL) which is a two wire twisted pair metallic medium typically used for transmission between the central office (LT) and the customer premise equipment (more commonly referred to as "Basic Access Interface on the Network side of the NT"). The ANSI T1.601-1988 (or CCITT Recommendation G.961 Annex II) standard defines a set of test loops which comprise the acceptance criteria for the assortment of "worst case" loops that could be seen in the North American loop plant. Operation over these loops, as well as the 0 km length loop, would assure performance on over 99 % of the North American loop plant. These loops are summarized in Figure 11. When used with the recommended passive line termination, the DSLIC will operate over 42 dB of line attenuation (@40 kHz) with a bit error rate of 10-7.

#### **ST-BUS Interface**

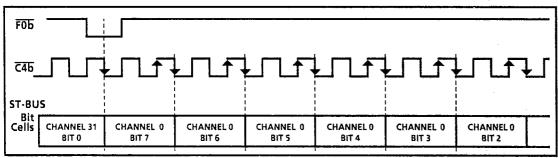

The ST-BUS is a synchronous time division multiplexed serial bussing scheme with data streams operating at 2048 kbit/s configured as 32, 64 kbit/s channels (refer to Figure 12). Synchronization of the data transfer is provided from a frame pulse which identifies the frame boundaries and repeats at an 8 KHz rate. Figure 12 shows how the frame pulse (F0b) defines the ST-BUS frame boundaries. All data is clocked into the device on the rising edge of the 4096 kHz clock (C4b) three quarters of the way into the bit cell, while data is clocked out on the falling edge of the 4096 kHz clock at the start of the bit cell.

The bits on the ST-BUS are numbered bit 7 to bit 0 as outlined in Figure 12. Information transferred from the system port to the line port, will maintain the integrity of the bit order.

All timing signals, i.e., FOb, C4b and SFb, are bidirectional. The I/O configuration of these pins is controlled by the mode of operation (LT or NT). In the LT mode, these timing signals must be supplied from an external source and the DSLIC will in turn uses these timing signals to transfer information to and from the line port or the ST-BUS port. In the NT mode, timing is generated from an on board digital phase locked loop which extracts timing from the

Figure 11. Performance Loops

received data on the DSL and generates the system frame pulse ( $\overline{F0b}$ ), the system 4096 kHz clock ( $\overline{C4b}$ ) and the system superframe pulse ( $\overline{SFb}$ ).

The superframe timing signal (\$Fb) is an active low signal with a period of 12ms which is required to provide a reference for structuring the maintenance channel (M channel). In the LT mode, the \$Fb is an input which, when set low during the system frame pulse (\$F0b), will set the phase of the transmit superframe. As an alternative, the \$Fb pin can be tied high and the device will automatically

establish the superframe position. This function can also be activated in software (LT mode only) through a bit in Control Register 1 (TxSFB). The transition of this bit from a 1 to a 0 will reset the superframe counter, and the beginning of the transmitted superframe will be referenced to the ST-BUS frame after the frame in which the transition in the TxSFB bit occurred. If the TxSFB bit is not being used, it should always be set to one.

Figure 12. ST-BUS Functional Timing

In the NT mode, the SFb pin is an output which generates an active low signal at the boundary of the transmit superframe. Since the SFb is referenced to the receive time base, SFb is only valid after superframe synchronization has been achieved. In the NT mode, the TxSFB bit is ignored since the transmit superframe has a fixed phase relationship with respect to the received superframe. T-75-11-17

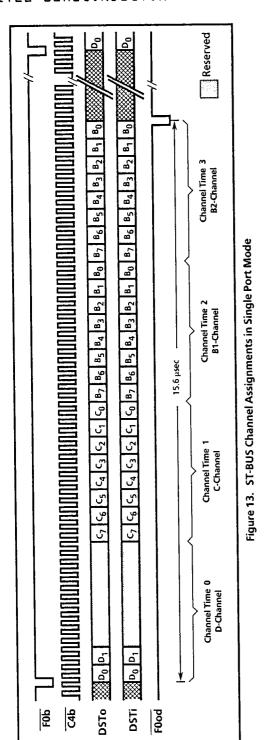

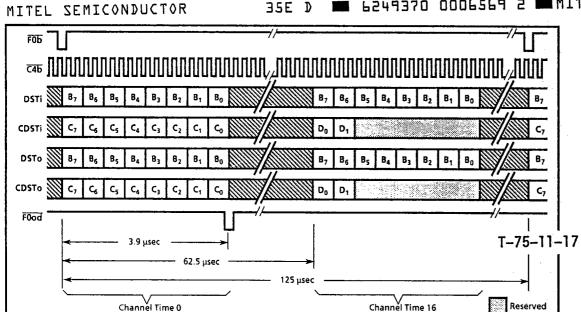

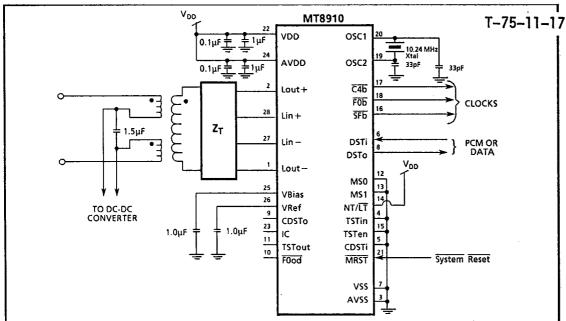

The DSLIC has two possible system port configurations; single port mode or dual port mode. In the single port mode, the DSLIC uses the first four timeslots of the DSTi and DSTo data streams (as shown in Figure 13). ST-BUS Channel 0 is allocated to the D-channel, ST-BUS Channel 1 to the C-channel, while ST-BUS Channel 2 and 3 are allocated to the B1 and B2 channels respectively. In this mode, the CDSTi and CDSTo streams are not used. In the dual port mode, the DSLIC uses both the DSTi/DSTo streams as well as the CDSTi/CDSTo streams to allow the separation of the data and control. The two B-channels are routed through the DSTi/DSTo streams and the C- and D-channels are routed through the CDSTi/CDSTo streams. In each case, timeslot 0 and 16 will carry the respective channels (refer to Figure 14). To simplify line card designs, the DSLIC provides a delayed frame pulse (FOod) to eliminate the need for a channel assignment circuit. This signal is used to drive subsequent devices in the daisy chain configuration. In this type of arrangement, only the first DSLIC in the chain will receive the system frame pulse (F0b) with the following devices receiving its predecessor's delayed frame pulse. In conjunction with the delayed frame pulse, the unused timeslots on the ST-BUS will be placed into a high impedance state to avoid having contention on the system bus.

Selecting the single port or the dual port mode is performed using Mode Select 1 (MS1). With MS1 = 0, the DSLIC is in the single port mode while MS1=1 places the DSLIC in the dual port mode. Mode Select 0 (MS0) determines the order of the Dand C-channels while the DSLIC is operating in the dual port mode. With MS0 = 0, the C-channel is found in timeslot 0 and the D-channel is found in timeslot 16. With MS0 = 1, the D-channel is found in timeslot 0 and the C-channel is found in timeslot 16 (refer to Table 1).

| 1454 | MSO  | Operating Mode |       |  |  |  |  |

|------|------|----------------|-------|--|--|--|--|

| MS1  | MISO | Dual/Single    | DC/CD |  |  |  |  |

| 0    | 0    | Single         | DC    |  |  |  |  |

| 0    | 1    | Single         | DC    |  |  |  |  |

| 1    | 0    | Dual           | CD    |  |  |  |  |

| 1    | 1    | Dual           | DC    |  |  |  |  |

Table 1. Truth Table for Mode Select Pins

Figure 14. ST-BUS Channel Assignment in Dual Port Mode

#### Control/Status Channels

The Control and Status information between the DSLIC transceiver and the controlling entity is carried by the C-channel. The DSLIC has three input registers; Control Register 1, 2 and 3 (selected through the CRSO and CRS1 bits) and four output registers; Status Register 1 through Status Register 4 (selected through the SRSO and SRS1 bits in Control Register 1).

The input C-channel is used to access Control Registers 1, 2 and 3. Bit 0 and 1 of the C-channel (CRSO and CRS1) allows the selection of the desired Control Register as described below.

| CRS1 | CRS0 | <b>Definition</b>  |

|------|------|--------------------|

| 0    | 0    | Control Register 1 |

| 0    | 1    | Control Register 2 |

| 1    | 0    | Control Register 3 |

| 1    | 1    | Reserved           |

The C-channel on the ST-BUS must be continuously written to every frame. If the user accesses a Control Register, the information in the other Control Registers is latched. Any input requested through the Control Registers will be activated on the next frame boundary.

#### **Control Register 1**

Setting CRS0 and CRS1=0 routes the C-channel to Control Register 1 allowing access to the functions described in Table 2. These bits are further described below.

Bits 7 and 6 of Control Register 1, SRS1 & SRS0, select which status register will be output in the next ST-BUS frame. The selection of the Status Register is as follows:

| SO Definition     |

|-------------------|

| Status Register 1 |

| Status Register 2 |

| Status Register 3 |

| Status Register 4 |

|                   |

Bit 5 of Control Register 1, TxSFB, is used to establish the position of the transmit superframe (LT mode only). Setting this bit from a logic one to a logic zero will reset the frame counters on the next occurrence of the frame pulse establishing the superframe position. Once the boundaries to the superframe have been established, the device will sustain the position of the superframe by allowing the counters to wrap around. The user can also elect to set this bit to a logic zero with a periodicity of 12 ms.

Bit 4 of Control Register 1, BSWAP, allows the multiplexing of the two B-channels transferred over the digital subscriber line with the B-channels presented at the system interface. A logic high on the bit will result in the B1-channel on the system interface to be transmitted in the B2-channel on the line port and vice versa. The same principle applies to the B2-channel at the system interface.

Bit 3 of Control Register 1, CCRC, allows the user to introduce errors in the CRC bits calculated by the

|     | bit 7  | bit | 6    | bit 5       | bit 4       | bit 3       | bit 2           | bit 1      | bit 0       | _<br>1 |

|-----|--------|-----|------|-------------|-------------|-------------|-----------------|------------|-------------|--------|

|     | SRS1   |     | 350  | TxSFB       | BSWAP       | CCRC        | START/STOP      | CRS1       | CR50        | 1      |

| Bit | Name   | e   | T    | ·           |             | De          | scription       |            | T-75-11     | _      |

| 7.6 | SRS1 S | RSD | Stat | us Pagistar | Salact Sala | cts which o | of the four sta | tus rogist | are will be | ~      |

| Bit  | Name       | Description T-75-11-17                                                                                                                                                                                                                                                                                                                                                 |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,6  | SRS1, SRS0 | Status Register Select. Selects which of the four status registers will be output in the next ST-BUS frame.                                                                                                                                                                                                                                                            |

| 5    | TxSFB      | Transmit Superframe Reset. In LT mode, transition from a 1 to a 0 on this bit resets the superframe counters in the next ST-BUS frame in order to establish the transmit superframe boundary. If the external pin is being used to set the superframe boundary this bit should be held high. Not used in NT mode.                                                      |

| 4    | BSWAP      | When this bit is set to 1, the location of the B1 channel on the ST-BUS is swapped with the location of the B2 channel. This affects both directions of the ST-BUS.                                                                                                                                                                                                    |

| 3    | CCRC       | Corrupt CRC. When set to 1, the 12 bit CRC transmitted on the line is corrupted.                                                                                                                                                                                                                                                                                       |

| 2    | START/STOP | A low to high transition while the transceiver is in the full reset state will initiate one activation attempt. A high to low transition of this bit while the transceiver is in the active state will initiate a deactivation procedure. During start-up, 2B+D channels should remain set to 0 or 1 until transparency of network is achieved (indicated by act = 1). |

| 1, 0 | CRS1, CRS0 | Control Register Select 1 and 0. Must be set to 0, 0 to address Control Register 1.                                                                                                                                                                                                                                                                                    |

Table 2. Control Register 1

DSLIC. This allows the user to verify the error detection protocol used over the M-channel.

Bit 2 of Control Register 1, START/STOP, provides a mechanism to allow the user to initiate a line activation or deactivation. This bit is edge sensitive with a low to high transition requesting an activation, and a high to low transition requesting a deactivation. The activation and deactivation procedure will follow the protocol defined in the ANSI T1.601-1988. The activation request will only be recognized if the transceiver is in a full reset state. Any activation attempt while the transceiver is in any other state will be ignored. Similarly, any deactivation request generated while the transceiver is not in the active state will be ignored.

#### **Control Register 2**

Setting CRS0=1 and CRS1=0 routes the C-channel to Control Register 2 allowing access to the functions described in Table 3. These bits are further described below.

Bits 7 to 4 of Control Register 2 (DS4 to DS1) provide access to the multiple diagnostic features supported on the DSLIC as outlined in Table 3. These include the per-channel loopbacks at the system interface as well as a loopback at the line interface. (It must be noted that the analog loopback, L<sub>out</sub> to L<sub>in</sub>, is only supported in the LT mode or with MSWAP in the NT mode and that the

output signal will still be presented to the line but will not follow the standard activation sequence). Along with the extensive loopback capabilities, the DSLIC also allows the generation of multiple signals which can be used during qualification and servicing of a DSL. The isolated pulse test diagnostics signal causes the transmission of a +3 or +1 symbol once every 1.5 ms. This will generate pulses that can be used for template measurements. The Insertion Loss Measurement (ILM) test signal is a scrambled all 1s 2B1Q coded signal which contain both the SW and ISW. This test signal can be used to make insertion loss measurements over the DSL loop. Lastly, the DSLIC can be placed into a quiet mode to allow a Remote Test Unit (RTU) to perform impulse noise, crosstalk and other transient impairment measurements as described in the ANSI "ISDN Management - Basic Rate Physical Layer".

Bit 3 of Control Register 2 (ADCGAIN) controls the gain value of the A/D converter. This function can be used to introduce more gain in the receive path when the transceiver is being used over long loops.

Bit 2 of Control Register 2 (MSWAP) may be used when the DSLIC is operating as an LT within a line card application. The mode swap feature has the effect of changing the scrambling polynomial and activation state machine such that it can simulate the operation of an NT transceiver. This allows a transmission test between two devices on the same line card. (For this function to work properly, the

35E D ■ 6249370 0006571 0 ■ MITC

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3   | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|---------|-------|-------|-------|

| DS4   | DS3   | DS2   | DS1   | ADCGAIN | MSWAP | CRS1  | CR\$0 |

| Bit      | Name       |                               |                      |                     |                        | Description                                    | T-75-11-17                                                                                  |

|----------|------------|-------------------------------|----------------------|---------------------|------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|

| 7,6,     | DS4 - DS1  | Diagnostic :                  | Select Bi            | ts.                 | <del></del>            |                                                |                                                                                             |

| 5,4      |            | DS4                           | DS3                  | DS2                 | DS1                    | Channels                                       | Function                                                                                    |

|          |            | 0                             | 0                    | 0                   | 0                      | -                                              | Normal Operation                                                                            |

|          |            | 0                             | STi to STo Loopback® |                     |                        |                                                |                                                                                             |

| į        |            | 0                             | 0                    | 1                   | 0                      | B2                                             | STi to STo Loopback®                                                                        |

| 1        |            | 0                             | 0                    | 1                   | 1                      | B1 + B2                                        | STi to STo Loopback®                                                                        |

| 1        |            | 0                             | 1                    | 0                   | 0                      | 2B + D                                         | STi to STo Loopback ®                                                                       |

| l        |            | 0                             | 1                    | 0                   | 1                      | B1                                             | STo to STi Loopback ®                                                                       |

|          |            | 0                             | 1                    | 1                   | 0                      | B2                                             | STo to STi Loopback ®                                                                       |

|          |            | 0                             | 1                    | 1                   | 1                      | B1 + B2                                        | STo to STi Loopback <sup>®</sup>                                                            |

|          |            | 1                             | 0                    | 0                   | 0                      | 2B + D                                         | STo to STi Loopback ®                                                                       |

| ļ        |            |                               |                      |                     |                        | L <sub>out</sub> to L <sub>in</sub> Loopback®® |                                                                                             |

|          |            | 1                             |                      |                     |                        | Isolated +3 pulse®                             |                                                                                             |

|          |            | 1                             | 0                    | 1                   | 1                      | -                                              | Isolated +1 pulse®                                                                          |

|          |            | 1                             | 1                    | 0                   | 0                      | -                                              | Transmit 10 kHz Tone                                                                        |

| İ        |            | 1                             | 1                    | 0                   | 1                      | •                                              | ILM Test Signal®                                                                            |

|          |            | 1                             | 1                    | 1                   | 0                      | -                                              | Quiet Mode                                                                                  |

| <u> </u> |            | 1                             | 11                   | 1                   | 1                      | -                                              | Reserved                                                                                    |

| 3        | ADCGAIN    | Selects between selects a 3 d | ween tw<br>B highe   | vo gain<br>rgain.   | values i               | n the delta-sigm                               | na A/D converter. When high,                                                                |

| 2        | MSWAP      | scrambling/                   | descran<br>ne same   | nbling p<br>LT line | oolynomi<br>card to ex | als and activation<br>change static da         | alt in the DSLIC using the NT's on sequence. This allows two ata in the B- and D- channels. |

| 1, 0     | CRS1, CRS0 | Control Reg<br>Register 2.    | jister Se            | lect 1 a            | nd 0. Mu               | ist be set to 0, 1                             | respectively to address Control                                                             |

Table 3. Control Register 2

The ST-BUS incoming data is still output on the line if the DSLIC is activated. Supported in both SINGLE and DUAL port modes. The incoming data from the line is still output on to the ST-BUS. The other incoming channels on the ST-BUS are still output on to the line if the device is activated. Supported in both SINGLE and DUAL port modes. Signal is internally looped back and is still output to the line and overrides the internal activation state machine. One pulse is transmitted every 1.5 ms.

The Insersion Loss Measurement Test Signal is a scrambled, framed 2B1Q signal.

|      | bit 7      | oit 6 | bit 5                                                                                            | bit 4      | bit 3        | bit 2                    | bit 1                       | bit 0        |            |  |  |  |

|------|------------|-------|--------------------------------------------------------------------------------------------------|------------|--------------|--------------------------|-----------------------------|--------------|------------|--|--|--|

|      | M1         | M2    | МЗ                                                                                               | M4         | M5           | M6                       | CRS1                        | CRS0         |            |  |  |  |

| Bit  | Name       |       |                                                                                                  | •          | Des          | scription                | <u> </u>                    | L            | the and of |  |  |  |

| 7-2  | M1 - M6    | the r | aintenance<br>next DSL B<br>ional descri                                                         | asic Frame | ts 1 to 6. M | -bits which we "Maintena | vill be trans<br>ance Chanr | mitted at th | e end      |  |  |  |

| 1, 0 | CRS1, CRS0 | Contr | Control Register Select 1 and 0. Must be set to 1, 0 respectively to address Control Register 3. |            |              |                          |                             |              |            |  |  |  |

Table 4. Control Register 3

input clocks to the two devices must be frequency locked.)

#### **Control Register 3**

Setting CRS1 and CRS0 to 1, 0, respectively, routes the input C-channel to Control Register 3, allowing access to the transmit M-bits as shown in Table 4. The transmit M-channel is a 4 kbit/s maintenance channel which may carry the EOC messages (with overhead) as specified in T1.601-1988. Except for the CRC bits, the M-bits are treated as a transparent data channel through the DSLIC. CRC bits will be generated by the transceiver and will be inserted into the M-channel during their respective M-bit time slots. (This implies that all input M-bits which are defined as CRC bits will be overwritten by the transceiver.) Structuring of the M-bits is described in the "Maintenance Channel" section of the functional description.

#### **Control Words After Reset**

Applying a logic low to the MRST pin will result in the three control registers assuming a reset state. Following a master reset, the three Control Registers will take the following states:

| Contr     | ol Re     | gister    | 1:        |           |           |           |           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| <u>C7</u> | <u>C6</u> | <u>C5</u> | <u>C4</u> | <u>C3</u> | <u>C2</u> | <u>Ç1</u> | <u>C0</u> |

| 0         | 0         | 1         | 0         | 0         | 0         | 0         | 0         |

| Contr     | ol Re     | gister    | 2:        |           |           |           |           |

| <u>C7</u> | <u>C6</u> | <u>C5</u> | <u>C4</u> | <u>C3</u> | <u>C2</u> | <u>C1</u> | <u>C0</u> |

| 0         | 0         | 0         | 0         | 0         | 0         | 0         | 1         |

| Contr     | ol Re     | gister    | 3:        |           |           |           |           |

| <u>C7</u> | <u>C6</u> | <u>C5</u> | <u>C4</u> | <u>C3</u> | <u>C2</u> | <u>C1</u> | <u>C0</u> |

|           |           |           | 4         |           |           | 4         | _         |

### Status Register 1

When SRID1=0 and SRID0=0, the contents of Status Register 1 are being output in the C-channel allowing the system to monitor the functions described below. (Refer to Table 5.)

Bits 7 and 6 of Status Register 1, SRID1 and SRID0, are used to identify which status register is being carried in the output C-channel. These bits are encoded as follows:

| SRID1 | SRID0 | <u>Definition</u> |

|-------|-------|-------------------|

| 0     | 0     | Status Register 1 |

| 0     | 1     | Status Register 2 |

| 1     | 0     | Status Register 3 |

| 1     | 1     | Status Register 4 |

Bits 5, 4 and 3 of Status Register 1, IS2, IS1 and IS0, provide an indication of the internal state of the device. The decoded states are as follows:

| <u> 152</u> | <u>IS1</u> | <u> 150</u> | Definition T-75-11-17                     |

|-------------|------------|-------------|-------------------------------------------|

| 0           | 0          | 0           | Full Reset                                |

| 0           | 0          | 1           | Training with no sync                     |

| 0           | 1          | 0           | Training with sync but no superframe sync |

| 0           | 1          | 1           | Training with sync and superframe sync    |

| 1           | 0          | 0           | Loss of sync                              |

| 1           | 0          | 1           | NA                                        |

| 1           | 1          | 0           | Loss of superframe sync                   |

| 1           | 1          | 1           | Active                                    |

Bit 2 of Status Register 1, RxSFIB, is used to indicate the reception of the receive superframe boundary in both the LT and NT modes.

Bit 0 of Status Register 1, CRCERR, indicates the state of the CRC check. A logic high on this bit states that the CRC check calculated by the DSLIC did not correspond to the CRC bits received in the M-channel. This bit will only be updated once every superframe.

#### Status Register 2

When SRID1=0 and SRID0=1, the contents of Status Register 2 are being output in the C-channel allowing the system to monitor the status of the quantizer signal to noise ratio bits (refer to Table 6). The QSNR bits reflect the eye closure of the received signal and represent the signal (+1 symbol) to noise ratio at the input of the quantizer. This information can be used to indicate the error performance of the transceiver. For a more accurate indication of QSNR, these bits should be averaged over a period of 64 ST-BUS frames (640 baud). The conversion of the five bit output to QSNR is shown in Table 6. For a bit error rate of greater than 10-7, the theoretical QSNR should be greater than 15.7dB.

#### **Status Register 3**

When SRID1=1 and SRID0=0, the contents of Status Register 3 are being output in the C-channel allowing the system to monitor the mean level of the received symbols (refer to Table 7). The Received Pulse Amplitude bits (RPA4 to RPA0) provide an estimate of the attenuation of the loop. The representation of the RPA bits is shown in Table 7.

# MITEL SEMICONDUCTOR 35E D == 6249370 0006573 4 == MITC

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2  | bit 1 | bit 0  |

|-------|-------|-------|-------|-------|--------|-------|--------|

| SRID1 | SRID0 | IS2   | IS1   | ISO   | RxSFIB | RSV   | CRCERR |

| Bit   | Name          |                  |                                                      | Description                                                                                                                                                                                                                                                         | T-75-11-17             |

|-------|---------------|------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 7,6   | SRID1, SRID0  | Status Reg       | Always reads 0,0 when Status Register 1              | is output.                                                                                                                                                                                                                                                          |                        |

| 5,4,3 | IS2, IS1, ISO | Internal St  IS2 | ate Indi<br><u>ISO</u><br>0<br>1<br>0<br>1<br>0<br>1 | cation. <u>Definition</u> Full Reset State Training with no Basic Frame Sync Training with Basic Frame Sync but no Su Training with Basic Frame Sync and Supe Loss of synchronization after E.C. has cor NA Loss of superframe sync after E.C. has cor Active State | rframe Sync<br>nverged |

| 2     | RxSFIB        |                  |                                                      | me Indication. When low, indicates the be<br>bit is low for one ST-BUS frame, then high                                                                                                                                                                             |                        |

| 1     | RSV           | Reserved.        | Always                                               | read a 0.                                                                                                                                                                                                                                                           |                        |